Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Core ProcessorXC800Core Size8-BitSpeed24MHzConnectivityCANbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Number Of Case-Nonting Type-Nonting Type-Not Type- | Details                    |                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------|

| Core Size8-BitSpeed24MHzConnectivityCANbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-Nutage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOperating TypeInternalOperating Type-Anov C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                      | Product Status             | Last Time Buy                                                                   |

| Speed24MHzConnectivityCANbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                   | Core Processor             | XC800                                                                           |

| ConnectivityCANbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-And Size / Case-Oscillator Device Package-                                                                                                                                                                                                                                                                                                                    | Core Size                  | 8-Bit                                                                           |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Package / Case-And Size-Package / Case-Supplic Device Package-                                                                                                                                                                                                                                                                                                                                                                | Speed                      | 24MHz                                                                           |

| Number of I/O34Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                       | Connectivity               | CANbus, SSI, UART/USART                                                         |

| Program Memory Size24KB (24K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                        | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Number of I/O              | 34                                                                              |

| EEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Program Memory Size        | 24KB (24K x 8)                                                                  |

| RAM Size1.75K × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Program Memory Type        | FLASH                                                                           |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EEPROM Size                | -                                                                               |

| Data Converters     A/D 8x10b       Oscillator Type     Internal       Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RAM Size                   | 1.75К х 8                                                                       |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type-Package / Case-Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data Converters            | A/D 8x10b                                                                       |

| Mounting Type     -       Package / Case     -       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | Internal                                                                        |

| Package / Case - Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | -                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Package / Case             | -                                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc886c6ffa5vackxuma1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Supplier Device Package    | -                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886c6ffa5vackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### XC886/888 Data Sheet

#### Revision History: V1.2 2009-07

| Previous   | s Versions: V1.0, V1.1                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------|

| Page       | Subjects (major changes since last revision)                                                                 |

| Changes    | s from V1.1 2009-01 to V1.2 2009-07                                                                          |

| 8 <b>9</b> | Note on LIN baud rate detection is added.                                                                    |

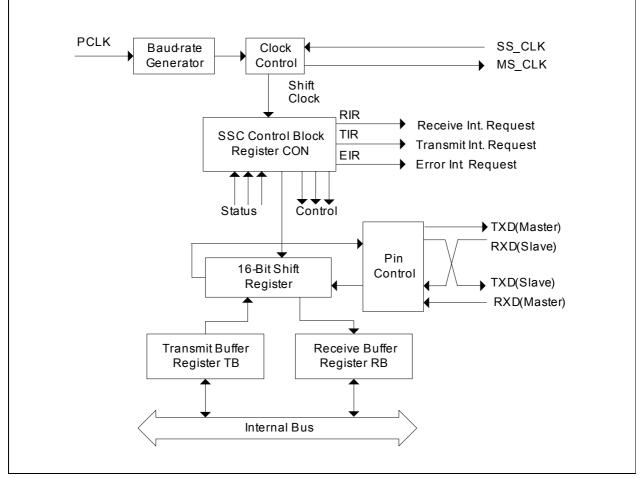

| 92         | RXD slave line in SSC block diagram is updated.                                                              |

| 108        | Electrical parameters are now valid for all variants, previous note on exclusion of ROM variants is removed. |

| 116        | Symbol for ADC error parameters are updated.                                                                 |

| 120        | Power supply current parameters for ROM variants are updated.                                                |

| 128        | Test condition for the on-chip oscillator short term deviation is updated.                                   |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

### **Summary of Features**

| Table 2Device Profile (cont'd) |

|--------------------------------|

|--------------------------------|

| Sales Type               | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|--------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Industrial         |

- Note: The asterisk (\*) above denotes the device configuration letters from **Table 1**. Corresponding ROM derivatives will be available on request.

- Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC886/888 throughout this document.

### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC886/888, please refer to your responsible sales representative or your local distributor.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

code or data. Therefore, even though the ROM device contains either a 24-Kbyte or 32-Kbyte ROM, the maximum size of code that can be placed in the ROM is the given size less four bytes.

### 3.2.1 Memory Protection Strategy

The XC886/888 memory protection strategy includes:

- Read-out protection: The user is able to protect the contents in the Flash (for Flash devices) and ROM (for ROM devices) memory from being read

- Flash protection is enabled by programming a valid password (8-bit non-zero value) via BSL mode 6.

- ROM protection is fixed with the ROM mask and is always enabled.

- Flash program and erase protection: This feature is available only for Flash devices.

### 3.2.1.1 Flash Memory Protection

As long as a valid password is available, all external access to the device, including the Flash, will be blocked.

For additional security, the Flash hardware protection can be enabled to implement a second layer of read-out protection, as well as to enable program and erase protection.

Flash hardware protection is available only for Flash devices and comes in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Flash Protection                      | Without hardware protection             | With hardware protection                     |                                                 |  |  |  |  |  |  |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|--|

| Hardware<br>Protection Mode           | -                                       | 0                                            | 1                                               |  |  |  |  |  |  |  |

| Activation                            | Program a valid passv                   | password via BSL mode 6                      |                                                 |  |  |  |  |  |  |  |

| Selection                             | Bit 4 of password = 0                   | Bit 4 of password = 1<br>MSB of password = 0 | Bit 4 of password = 1<br>MSB of password = 1    |  |  |  |  |  |  |  |

| P-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in the P-Flash             | Read instructions in the P-Flash or D-<br>Flash |  |  |  |  |  |  |  |

| External access<br>to P-Flash         | Not possible                            | Not possible                                 | Not possible                                    |  |  |  |  |  |  |  |

#### Table 4Flash Protection Modes

# 3.2.2 Special Function Register

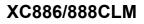

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_{H}$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

# 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Address Extension by Mapping

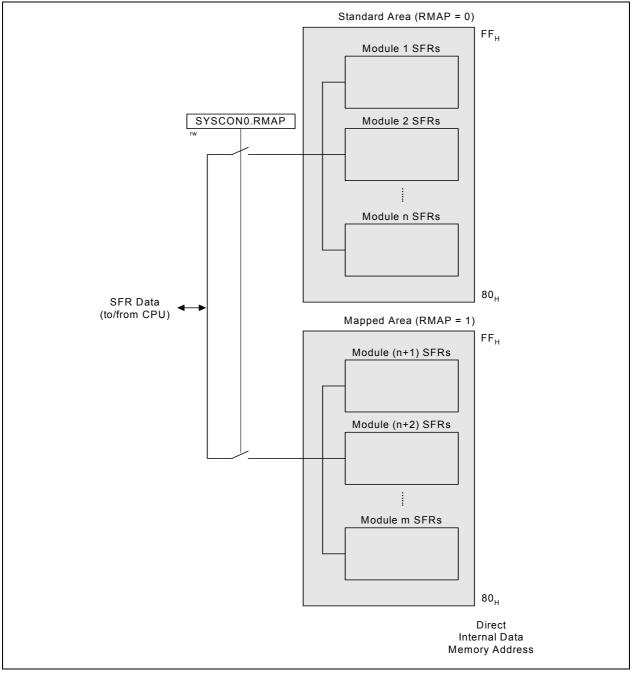

Overwrite the contents of PAGE with the contents of STx, ignoring the value written to the bit positions of PAGE

(this is done at the end of the interrupt routine to restore the previous page setting before the interrupt occurred)

### Figure 10 Storage Elements for Paging

With this mechanism, a certain number of interrupt routines (or other routines) can perform page changes without reading and storing the previously used page information. The use of only write operations makes the system simpler and faster. Consequently, this mechanism significantly improves the performance of short interrupt routines.

The XC886/888 supports local address extension for:

- Parallel Ports

- Analog-to-Digital Converter (ADC)

- Capture/Compare Unit 6 (CCU6)

- System Control Registers

The page register has the following definition:

### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

# 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                            | Bit       | 7         | 6    | 5    | 4           | 3         | 2    | 1       | 0          |  |  |

|-----------------|----------------------------------------------------------|-----------|-----------|------|------|-------------|-----------|------|---------|------------|--|--|

| RMAP =          | = 0 or 1                                                 | I.        |           |      |      |             |           |      |         |            |  |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                | Bit Field | Field SP  |      |      |             |           |      |         |            |  |  |

|                 | Stack Pointer Register                                   | Туре      |           |      |      | r           | W         |      |         |            |  |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                               | Bit Field | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1    | DPL0       |  |  |

|                 | Data Pointer Register Low                                | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw      | rw         |  |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                               | Bit Field | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1    | DPH0       |  |  |

|                 | Data Pointer Register High                               | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw      | rw         |  |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                              | Bit Field | SMOD      |      | 0    |             | GF1       | GF0  | 0       | IDLE       |  |  |

|                 | Power Control Register                                   | Туре      | rw        |      | r    |             | rw        | rw   | r       | rw         |  |  |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                              | Bit Field | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0     | IT0        |  |  |

|                 | Timer Control Register                                   | Туре      | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh     | rw         |  |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register       | Bit Field | GATE<br>1 | T1S  | T1   | 1M          | GATE<br>0 | TOS  | TOS TOM |            |  |  |

|                 |                                                          | Туре      | rw        | rw   | r    | w           | rw        | rw   | r       | w          |  |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                               | Bit Field |           | •    |      | V           | AL        | •    |         |            |  |  |

|                 | Timer 0 Register Low                                     | Туре      |           | rwh  |      |             |           |      |         |            |  |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                               | Bit Field | VAL       |      |      |             |           |      |         |            |  |  |

|                 | Timer 1 Register Low                                     | Туре      | rwh       |      |      |             |           |      |         |            |  |  |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |         |            |  |  |

|                 | Timer 0 Register High                                    | Туре      |           |      |      | rv          | vh        |      |         |            |  |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |         |            |  |  |

|                 | Timer 1 Register High                                    | Туре      |           |      |      | rv          | vh        |      |         |            |  |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                              | Bit Field | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI      | RI         |  |  |

|                 | Serial Channel Control Register                          | Туре      | rw        | rw   | rw   | rw          | rw        | rwh  | rwh     | rwh        |  |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                              | Bit Field | Field VAL |      |      |             |           |      |         |            |  |  |

|                 | Serial Data Buffer Register                              | Туре      |           |      |      | rv          | vh        |      |         |            |  |  |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub><br>Extended Operation Register | Bit Field |           | 0    |      | TRAP_<br>EN | 0         |      |         | DPSE<br>L0 |  |  |

|                 |                                                          | Туре      |           | r    |      | rw          | r         |      |         | rw         |  |  |

### Table 5 CPU Register Overview

| Addr            | Register Name                                                     | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0         |

|-----------------|-------------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|-----------|

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                       | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0       |

|                 | Interrupt Enable Register 0                                       | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                         | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0       |

|                 | Interrupt Priority Register                                       | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                        | Bit Field | (           | )           | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H      |

|                 | Interrupt Priority High Register                                  | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                        | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р         |

|                 | Program Status Word Register                                      | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh        |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub>                                        | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0      |

|                 | Accumulator Register                                              | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub><br>Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                          | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1        | B0        |

|                 | B Register                                                        | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F8 <sub>H</sub> | IP1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 Register       | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

#### Table 5CPU Register Overview (cont'd)

# 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 6MDU Register Overview

| Addr            | Register Name                                         | Bit            | 7    | 6  | 5    | 4         | 3   | 2      | 1    | 0   |

|-----------------|-------------------------------------------------------|----------------|------|----|------|-----------|-----|--------|------|-----|

| RMAP =          | = 1                                                   | •              |      | •  | •    | •         | •   | •      | •    |     |

| в0 <sub>Н</sub> | MDUSTAT Reset: 00 <sub>H</sub>                        | Bit Field      |      |    | 0    |           | BSY | IERR   | IRDY |     |

|                 | MDU Status Register                                   | Туре           |      |    | r    |           |     | rh     | rwh  | rwh |

| в1 <sub>Н</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field      | IE   | IR | RSEL | STAR<br>T |     | OPCODE |      |     |

|                 |                                                       | Туре           | rw   | rw | rw   | rwh       |     | r      | w    |     |

| B2 <sub>H</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field DATA |      |    |      |           |     |        |      |     |

|                 | MDU Operand Register 0                                | Туре           | rw   |    |      |           |     |        |      |     |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field      | DATA |    |      |           |     |        |      |     |

|                 | MDU Result Register 0                                 |                | rh   |    |      |           |     |        |      |     |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                            | Bit Field      | DATA |    |      |           |     |        |      |     |

| M               | MDU Operand Register 1                                | Туре           |      |    |      | r         | W   |        |      |     |

| Addr            | Register Name              | Bit       | 7    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5 | 4    | 3  | 2 | 1 | 0 |

|-----------------|----------------------------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----|---|---|---|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |      | DATA       nh       DATA       nW       DATA       nW       DATA       nh       DATA       nW       DATA       nh       DATA       nh       DATA       nh       DATA       nh       DATA       nW       DATA       nW       nh       nh |   |      |    |   |   |   |

|                 | MDU Result Register 1      | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | h  |   |   |   |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DA   | TA |   |   |   |

|                 | MDU Operand Register 2     | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | w  |   |   |   |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DATA |    |   |   |   |

|                 | MDU Result Register 2      | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | h  |   |   |   |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |      | DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |    |   |   |   |

|                 | MDU Operand Register 3     | Туре      |      | rw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |    |   |   |   |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DA   | TA |   |   |   |

|                 | MDU Result Register 3      | Туре      | rh   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |    |   |   |   |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DA   | TA |   |   |   |

|                 | MDU Operand Register 4     | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | w  |   |   |   |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DA   | TA |   |   |   |

|                 | MDU Result Register 4      | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | h  |   |   |   |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field | DATA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |    |   |   |   |

|                 | MDU Operand Register 5     | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |    |   |   |   |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | DA   | TA |   |   |   |

|                 | MDU Result Register 5      | Туре      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | r    | 'n |   |   |   |

### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |  |  |

|-----------------|----------------------------------|-----------|-------|---|---|----|-----|---|---|---|--|--|

| RMAP =          | = 1                              |           |       |   |   |    |     | 1 |   |   |  |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |

|                 | CORDIC X Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |  |

|                 | CORDIC X Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |

|                 | CORDIC Y Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |  |

|                 | CORDIC Y Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |  |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |  |  |

|                 | CORDIC Z Data Low Byte           | Туре      |       |   |   | r  | W   |   |   |   |  |  |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field | DATAH |   |   |    |     |   |   |   |  |  |

|                 | CORDIC Z Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |  |

### Table 8SCU Register Overview (cont'd)

| Addr            | Register Name                                                  | Bit       | 7           | 6           | 5                  | 4           | 3            | 2             | 1           | 0           |  |

|-----------------|----------------------------------------------------------------|-----------|-------------|-------------|--------------------|-------------|--------------|---------------|-------------|-------------|--|

| вс <sub>Н</sub> | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register            | Bit Field | 0           | FNMI<br>ECC | FNMI<br>VDDP       | FNMI<br>VDD | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL | FNMI<br>WDT |  |

|                 |                                                                | Туре      | r           | rwh         | rwh                | rwh         | rwh          | rwh           | rwh         | rwh         |  |

| вd <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>                                    | Bit Field | BG          | SEL         | 0                  | BRDIS       |              | BRPRE         |             | R           |  |

|                 | Baud Rate Control Register                                     |           | rw r rw     |             |                    |             | rw           |               |             | rw          |  |

| be <sub>h</sub> | BG Reset: 00 <sub>H</sub>                                      | Bit Field | BR_VALUE    |             |                    |             |              |               |             |             |  |

|                 | Baud Rate Timer/Reload<br>Register                             | Туре      | rwh         |             |                    |             |              |               |             |             |  |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub><br>Fractional Divider Control     | Bit Field | BGS         | SYNE<br>N   | ERRS<br>YN         | EOFS<br>YN  | BRK          | NDOV          | FDM         | FDEN        |  |

|                 | Register                                                       | Туре      | rw          | rw          | rwh                | rwh         | rwh          | rwh           | rw          | rw          |  |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                  | Bit Field | STEP        |             |                    |             |              |               |             |             |  |

|                 | Fractional Divider Reload<br>Register                          | Туре      | rw          |             |                    |             |              |               |             |             |  |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                   | Bit Field | RESULT      |             |                    |             |              |               |             |             |  |

|                 | Fractional Divider Result<br>Register                          | Туре      | rh          |             |                    |             |              |               |             |             |  |

| RMAP =          | : 0, PAGE 1                                                    |           |             |             |                    |             |              |               |             |             |  |

| вз <sub>Н</sub> | ID Reset: UU <sub>H</sub><br>Identity Register                 | Bit Field | PRODID      |             |                    |             |              | VERID         |             |             |  |

|                 |                                                                | Туре      |             | r           |                    |             |              | r             | r           |             |  |

| B4 <sub>H</sub> | PMCON0 Reset: 00 <sub>H</sub><br>Power Mode Control Register 0 | Bit Field | 0           | WDT<br>RST  | WKRS               | WK<br>SEL   | SD           | PD            | V           | /S          |  |

|                 |                                                                | Туре      | r           | rwh         | rwh                | rw          | rw           | rwh           | rw          |             |  |

| в5 <sub>Н</sub> | PMCON1 Reset: 00 <sub>H</sub><br>Power Mode Control Register 1 | Bit Field | 0           | CDC_<br>DIS | CAN_<br>DIS        | MDU_<br>DIS | T2_<br>DIS   | CCU_<br>DIS   | SSC_<br>DIS | ADC_<br>DIS |  |

|                 |                                                                | Туре      | r           | rw          | rw                 | rw          | rw           | rw            | rw          | rw          |  |

| в6 <sub>Н</sub> | OSC_CON Reset: 08 <sub>H</sub><br>OSC Control Register         | Bit Field | 0 OSC<br>PD |             |                    | XPD         | OSC<br>SS    | ORD<br>RES    | OSCR        |             |  |

|                 |                                                                | Туре      |             | r           |                    | rw          | rw           | rw            | rwh         | rh          |  |

| в7 <sub>Н</sub> | PLL_CON Reset: 90 <sub>H</sub><br>PLL Control Register         | Bit Field | NDIV        |             |                    | VCO<br>BYP  | OSC<br>DISC  | RESL<br>D     | LOCK        |             |  |

|                 |                                                                | Туре      |             | r           | w rw               |             | rw           | rw            | rwh         | rh          |  |

| βΑ <sub>Η</sub> | CMCON Reset: 10 <sub>H</sub><br>Clock Control Register         | Bit Field | VCO<br>SEL  | KDIV        | 0                  | FCCF<br>G   |              | CLKREL        |             |             |  |

|                 |                                                                | Туре      | rw          | rw          | r                  | rw          | rw           |               |             |             |  |

| вв <sub>Н</sub> | PASSWD Reset: 07 <sub>H</sub><br>Password Register             | Bit Field | eld PASS    |             | PROT MODE<br>ECT_S |             |              | DE            |             |             |  |

|                 |                                                                | Туре      | wh rh rw    |             |                    |             |              |               | w           |             |  |

| вс <sub>Н</sub> | FEAL Reset: 00 <sub>H</sub>                                    | Bit Field | ECCERRADDR  |             |                    |             |              |               |             |             |  |

|                 | Flash Error Address Register                                   | Туре      | rh          |             |                    |             |              |               |             |             |  |

| вd <sub>Н</sub> | FEAH Reset: 00 <sub>H</sub>                                    | Bit Field | ECCERRADDR  |             |                    |             |              |               |             |             |  |

|                 | Flash Error Address Register                                   | Туре      | rh          |             |                    |             |              |               |             |             |  |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                   | Bit       | 7                    | 6            | 5   | 4        | 3       | 2    | 1       | 0    |  |

|-----------------|-----------------------------------------------------------------|-----------|----------------------|--------------|-----|----------|---------|------|---------|------|--|

| CDH             | ADC_LCBR Reset: B7 <sub>H</sub>                                 | Bit Field | BOUND1               |              |     |          | BOUND0  |      |         |      |  |

|                 | Limit Check Boundary Register                                   | Туре      | rw rw                |              |     |          |         |      |         |      |  |

| CEH             | ADC_INPCR0 Reset: 00 <sub>H</sub>                               | Bit Field | STC                  |              |     |          |         |      |         |      |  |

|                 | Input Class 0 Register                                          | Туре      |                      |              |     | r        | w       |      |         |      |  |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub><br>External Trigger Control    | Bit Field | SYNE<br>N1           | SYNE ETRSEL1 |     |          | ETRSEL0 |      |         |      |  |

|                 | Register                                                        | Туре      | rw rw rw             |              |     |          | rw      |      |         |      |  |

| RMAP =          | 0, PAGE 1                                                       | •         |                      | •            |     |          |         |      |         |      |  |

| CAH             | ADC_CHCTR0 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | LCC          |     |          | 0       |      | RESRSEL |      |  |

|                 | Channel Control Register 0                                      | Туре      | r                    | rw           |     |          |         | r    | n       | N    |  |

| св <sub>Н</sub> | ADC_CHCTR1 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | LCC          |     |          | 0       |      | RESE    | RSEL |  |

|                 | Channel Control Register 1                                      | Туре      | r                    | rw           |     |          |         | r    | n       | N    |  |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | LCC          |     |          | (       | 0    |         | RSEL |  |

|                 | Channel Control Register 2                                      | Туре      | r                    |              | rw  |          |         | r    |         | rw   |  |

| CDH             | ADC_CHCTR3 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    |              | LCC |          | (       | C    | RESE    | RSEL |  |

|                 | Channel Control Register 3                                      | Туре      | r                    | rw           |     |          | r       |      | rw      |      |  |

| CEH             | ADC_CHCTR4 Reset: 00 <sub>H</sub><br>Channel Control Register 4 | Bit Field | 0                    | LCC          |     |          | 0       |      | RESRSEL |      |  |

| Ch              |                                                                 | Туре      | r                    | r rw         |     |          | r       |      | rw      |      |  |

| CFH             | ADC_CHCTR5 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | LCC          |     | 0        |         | RESE | RSEL    |      |  |

|                 | Channel Control Register 5                                      | Туре      | r                    | r rw         |     |          |         | r    |         | N    |  |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | 0 LCC        |     |          | (       | C    | RESE    | RSEL |  |

|                 | Channel Control Register 6                                      | Туре      | r                    | r rw         |     |          | r       |      | n       | N    |  |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00 <sub>H</sub>                               | Bit Field | 0                    | LCC          |     |          | (       | )    | RESE    | RSEL |  |

|                 | Channel Control Register 7                                      | Туре      | r                    | r rw         |     |          | r       |      | n       | N    |  |

| RMAP =          | 0, PAGE 2                                                       |           | •                    |              |     |          |         |      |         |      |  |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00 <sub>H</sub>                               | Bit Field | RES                  | SULT         | 0   | VF       | DRC     |      | CHNR    |      |  |

|                 | Result Register 0 Low                                           | Туре      | rh r rh              |              |     |          | rh rh   |      |         |      |  |

| св <sub>Н</sub> | ADC_RESR0H Reset: 00 <sub>H</sub><br>Result Register 0 High     | Bit Field | RESULT               |              |     |          |         |      |         |      |  |

|                 |                                                                 | Туре      | rh                   |              |     |          |         |      |         |      |  |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00 <sub>H</sub><br>Result Register 1 Low      | Bit Field | RES                  | SULT 0 VF DF |     | DRC      | CHNR    |      |         |      |  |

|                 |                                                                 | Туре      | rh r rh              |              | rh  | rh       |         |      |         |      |  |

| CDH             | ADC_RESR1H Reset: 00 <sub>H</sub><br>Result Register 1 High     | Bit Field | RESULT               |              |     |          |         |      |         |      |  |

|                 |                                                                 | Туре      | rh                   |              |     |          |         |      |         |      |  |

| Ceh             | ADC_RESR2L Reset: 00 <sub>H</sub><br>Result Register 2 Low      | Bit Field | RESULT 0 VF DRC CHNR |              |     |          |         |      |         |      |  |

|                 |                                                                 | Туре      | rh r rh rh rh        |              |     |          |         |      |         |      |  |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00 <sub>H</sub>                               | Bit Field | RESULT               |              |     |          |         |      |         |      |  |

|                 | Result Register 2 High                                          | Туре      | rh                   |              |     |          |         |      |         |      |  |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00 <sub>H</sub>                               | Bit Field | RESULT 0 VF          |              |     | DRC CHNR |         |      |         |      |  |

|                 | Result Register 3 Low                                           | Туре      | r                    | 'n           | r   | rh       | rh      |      | rh      |      |  |

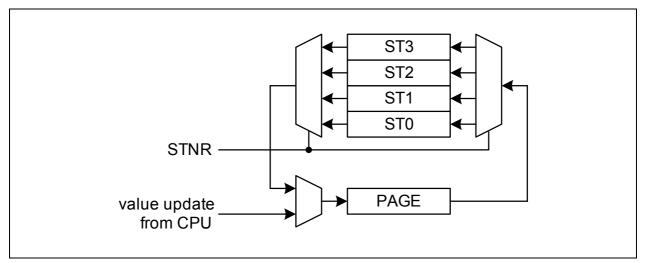

### 3.4 Interrupt System

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC886/888 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

### 3.4.1 Interrupt Source

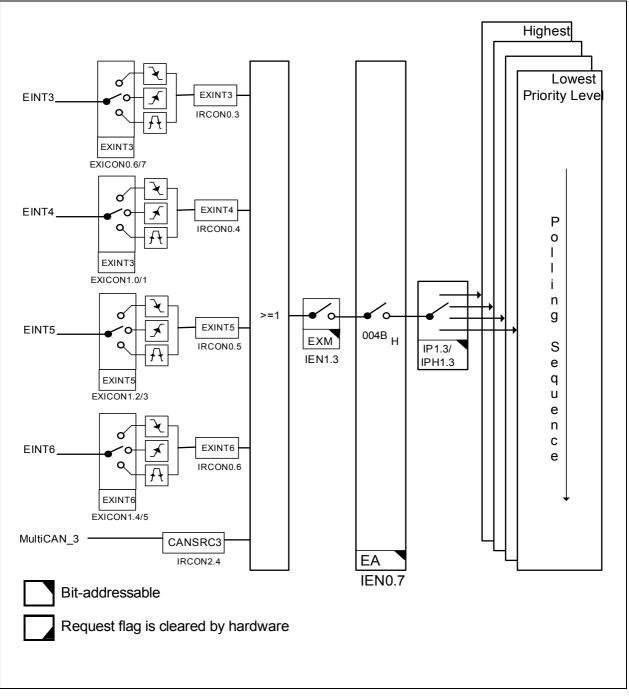

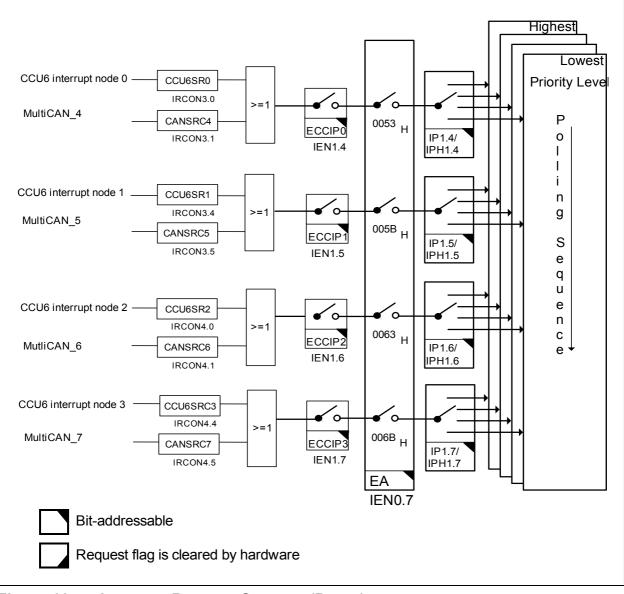

**Figure 13** to **Figure 17** give a general overview of the interrupt sources and nodes, and their corresponding control and status flags.

Figure 13 Non-Maskable Interrupt Request Sources

Figure 17 Interrupt Request Sources (Part 4)

Figure 18 Interrupt Request Sources (Part 5)

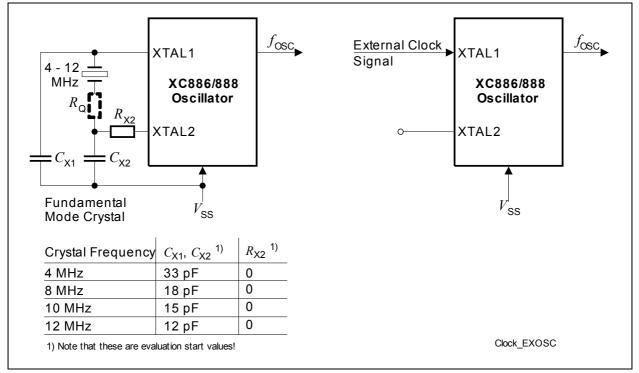

### Figure 25 External Oscillator Circuitry

Note: For crystal operation, it is strongly recommended to measure the negative resistance in the final target system (layout) to determine the optimum parameters for the oscillator operation. Please refer to the minimum and maximum values of the negative resistance specified by the crystal supplier.

### XC886/888CLM

**Functional Description**

Figure 32 SSC Block Diagram

# Table 36Chip Identification Number (cont'd)

| Product Variant  | Chip Identification Number |         |         |  |  |  |  |

|------------------|----------------------------|---------|---------|--|--|--|--|

|                  | AA-Step                    | AB-Step | AC-Step |  |  |  |  |

| XC886LM-6RFA 3V3 | 22411522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-6RFA 3V3 | 22411523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-8RFA 3V3 | 22480502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-8RFA 3V3 | 22480503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-8RFA 3V3  | 22480542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-8RFA 3V3  | 22480543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-8RFA 3V3   | 22480562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-8RFA 3V3   | 22480563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-6RFA 3V3 | 22491502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-6RFA 3V3 | 22491503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-6RFA 3V3  | 22491542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-6RFA 3V3  | 22491543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-6RFA 3V3   | 22491562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-6RFA 3V3   | 22491563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CLM-8RFA 5V | 22800502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CLM-8RFA 5V | 22800503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886LM-8RFA 5V  | 22800522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-8RFA 5V  | 22800523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CLM-6RFA 5V | 22811502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CLM-6RFA 5V | 22811503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886LM-6RFA 5V  | 22811522 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888LM-6RFA 5V  | 22811523 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-8RFA 5V  | 22880502 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888CM-8RFA 5V  | 22880503 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886C-8RFA 5V   | 22880542 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888C-8RFA 5V   | 22880543 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886-8RFA 5V    | 22880562 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC888-8RFA 5V    | 22880563 <sub>H</sub>      | -       | -       |  |  |  |  |

| XC886CM-6RFA 5V  | 22891502 <sub>H</sub>      | -       | -       |  |  |  |  |

#### **Electrical Parameters**

### 4.2.2 Supply Threshold Characteristics

Table 39 provides the characteristics of the supply threshold in the XC886/888.

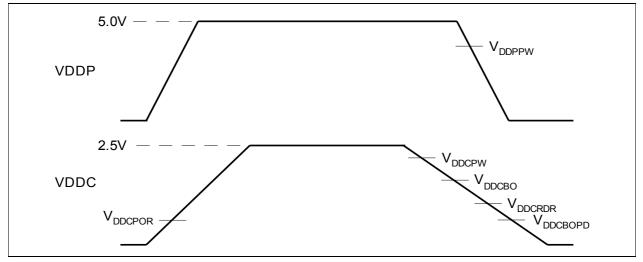

Figure 38 Supply Threshold Parameters

| Table 39 | Supply Threshold Parameters | (Operating Conditions apply) |

|----------|-----------------------------|------------------------------|

|----------|-----------------------------|------------------------------|

| Parameters                                                         | Symbol               |    | L    | Unit |      |   |

|--------------------------------------------------------------------|----------------------|----|------|------|------|---|

|                                                                    |                      |    | min. | typ. | max. |   |

| $V_{\rm DDC}$ prewarning voltage <sup>1)</sup>                     | V <sub>DDCPW</sub>   | CC | 2.2  | 2.3  | 2.4  | V |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | CC | 2.0  | 2.1  | 2.2  | V |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | CC | 0.9  | 1.0  | 1.1  | V |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | CC | 1.3  | 1.5  | 1.7  | V |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | CC | 3.4  | 4.0  | 4.6  | V |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | CC | 1.3  | 1.5  | 1.7  | V |

1) Detection is disabled in power-down mode.

2) Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

4) The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

#### **Electrical Parameters**

### 4.3.2 Output Rise/Fall Times

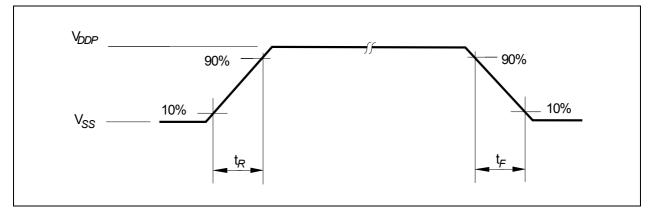

Table 45 provides the characteristics of the output rise/fall times in the XC886/888.

#### Table 45 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions          |

|-------------------------------|---------------------------------|-----------------|------|------|--------------------------|

|                               |                                 | min.            | max. |      |                          |