Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Core ProcessorXC800Core Size8-BitSpeed24MHzConnectivityCANbus, LINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case9C-TQFP-48          | Details                    |                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------|

| Core Size8-BitSpeed24MHzConnectivityCANbus, LINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupple Towice PackagePG-TQFP-48 | Product Status             | Last Time Buy                                                                     |

| Speed24MHzConnectivityCANbus, LINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting Type84-LQFPSupplier Device PackagePG-TQFP-48                                        | Core Processor             | XC800                                                                             |

| ConnectivityCANbus, LINbus, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                       | Core Size                  | 8-Bit                                                                             |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting Type8urface MountPackage / Case48-LQFPSupplier Device PackagePG-TQF-48                                                                   | Speed                      | 24MHz                                                                             |

| Number of I/O34Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting Type84-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                             | Connectivity               | CANbus, LINbus, SSI, UART/USART                                                   |

| Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                 | Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Program Memory TypeFLASHEEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                  | Number of I/O              | 34                                                                                |

| EEPROM Size-RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                          | Program Memory Size        | 32KB (32K x 8)                                                                    |

| RAM Size1.75K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                                      | Program Memory Type        | FLASH                                                                             |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                                                       | EEPROM Size                | -                                                                                 |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                                                                                            | RAM Size                   | 1.75K x 8                                                                         |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                                                                                                                    | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case48-LQFPSupplier Device PackagePG-TQFP-48                                                                                                                                                                                                                                                                                                           | Data Converters            | A/D 8x10b                                                                         |

| Mounting Type     Surface Mount       Package / Case     48-LQFP       Supplier Device Package     PG-TQFP-48                                                                                                                                                                                                                                                                                                                     | Oscillator Type            | Internal                                                                          |

| Package / Case 48-LQFP<br>Supplier Device Package PG-TQFP-48                                                                                                                                                                                                                                                                                                                                                                      | Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Supplier Device Package PG-TQFP-48                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Surface Mount                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 48-LQFP                                                                           |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc886clm8ffa5vackxuma1                                                                                                                                                                                                                                                                                                                                    | Supplier Device Package    | PG-TQFP-48                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                   | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886clm8ffa5vackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2009-07 Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **General Device Information**

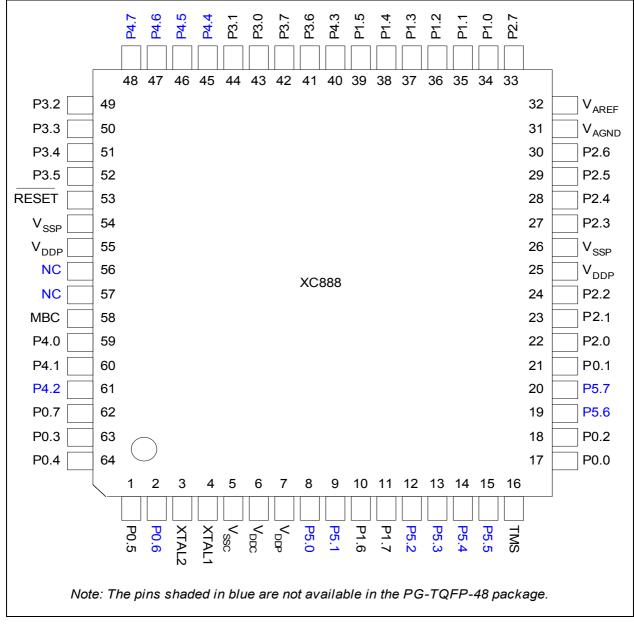

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

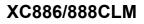

#### 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_{H}$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

### 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Address Extension by Mapping

SYSCON0

#### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                    |

|-------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is enabled</li> <li>The access to the mapped SFR area is enabled</li> </ul> |

| 1     | 2             | r    | <b>Reserved</b><br>Returns 1 if read; should be written with 1.                                                                                                |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

### 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 9**.

| Addr            | Register Name              | Bit       | 7                                                                                                                                                                                                                                       | 6 | 5 | 4  | 3                  | 2 | 1 | 0 |  |  |  |

|-----------------|----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|--------------------|---|---|---|--|--|--|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Result Register 1      | Туре      |                                                                                                                                                                                                                                         |   |   | r  | h                  |   |   |   |  |  |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Operand Register 2     | Туре      |                                                                                                                                                                                                                                         |   |   | r  | w                  |   |   |   |  |  |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field | DATA  h  DATA  h  DATA  DATA  DATA  rw  DATA  A  DATA  h  DATA  h  DATA  rw  DATA  h  h  DATA  h  h  h  h  h  h  h  h  h  h  h  h  h |   |   |    |                    |   |   |   |  |  |  |

|                 | MDU Result Register 2      | Туре      |                                                                                                                                                                                                                                         |   |   | r  | h                  |   |   |   |  |  |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Operand Register 3     | Туре      |                                                                                                                                                                                                                                         |   |   | r  | w                  |   |   |   |  |  |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Result Register 3      | Туре      |                                                                                                                                                                                                                                         |   |   | r  | h                  |   |   |   |  |  |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Operand Register 4     | Туре      |                                                                                                                                                                                                                                         |   |   | r  | w                  |   |   |   |  |  |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Result Register 4      | Туре      |                                                                                                                                                                                                                                         |   |   | r  | h                  |   |   |   |  |  |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Operand Register 5     | Туре      |                                                                                                                                                                                                                                         |   |   | r  | DATA<br>rw<br>DATA |   |   |   |  |  |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |                                                                                                                                                                                                                                         |   |   | DA | TA                 |   |   |   |  |  |  |

|                 | MDU Result Register 5      | Туре      | rh                                                                                                                                                                                                                                      |   |   |    |                    |   |   |   |  |  |  |

#### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7     | 6     | 5 | 4  | 3   | 2 | 1 | 0 |  |  |  |

|-----------------|----------------------------------|-----------|-------|-------|---|----|-----|---|---|---|--|--|--|

| RMAP =          | = 1                              |           | J     |       |   |    |     | 1 |   |   |  |  |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |       |       |   | DA | TAL |   |   |   |  |  |  |

|                 | CORDIC X Data Low Byte           | Туре      |       |       |   | r  | W   |   |   |   |  |  |  |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       | DATAH |   |    |     |   |   |   |  |  |  |

|                 | CORDIC X Data High Byte          | Туре      | rw    |       |   |    |     |   |   |   |  |  |  |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | DATAL |       |   |    |     |   |   |   |  |  |  |

|                 | CORDIC Y Data Low Byte           | Туре      |       |       |   | r  | W   |   |   |   |  |  |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |       |       |   | DA | TAH |   |   |   |  |  |  |

|                 | CORDIC Y Data High Byte          | Туре      |       |       |   | r  | W   |   |   |   |  |  |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |       |       |   | DA | TAL |   |   |   |  |  |  |

|                 | CORDIC Z Data Low Byte           | Туре      | rw    |       |   |    |     |   |   |   |  |  |  |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field | DATAH |       |   |    |     |   |   |   |  |  |  |

|                 | CORDIC Z Data High Byte          | Туре      | rw    |       |   |    |     |   |   |   |  |  |  |

| Addr            | Register Name                                                        | Bit       | 7            | 6 | 5           | 4           | 3          | 2           | 1             | 0             |

|-----------------|----------------------------------------------------------------------|-----------|--------------|---|-------------|-------------|------------|-------------|---------------|---------------|

| ве <sub>Н</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field | (            | ) | TLEN        | COUT<br>S   |            | CO          | REL           | <u> </u>      |

|                 |                                                                      | Туре      |              | r | rw          | rw          |            | r           | w             |               |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register    | Bit Field |              |   |             | 0           |            |             |               | DFLAS<br>HEN  |

|                 |                                                                      | Туре      |              |   |             | r           |            |             |               | rwh           |

| RMAP =          | = 0, PAGE 3                                                          |           |              |   |             |             |            |             |               |               |

| вз <sub>Н</sub> | XADDRH Reset: F0 <sub>H</sub>                                        | Bit Field |              |   |             | ADI         | ORH        |             |               |               |

|                 | On-chip XRAM Address Higher<br>Order                                 | Туре      |              |   |             | r           | w          |             |               |               |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub><br>Interrupt Request Register 3        | Bit Field | (            | ) | CANS<br>RC5 | CCU6<br>SR1 | (          | )           | CCU6<br>SR0   |               |

|                 |                                                                      | Туре      | 1            | r | rwh         | rwh         | I          | · rwh       |               | rwh           |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub><br>Interrupt Request Register 4        | Bit Field | (            | ) | CANS<br>RC7 | CCU6<br>SR3 | (          | )           | CANS<br>RC6   | CCU6<br>SR2   |

|                 |                                                                      | Туре      | I            | r | rwh         | rwh         | l          | r           | rwh           | rwh           |

| в7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS | ( | )           | UR′         | IRIS       | T21EX<br>IS | JTAGT<br>DIS1 | JTAGT<br>CKS1 |

|                 | 1                                                                    | Туре      | rw           |   | r           | r           | w          | rw          | rw            | rw            |

| ва <sub>Н</sub> | MODPISEL2 Reset: 00 <sub>H</sub>                                     | Bit Field |              | ( | )           |             | T21IS      | T2IS        | T1IS          | TOIS          |

|                 | Peripheral Input Select Register 2                                   | Туре      |              |   | r           |             | rw         | rw          | rw            | rw            |

| вв <sub>Н</sub> | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field |              |   | (           | 0           |            |             | UART<br>1_DIS | T21_D<br>IS   |

|                 |                                                                      | Туре      |              |   | I           | r           |            |             | rw            | rw            |

| вd <sub>Н</sub> | MODSUSP Reset: 01 <sub>H</sub><br>Module Suspend Control             | Bit Field |              | 0 |             | T21SU<br>SP | T2SUS<br>P | T13SU<br>SP | T12SU<br>SP   | WDTS<br>USP   |

|                 | Register                                                             | Туре      |              | r |             | rw          | rw         | rw          | rw            | rw            |

#### Table 8SCU Register Overview (cont'd)

# 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 9WDT Register Overview

| Addr            | Register Name                                           | Bit       | 7 6 5 4 3 2 1 |   |            |           |   |           | 1         | 0         |

|-----------------|---------------------------------------------------------|-----------|---------------|---|------------|-----------|---|-----------|-----------|-----------|

| RMAP =          | : 1                                                     |           |               |   |            |           |   |           |           |           |

| вв <sub>Н</sub> | WDTCON Reset: 00 <sub>H</sub><br>Watchdog Timer Control | Bit Field | (             | ) | WINB<br>EN | WDTP<br>R | 0 | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|                 | Register                                                | Туре      | 1             |   | rw         | rh        | r | rw        | rwh       | rw        |

| вс <sub>Н</sub> | WDTREL Reset: 00 <sub>H</sub>                           | Bit Field |               |   |            |           |   |           |           |           |

|                 | Watchdog Timer Reload<br>Register                       | Туре      | rw            |   |            |           |   |           |           |           |

| вd <sub>Н</sub> | WDTWINB Reset: 00 <sub>H</sub>                          | Bit Field | ld WDTWINB    |   |            |           |   |           |           |           |

|                 | Watchdog Window-Boundary<br>Count Register              | Туре      |               |   |            | r         | w |           |           |           |

### Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                | Bit       | 7              | 6          | 5    | 4         | 3    | 2           | 1       | 0           |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|-----------------|--------------------------------------------------------------|-----------|----------------|------------|------|-----------|------|-------------|---------|-------------|--|-------------|--|------------|--|-----------|--|------|--|------|--|------|--|------|--|------|--|------|--|----------|--|----------|--|---------|--|--|------|--|

| CDH             | ADC_LCBR Reset: B7 <sub>H</sub>                              | Bit Field |                | BOU        | IND1 |           |      | BOL         | JND0    |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Limit Check Boundary Register                                | Туре      |                | r          | N    |           |      | r           | w       |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CEH             | ADC_INPCR0 Reset: 00 <sub>H</sub>                            | Bit Field |                |            |      | S         | тс   |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Input Class 0 Register                                       | Туре      |                |            |      | r         | w    |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub><br>External Trigger Control | Bit Field | SYNE<br>N1     | SYNE<br>N0 |      | ETRSEL    | 1    |             | ETRSELO |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Register                                                     | Туре      | rw             | rw         |      | rw        |      |             | rw      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| RMAP =          | 0, PAGE 1                                                    |           |                |            | •    |           |      |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CAH             | ADC_CHCTR0 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | )           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 0                                   | Туре      | r              |            | rw   |           |      | r           | n       | N           |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| св <sub>Н</sub> | ADC_CHCTR1 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | C           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 1                                   | Туре      | r              |            | rw   |           |      | r           | n       | N           |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | )           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 2                                   | Туре      | r              |            | rw   |           |      | r           | rw      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CDH             | ADC_CHCTR3 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | C           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 3                                   | Туре      | r              |            | rw   |           |      | r           | RES     |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CEH             | ADC_CHCTR4 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | )           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 4                                   | Туре      | r              |            | rw   |           |      | r           | rw      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CFH             | ADC_CHCTR5 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | )           | RESRSEL |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 5                                   | Туре      | r              |            | rw   |           |      | r           | rw      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | C           | RESRSEL |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 6                                   | Туре      | r              |            | rw   |           |      | r           | n       | N           |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00 <sub>H</sub>                            | Bit Field | 0              |            | LCC  |           | (    | )           | RESE    | RSEL        |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Channel Control Register 7                                   | Туре      | r              |            | rw   |           |      | r           | n       | N           |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| RMAP =          | 0, PAGE 2                                                    |           | •              |            |      |           |      |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00 <sub>H</sub>                            | Bit Field | RES            | SULT       | 0    | VF        | DRC  |             | CHNR    |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 0 Low                                        | Туре      | r              | h          | r    | rh        | rh   |             | rh      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| св <sub>Н</sub> | ADC_RESR0H Reset: 00 <sub>H</sub>                            | Bit Field |                |            |      | RES       | SULT |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 0 High                                       | Туре      |                |            |      | I         | ħ    |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00 <sub>H</sub>                            | Bit Field | RES            | SULT       | 0    | VF        | DRC  |             | CHNR    |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 1 Low                                        | Туре      | r              | 'n         | r    | rh        | rh   |             | rh      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CDH             | ADC_RESR1H Reset: 00 <sub>H</sub>                            | Bit Field |                |            |      | RES       | SULT |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 1 High                                       | Туре      |                |            |      | I         | 'n   |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CEH             | ADC_RESR2L Reset: 00 <sub>H</sub>                            | Bit Field | RES            | SULT       | 0    | VF        | DRC  |             | CHNR    |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 2 Low                                        | Туре      | r              | h          | r    | rh        | rh   |             | rh      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| CF <sub>H</sub> |                                                              |           | Bit Field RESU |            |      | SULT      |      |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

|                 | Result Register 2 High                                       | Туре      |                |            |      |           | ħ    |             |         |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00 <sub>H</sub>                            | Bit Field | RES            | SULT 0 VF  |      | SULT 0 VF |      | RESULT 0 VF |         | RESULT 0 VF |  | RESULT 0 VF |  | ESULT 0 VF |  | SULT 0 VF |  | JLT 0 VF |  | JLT 0 VF |  | LT 0 VF |  |  | CHNR |  |

|                 | Result Register 3 Low                                        | Туре      | r              | 'n         | r    | rh        | rh   |             | rh      |             |  |             |  |            |  |           |  |      |  |      |  |      |  |      |  |      |  |      |  |          |  |          |  |         |  |  |      |  |

#### Table 13T21 Register Overview (cont'd)

| Addr            | Register Name         | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|-----------------------|-----------|-------|---|---|----|-----|---|---|---|

| C5 <sub>H</sub> | - 1                   | Bit Field |       |   |   | TH | IL2 |   |   |   |

|                 | Timer 2 Register High | Туре      | e rwh |   |   |    |     |   |   |   |

### 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 14 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2                       | 1          | 0          |  |  |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|-------------------------|------------|------------|--|--|

| RMAP =          | = 0                                                                          |           |            |            |            |            |            |                         |            |            |  |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          |                         | PAGE       |            |  |  |

|                 | Page Register                                                                | Туре      | ١          | N          | ۱          | N          | r          |                         | rw         |            |  |  |

| RMAP =          | = 0, PAGE 0                                                                  |           |            |            |            |            |            |                         |            |            |  |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub><br>Capture/Compare Shadow Register       | Bit Field |            |            |            | CC6        | 63SL       |                         |            |            |  |  |

|                 | for Channel CC63 Low                                                         | Туре      |            |            |            | rw         |            |                         |            |            |  |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 3SH        | 3SH                     |            |            |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC63 High                     | Туре      |            |            |            | r          | w          |                         |            |            |  |  |

| 9CH             | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (          | 0          | DT<br>RES  | T12<br>RES              |            |            |  |  |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w                       | w          | w          |  |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13 T13R T13<br>RES S R |            |            |  |  |

|                 |                                                                              | Туре      | w          | w          |            | r          |            | w w w                   |            |            |  |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |            |            | MC         | MPS                     |            |            |  |  |

|                 | Register Low                                                                 | Туре      | w          | r          |            |            | r          | w                       |            |            |  |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |            | CURHS      |            |                         | EXPHS      |            |  |  |

|                 | Register High                                                                | Туре      | w          | r          |            | rw         |            |                         | rw         |            |  |  |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F | RCC6<br>2R | RCC6<br>1F | RCC6<br>1R              | RCC6<br>0F | RCC6<br>0R |  |  |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w                       | w          | w          |  |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E   | RCHE       | 0          | RTRP<br>F               | RT13<br>PM | RT13<br>CM |  |  |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w                       | w          | w          |  |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |            |            |            |                         |            | MCC6<br>0S |  |  |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |            | w                       | w          | w          |  |  |

| а7 <sub>Н</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3R |            | 0          |            | MCC6 MCC6 MC<br>2R 1R C |            |            |  |  |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w                       | w          | w          |  |  |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

### 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 15 UART1 Register Overview

| Addr            | Register Name                          | Bit       | 7   | 6   | 5   | 4    | 3     | 2       | 1   | 0    |  |  |   |

|-----------------|----------------------------------------|-----------|-----|-----|-----|------|-------|---------|-----|------|--|--|---|

| RMAP =          | = 1                                    | 1         |     |     |     |      |       |         |     | 1    |  |  |   |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>            | Bit Field | SM0 | SM1 | SM2 | REN  | TB8   | RB8     | TI  | RI   |  |  |   |

|                 | Serial Channel Control Register        | Туре      | rw  | rw  | rw  | rw   | rw    | rwh     | rwh | rwh  |  |  |   |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>            | Bit Field |     |     |     | V    | AL    |         |     |      |  |  |   |

|                 | Serial Data Buffer Register            | Туре      |     |     |     | rv   | vh    |         |     |      |  |  |   |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>            | Bit Field | 0   |     |     |      |       | 0 BRPRE |     |      |  |  | R |

|                 | Baud Rate Control Register             | Туре      |     |     | r   |      |       | rw rv   |     |      |  |  |   |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>              | Bit Field |     |     |     | BR_V | 'ALUE |         |     |      |  |  |   |

|                 | Baud Rate Timer/Reload<br>Register     | Туре      |     |     |     | rv   | vh    |         |     |      |  |  |   |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>           | Bit Field |     |     | 0   |      |       | NDOV    | FDM | FDEN |  |  |   |

|                 | Fractional Divider Control<br>Register | Туре      |     |     | r   |      |       | rwh     | rw  | rw   |  |  |   |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>          | Bit Field |     |     |     | ST   | ΈP    |         |     |      |  |  |   |

|                 | Fractional Divider Reload<br>Register  | Туре      |     |     |     | r    | rw    |         |     |      |  |  |   |

| Ceh             | FDRES Reset: 00 <sub>H</sub>           | Bit Field |     |     |     | RES  | SULT  |         |     |      |  |  |   |

|                 | Fractional Divider Result<br>Register  | Туре      |     |     |     | r    | h     |         |     |      |  |  |   |

#### Table 17CAN Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7 6 5 4 3 2 1 0 |  |  |    |    |  |  |  |  |

|-----------------|------------------------------|-----------|-----------------|--|--|----|----|--|--|--|--|

| db <sub>H</sub> | DATA0 Reset: 00 <sub>H</sub> | Bit Field |                 |  |  | С  | D  |  |  |  |  |

|                 | CAN Data Register 0          | Туре      |                 |  |  | rv | vh |  |  |  |  |

| DC <sub>H</sub> | DATA1 Reset: 00 <sub>H</sub> | Bit Field | CD              |  |  |    |    |  |  |  |  |

|                 | CAN Data Register 1          | Туре      | Type rwh        |  |  |    |    |  |  |  |  |

| dd <sub>H</sub> | DATA2 Reset: 00 <sub>H</sub> | Bit Field |                 |  |  | С  | D  |  |  |  |  |

|                 | CAN Data Register 2          | Туре      |                 |  |  | rv | vh |  |  |  |  |

| de <sub>h</sub> | DATA3 Reset: 00 <sub>H</sub> | Bit Field | d CD            |  |  |    |    |  |  |  |  |

|                 | CAN Data Register 3          | Туре      | rwh             |  |  |    |    |  |  |  |  |

#### 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 18 OCDS Register Overview

| Addr                                                                          | Register Name                                                              | Bit        | 7             | 6         | 5          | 4          | 3           | 2         | 1          | 0         |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------|---------------|-----------|------------|------------|-------------|-----------|------------|-----------|

| RMAP = 1                                                                      |                                                                            |            |               |           |            |            |             |           |            |           |

| E9 <sub>H</sub>                                                               | MMCR2 Reset: 1U <sub>H</sub><br>Monitor Mode Control 2<br>Register         | Bit Field  | STMO<br>DE    | EXBC      | DSUS<br>P  | MBCO<br>N  | ALTDI       | MMEP      | MMOD<br>E  | JENA      |

|                                                                               |                                                                            | Туре       | rw            | rw        | rw         | rwh        | rw          | rwh       | rh         | rh        |

| F1 <sub>H</sub> MMCR<br>Monitor Mode 0                                        | MMCR Reset: 00 <sub>H</sub><br>Monitor Mode Control Register               | Bit Field  | MEXIT<br>_P   | MEXIT     | 0          | MSTE<br>P  | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |

|                                                                               |                                                                            | Туре       | w             | rwh       | r          | rw         | w           | rwh       | rh         | rh        |

|                                                                               | MMSR Reset: 00 <sub>H</sub><br>Monitor Mode Status Register                | Bit Field  | MBCA<br>M     | MBCIN     | EXBF       | SWBF       | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |

|                                                                               |                                                                            | Туре       | rw            | rwh       | rwh        | rwh        | rwh         | rwh       | rwh        | rwh       |

| F3 <sub>H</sub> MMBPCR Reset: 00 <sub>H</sub><br>Breakpoints Control Register | Bit Field                                                                  | SWBC HWB3C |               | HWB2C     |            | HWB1<br>C  | HWB0C       |           |            |           |

|                                                                               |                                                                            | Туре       | rw rw rw rw   |           | rw         | rw         |             |           |            |           |

| М                                                                             | MMICR Reset: 00 <sub>H</sub><br>Monitor Mode Interrupt Control<br>Register | Bit Field  | DVEC<br>T     | DRET<br>R | COMR<br>ST | MSTS<br>EL | MMUI<br>E_P | MMUI<br>E | RRIE_<br>P | RRIE      |

|                                                                               |                                                                            | Туре       | rwh           | rwh       | rwh        | rh         | w           | rw        | w          | rw        |

| F5 <sub>H</sub>                                                               | MMDR Reset: 00 <sub>H</sub>                                                | Bit Field  | MMRR          |           |            |            |             |           |            |           |

|                                                                               | Monitor Mode Data Transfer<br>Register<br>Receive                          | Туре       | rh            |           |            |            |             |           |            |           |

| F6 <sub>H</sub>                                                               | HWBPSR Reset: 00 <sub>H</sub><br>Hardware Breakpoints Select               | Bit Field  | 0 BPSEL BPSEL |           |            |            |             |           |            |           |

|                                                                               | Register                                                                   | Туре       | r w rw        |           |            |            |             |           |            |           |

| F7 <sub>H</sub>                                                               | HWBPDR Reset: 00 <sub>H</sub>                                              | Bit Field  | HWBPxx        |           |            |            |             |           |            |           |

|                                                                               | Hardware Breakpoints Data<br>Register                                      | Туре       | rw            |           |            |            |             |           |            |           |

| EB <sub>H</sub>                                                               | MMWR1 Reset: 00 <sub>H</sub>                                               | Bit Field  | MMWR1         |           |            |            |             |           |            |           |

|                                                                               | Monitor Work Register 1                                                    | Туре       | rw            |           |            |            |             |           |            |           |

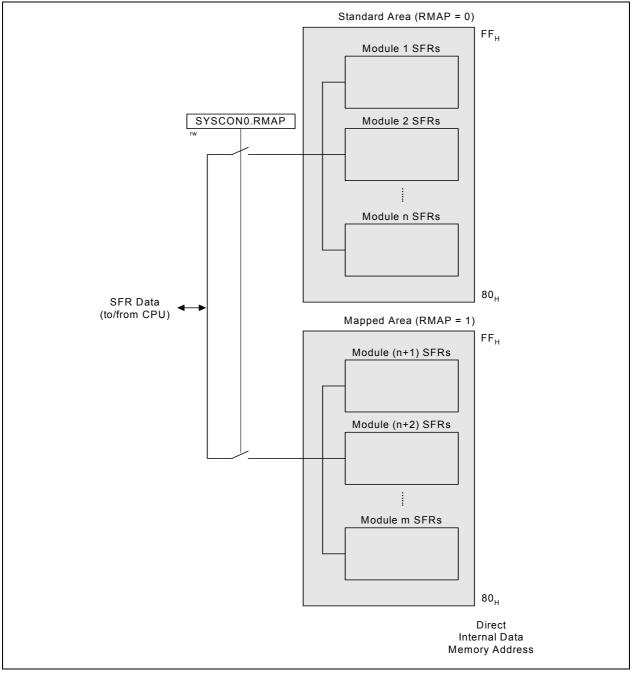

#### 3.4 Interrupt System

The XC800 Core supports one non-maskable interrupt (NMI) and 14 maskable interrupt requests. In addition to the standard interrupt functions supported by the core, e.g., configurable interrupt priority and interrupt masking, the XC886/888 interrupt system provides extended interrupt support capabilities such as the mapping of each interrupt vector to several interrupt sources to increase the number of interrupt sources supported, and additional status registers for detecting and determining the interrupt source.

#### 3.4.1 Interrupt Source

**Figure 13** to **Figure 17** give a general overview of the interrupt sources and nodes, and their corresponding control and status flags.

Figure 13 Non-Maskable Interrupt Request Sources

### **Functional Description**

| Interrupt Vector<br>Source Address |                   | Assignment for<br>XC886/888                           | Enable Bit | SFR  |  |

|------------------------------------|-------------------|-------------------------------------------------------|------------|------|--|

| XINTR6                             | 0033 <sub>H</sub> | MultiCAN Nodes 1 and 2                                | EADC       | IEN1 |  |

|                                    |                   | ADC[1:0]                                              | _          |      |  |

| XINTR7                             | 003B <sub>H</sub> | SSC                                                   | ESSC       |      |  |

| XINTR8                             | 0043 <sub>H</sub> | External Interrupt 2                                  | EX2        |      |  |

|                                    |                   | T21                                                   | _          |      |  |

|                                    |                   | CORDIC                                                | _          |      |  |

|                                    |                   | UART1                                                 |            |      |  |

|                                    |                   | UART1 Fractional Divider<br>(Normal Divider Overflow) |            |      |  |

|                                    |                   | MDU[1:0]                                              | _          |      |  |

| XINTR9                             | 004B <sub>H</sub> | External Interrupt 3                                  | EXM        |      |  |

|                                    |                   | External Interrupt 4                                  | _          |      |  |

|                                    |                   | External Interrupt 5                                  | _          |      |  |

|                                    |                   | External Interrupt 6                                  | _          |      |  |

|                                    |                   | MultiCAN Node 3                                       |            |      |  |

| XINTR10                            | 0053 <sub>H</sub> | CCU6 INP0                                             | ECCIP0     |      |  |

|                                    |                   | MultiCAN Node 4                                       |            |      |  |

| XINTR11                            | 005B <sub>H</sub> | CCU6 INP1                                             | ECCIP1     |      |  |

|                                    |                   | MultiCAN Node 5                                       |            |      |  |

| XINTR12                            | 0063 <sub>H</sub> | CCU6 INP2                                             | ECCIP2     |      |  |

|                                    |                   | MultiCAN Node 6                                       |            |      |  |

| XINTR13                            | 006B <sub>H</sub> | CCU6 INP3                                             | ECCIP3     |      |  |

|                                    |                   | MultiCAN Node 7                                       |            |      |  |

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

# Table 26System frequency ( $f_{sys}$ = 96 MHz)

| Power Saving Mode | Action                                                                                                                   |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Idle              | Clock to the CPU is disabled.                                                                                            |  |  |  |  |  |  |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |  |  |  |  |  |  |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |  |  |  |  |  |  |

# 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC886/888 Core in real-time control applications, which require fast mathematical computations.

#### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 28 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |

|--------------------------|--------|-----------|---------------------------------------------|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |

Table 28

MDU Operation Characteristics

#### XC886/888CLM

#### **Functional Description**

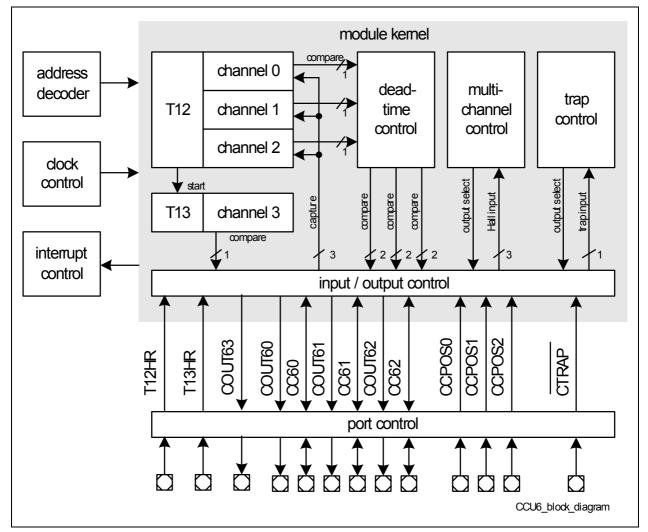

Figure 33 CCU6 Block Diagram

However, it is important to note that the conversion error could increase due to loss of charges on the capacitors, if  $f_{ADC}$  becomes too low during slow-down mode.

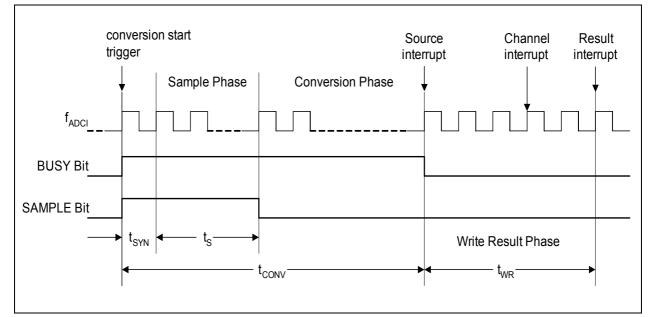

# 3.21.2 ADC Conversion Sequence

The analog-to-digital conversion procedure consists of the following phases:

- Synchronization phase (*t*<sub>SYN</sub>)

- Sample phase  $(t_S)$

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 36 ADC Conversion Timing

#### **Electrical Parameters**

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                                |                   |    | min. max.                   |                             |      |                           |  |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |  |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |  |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                                |                   |    | -                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |  |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | _                           | V    | CMOS Mode <sup>1)</sup>   |  |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |  |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |  |

#### **Electrical Parameters**

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$

#### **Electrical Parameters**

# Table 43Power Supply Current Parameters (Operating Conditions apply;<br/> $V_{\text{DDP}}$ = 3.3V range)

| Parameter                     | Symbol           | Limit Values       |                    | Unit | <b>Test Condition</b>      |  |

|-------------------------------|------------------|--------------------|--------------------|------|----------------------------|--|

|                               |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> |      |                            |  |

| V <sub>DDP</sub> = 3.3V Range |                  |                    |                    |      |                            |  |

| Active Mode                   | I <sub>DDP</sub> | 25.6               | 31.0               | mA   | Flash Device <sup>3)</sup> |  |

|                               |                  | 23.4               | 28.6               | mA   | ROM Device <sup>3)</sup>   |  |

| Idle Mode                     | I <sub>DDP</sub> | 19.9               | 24.7               | mA   | Flash Device <sup>4)</sup> |  |

|                               |                  | 17.5               | 20.7               | mA   | ROM Device <sup>4)</sup>   |  |

| Active Mode with slow-down    | I <sub>DDP</sub> | 13.3               | 16.2               | mA   | Flash Device <sup>5)</sup> |  |

| enabled                       |                  | 11.5               | 13.7               | mA   | ROM Device <sup>5)</sup>   |  |

| Idle Mode with slow-down      | I <sub>DDP</sub> | 11.1               | 14.4               | mA   | Flash Device <sup>6)</sup> |  |

| enabled                       |                  | 9.3                | 11.4               | mA   | ROM Device <sup>6)</sup>   |  |

1) The typical  $I_{\text{DDP}}$  values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

2) The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 125 °C and  $V_{\text{DDP}}$  = 3.6 V).