Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 24MHz                                                                             |

| Connectivity               | CANbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 34                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1.75К х 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 140°C (TA)                                                                |

| Mounting Type              | · ·                                                                               |

| Package / Case             | -                                                                                 |

| Supplier Device Package    | -                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886cm8ffa3v3ackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 4.3.3 | Power-on Reset and PLL Timing 126      |

|-------|----------------------------------------|

| 4.3.4 | On-Chip Oscillator Characteristics 128 |

| 4.3.5 | External Clock Drive XTAL1 129         |

| 4.3.6 | JTAG Timing                            |

| 4.3.7 | SSC Master Mode Timing 132             |

| 5     | Package and Quality Declaration        |

| 5.1   | Package Parameters                     |

| 5.2   | Package Outline                        |

| 5.3   | Quality Declaration                    |

### Summary of Features

Features: (continued)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Six ports

- Up to 48 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Four 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2 and Timer 21 (T2 and T21)

- Multiplication/Division Unit for arithmetic operations (MDU)

- Software libraries to support floating point and MDU calculations

- CORDIC Coprocessor for computation of trigonometric, hyperbolic and linear functions

- MultiCAN with 2 nodes, 32 message objects

- Capture/compare unit for PWM signal generation (CCU6)

- Two full-duplex serial interfaces (UART and UART1)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 12-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- Packages:

- PG-TQFP-48

- PG-TQFP-64

- Temperature range *T*<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

## XC886/888CLM

#### **General Device Information**

| Symbol            | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                     |

|-------------------|----------------------------|------|----------------|--------------------------------------------------------------------------------------------------------------|

| V <sub>DDP</sub>  | 7, 17, 43/<br>7, 25, 55    | _    | -              | <b>I/O Port Supply (3.3 or 5.0 V)</b><br>Also used by EVR and analog modules. All<br>pins must be connected. |

| $V_{\rm SSP}$     | 18, 42/26, 54              | _    | -              | I/O Port Ground<br>All pins must be connected.                                                               |

| $V_{DDC}$         | 6/6                        | _    | _              | Core Supply Monitor (2.5 V)                                                                                  |

| V <sub>SSC</sub>  | 5/5                        | _    | _              | Core Supply Ground                                                                                           |

| $V_{AREF}$        | 24/32                      | _    | _              | ADC Reference Voltage                                                                                        |

| $V_{AGND}$        | 23/31                      | _    | _              | ADC Reference Ground                                                                                         |

| XTAL1             | 4/4                        | I    | Hi-Z           | External Oscillator Input<br>(backup for on-chip OSC, normally NC)                                           |

| XTAL2             | 3/3                        | 0    | Hi-Z           | External Oscillator Output<br>(backup for on-chip OSC, normally NC)                                          |

| TMS               | 10/16                      | 1    | PD             | Test Mode Select                                                                                             |

| RESET             | 41/53                      | 1    | PU             | Reset Input                                                                                                  |

| MBC <sup>1)</sup> | 44/58                      | 1    | PU             | Monitor & BootStrap Loader Control                                                                           |

| NC                | -/56, 57                   | _    | -              | No Connection                                                                                                |

### Table 3Pin Definitions and Functions (cont'd)

1) An external pull-up device in the range of 4.7 k $\Omega$  to 100 k $\Omega$ . is required to enter user mode. Alternatively MBC can be tied to high if alternate functions (for debugging) of the pin are not utilized.

The page register has the following definition:

## MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

# XC886/888CLM

# **Functional Description**

# Table 10Port Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|---------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| RMAP =          | = 0, PAGE 1                                                         |           |    |    |    |    |    |    | L  |    |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Select Register                                | Туре      | rw |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| A0 <sub>H</sub> | P2_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| A1 <sub>H</sub> | P2_PUDEN Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| во <sub>Н</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| в1 <sub>Н</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| C8 <sub>H</sub> | P4_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| RMAP =          | = 0, PAGE 2                                                         |           |    |    |    |    |    |    |    |    |

| <sup>80</sup> H | P0_ALTSEL0 Reset: 00 <sub>H</sub>                                   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Alternate Select 0 Register                                      | Туре      | rw |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub><br>P0 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00 <sub>H</sub><br>P1 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 91 <sub>H</sub> | P1_ALTSEL1 Reset: 00 <sub>H</sub><br>P1 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 92 <sub>H</sub> | P5_ALTSEL0 Reset: 00 <sub>H</sub><br>P5 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

# Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                | Bit       | 7          | 6          | 5    | 4      | 3    | 2   | 1       | 0    |

|-----------------|--------------------------------------------------------------|-----------|------------|------------|------|--------|------|-----|---------|------|

| CDH             | ADC_LCBR Reset: B7 <sub>H</sub>                              | Bit Field |            | BOU        | IND1 |        |      | BOL | JND0    |      |

|                 | Limit Check Boundary Register                                | Туре      |            | r          | N    |        |      | r   | w       |      |

| CEH             | ADC_INPCR0 Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | S      | тс   |     |         |      |

|                 | Input Class 0 Register                                       | Туре      |            |            |      | r      | w    |     |         |      |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub><br>External Trigger Control | Bit Field | SYNE<br>N1 | SYNE<br>N0 |      | ETRSEL | 1    |     | ETRSELO |      |

|                 | Register                                                     | Туре      | rw         | rw         |      | rw     |      |     | rw      |      |

| RMAP =          | 0, PAGE 1                                                    |           | •          |            | •    |        |      | •   |         |      |

| CAH             | ADC_CHCTR0 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )   | RESE    | RSEL |

|                 | Channel Control Register 0                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| св <sub>Н</sub> | ADC_CHCTR1 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | C   | RESE    | RSEL |

|                 | Channel Control Register 1                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )   | RESE    | RSEL |

|                 | Channel Control Register 2                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| CDH             | ADC_CHCTR3 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | C   | RESE    | RSEL |

|                 | Channel Control Register 3                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| CEH             | ADC_CHCTR4 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )   | RESE    | RSEL |

|                 | Channel Control Register 4                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| CFH             | ADC_CHCTR5 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )   | RESE    | RSEL |

|                 | Channel Control Register 5                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | C   | RESE    | RSEL |

|                 | Channel Control Register 6                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00 <sub>H</sub>                            | Bit Field | 0          |            | LCC  |        | (    | )   | RESE    | RSEL |

|                 | Channel Control Register 7                                   | Туре      | r          |            | rw   |        |      | r   | n       | N    |

| RMAP =          | 0, PAGE 2                                                    |           | •          |            |      |        |      |     |         |      |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |     | CHNR    |      |

|                 | Result Register 0 Low                                        | Туре      | r          | h          | r    | rh     | rh   |     | rh      |      |

| св <sub>Н</sub> | ADC_RESR0H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |     |         |      |

|                 | Result Register 0 High                                       | Туре      |            |            |      | I      | ħ    |     |         |      |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |     | CHNR    |      |

|                 | Result Register 1 Low                                        | Туре      | r          | 'n         | r    | rh     | rh   |     | rh      |      |

| CDH             | ADC_RESR1H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |     |         |      |

|                 | Result Register 1 High                                       | Туре      |            |            |      | I      | 'n   |     |         |      |

| CEH             | ADC_RESR2L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |     | CHNR    |      |

|                 | Result Register 2 Low                                        | Туре      | r          | h          | r    | rh     | rh   |     | rh      |      |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |      | RES    | SULT |     |         |      |

|                 | Result Register 2 High                                       | Туре      |            |            |      |        | ħ    |     |         |      |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00 <sub>H</sub>                            | Bit Field | RES        | SULT       | 0    | VF     | DRC  |     | CHNR    |      |

|                 | Result Register 3 Low                                        | Туре      | r          | 'n         | r    | rh     | rh   |     | rh      |      |

# Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1           | 0           |

|-----------------|----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|-------------|-------------|

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                   | Bit Field |            | 1          | 1          | CC6        | 60VH       | 1          | 1           | 1           |

|                 | Capture/Compare Register for<br>Channel CC60 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VL       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 Low                     | Туре      |            |            |            | r          | 'n         |            |             |             |

| FD <sub>H</sub> | CCU6_CC61RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 61VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC61 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VL       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 Low                     | Туре      |            |            |            | r          | h          |            |             |             |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00 <sub>H</sub>                                   | Bit Field |            |            |            | CC6        | 62VH       |            |             |             |

|                 | Capture/Compare Register for<br>Channel CC62 High                    | Туре      |            |            |            | r          | 'n         |            |             |             |

| RMAP =          | 0, PAGE 2                                                            | _         |            |            |            |            | _          |            |             |             |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub>                                 | Bit Field |            | MS         | EL61       |            |            | MSE        | EL60        |             |

|                 | T12 Capture/Compare Mode Select<br>Register Low                      | Туре      |            | r          | w          |            |            | r          | w           |             |

| 9В <sub>Н</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                 | Bit Field | DBYP       |            | HSYNC      |            |            | MSE        | EL62        |             |

|                 | T12 Capture/Compare Mode Select<br>Register High                     | Туре      | rw         |            | rw         |            |            | r          | w           |             |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub>                                     |           | ENCC       |            |            |            |            |            |             |             |

|                 | Capture/Compare Interrupt Enable<br>Register Low                     |           | 2<br>PM    | 2<br>OM    | 62F        | 62R        | 61F        | 61R        | 60F         | 60R         |

|                 |                                                                      | Туре      | rw          | rw          |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Enable | Bit Field | EN<br>STR  | EN<br>IDLE | EN<br>WHE  | EN<br>CHE  | 0          | EN<br>TRPF | ENT1<br>3PM | ENT1<br>3CM |

|                 | Register High                                                        | Туре      | rw         | rw         | rw         | rw         | r          | rw         | rw          | rw          |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                     | Bit Field | INP        | CHE        | INPO       | CC62       | INPO       | CC61       | INPO        | CC60        |

|                 | Capture/Compare Interrupt Node<br>Pointer Register Low               | Туре      | r          | w          | r          | w          | r          | w          | r           | w           |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                     | Bit Field | (          | 0          | INP        | T13        | 3 INPT12   |            | INP         | ERR         |

|                 | Capture/Compare Interrupt Node<br>Pointer Register High              | Туре      |            | r          | r          | w          | r          | w          | r           | w           |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | ST12<br>PM | ST12<br>OM | SCC6<br>2F | SCC6<br>2R | SCC6<br>1F | SCC6<br>1R | SCC6<br>0F  | SCC6<br>0R  |

|                 | Set Register Low                                                     | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status | Bit Field | SSTR       | SIDLE      | SWHE       | SCHE       | SWH<br>C   | STRP<br>F  | ST13<br>PM  | ST13<br>CM  |

|                 | Set Register High                                                    | Туре      | w          | w          | w          | w          | w          | w          | w           | w           |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub>                                     | Bit Field | PSL63      | 0          |            |            | P          | SL         | •           |             |

|                 | Passive State Level Register                                         | Туре      | rwh        | r          |            |            | rv         | vh         |             |             |

| а7 <sub>Н</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub>                                   | Bit Field | (          | 0          | SW         | SYN        | 0          |            | SWSEL       |             |

|                 | Multi-Channel Mode Control Register                                  | Туре      |            | r          | r          | w          | r          |            | rw          |             |

| FA <sub>H</sub> | CCU6_TCTR2LReset: 00HTimer Control Register 2 Low                    | Bit Field | 0          | T13        | TED        |            | T13TEC     |            | T13<br>SSC  | T12<br>SSC  |

|                 |                                                                      | Туре      | r          | r          | W          |            | rw         |            | rw          | rw          |

# Table 18OCDS Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|------------------------------|-----------|---|---|---|----|-----|---|---|---|

| EC <sub>H</sub> | MMWR2 Reset: 00 <sub>H</sub> | Bit Field |   |   |   | MM | WR2 |   |   |   |

|                 | Monitor Work Register 2      | Туре      |   |   |   | n  | w   |   |   |   |

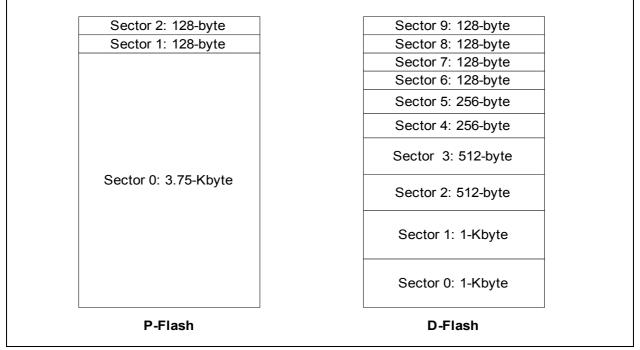

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

# 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

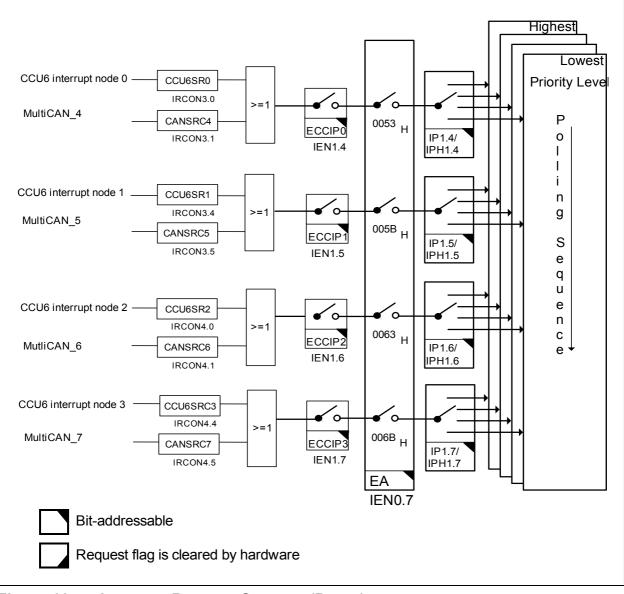

Figure 18 Interrupt Request Sources (Part 5)

# 3.5 Parallel Ports

The XC886 has 34 port pins organized into five parallel ports, Port 0 (P0) to Port 4 (P4), while the XC888 has 48 port pins organized into six parallel ports, Port 0 (P0) to Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1, P3, P4 and P5 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals. Converter (ADC).

### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

### Input Port Features

- Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- Alternate input for on-chip peripherals

- Analog input for ADC module

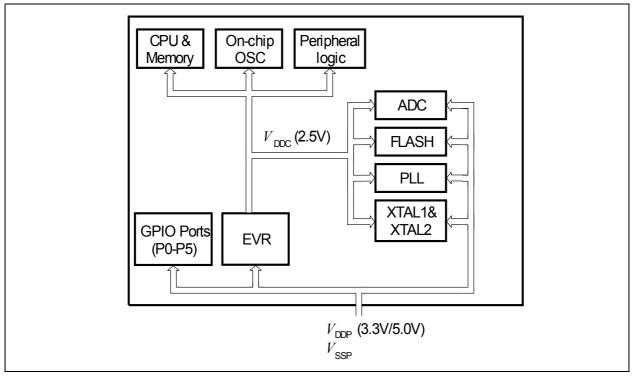

# 3.6 Power Supply System with Embedded Voltage Regulator

The XC886/888 microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 21** shows the XC886/888 power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 21 XC886/888 Power Supply System

### **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 3.3 V/5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- · Low power voltage regulator provided in power-down mode

- $V_{\text{DDC}}$  and  $V_{\text{DDP}}$  prewarning detection

- $V_{\text{DDC}}$  brownout detection

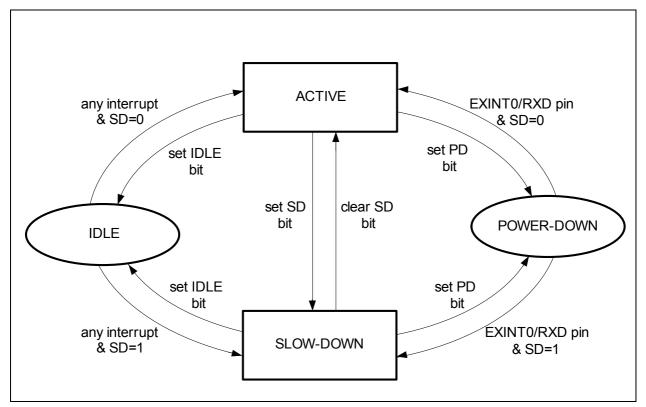

# 3.9 Power Saving Modes

The power saving modes of the XC886/888 provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- Power-down of the entire system with fast restart capability

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 27**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- Idle mode

- Slow-down mode

- Power-down mode

Figure 27 Transition between Power Saving Modes

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.4)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 29**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

## 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |

# 3.19 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

### Timer T12 Features

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- · Generation of center-aligned and edge-aligned PWM

- Supports single-shot mode

- Supports many interrupt request sources

- Hysteresis-like control mode

### **Timer T13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Supports single-shot mode

### Additional Features

- Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- · Control modes for multi-channel AC-drives

- Output levels can be selected and adapted to the power stage

The block diagram of the CCU6 module is shown in **Figure 33**.

# Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                      | Symbo                 |    | Limit                                                    | Values                  | Unit | Test Conditions                                        |  |

|--------------------------------------------------------------------------------|-----------------------|----|----------------------------------------------------------|-------------------------|------|--------------------------------------------------------|--|

|                                                                                |                       |    | min.                                                     | max.                    |      |                                                        |  |

| Input high voltage on RESET pin                                                | $V_{IHR}$             | SR | $0.7 \times V_{ m DDP}$                                  | -                       | V    | CMOS Mode                                              |  |

| Input high voltage on<br>TMS pin                                               | V <sub>IHT</sub>      | SR | $0.75 \times V_{ m DDP}$                                 | -                       | V    | CMOS Mode                                              |  |

| Input Hysteresis on port pins                                                  | HYSP                  | CC | $\begin{array}{c} 0.07 \times \\ V_{ m DDP} \end{array}$ | -                       | V    | CMOS Mode <sup>1)</sup>                                |  |

| Input Hysteresis on<br>XTAL1                                                   | HYSX                  | CC | $\begin{array}{c} 0.07 \times \\ V_{ m DDC} \end{array}$ | -                       | V    | 1)                                                     |  |

| Input low voltage at<br>XTAL1                                                  | $V_{ILX}$             | SR | V <sub>SS</sub> -<br>0.5                                 | $0.3 \times V_{ m DDC}$ | V    |                                                        |  |

| Input high voltage at XTAL1                                                    | V <sub>IHX</sub>      | SR | $0.7 \times V_{ m DDC}$                                  | V <sub>DDC</sub> + 0.5  | V    |                                                        |  |

| Pull-up current                                                                | $I_{\rm PU}$          | SR | _                                                        | -10                     | μA   | V <sub>IHP,min</sub>                                   |  |

|                                                                                |                       |    | -150                                                     | _                       | μA   | $V_{\rm ILP,max}$                                      |  |

| Pull-down current                                                              | $I_{\rm PD}$          | SR | -                                                        | 10                      | μA   | $V_{ILP,max}$                                          |  |

|                                                                                |                       |    | 150                                                      | -                       | μA   | $V_{\rm IHP,min}$                                      |  |

| Input leakage current                                                          | I <sub>OZ1</sub>      | CC | -1                                                       | 1                       | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |  |

| Input current at XTAL1                                                         | $I_{ILX}$             | CC | -10                                                      | 10                      | μA   |                                                        |  |

| Overload current on any pin                                                    | I <sub>OV</sub>       | SR | -5                                                       | 5                       | mA   |                                                        |  |

| Absolute sum of overload currents                                              | $\Sigma  I_{\rm OV} $ | SR | -                                                        | 25                      | mA   | 3)                                                     |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                           | V <sub>PO</sub>       | SR | -                                                        | 0.3                     | V    | 4)                                                     |  |

| Maximum current per pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )            | I <sub>M</sub> SR     | SR | -                                                        | 15                      | mA   |                                                        |  |

| Maximum current for all pins (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $      | SR | -                                                        | 90                      | mA   |                                                        |  |

| Maximum current into $V_{\text{DDP}}$                                          | I <sub>MVDDP</sub>    | SR | -                                                        | 120                     | mA   | 3)                                                     |  |

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                                |                   |    | min. max.                   |                             |      |                           |  |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |  |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |  |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                                |                   |    | —                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |  |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | -                           | V    | CMOS Mode <sup>1)</sup>   |  |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |  |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |  |

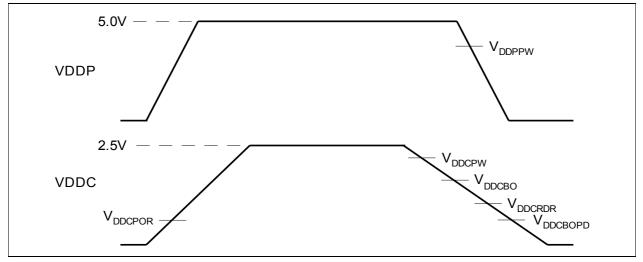

### 4.2.2 Supply Threshold Characteristics

Table 39 provides the characteristics of the supply threshold in the XC886/888.

Figure 38 Supply Threshold Parameters

| Table 39 | Supply Threshold Parameters | (Operating Conditions apply) |

|----------|-----------------------------|------------------------------|

|----------|-----------------------------|------------------------------|

| Parameters                                                         | Symbol               |    | Limit Values |      |      | Unit |

|--------------------------------------------------------------------|----------------------|----|--------------|------|------|------|

|                                                                    |                      |    | min.         | typ. | max. |      |

| $V_{\rm DDC}$ prewarning voltage <sup>1)</sup>                     | V <sub>DDCPW</sub>   | CC | 2.2          | 2.3  | 2.4  | V    |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | CC | 2.0          | 2.1  | 2.2  | V    |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | CC | 0.9          | 1.0  | 1.1  | V    |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | CC | 1.3          | 1.5  | 1.7  | V    |

| $V_{\rm DDP}$ prewarning voltage <sup>3)</sup>                     | V <sub>DDPPW</sub>   | CC | 3.4          | 4.0  | 4.6  | V    |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | CC | 1.3          | 1.5  | 1.7  | V    |

1) Detection is disabled in power-down mode.

2) Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V. Detection must be disabled for external power supply of 3.3V.

4) The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

# 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$