# Infineon Technologies - XC886LM6FFA5VACFXUMA1 Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                         |

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | LINbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 34                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | -                                                                                |

| Package / Case             | -                                                                                |

| Supplier Device Package    | -                                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886lm6ffa5vacfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                                                                                        |                                                                                                                                                        |  |  |  |  |

|--------|----------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P2     |                            | I    |                | Port 2 Port 2 is an 8-bit general purpose input-only port. It can be used as alternate functions for the digital inputs of the JTAG and CCU6. It is also used as the analog inputs for the ADC. |                                                                                                                                                        |  |  |  |  |

| P2.0   | 14/22                      |      | Hi-Z           | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>TCK_1<br>CC61_3<br>AN0                                                                                                                                       | CCU6 Hall Input 0 External Interrupt Input 1 CCU6 Timer 12 Hardware Run Input JTAG Clock Input Input of Capture/Compare channel 1 Analog Input 0       |  |  |  |  |

| P2.1   | 15/23                      |      | Hi-Z           | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>TDI_1<br>CC62_3<br>AN1                                                                                                                                       | CCU6 Hall Input 1 External Interrupt Input 2 CCU6 Timer 13 Hardware Run Input JTAG Serial Data Input Input of Capture/Compare channel 2 Analog Input 1 |  |  |  |  |

| P2.2   | 16/24                      |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>CC60_3<br>AN2                                                                                                                                                            | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0<br>Analog Input 2                                                        |  |  |  |  |

| P2.3   | 19/27                      |      | Hi-Z           | AN3                                                                                                                                                                                             | Analog Input 3                                                                                                                                         |  |  |  |  |

| P2.4   | 20/28                      |      | Hi-Z           | AN4                                                                                                                                                                                             | Analog Input 4                                                                                                                                         |  |  |  |  |

| P2.5   | 21/29                      |      | Hi-Z           | AN5                                                                                                                                                                                             | Analog Input 5                                                                                                                                         |  |  |  |  |

| P2.6   | 22/30                      |      | Hi-Z           | AN6                                                                                                                                                                                             | Analog Input 6                                                                                                                                         |  |  |  |  |

| P2.7   | 25/33                      |      | Hi-Z           | AN7                                                                                                                                                                                             | Analog Input 7                                                                                                                                         |  |  |  |  |

# **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                          |                                                                        |  |  |  |

|--------|----------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| P5     |                            | I/O  |                | Port 5 Port 5 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for UART, UART1 and JTAG. |                                                                        |  |  |  |

| P5.0   | <b>-/8</b>                 |      | PU             | EXINT1_1                                                                                                                          | External Interrupt Input 1                                             |  |  |  |

| P5.1   | <b>-</b> /9                |      | PU             | EXINT2_1                                                                                                                          | External Interrupt Input 2                                             |  |  |  |

| P5.2   | <b>-/12</b>                |      | PU             | RXD_2                                                                                                                             | UART Receive Data Input                                                |  |  |  |

| P5.3   | <b>-</b> /13               |      | PU             | TXD_2                                                                                                                             | UART Transmit Data Output/Clock Output                                 |  |  |  |

| P5.4   | <b>-/14</b>                |      | PU             | RXDO_2                                                                                                                            | UART Transmit Data Output                                              |  |  |  |

| P5.5   | <b>-/15</b>                |      | PU             | TDO_2<br>TXD1_2                                                                                                                   | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output |  |  |  |

| P5.6   | <b>-</b> /19               |      | PU             | TCK_2<br>RXDO1_2                                                                                                                  | JTAG Clock Input<br>UART1 Transmit Data Output                         |  |  |  |

| P5.7   | <b>-/20</b>                |      | PU             | TDI_2<br>RXD1_2                                                                                                                   | JTAG Serial Data Input<br>UART1 Receive Data Input                     |  |  |  |

Data Sheet 17 V1.2, 2009-07

# 3 Functional Description

Chapter 3 provides an overview of the XC886/888 functional description.

### 3.1 Processor Architecture

The XC886/888 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC886/888 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The XC886/888 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and Special Function Registers (SFRs).

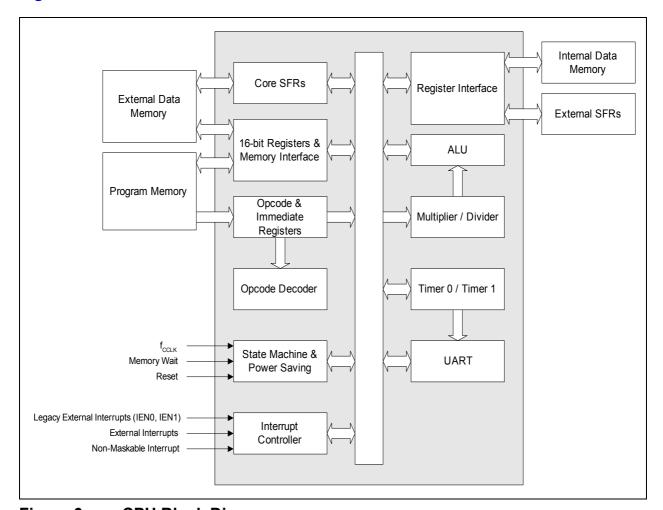

Figure 6 shows the CPU functional blocks.

Figure 6 CPU Block Diagram

Table 4 Flash Protection Modes (cont'd)

| Flash Protection                      | Without hardware protection             | With hardware prote                                                                                     | ction                                              |

|---------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| P-Flash program and erase             | Possible                                | Not possible                                                                                            | Not possible                                       |

| D-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in any program memory                                                                 | Read instructions in<br>the P-Flash or D-<br>Flash |

| External access to D-Flash            | Not possible                            | Not possible                                                                                            | Not possible                                       |

| D-Flash<br>program                    | Possible                                | Possible                                                                                                | Not possible                                       |

| D-Flash erase                         | Possible                                | Possible, on condition that bit DFLASHEN in register MISC_CON is set to 1 prior to each erase operation | Not possible                                       |

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. The Flash protection is then disabled upon the next reset.

For the ROM device, the ROM is protected at all times and BSL mode 6 is used only to block external access to the device. However, unlike the Flash device, it is not possible to disable the memory protection of the ROM device. Here, entering BSL mode 6 will result in a protection error.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

Although no protection scheme can be considered infallible, the XC886/888 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

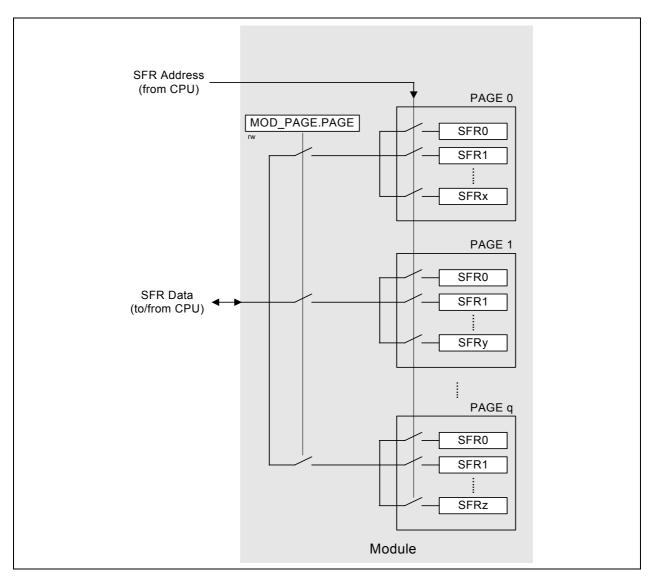

## 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to  $FF_H$ . All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

# 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_{\rm H}$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_{\rm H}$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Data Sheet 23 V1.2, 2009-07

Figure 9 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

# 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**. *Note: The addresses of the bitaddressable SFRs appear in bold typeface.*

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

Table 5 CPU Register Overview

| Addr            | Register Name                                         | Bit       | 7            | 6    | 5    | 4           | 3         | 2    | 1    | 0          |  |

|-----------------|-------------------------------------------------------|-----------|--------------|------|------|-------------|-----------|------|------|------------|--|

| RMAP =          | = 0 or 1                                              | I.        | I .          |      | I    | I           | I         | I    | I    | ·          |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                             | Bit Field | Bit Field SP |      |      |             |           |      |      |            |  |

|                 | Stack Pointer Register                                | Туре      | rw           |      |      |             |           |      |      |            |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                            | Bit Field | DPL7         | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |  |

|                 | Data Pointer Register Low                             | Туре      | rw           | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                            | Bit Field | DPH7         | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |  |

|                 | Data Pointer Register High                            | Туре      | rw           | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                           | Bit Field | SMOD         |      | 0    |             | GF1       | GF0  | 0    | IDLE       |  |

|                 | Power Control Register                                | Туре      | rw           |      | r    |             | rw        | rw   | r    | rw         |  |

| 88 <sub>H</sub> | TCON Reset: 00 <sub>H</sub>                           | Bit Field | TF1          | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |  |

|                 | Timer Control Register                                | Туре      | rwh          | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub> Timer Mode Register       | Bit Field | GATE<br>1    | T1S  | T1M  |             | GATE<br>0 | TOS  | TO   | OM         |  |

|                 |                                                       | Туре      | rw           | rw   | r    | W           | rw        | rw   | r    | W          |  |

| 8A <sub>H</sub> | TL0 Reset: 00H                                        | Bit Field |              |      |      | V           | ٩L        |      |      |            |  |

|                 | Timer 0 Register Low                                  | Туре      | rwh          |      |      |             |           |      |      |            |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                            | Bit Field |              |      |      | V           | AL        |      |      |            |  |

|                 | Timer 1 Register Low                                  | Туре      |              |      |      | rv          | wh        |      |      |            |  |

| 8C <sub>H</sub> | THO Reset: 00H                                        | Bit Field |              |      |      | V           | ٩L        |      |      |            |  |

|                 | Timer 0 Register High                                 | Туре      |              |      |      | rv          | vh        |      |      |            |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                            | Bit Field |              |      |      | V           | ٩L        |      |      |            |  |

|                 | Timer 1 Register High                                 | Туре      |              |      |      | rv          | vh        |      |      |            |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                           | Bit Field | SM0          | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |  |

|                 | Serial Channel Control Register                       | Туре      | rw           | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                           | Bit Field |              |      |      | V           | ٩L        |      |      |            |  |

|                 | Serial Data Buffer Register                           | Туре      |              |      |      | rv          | vh        |      |      |            |  |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub> Extended Operation Register | Bit Field |              | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |  |

|                 |                                                       | Туре      |              | ŗ    |      | rw          |           | r    |      | rw         |  |

Table 8 SCU Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7             | 6 | 5           | 4               | 3             | 2           | 1             | 0             |

|-----------------|----------------------------------------------------------------------|-----------|---------------|---|-------------|-----------------|---------------|-------------|---------------|---------------|

| BE <sub>H</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field | 0 TLEN COUT S |   |             |                 | СО            | REL         |               |               |

|                 |                                                                      | Туре      |               | r | rw          | rw              |               | r           | W             |               |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register    | Bit Field |               |   |             | 0               |               |             |               | DFLAS<br>HEN  |

|                 |                                                                      | Туре      |               |   |             | r               |               |             |               | rwh           |

| RMAP =          | = 0, PAGE 3                                                          |           |               |   |             |                 |               |             |               |               |

| B3 <sub>H</sub> | XADDRH Reset: F0H                                                    | Bit Field |               |   |             | ADI             | ORH           |             |               |               |

|                 | On-chip XRAM Address Higher Order                                    | Туре      |               |   |             | r               | W             |             |               |               |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub> Interrupt Request Register 3           | Bit Field |               | 0 | CANS<br>RC5 | CCU6<br>SR1     | (             | 0           | CANS<br>RC4   | CCU6<br>SR0   |

|                 |                                                                      | Туре      | r             |   | rwh         | rwh             | r             |             | rwh           | rwh           |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub> Interrupt Request Register 4           | Bit Field |               | 0 | CANS<br>RC7 | CCU6<br>SR3     | 0             |             | CANS<br>RC6   | CCU6<br>SR2   |

|                 |                                                                      | Туре      |               | r | rwh         | rwh             |               | r           | rwh           | rwh           |

| В7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS  |   | 0           | UR <sup>2</sup> | RIS           | T21EX<br>IS | JTAGT<br>DIS1 | JTAGT<br>CKS1 |

|                 | 1                                                                    | Туре      | rw            |   | r           | r               | W             | rw          | rw            | rw            |

| BA <sub>H</sub> | MODPISEL2 Reset: 00H                                                 | Bit Field |               | ( | 0           |                 | T21IS         | T2IS        | T1IS          | TOIS          |

|                 | Peripheral Input Select Register 2                                   | Туре      |               |   | r           |                 | rw            | rw          | rw            | rw            |

| ввн             | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field | 0             |   |             |                 | UART<br>1_DIS | T21_D<br>IS |               |               |

|                 |                                                                      | Туре      |               |   |             | r               |               |             | rw            | rw            |

| BD <sub>H</sub> | MODSUSP Reset: 01 <sub>H</sub> Module Suspend Control                | Bit Field |               | 0 |             | T21SU<br>SP     | T2SUS<br>P    | T13SU<br>SP | T12SU<br>SP   | WDTS<br>USP   |

|                 | Register                                                             | Туре      |               | r |             | rw              | rw            | rw          | rw            | rw            |

# 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 9 WDT Register Overview

| Addr   | Register Name                           | Bit       | 7       | 6 | 5          | 4         | 3 | 2         | 1         | 0         |

|--------|-----------------------------------------|-----------|---------|---|------------|-----------|---|-----------|-----------|-----------|

| RMAP = | : 1                                     |           |         |   |            |           |   |           |           |           |

| ввн    | Watchdog Timer Control                  |           | (       | ) | WINB<br>EN | WDTP<br>R | 0 | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|        | Register                                | Туре      |         | r | rw         | rh        | r | rw        | rwh       | rw        |

| всн    | WDTREL Reset: 00 <sub>H</sub>           | Bit Field | WDTREL  |   |            |           |   |           |           |           |

|        | Watchdog Timer Reload<br>Register       | Туре      |         |   |            | rw        |   |           |           |           |

| вDН    | WDTWINB Reset: 00 <sub>H</sub>          | Bit Field | WDTWINB |   |            |           |   |           |           |           |

|        | Watchdog Window-Boundary Count Register | Туре      | rw      |   |            |           |   |           |           |           |

Table 10 Port Register Overview (cont'd)

| Addr            | Register Name                  | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|--------------------------------|-----------|----|----|----|----|----|----|----|----|

| 93 <sub>H</sub> | P5_ALTSEL1 Reset: 00H          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Alternate Select 1 Register | Туре      | rw |

| во <sub>Н</sub> | P3_ALTSEL0 Reset: 00H          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 0 Register | Туре      | rw |

| В1 <sub>Н</sub> | P3_ALTSEL1 Reset: 00H          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register | Туре      | rw |

| C8 <sub>H</sub> | P4_ALTSEL0 Reset: 00H          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 0 Register | Туре      | rw |

| C9 <sub>H</sub> | P4_ALTSEL1 Reset: 00H          | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Alternate Select 1 Register | Туре      | rw |

| RMAP =          | = 0, PAGE 3                    |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register | Туре      | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Open Drain Control Register | Туре      | rw |

| 92 <sub>H</sub> | P5_OD Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Open Drain Control Register | Туре      | rw |

| во <sub>Н</sub> | P3_OD Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register | Туре      | rw |

| C8H             | P4_OD Reset: 00 <sub>H</sub>   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Open Drain Control Register | Туре      | rw |

# 3.2.4.7 ADC Registers

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

Table 11 ADC Register Overview

| Addr            | Register Name                                                     | Bit       | 7         | 6         | 5     | 4    | 3    | 2     | 1          | 0     |

|-----------------|-------------------------------------------------------------------|-----------|-----------|-----------|-------|------|------|-------|------------|-------|

| RMAP =          | = 0                                                               |           |           |           |       |      |      |       |            |       |

| D1 <sub>H</sub> | ADC_PAGE Reset: 00H                                               | Bit Field | С         | )P        | ST    | NR   | 0    |       | PAGE       |       |

|                 | Page Register                                                     | Туре      | ١         | V         | ١     | V    | r    |       | rw         |       |

| RMAP =          | = 0, PAGE 0                                                       |           |           |           |       |      |      |       |            |       |

| CAH             | ADC_GLOBCTR Reset: 30H                                            | Bit Field | ANON      | DW        | CTC 0 |      |      |       |            |       |

|                 | Global Control Register                                           | Туре      | rw        | rw        | r     | W    |      | r     |            |       |

| CB <sub>H</sub> | ADC_GLOBSTR Reset: 00 <sub>H</sub><br>Global Status Register      | Bit Field |           | 0         |       | CHNR |      | 0     | SAMP<br>LE | BUSY  |

|                 |                                                                   | Туре      |           | r         | rh    |      |      | r     | rh         | rh    |

| сс <sub>Н</sub> | ADC_PRAR Reset: 00 <sub>H</sub> Priority and Arbitration Register | Bit Field | ASEN<br>1 | ASEN<br>0 | 0     | ARBM | CSM1 | PRIO1 | CSM0       | PRIO0 |

|                 |                                                                   | Туре      | rw        | rw        | r     | rw   | rw   | rw    | rw         | rw    |

Table 11

ADC Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|-----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00H                                                 | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 3 High                                                | Туре      | rh         |            |            |            |            |            |            |            |

| RMAP =          | 0, PAGE 3                                                             | I.        | I          |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00H                                                | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 0, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| СВН             | ADC_RESRA0H Reset: 00H                                                | Bit Field |            |            |            | RES        | ULT        |            |            |            |

|                 | Result Register 0, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| CCH             | ADC_RESRA1L Reset: 00H                                                | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 1, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CDH             | ADC_RESRA1H Reset: 00H                                                | Bit Field |            |            |            | RES        | ULT        | L          |            |            |

|                 | Result Register 1, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| CEH             | ADC_RESRA2L Reset: 00H                                                | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |

|                 | Result Register 2, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00H                                                | Bit Field |            |            |            | RES        | ULT        | ULT        |            |            |

|                 | Result Register 2, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00H                                                | Bit Field |            | RESULT     |            | VF         | DRC CHNR   |            |            |            |

|                 | Result Register 3, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00H                                                | Bit Field |            |            |            | RES        | SULT       |            |            |            |

|                 | Result Register 3, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |

| RMAP =          | = 0, PAGE 4                                                           |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub> Result Control Register 0             | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| СВН             | ADC_RCR1 Reset: 00 <sub>H</sub> Result Control Register 1             | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| ссн             | ADC_RCR2 Reset: 00 <sub>H</sub> Result Control Register 2             | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub> Result Control Register 3             | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CEH             | ADC_VFCR Reset: 00H                                                   | Bit Field |            | (          | 0          |            | VFC3       | VFC2       | VFC1       | VFC0       |

|                 | Valid Flag Clear Register                                             | Туре      |            |            | r          |            | W          | W          | W          | W          |

| RMAP =          | 0, PAGE 5                                                             |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register  | Bit Field | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |

|                 |                                                                       | Туре      | rh         |

| СВН             | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register | Bit Field | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |

|                 |                                                                       | Туре      |            |            |            |            |            |            |            |            |

#### 3.7.1 Module Reset Behavior

Table 22 lists the functions of the XC886/888 and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

Table 22 Effect of Reset on Device Functions

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset         | Hardware<br>Reset         | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              |                           |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

# 3.7.2 Booting Scheme

When the XC886/888 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 23** shows the available boot options in the XC886/888.

Table 23 XC886/888 Boot Selection

| MBC | TMS | P0.0 | Type of Mode                                                           | PC Start Value    |

|-----|-----|------|------------------------------------------------------------------------|-------------------|

| 1   | 0   | X    | User Mode <sup>1)</sup> ; on-chip OSC/PLL non-bypassed                 | 0000 <sub>H</sub> |

| 0   | 0   | X    | BSL Mode; on-chip OSC/PLL non-bypassed <sup>2)</sup>                   | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-bypassed                                | 0000 <sub>H</sub> |

| 1   | 1   | 0    | User (JTAG) Mode <sup>3)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

#### **PLL Mode**

The system clock is derived from the oscillator clock, multiplied by the N factor, and divided by the P and K factors. Both VCO bypass and PLL bypass must be inactive for this PLL mode. The PLL mode is used during normal system operation.

$$f_{SYS} = f_{OSC} \times \frac{N}{P \times K}$$

(3.3)

## **System Frequency Selection**

For the XC886/888, the value of P is fixed to 1. In order to obtain the required fsys, the value of N and K can be selected by bits NDIV and KDIV respectively for different oscillator inputs. The output frequency must always be configured for 96 MHz. **Table 24** provides examples on how  $f_{\rm sys}$  = 96 MHz can be obtained for the different oscillator sources.

Table 24 System frequency ( $f_{svs}$  = 96 MHz)

| Oscillator | Fosc    | N  | Р | K | Fsys   |

|------------|---------|----|---|---|--------|

| On-chip    | 9.6 MHz | 20 | 1 | 2 | 96 MHz |

| External   | 8 MHz   | 24 | 1 | 2 | 96 MHz |

|            | 6 MHz   | 32 | 1 | 2 | 96 MHz |

|            | 4 MHz   | 48 | 1 | 2 | 96 MHz |

Data Sheet 74 V1.2, 2009-07

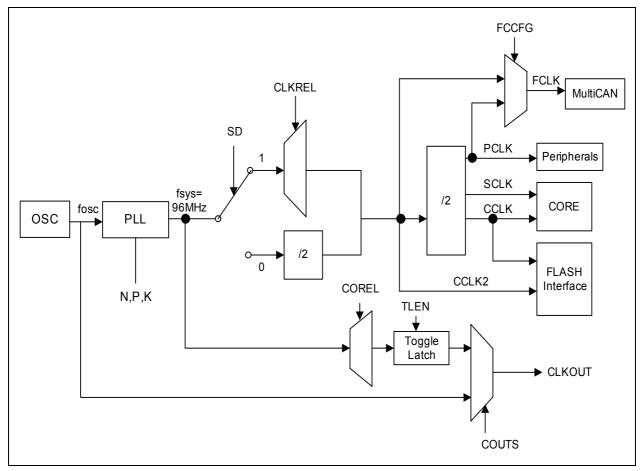

# 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{\rm sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{\text{sys}}$

# 3.12 CORDIC Coprocessor

The CORDIC Coprocessor provides CPU with hardware support for the solving of circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions.

#### **Features**

- Modes of operation

- Supports all CORDIC operating modes for solving circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions

- Integrated look-up tables (LUTs) for all operating modes

- Circular vectoring mode: Extended support for values of initial X and Y data up to full range of [-2<sup>15</sup>,(2<sup>15</sup>-1)] for solving angle and magnitude

- Circular rotation mode: Extended support for values of initial Z data up to full range of  $[-2^{15},(2^{15}-1)]$ , representing angles in the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$  for solving trigonometry

- Implementation-dependent operational frequency of up to 80 MHz

- · Gated clock input to support disabling of module

- 16-bit accessible data width

- 24-bit kernel data width plus 2 overflow bits for X and Y each

- 20-bit kernel data width plus 1 overflow bit for Z

- With KEEP bit to retain the last value in the kernel register for a new calculation

- 16 iterations per calculation: Approximately 41 clock-cycles or less, from set of start (ST) bit to set of end-of-calculation flag, excluding time taken for write and read access of data bytes.

- Twos complement data processing

- Only exception: X result data with user selectable option for unsigned result

- X and Y data generally accepted as integer or rational number; X and Y must be of the same data form

- Entries of LUTs are 20-bit signed integers

- Entries of atan and atanh LUTs are integer representations (S19) of angles with the scaling such that  $[-2^{15},(2^{15}-1)]$  represents the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$

- Accessible Z result data for circular and hyperbolic functions is integer in data form of S15

- Emulated LUT for linear function

- Data form is 1 integer bit and 15-bit fractional part (1.15)

- Accessible Z result data for linear function is rational number with fixed data form of S4.11 (signed 4Q16)

- Truncation Error

- The result of a CORDIC calculation may return an approximation due to truncation of LSBs

- Good accuracy of the CORDIC calculated result data, especially in circular mode

- Interrupt

- On completion of a calculation

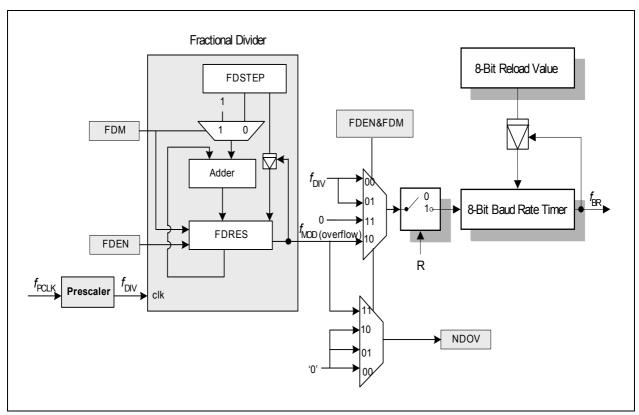

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 30**.

Figure 30 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP

(to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

Data Sheet 86 V1.2, 2009-07

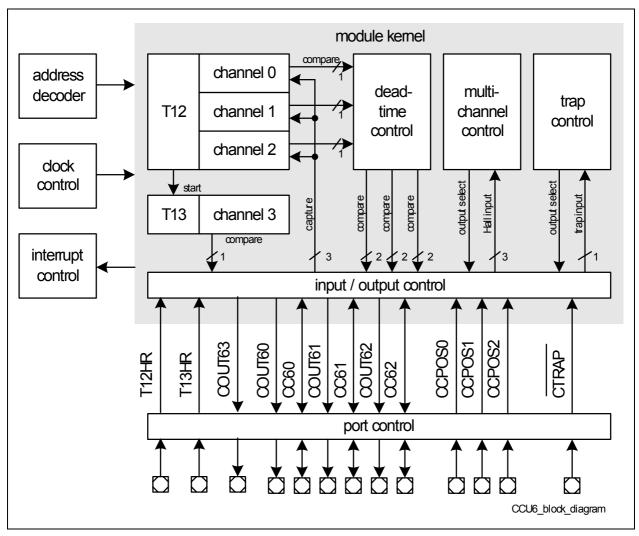

Figure 33 CCU6 Block Diagram

- CAN functionality according to CAN specification V2.0 B active.

- Dedicated control registers are provided for each CAN node.

- A data transfer rate up to 1 MBaud is supported.

- Flexible and powerful message transfer control and error handling capabilities are implemented.

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter.

- Full-CAN functionality: A set of 32 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message Objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 8 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 8 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 64 notification bits.

Data Sheet 98 V1.2, 2009-07

## **Electrical Parameters**

## 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

# 4.2.1 Input/Output Characteristics

Table 38 provides the characteristics of the input/output pins of the XC886/888.

Table 38

Input/Output Characteristics (Operating Conditions apply)

| Parameter                                                | Symbol     |    | Limit Values           |                               | Unit | Test Conditions                                          |

|----------------------------------------------------------|------------|----|------------------------|-------------------------------|------|----------------------------------------------------------|

|                                                          |            |    | min.                   | max.                          |      |                                                          |

| $V_{\rm DDP}$ = 5 V Range                                |            |    |                        |                               |      |                                                          |

| Output low voltage                                       | $V_{OL}$   | CC | _                      | 1.0                           | V    | $I_{\rm OL}$ = 15 mA                                     |

|                                                          |            |    | _                      | 1.0                           | V    | $I_{\rm OL}$ = 5 mA, current into all pins > 60 mA       |

|                                                          |            |    | _                      | 0.4                           | V    | $I_{\rm OL}$ = 5 mA, current into all pins $\leq$ 60 mA  |

| Output high voltage                                      | $V_{OH}$   | CC | V <sub>DDP</sub> - 1.0 | _                             | V    | I <sub>OH</sub> = -15 mA                                 |

|                                                          |            |    | V <sub>DDP</sub> - 1.0 | -                             | V    | $I_{\rm OH}$ = -5 mA, current from all pins > 60 mA      |

|                                                          |            |    | V <sub>DDP</sub> - 0.4 | _                             | V    | $I_{\rm OH}$ = -5 mA, current from all pins $\leq$ 60 mA |

| Input low voltage on port pins (all except P0.0 & P0.1)  | $V_{ILP}$  | SR | _                      | $0.3 \times V_{\text{DDP}}$   | V    | CMOS Mode                                                |

| Input low voltage on P0.0 & P0.1                         | $V_{ILP0}$ | SR | -0.2                   | $0.3 \times V_{\mathrm{DDP}}$ | V    | CMOS Mode                                                |

| Input low voltage on RESET pin                           | $V_{ILR}$  | SR | _                      | $0.3 \times V_{\mathrm{DDP}}$ | V    | CMOS Mode                                                |

| Input low voltage on TMS pin                             | $V_{ILT}$  | SR | _                      | $0.3 \times V_{\mathrm{DDP}}$ | V    | CMOS Mode                                                |

| Input high voltage on port pins (all except P0.0 & P0.1) | $V_{IHP}$  | SR | $0.7 \times V_{DDP}$   | _                             | V    | CMOS Mode                                                |

| Input high voltage on P0.0 & P0.1                        | $V_{IHP0}$ | SR | $0.7 	imes V_{ m DDP}$ | $V_{DDP}$                     | V    | CMOS Mode                                                |

# **Electrical Parameters**

Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                | Symbol     |    | Limit Values                   |                                                                    | Unit | Test Conditions           |

|----------------------------------------------------------|------------|----|--------------------------------|--------------------------------------------------------------------|------|---------------------------|

|                                                          |            |    | min. max.                      |                                                                    |      |                           |

| Maximum current out of $V_{\rm SS}$                      | $I_{MVSS}$ | SR | _                              | 120                                                                | mA   | 3)                        |

| $V_{\rm DDP}$ = 3.3 V Range                              |            |    |                                |                                                                    |      |                           |

| Output low voltage                                       | $V_{OL}$   | CC | _                              | 1.0                                                                | V    | I <sub>OL</sub> = 8 mA    |

|                                                          |            |    | _                              | 0.4                                                                | V    | $I_{\rm OL}$ = 2.5 mA     |

| Output high voltage                                      | $V_{OH}$   | CC | V <sub>DDP</sub> - 1.0         | _                                                                  | V    | $I_{\mathrm{OH}}$ = -8 mA |

|                                                          |            |    | V <sub>DDP</sub> - 0.4         | _                                                                  | V    | $I_{\rm OH}$ = -2.5 mA    |

| Input low voltage on port pins (all except P0.0 & P0.1)  | $V_{ILP}$  | SR | _                              | $0.3 \times V_{\text{DDP}}$                                        | V    | CMOS Mode                 |

| Input low voltage on P0.0 & P0.1                         | $V_{ILP0}$ | SR | -0.2                           | $0.3 \times V_{\mathrm{DDP}}$                                      | V    | CMOS Mode                 |

| Input low voltage on RESET pin                           | $V_{ILR}$  | SR | _                              | $0.3 \times V_{\mathrm{DDP}}$                                      | V    | CMOS Mode                 |

| Input low voltage on<br>TMS pin                          | $V_{ILT}$  | SR | _                              | $\begin{array}{c} \text{0.3} \times \\ V_{\text{DDP}} \end{array}$ | V    | CMOS Mode                 |

| Input high voltage on port pins (all except P0.0 & P0.1) | $V_{IHP}$  | SR | $0.7 \times V_{\text{DDP}}$    | _                                                                  | V    | CMOS Mode                 |

| Input high voltage on P0.0 & P0.1                        | $V_{IHP0}$ | SR | $0.7 	imes V_{ m DDP}$         | $V_{DDP}$                                                          | V    | CMOS Mode                 |

| Input high voltage on<br>RESET pin                       | $V_{IHR}$  | SR | $0.7 	imes V_{ m DDP}$         | -                                                                  | V    | CMOS Mode                 |

| Input high voltage on<br>TMS pin                         | $V_{IHT}$  | SR | $0.75 \times V_{\mathrm{DDP}}$ | _                                                                  | V    | CMOS Mode                 |

| Input Hysteresis                                         | HYS        | CC | $V_{\mathrm{DDP}}$             | _                                                                  | V    | CMOS Mode <sup>1)</sup>   |

| Input Hysteresis on<br>XTAL1                             | HYSX       | CC | $V_{\mathrm{DDC}}$             | _                                                                  | V    | 1)                        |

| Input low voltage at XTAL1                               | $V_{ILX}$  | SR | V <sub>SS</sub> - 0.5          | $0.3 \times V_{\mathrm{DDC}}$                                      | V    |                           |

## **Electrical Parameters**

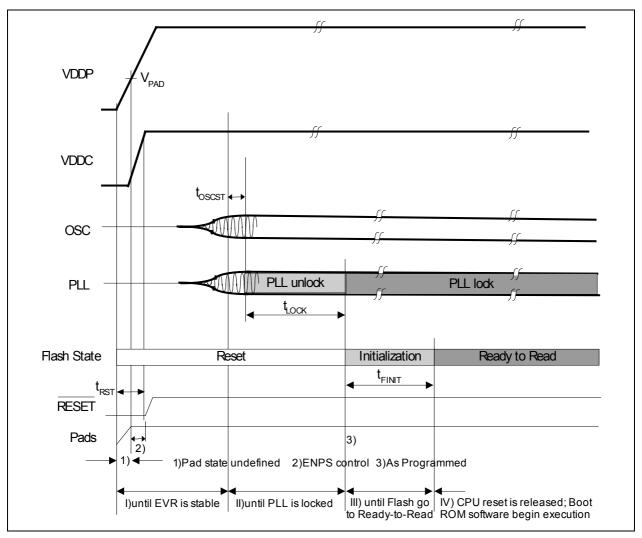

Figure 44 Power-on Reset Timing

Data Sheet 127 V1.2, 2009-07