Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | LINbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 34                                                                               |

| Program Memory Size        | 24KB (24K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-48                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886lm6ffa5vackxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_{H}$  to FF<sub>H</sub>. All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

## 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_H$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_H$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

### 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

## 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                            | Bit       | 7         | 6    | 5    | 4           | 3         | 2    | 1    | 0          |  |

|-----------------|----------------------------------------------------------|-----------|-----------|------|------|-------------|-----------|------|------|------------|--|

| RMAP =          | = 0 or 1                                                 | I.        |           |      |      |             |           |      |      |            |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                | Bit Field |           |      |      | S           | P         |      |      |            |  |

|                 | Stack Pointer Register                                   | Туре      |           |      |      | r           | W         |      |      |            |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                               | Bit Field | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |  |

|                 | Data Pointer Register Low                                | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                               | Bit Field | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |  |

|                 | Data Pointer Register High                               | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                              | Bit Field | SMOD      |      | 0    |             | GF1       | GF0  | 0    | IDLE       |  |

|                 | Power Control Register                                   | Туре      | rw        |      | r    |             | rw        | rw   | r    | rw         |  |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                              | Bit Field | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |  |

|                 | Timer Control Register                                   | Туре      | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register       | Bit Field | GATE<br>1 | T1S  | T1   | 1M          | GATE<br>0 | TOS  | T    | M          |  |

|                 |                                                          | Туре      | rw        | rw   | r    | w           | rw        | rw   | r    | w          |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                               | Bit Field |           | •    |      | V           | AL        | •    |      |            |  |

|                 | Timer 0 Register Low                                     | Туре      | rwh       |      |      |             |           |      |      |            |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Timer 1 Register Low                                     | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                               | Bit Field | VAL       |      |      |             |           |      |      |            |  |

|                 | Timer 0 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Timer 1 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                              | Bit Field | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |  |

|                 | Serial Channel Control Register                          | Туре      | rw        | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                              | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Serial Data Buffer Register                              | Туре      | rwh       |      |      |             |           |      |      |            |  |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub><br>Extended Operation Register | Bit Field |           | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |  |

|                 | · · ·                                                    | Туре      |           | r    |      | rw          |           | r    |      | rw         |  |

#### Table 5 CPU Register Overview

| Addr            | Register Name              | Bit       | 7          | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|-----------------|----------------------------|-----------|------------|------|---|----|----|---|---|---|--|--|--|--|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |            |      |   | DA | TA |   |   |   |  |  |  |  |

|                 | MDU Result Register 1      | Туре      | rh         |      |   |    |    |   |   |   |  |  |  |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |            |      |   | DA | TA |   |   |   |  |  |  |  |

|                 | MDU Operand Register 2     | Туре      | rw         |      |   |    |    |   |   |   |  |  |  |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |            | DATA |   |    |    |   |   |   |  |  |  |  |

|                 | MDU Result Register 2      | Туре      |            |      |   | r  | h  |   |   |   |  |  |  |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field |            |      |   | DA | TA |   |   |   |  |  |  |  |

|                 | MDU Operand Register 3     | Туре      | rw         |      |   |    |    |   |   |   |  |  |  |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field |            | DATA |   |    |    |   |   |   |  |  |  |  |

|                 | MDU Result Register 3      | Туре      | rh         |      |   |    |    |   |   |   |  |  |  |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field | DATA       |      |   |    |    |   |   |   |  |  |  |  |

|                 | MDU Operand Register 4     | Туре      |            |      |   | r  | w  |   |   |   |  |  |  |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |            |      |   | DA | TA |   |   |   |  |  |  |  |

|                 | MDU Result Register 4      | Туре      |            |      |   | r  | h  |   |   |   |  |  |  |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field | Field DATA |      |   |    |    |   |   |   |  |  |  |  |

|                 | MDU Operand Register 5     | Туре      | e rw       |      |   |    |    |   |   |   |  |  |  |  |

| в7 <sub>Н</sub> | MDU Result Register 5      | Bit Field |            |      |   | DA | TA |   |   |   |  |  |  |  |

|                 |                            | Туре      |            |      |   | r  | 'n |   |   |   |  |  |  |  |

#### Table 6MDU Register Overview (cont'd)

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |  |  |  |

|-----------------|----------------------------------|-----------|-------|---|---|----|-----|---|---|---|--|--|--|

| RMAP =          | = 1                              |           |       |   |   |    |     | 1 |   |   |  |  |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |  |  |  |

|                 | CORDIC X Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |  |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |  |  |

|                 | CORDIC X Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |  |  |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |  |

|                 | CORDIC Y Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field | DATAH |   |   |    |     |   |   |   |  |  |  |

|                 | CORDIC Y Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |  |  |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |  |  |

|                 | CORDIC Z Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |  |  |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | ТАН |   |   |   |  |  |  |

|                 | CORDIC Z Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |  |  |  |

| Addr            | Register Name                                                        | Bit       | 7            | 6 | 5           | 4           | 3          | 2           | 1             | 0             |

|-----------------|----------------------------------------------------------------------|-----------|--------------|---|-------------|-------------|------------|-------------|---------------|---------------|

| ве <sub>Н</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field | (            | ) | TLEN        | COUT<br>S   |            | CO          | REL           | <u> </u>      |

|                 |                                                                      | Туре      |              | r | rw          | rw          | rw         |             |               |               |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register    | Bit Field |              |   |             | 0           |            |             |               | DFLAS<br>HEN  |

|                 |                                                                      | Туре      |              |   |             | r           |            |             |               | rwh           |

| RMAP =          | = 0, PAGE 3                                                          |           |              |   |             |             |            |             |               |               |

| вз <sub>Н</sub> | XADDRH Reset: F0 <sub>H</sub>                                        | Bit Field |              |   |             | ADI         | ORH        |             |               |               |

|                 | On-chip XRAM Address Higher<br>Order                                 | Туре      |              |   |             | r           | w          |             |               |               |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub><br>Interrupt Request Register 3        | Bit Field | (            | ) | CANS<br>RC5 | CCU6<br>SR1 | (          | )           | CANS<br>RC4   | CCU6<br>SR0   |

|                 |                                                                      | Туре      | 1            | r | rwh         | rwh         | r          |             | rwh           | rwh           |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub><br>Interrupt Request Register 4        | Bit Field | (            | ) | CANS<br>RC7 | CCU6<br>SR3 | 0          |             | CANS<br>RC6   | CCU6<br>SR2   |

|                 |                                                                      | Туре      | I            | r | rwh         | rwh         | l          | r           | rwh           | rwh           |

| в7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS | ( | )           | UR′         | IRIS       | T21EX<br>IS | JTAGT<br>DIS1 | JTAGT<br>CKS1 |

|                 | 1                                                                    | Туре      | rw           |   | r           | r           | w          | rw          | rw            | rw            |

| ва <sub>Н</sub> | MODPISEL2 Reset: 00 <sub>H</sub>                                     | Bit Field |              | ( | )           |             | T21IS      | T2IS        | T1IS          | TOIS          |

|                 | Peripheral Input Select Register 2                                   | Туре      |              |   | r           |             | rw         | rw          | rw            | rw            |

| вв <sub>Н</sub> | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field | 0            |   |             | 0           |            |             | UART<br>1_DIS | T21_D<br>IS   |

|                 |                                                                      | Туре      | r            |   |             |             | rw         | rw          |               |               |

| вd <sub>Н</sub> | MODSUSP Reset: 01 <sub>H</sub><br>Module Suspend Control             | Bit Field | 0            |   |             | T21SU<br>SP | T2SUS<br>P | T13SU<br>SP | T12SU<br>SP   | WDTS<br>USP   |

|                 | Register                                                             | Туре      |              | r |             | rw          | rw         | rw          | rw            | rw            |

#### Table 8SCU Register Overview (cont'd)

# 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 9WDT Register Overview

| Addr            | Register Name                              | Bit       | 7      | 6 | 5          | 4         | 3    | 2         | 1         | 0         |

|-----------------|--------------------------------------------|-----------|--------|---|------------|-----------|------|-----------|-----------|-----------|

| RMAP =          | RMAP = 1                                   |           |        |   |            |           |      |           |           |           |

| вв <sub>Н</sub> | Watchdog Timer Control                     |           | (      | ) | WINB<br>EN | WDTP<br>R | 0    | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|                 | Register                                   | Туре      | pe r   |   | rw         | rh        | r    | rw        | rwh       | rw        |

| вс <sub>Н</sub> | H WDTREL Reset: 00 <sub>H</sub>            |           | WDTREL |   |            |           |      |           |           |           |

|                 | Watchdog Timer Reload<br>Register          | Туре      |        |   | rw         |           |      |           |           |           |

| вd <sub>Н</sub> | WDTWINB Reset: 00 <sub>H</sub>             | Bit Field |        |   |            | WDT       | WINB |           |           |           |

|                 | Watchdog Window-Boundary<br>Count Register | Туре      |        |   |            | r         | w    |           |           |           |

# XC886/888CLM

## **Functional Description**

## Table 10Port Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|---------------------------------------------------------------------|-----------|----|----|----|----|----|----|----|----|

| RMAP =          | = 0, PAGE 1                                                         |           |    |    |    |    |    |    | L  |    |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Select Register                                | Туре      | rw |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P1 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P5 Pull-Up/Pull-Down Enable Register                                | Туре      | rw |

| A0 <sub>H</sub> | P2_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| A1 <sub>H</sub> | P2_PUDEN Reset: 00 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P2 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| во <sub>Н</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| в1 <sub>Н</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| C8 <sub>H</sub> | P4_PUDSEL Reset: FF <sub>H</sub>                                    | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Select<br>Register                             | Туре      | rw |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                     | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P4 Pull-Up/Pull-Down Enable<br>Register                             | Туре      | rw |

| RMAP =          | = 0, PAGE 2                                                         |           |    |    |    |    |    |    |    |    |

| <sup>80</sup> H | P0_ALTSEL0 Reset: 00 <sub>H</sub>                                   | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Alternate Select 0 Register                                      | Туре      | rw |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub><br>P0 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00 <sub>H</sub><br>P1 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 91 <sub>H</sub> | P1_ALTSEL1 Reset: 00 <sub>H</sub><br>P1 Alternate Select 1 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

| 92 <sub>H</sub> | P5_ALTSEL0 Reset: 00 <sub>H</sub><br>P5 Alternate Select 0 Register | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 |                                                                     | Туре      | rw |

# 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

| Addr            | Register Name                                               | Bit       | 7          | 6          | 5           | 4    | 3         | 2     | 1    | 0          |

|-----------------|-------------------------------------------------------------|-----------|------------|------------|-------------|------|-----------|-------|------|------------|

| RMAP =          | = 0                                                         |           |            |            |             |      |           |       |      |            |

| c₀H             | T2_T2CON Reset: 00 <sub>H</sub><br>Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | )    | EXEN<br>2 | TR2   | C/T2 | CP/<br>RL2 |

|                 |                                                             | Туре      | rwh        | rwh        | I           | r    | rw        | rwh   | rw   | rw         |

| C1 <sub>H</sub> | T2_T2MOD Reset: 00 <sub>H</sub><br>Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |           | T2PRE |      | DCEN       |

|                 |                                                             | Туре      | rw         | rw         | rw          | rw   | rw        | rw    | rw   | rw         |

| C2 <sub>H</sub> | 2 <sub>H</sub> T2_RC2L Reset: 00 <sub>H</sub>               |           |            |            |             | R    | C2        |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register Low                      | Туре      | rwh        |            |             |      |           |       |      |            |

| C3 <sub>H</sub> | T2_RC2H Reset: 00 <sub>H</sub>                              | Bit Field | RC2        |            |             |      |           |       |      |            |

|                 | Timer 2 Reload/Capture<br>Register High                     | Туре      |            |            |             | rv   | vh        |       |      |            |

| C4 <sub>H</sub> | T2_T2L Reset: 00 <sub>H</sub>                               | Bit Field |            |            |             | TH   | IL2       |       |      |            |

|                 | Timer 2 Register Low                                        | Туре      | Гуре rwh   |            |             |      |           |       |      |            |

| C5 <sub>H</sub> | H T2_T2H Reset: 00 <sub>H</sub>                             | Bit Field |            |            |             | T⊦   | IL2       |       |      |            |

|                 | Timer 2 Register High                                       | Туре      |            |            |             | rv   | vh        |       |      |            |

#### Table 12T2 Register Overview

# 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 13T21 Register Overview

|                 | 0                                                                           |           |            |            |             |      |       |     |      |            |  |

|-----------------|-----------------------------------------------------------------------------|-----------|------------|------------|-------------|------|-------|-----|------|------------|--|

| Addr            | Register Name                                                               | Bit       | 7          | 6          | 5           | 4    | 3     | 2   | 1    | 0          |  |

| RMAP =          | = 1                                                                         |           |            |            |             |      |       |     |      |            |  |

| C0H             | T21_T2CONReset: 00HTimer 2 Control Register                                 | Bit Field | TF2        | EXF2       | (           | 0    |       | TR2 | C/T2 | CP/<br>RL2 |  |

|                 |                                                                             | Туре      | rwh        | rwh        | I           | r    | rw    | rwh | rw   | rw         |  |

| C1 <sub>H</sub> | T21_T2MODReset: 00Timer 2 Mode Register                                     | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN | T2PRE |     | DCEN |            |  |

|                 |                                                                             | Туре      | rw         | rw         | rw          | rw   | rw    | rw  | rw   | rw         |  |

| C2 <sub>H</sub> | T21_RC2L Reset: 00 <sub>H</sub>                                             | Bit Field | RC2        |            |             |      |       |     |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register Low                                      | Туре      | rwh        |            |             |      |       |     |      |            |  |

| C3 <sub>H</sub> | T21_RC2H Reset: 00 <sub>H</sub>                                             | Bit Field |            |            |             | R    | C2    |     |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register High                                     | Туре      | rwh        |            |             |      |       |     |      |            |  |

| C4 <sub>H</sub> | <sup>1</sup> H <b>T21_T2L Reset: 00<sub>H</sub></b><br>Timer 2 Register Low |           |            |            |             | TH   | IL2   |     |      |            |  |

|                 |                                                                             |           |            |            |             | ٢٧   | vh    |     |      |            |  |

## 3.3 Flash Memory

The Flash memory provides an embedded user-programmable non-volatile memory, allowing fast and reliable storage of user code and data. It is operated from a single 2.5 V supply from the Embedded Voltage Regulator (EVR) and does not require additional programming or erasing voltage. The sectorization of the Flash memory allows each sector to be erased independently.

### Features

- In-System Programming (ISP) via UART

- In-Application Programming (IAP)

- Error Correction Code (ECC) for dynamic correction of single-bit errors

- Background program and erase operations for CPU load minimization

- Support for aborting erase operation

- Minimum program width<sup>1)</sup> of 32-byte for D-Flash and 64-byte for P-Flash

- 1-sector minimum erase width

- 1-byte read access

- Flash is delivered in erased state (read all zeros)

- Operating supply voltage: 2.5 V ± 7.5 %

- Read access time:  $3 \times t_{CCLK} = 125 \text{ ns}^{2}$

- Program time: 248256 /  $f_{SYS}^{(3)}$  = 2.6 ms<sup>3)</sup>

- Erase time: 9807360 / f<sub>SYS</sub> = 102 ms<sup>3)</sup>

<sup>1)</sup> P-Flash: 64-byte wordline can only be programmed once, i.e., one gate disturb allowed. D-Flash: 32-byte wordline can be programmed twice, i.e., two gate disturbs allowed.

<sup>2)</sup> Values shown here are typical values.  $f_{sys}$  = 96 MHz ± 7.5% ( $f_{CCLK}$  = 24 MHz ± 7.5 %) is the maximum frequency range for Flash read access.

<sup>3)</sup> Values shown here are typical values.  $f_{sys} = 96 \text{ MHz} \pm 7.5\%$  is the only frequency range for Flash programming and erasing.  $f_{sysmin}$  is used for obtaining the worst case timing.

# 3.6 Power Supply System with Embedded Voltage Regulator

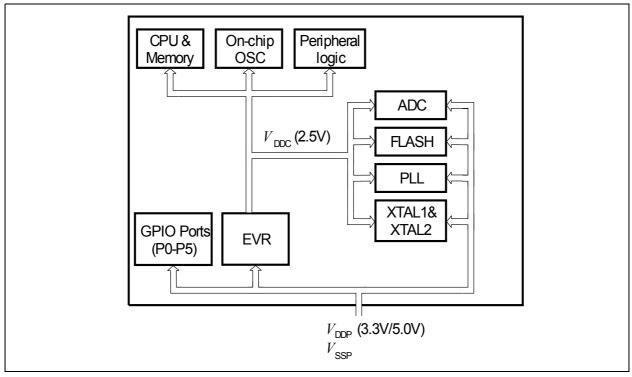

The XC886/888 microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 21** shows the XC886/888 power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

Figure 21 XC886/888 Power Supply System

### **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 3.3 V/5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- · Low power voltage regulator provided in power-down mode

- $V_{\text{DDC}}$  and  $V_{\text{DDP}}$  prewarning detection

- $V_{\text{DDC}}$  brownout detection

- 1) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 2) OSC is bypassed in MultiCAN BSL mode

- 3) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

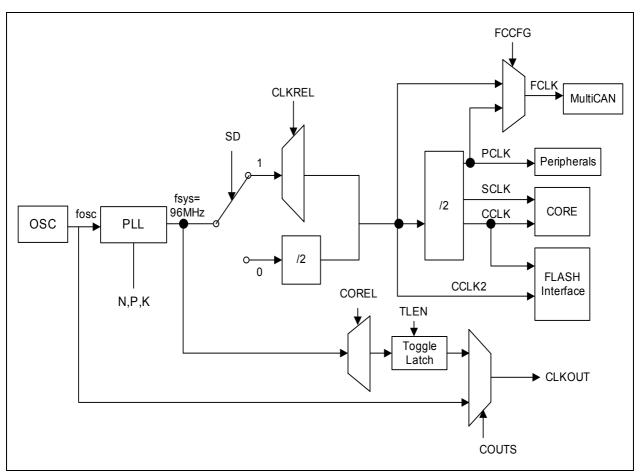

## 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC886/888. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### Features

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support

The CGU consists of an oscillator circuit and a PLL. In the XC886/888, the oscillator can be from either of these two sources: the on-chip oscillator (9.6 MHz) or the external oscillator (4 MHz to 12 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

### 3.8.2 Clock Management

The CGU generates all clock signals required within the microcontroller from a single clock,  $f_{sys}$ . During normal system operation, the typical frequencies of the different modules are as follow:

- CPU clock: CCLK, SCLK = 24 MHz

- Fast clock (used by MultiCAN): FCLK = 24 or 48 MHz

- Peripheral clock: PCLK = 24 MHz

- Flash Interface clock: CCLK2 = 48 MHz and CCLK = 24 MHz

In addition, different clock frequencies can be output to pin CLKOUT (P0.0 or P0.7). The clock output frequency, which is derived from the clock output divider (bit COREL), can further be divided by 2 using toggle latch (bit TLEN is set to 1). The resulting output frequency has a 50% duty cycle. **Figure 26** shows the clock distribution of the XC886/888.

Figure 26 Clock Generation from  $f_{sys}$

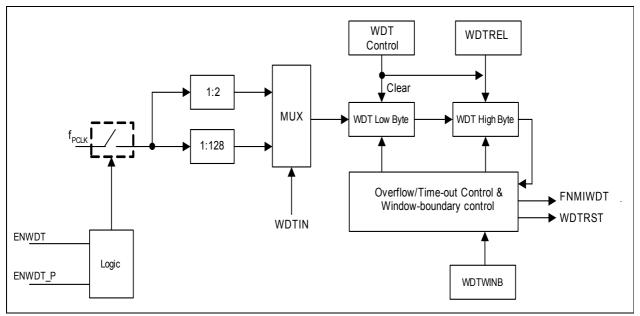

## 3.10 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failures. The WDT is reset at a regular interval that is predefined by the user. The CPU must service the WDT within this interval to prevent the WDT from causing an XC886/888 system reset. Hence, routine service of the WDT confirms that the system is functioning properly. This ensures that an accidental malfunction of the XC886/888 will be aborted in a user-specified time period.

In debug mode, the WDT is default suspended and stops counting. Therefore, there is no need to refresh the WDT during debugging.

#### Features

- 16-bit Watchdog Timer

- Programmable reload value for upper 8 bits of timer

- Programmable window boundary

- Selectable input frequency of  $f_{PCLK}/2$  or  $f_{PCLK}/128$

- Time-out detection with NMI generation and reset prewarning activation (after which a system reset will be performed)

The WDT is a 16-bit timer incremented by a count rate of  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$ . This 16-bit timer is realized as two concatenated 8-bit timers. The upper 8 bits of the WDT can be preset to a user-programmable value via a watchdog service access in order to modify the watchdog expire time period. The lower 8 bits are reset on each service access. **Figure 28** shows the block diagram of the WDT unit.

Figure 28 WDT Block Diagram

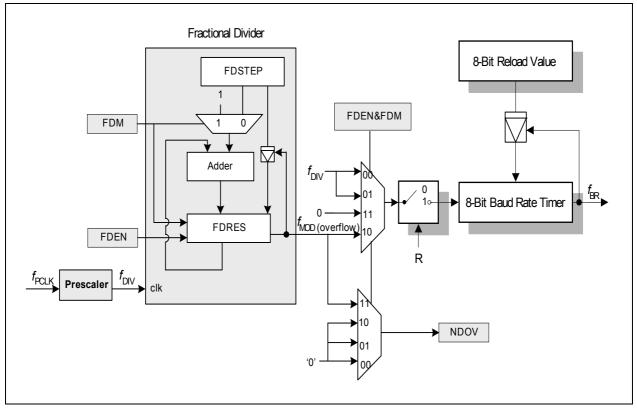

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 30**.

#### Figure 30 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

### XC886/888CLM

### **Functional Description**

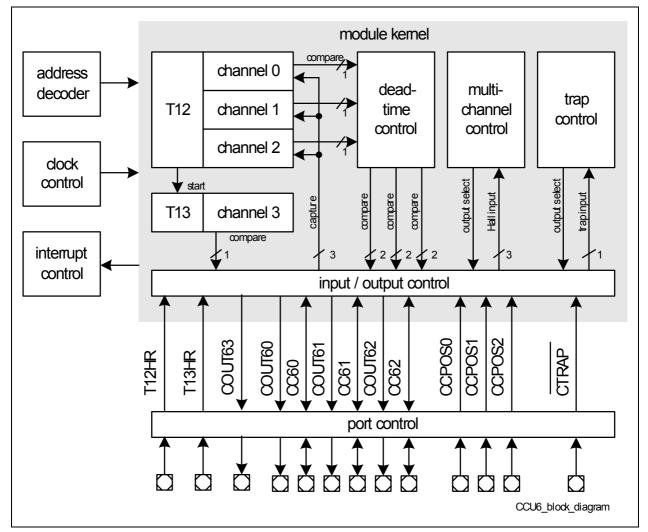

Figure 33 CCU6 Block Diagram

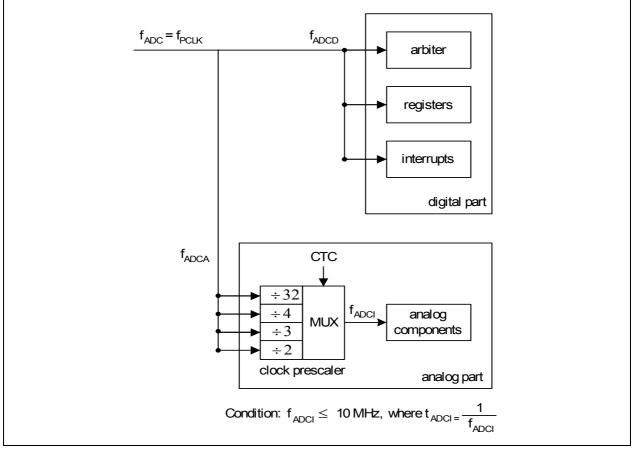

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

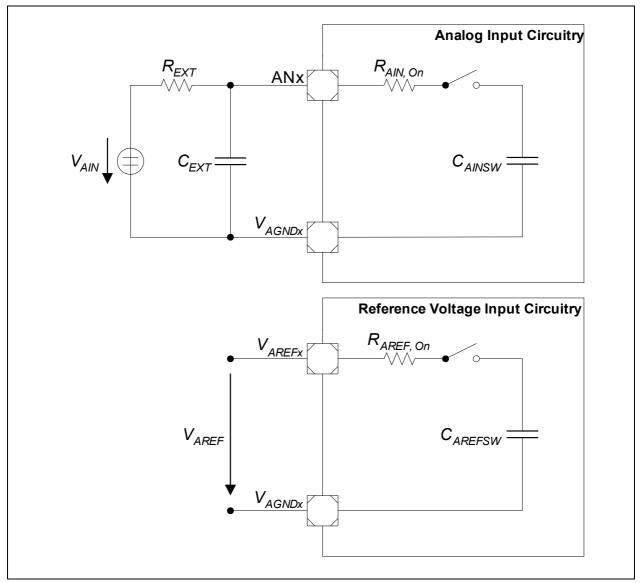

#### Table 40ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

|                                                              |                     |    |      | -       |                           | -    |                         |

|--------------------------------------------------------------|---------------------|----|------|---------|---------------------------|------|-------------------------|

| Parameter                                                    | Symbol              |    | Liı  | mit Val | ues                       | Unit | Test Conditions/        |

|                                                              |                     |    | min. | typ .   | max.                      |      | Remarks                 |

| Overload current coupling factor for                         | K <sub>OVD</sub>    | CC | -    | -       | 5.0 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV} > 0^{1)3)$  |

| digital I/O pins                                             |                     |    | -    | -       | 1.0 x<br>10 <sup>-2</sup> | -    | $I_{\rm OV} < 0^{1)3)}$ |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>AREFSW</sub> | CC | _    | 10      | 20                        | pF   | 1)4)                    |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub>  | CC | _    | 5       | 7                         | pF   | 1)5)                    |

| Input resistance of the reference input                      | R <sub>AREF</sub>   | CC | -    | 1       | 2                         | kΩ   | 1)                      |

| Input resistance of<br>the selected analog<br>channel        | R <sub>AIN</sub>    | CC | _    | 1       | 1.5                       | kΩ   | 1)                      |

1) Not subjected to production test, verified by design/characterization

2) TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V,  $V_{DDP}$  = 5.0 V.

- 3) An overload current  $(I_{OV})$  through a pin injects a certain error current  $(I_{INJ})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{OZ})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ1}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

Figure 39 ADC Input Circuits

# 4.3.4 On-Chip Oscillator Characteristics

Table 47 provides the characteristics of the on-chip oscillator in the XC886/888.

| Table 47 | On-chip Oscillator Characteristics (Operating Conditions apply) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter                      | Symbol           |    | Limit Values |      |      | Unit | Test Conditions                                                                                                                    |  |

|--------------------------------|------------------|----|--------------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                                |                  |    | min.         | typ. | max. |      |                                                                                                                                    |  |

| Nominal frequency              | f <sub>nom</sub> | CC | 9.36         | 9.6  | 9.84 | MHz  | under nominal conditions <sup>1)</sup>                                                                                             |  |

| Long term frequency deviation  | Δf <sub>LT</sub> | CC | -5.0         | -    | 5.0  | %    | with respect to $f_{\text{NOM}}$ , over<br>lifetime and temperature<br>(-10°C to 125°C), for one<br>given device after<br>trimming |  |

|                                |                  |    | -6.0         | -    | 0    | %    | with respect to $f_{NOM}$ , over<br>lifetime and temperature<br>(-40°C to<br>-10°C), for one given<br>device after trimming        |  |

| Short term frequency deviation | $\Delta f_{ST}$  | CC | -1.0         | -    | 1.0  | %    | within one LIN message<br>(<10 ms 100 ms)                                                                                          |  |

1) Nominal condition:  $V_{\text{DDC}}$  = 2.5 V,  $T_{\text{A}}$  = + 25°C.

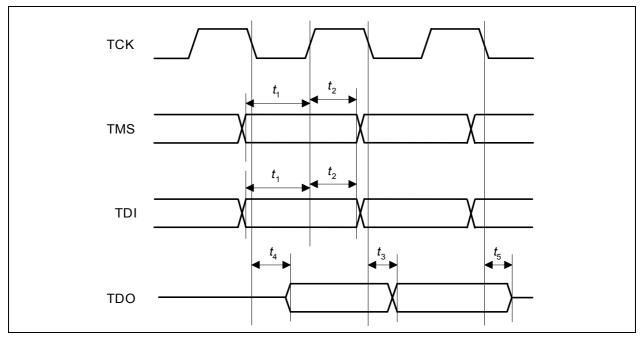

| Table 50JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |                       |    |        |     |      |                           |  |  |

|-----------------------------------------------------------------------|-----------------------|----|--------|-----|------|---------------------------|--|--|

| Parameter                                                             | Symbol                |    | Limits |     | Unit | Test                      |  |  |

|                                                                       |                       |    | min    | max |      | Conditions                |  |  |

| TDO high impedance to valid                                           | <i>t</i> <sub>4</sub> | CC | -      | 27  | ns   | 5V Device <sup>1)</sup>   |  |  |

| output from TCK                                                       |                       |    | -      | 36  | ns   | 3.3V Device <sup>1)</sup> |  |  |

| TDO valid output to high                                              | $t_5$                 | CC | -      | 22  | ns   | 5V Device <sup>1)</sup>   |  |  |

| impedance from TCK                                                    |                       |    | -      | 28  | ns   | 3.3V Device <sup>1)</sup> |  |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

#### Package and Quality Declaration

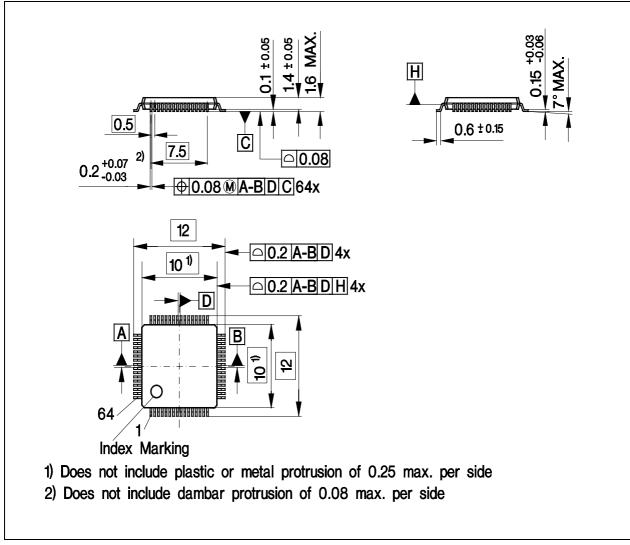

### Figure 49 PG-TQFP-64 Package Outline

www.infineon.com

Published by Infineon Technologies AG