Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                    |

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | LINbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 34                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-48                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc886lm8ffi5vacfxuma1 |

# XC886/888CLM

|                                           | Table of Content                                                                            | ts             |

|-------------------------------------------|---------------------------------------------------------------------------------------------|----------------|

| 4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7 | Power-on Reset and PLL Timing                                                               | 28<br>29<br>30 |

| <b>5</b><br>5.1<br>5.2<br>5.3             | Package and Quality Declaration13Package Parameters13Package Outline13Quality Declaration13 | 33<br>34       |

### **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                       |                                                                                                                                            |

|--------|----------------------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose an be used as alternate functions i, CCU6, UART, Timer 0, Timer 1, ler 21, MultiCAN and SSC.           |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                |

| P1.1   | 27/35                      |      | PU             | EXINT3 T0_1 TDO_1 TXD_0  TXDC0_0               | External Interrupt Input 3 Timer 0 Input JTAG Serial Data Output UART Transmit Data Output/Clock Output MultiCAN Node 0 Transmitter Output |

| P1.2   | 28/36                      |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                     |

| P1.3   | 29/37                      |      | PU             | MTSR_0 TXDC1_3                                 | SSC Master Transmit Output/Slave Receive Input MultiCAN Node 1 Transmitter Output                                                          |

| P1.4   | 30/38                      |      | PU             | MRST_0 EXINT0_1 RXDC1_3                        | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                         |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0 External Interrupt Input 5 Timer 1 Input Timer 2 External Flag Output UART Transmit Data Output                          |

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                                                                                          |                                                                        |  |  |  |  |

|--------|----------------------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| P5     |                            | I/O  |                | Port 5 Port 5 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for UART, UART1 and JTAG. |                                                                        |  |  |  |  |

| P5.0   | <b>-/8</b>                 |      | PU             | EXINT1_1                                                                                                                          | External Interrupt Input 1                                             |  |  |  |  |

| P5.1   | <b>-</b> /9                |      | PU             | EXINT2_1                                                                                                                          | External Interrupt Input 2                                             |  |  |  |  |

| P5.2   | <b>-/12</b>                |      | PU             | RXD_2                                                                                                                             | UART Receive Data Input                                                |  |  |  |  |

| P5.3   | <b>-</b> /13               |      | PU             | TXD_2                                                                                                                             | UART Transmit Data Output/Clock Output                                 |  |  |  |  |

| P5.4   | <b>-/14</b>                |      | PU             | RXDO_2                                                                                                                            | UART Transmit Data Output                                              |  |  |  |  |

| P5.5   | <b>-/15</b>                |      | PU             | TDO_2<br>TXD1_2                                                                                                                   | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output |  |  |  |  |

| P5.6   | <del>-</del> /19           |      | PU             | TCK_2<br>RXDO1_2                                                                                                                  | JTAG Clock Input<br>UART1 Transmit Data Output                         |  |  |  |  |

| P5.7   | <b>-/20</b>                |      | PU             | TDI_2<br>RXD1_2                                                                                                                   | JTAG Serial Data Input<br>UART1 Receive Data Input                     |  |  |  |  |

Data Sheet 17 V1.2, 2009-07

Table 4 Flash Protection Modes (cont'd)

| Flash Protection                      | Without hardware protection             | With hardware protection                                                                                |                                                    |  |  |  |  |  |

|---------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| P-Flash program and erase             | Possible                                | Not possible                                                                                            | Not possible                                       |  |  |  |  |  |

| D-Flash<br>contents can be<br>read by | Read instructions in any program memory | Read instructions in any program memory                                                                 | Read instructions in<br>the P-Flash or D-<br>Flash |  |  |  |  |  |

| External access to D-Flash            | Not possible                            | Not possible                                                                                            | Not possible                                       |  |  |  |  |  |

| D-Flash<br>program                    | Possible                                | Possible                                                                                                | Not possible                                       |  |  |  |  |  |

| D-Flash erase                         | Possible                                | Possible, on condition that bit DFLASHEN in register MISC_CON is set to 1 prior to each erase operation | Not possible                                       |  |  |  |  |  |

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. The Flash protection is then disabled upon the next reset.

For the ROM device, the ROM is protected at all times and BSL mode 6 is used only to block external access to the device. However, unlike the Flash device, it is not possible to disable the memory protection of the ROM device. Here, entering BSL mode 6 will result in a protection error.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

Although no protection scheme can be considered infallible, the XC886/888 memory protection strategy provides a very high level of protection for a general purpose microcontroller.

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | W    | <ul> <li>Operation</li> <li>0X Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>10 New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> <li>11 Automatic restore page action. The value written to the bit positions PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | Reserved Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_B$ , writing  $10011_B$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_B$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_H$  or  $A8_H$ . It can only be changed when bit field PASS is written with  $11000_B$ , for example, writing  $D0_H$  to PASSWD register disables the bit protection scheme.

Note that access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include the N- and K-Divider bits, NDIV and KDIV; the Watchdog Timer enable bit, WDTEN; and the power-down and slow-down enable bits, PD and SD.

# Table 8 SCU Register Overview (cont'd)

| Addr            | Register Name                                                  | Bit       | 7                  | 6           | 5            | 4           | 3            | 2             | 1           | 0           |  |

|-----------------|----------------------------------------------------------------|-----------|--------------------|-------------|--------------|-------------|--------------|---------------|-------------|-------------|--|

| всн             | NMISR Reset: 00 <sub>H</sub><br>NMI Status Register            | Bit Field | 0                  | FNMI<br>ECC | FNMI<br>VDDP | FNMI<br>VDD | FNMI<br>OCDS | FNMI<br>FLASH | FNMI<br>PLL | FNMI<br>WDT |  |

|                 |                                                                | Туре      | r                  | rwh         | rwh          | rwh         | rwh          | rwh           | rwh         | rwh         |  |

| BDH             | BCON Reset: 00 <sub>H</sub>                                    | Bit Field | BGSEL 0 BRDIS      |             |              | BRPRE       |              |               | R           |             |  |

|                 | Baud Rate Control Register                                     | Туре      | r                  | W           | r            | rw          |              | rw            |             | rw          |  |

| BE <sub>H</sub> | BG Reset: 00 <sub>H</sub>                                      | Bit Field |                    |             |              |             |              |               |             |             |  |

|                 | Baud Rate Timer/Reload<br>Register                             | Туре      |                    |             |              | rv          | vh           |               |             |             |  |

| E9 <sub>H</sub> | FDCON Reset: 00 <sub>H</sub> Fractional Divider Control        | Bit Field | BGS                | SYNE<br>N   | ERRS<br>YN   | EOFS<br>YN  | BRK          | NDOV          | FDEN        |             |  |

|                 | Register                                                       | Туре      | rw                 | rw          | rwh          | rwh         | rwh          | rwh           | rw          | rw          |  |

| EA <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                  | Bit Field |                    |             |              | ST          | ΈP           |               |             |             |  |

|                 | Fractional Divider Reload<br>Register                          | Туре      |                    |             |              | r           | w            |               |             |             |  |

| EB <sub>H</sub> | FDRES Reset: 00 <sub>H</sub>                                   | Bit Field |                    |             |              | RES         | SULT         |               |             |             |  |

|                 | Fractional Divider Result Register                             | Туре      |                    |             |              | r           | h            |               |             |             |  |

| RMAP =          | 0, PAGE 1                                                      | I .       |                    |             |              |             |              |               |             |             |  |

| вз <sub>Н</sub> | ID Reset: UU <sub>H</sub>                                      | Bit Field | PRODID             |             |              |             | VERID        |               |             |             |  |

|                 | Identity Register                                              | Туре      |                    |             | r            |             |              |               | r           |             |  |

| B4 <sub>H</sub> | PMCON0 Reset: 00 <sub>H</sub><br>Power Mode Control Register 0 | Bit Field | 0                  | WDT<br>RST  | WKRS         | WK<br>SEL   | SD           | PD WS         |             | WS          |  |

|                 |                                                                | Туре      | r                  | rwh         | rwh          | rw          | rw           | rwh           | rw          |             |  |

| В5 <sub>Н</sub> | PMCON1 Reset: 00 <sub>H</sub><br>Power Mode Control Register 1 | Bit Field | 0                  | CDC_<br>DIS | CAN_<br>DIS  | MDU_<br>DIS | T2_<br>DIS   | CCU_<br>DIS   | SSC_<br>DIS | ADC_<br>DIS |  |

|                 |                                                                | Туре      | r                  | rw          | rw           | rw          | rw           | rw            | rw          | rw          |  |

| B6 <sub>H</sub> | OSC_CON Reset: 08 <sub>H</sub> OSC Control Register            | Bit Field |                    | 0           |              | OSC<br>PD   | XPD          | OSC<br>SS     | ORD<br>RES  | OSCR        |  |

|                 |                                                                | Туре      |                    | r           |              | rw          | rw           | rw            | rwh         | rh          |  |

| B7 <sub>H</sub> | PLL_CON Reset: 90 <sub>H</sub> PLL Control Register            | Bit Field |                    | NE          | OIV          |             | VCO<br>BYP   | OSC<br>DISC   | RESL<br>D   | LOCK        |  |

|                 |                                                                | Туре      |                    | r           | w            |             | rw           | rw            | rwh         | rh          |  |

| <sup>BA</sup> H | CMCON Reset: 10 <sub>H</sub><br>Clock Control Register         | Bit Field | VCO<br>SEL         | KDIV        | 0            | FCCF<br>G   |              | CLK           | REL         |             |  |

|                 |                                                                | Туре      | rw                 | rw          | r            | rw          |              | r             | W           |             |  |

| BB <sub>H</sub> | PASSWD Reset: 07 <sub>H</sub><br>Password Register             | Bit Field | d PASS PROT MO     |             |              |             |              | DE            |             |             |  |

|                 |                                                                | Туре      | wh rh rw           |             |              |             |              | w             |             |             |  |

| всн             | FEAL Reset: 00 <sub>H</sub> Flash Error Address Register       | Bit Field | t Field ECCERRADDR |             |              |             |              |               |             |             |  |

|                 | Low                                                            | Туре      |                    |             |              | r           | h            |               |             |             |  |

| вDН             | FEAH Reset: 00 <sub>H</sub>                                    | Bit Field |                    |             |              | ECCER       | RADDR        |               |             |             |  |

|                 | Flash Error Address Register High                              | Туре      |                    |             |              | r           | h            |               |             |             |  |

Table 9 WDT Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------|------------------------------|-----------|-----|-----|---|---|---|---|---|---|--|--|

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>  | Bit Field |     | WDT |   |   |   |   |   |   |  |  |

|                 | Watchdog Timer Register Low  | Туре      | rh  |     |   |   |   |   |   |   |  |  |

| BF <sub>H</sub> | WDTH Reset: 00 <sub>H</sub>  | Bit Field | WDT |     |   |   |   |   |   |   |  |  |

|                 | Watchdog Timer Register High | Туре      |     |     |   | r | h |   |   |   |  |  |

# 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

Table 10 Port Register Overview

| Addr            | Register Name                  | Bit       | 7  | 6  | 5    | 4  | 3  | 2    | 1  | 0  |

|-----------------|--------------------------------|-----------|----|----|------|----|----|------|----|----|

| RMAP =          | = 0                            |           |    | •  | •    |    | •  |      |    |    |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00H           | Bit Field | C  | )P | STNR |    | 0  | PAGE |    |    |

|                 | Page Register                  | Туре      | \  | N  | V    | V  | r  | rw   |    |    |

| RMAP =          | = 0, PAGE 0                    |           |    |    |      |    |    |      |    |    |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P0 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P0 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P1 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| 91 <sub>H</sub> | P1_DIR Reset: 00H              | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P1 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P5 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| 93 <sub>H</sub> | P5_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P5 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| A0 <sub>H</sub> | P2_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P2 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| A1 <sub>H</sub> | P2_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P2 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P3 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| В1 <sub>Н</sub> | P3_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P3 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| C8H             | P4_DATA Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P4 Data Register               | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

| C9 <sub>H</sub> | P4_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7 | P6 | P5   | P4 | P3 | P2   | P1 | P0 |

|                 | P4 Direction Register          | Туре      | rw | rw | rw   | rw | rw | rw   | rw | rw |

Table 11

ADC Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7           | 6          | 5    | 4                   | 3    | 2    | 1       | 0    |

|-----------------|-----------------------------------------------------------|-----------|-------------|------------|------|---------------------|------|------|---------|------|

| CDH             | ADC_LCBR Reset: B7H                                       | Bit Field |             | BOL        | JND1 |                     |      | BOL  | JND0    |      |

|                 | Limit Check Boundary Register                             | Туре      |             | r          | W    |                     |      | r    | w       |      |

| CEH             | ADC_INPCR0 Reset: 00H                                     | Bit Field |             |            |      | S.                  | ТС   |      |         |      |

|                 | Input Class 0 Register                                    | Туре      |             |            |      | r                   | W    |      |         |      |

| CF <sub>H</sub> | ADC_ETRCR Reset: 00 <sub>H</sub> External Trigger Control | Bit Field | SYNE<br>N1  | SYNE<br>N0 |      | ETRSEL <sup>2</sup> | l    |      | ETRSELO |      |

|                 | Register                                                  | Туре      | rw          | rw         |      | rw                  |      |      | rw      |      |

| RMAP =          | = 0, PAGE 1                                               |           |             |            |      |                     |      |      |         |      |

| CA <sub>H</sub> | ADC_CHCTR0 Reset: 00H                                     | Bit Field | 0           |            | LCC  |                     | (    | 0    | RESI    | RSEL |

|                 | Channel Control Register 0                                | Туре      | r           |            | rw   |                     |      | r    | r       | N    |

| СВН             | ADC_CHCTR1 Reset: 00H                                     | Bit Field | 0           |            | LCC  |                     |      | 0    | RESI    | RSEL |

|                 | Channel Control Register 1                                | Туре      | r           |            | rw   |                     |      | r    | r       | N    |

| сс <sub>Н</sub> | ADC_CHCTR2 Reset: 00H                                     | Bit Field | 0           |            | LCC  |                     | (    | 0    | RESI    | RSEL |

|                 | Channel Control Register 2                                | Туре      | r           |            | rw   |                     |      | r    | r       | N    |

| CDH             | ADC_CHCTR3 Reset: 00H                                     | Bit Field | 0           |            | LCC  |                     | (    | 0    | RESI    | RSEL |

|                 | Channel Control Register 3                                | Туре      | r           |            | rw   |                     |      | r    | r       | N    |

| CEH             | ADC_CHCTR4 Reset: 00H                                     | Bit Field | 0           | 0 LCC      |      |                     | 0    |      | RESRSEL |      |

|                 | Channel Control Register 4                                | Туре      | r rw        |            |      | r                   | r    | N    |         |      |

| CF <sub>H</sub> | ADC_CHCTR5 Reset: 00H                                     | Bit Field | 0           | 0 LCC      |      |                     | 0    | RESI | RSEL    |      |

|                 | Channel Control Register 5                                | Туре      | r           | r rw       |      |                     | r    | r    | N       |      |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 00H                                     | Bit Field | 0           | LCC        |      | (                   | 0    | RESI | RSEL    |      |

|                 | Channel Control Register 6                                | Туре      | r           |            | rw   |                     | r    |      | rw      |      |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 00H                                     | Bit Field | 0           |            | LCC  |                     | 0    |      | RESRSEL |      |

|                 | Channel Control Register 7                                | Туре      | r           |            | rw   |                     |      | r    | rw      |      |

| RMAP =          | = 0, PAGE 2                                               |           |             |            |      |                     |      |      |         |      |

| CA <sub>H</sub> | ADC_RESR0L Reset: 00H                                     | Bit Field | RES         | SULT       | 0    | VF                  | DRC  |      | CHNR    |      |

|                 | Result Register 0 Low                                     | Туре      | r           | h          | r    | rh                  | rh   |      | rh      |      |

| СВН             | ADC_RESR0H Reset: 00H                                     | Bit Field |             |            |      | RES                 | SULT |      |         |      |

|                 | Result Register 0 High                                    | Туре      |             |            |      | r                   | h    |      |         |      |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00H                                     | Bit Field | RES         | SULT       | 0    | VF                  | DRC  |      | CHNR    |      |

|                 | Result Register 1 Low                                     | Туре      | r           | h          | r    | rh                  | rh   |      | rh      |      |

| CDH             | ADC_RESR1H Reset: 00H                                     | Bit Field |             |            |      | RES                 | SULT |      |         |      |

|                 | Result Register 1 High                                    | Туре      |             |            |      | r                   | h .  |      |         |      |

| CEH             | ADC_RESR2L Reset: 00H                                     | Bit Field | RESULT 0 VF |            |      | VF                  | DRC  |      | CHNR    |      |

|                 | Result Register 2 Low                                     | Туре      | r           | h .        | r    | rh                  | rh   |      | rh      |      |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00H                                     | Bit Field |             |            |      | RES                 | SULT |      |         |      |

|                 | Result Register 2 High                                    | Туре      |             |            |      | r                   | h    |      |         |      |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00H                                     | Bit Field | RES         | SULT       | 0    | VF                  | DRC  |      | CHNR    |      |

|                 | Result Register 3 Low                                     | Туре      | r           | h          | r    | rh                  | rh   |      | rh      |      |

# 3.2.4.8 Timer 2 Registers

The Timer 2 SFRs can be accessed in the standard memory area (RMAP = 0).

Table 12 T2 Register Overview

| Addr            | Register Name                                            | Bit       | 7          | 6          | 5           | 4    | 3   | 2         | 1    | 0          |  |

|-----------------|----------------------------------------------------------|-----------|------------|------------|-------------|------|-----|-----------|------|------------|--|

| RMAP =          | = 0                                                      |           |            |            | •           |      |     |           |      |            |  |

| C0H             | T2_T2CON Reset: 00 <sub>H</sub> Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | 0    |     | TR2       | C/T2 | CP/<br>RL2 |  |

|                 |                                                          | Туре      | rwh        | rwh        | 1           | r    | rw  | rw rwh rw |      | rw         |  |

| C1 <sub>H</sub> | T2_T2MOD Reset: 00 <sub>H</sub> Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN |     | T2PRE     |      | DCEN       |  |

|                 |                                                          | Туре      | rw         | rw         | rw          | rw   | rw  | rw        | rw   | rw         |  |

| C2 <sub>H</sub> | T2_RC2L Reset: 00H                                       | Bit Field |            |            |             | R    | C2  |           |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register Low                   | Туре      | rwh        |            |             |      |     |           |      |            |  |

| C3 <sub>H</sub> | T2_RC2H Reset: 00H                                       | Bit Field | RC2        |            |             |      |     |           |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register High                  | Туре      | rwh        |            |             |      |     |           |      |            |  |

| C4 <sub>H</sub> | T2_T2L Reset: 00H                                        | Bit Field |            |            |             | TH   | IL2 |           |      |            |  |

|                 | Timer 2 Register Low                                     | Туре      | rwh        |            |             |      |     |           |      |            |  |

| C5 <sub>H</sub> | T2_T2H Reset: 00 <sub>H</sub>                            | Bit Field |            |            |             | T⊦   | IL2 |           |      |            |  |

|                 | Timer 2 Register High                                    | Туре      |            |            |             | rv   | /h  |           |      |            |  |

# 3.2.4.9 Timer 21 Registers

The Timer 21 SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 13 T21 Register Overview

| Addr            | Register Name                                             | Bit       | 7          | 6          | 5           | 4    | 3     | 2   | 1    | 0          |  |

|-----------------|-----------------------------------------------------------|-----------|------------|------------|-------------|------|-------|-----|------|------------|--|

| RMAP =          | = 1                                                       |           |            |            |             |      |       |     |      |            |  |

| C0H             | T21_T2CON Reset: 00 <sub>H</sub> Timer 2 Control Register | Bit Field | TF2        | EXF2       | (           | 0    |       | TR2 | C/T2 | CP/<br>RL2 |  |

|                 |                                                           | Туре      | rwh        | rwh        | ı           | r    | rw    | rwh | rw   | rw         |  |

| C1 <sub>H</sub> | T21_T2MOD Reset: 00 <sub>H</sub> Timer 2 Mode Register    | Bit Field | T2RE<br>GS | T2RH<br>EN | EDGE<br>SEL | PREN | T2PRE |     | DCEN |            |  |

|                 |                                                           | Туре      | rw         | rw         | rw          | rw   | rw    | rw  | rw   | rw         |  |

| C2 <sub>H</sub> | T21_RC2L Reset: 00H                                       | Bit Field | RC2        |            |             |      |       |     |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register Low                    | Туре      | rwh        |            |             |      |       |     |      |            |  |

| C3 <sub>H</sub> | T21_RC2H Reset: 00H                                       | Bit Field |            |            |             | R    | C2    |     |      |            |  |

|                 | Timer 2 Reload/Capture<br>Register High                   | Туре      | rwh        |            |             |      |       |     |      |            |  |

| C4 <sub>H</sub> | T21_T2L Reset: 00 <sub>H</sub>                            | Bit Field | THL2       |            |             |      |       |     |      |            |  |

|                 | Timer 2 Register Low                                      | Туре      |            |            |             | rv   | vh    |     |      |            |  |

**Table 19** shows the Flash data retention and endurance targets.

Table 19 Flash Data Retention and Endurance (Operating Conditions apply)

| Retention     | Endurance <sup>1)</sup> | Size                          | Remarks              |

|---------------|-------------------------|-------------------------------|----------------------|

| Program Flash |                         |                               |                      |

| 20 years      | 1,000 cycles            | up to 32 Kbytes <sup>2)</sup> | for 32-Kbyte Variant |

| 20 years      | 1,000 cycles            | up to 24 Kbytes <sup>2)</sup> | for 24-Kbyte Variant |

| Data Flash    |                         |                               |                      |

| 20 years      | 1,000 cycles            | 4 Kbytes                      |                      |

| 5 years       | 10,000 cycles           | 1 Kbyte                       |                      |

| 2 years       | 70,000 cycles           | 512 bytes                     |                      |

| 2 years       | 100,000 cycles          | 128 bytes                     |                      |

<sup>1)</sup> One cycle refers to the programming of all wordlines in a sector and erasing of sector. The Flash endurance data specified in **Table 19** is valid only if the following conditions are fulfilled:

- the maximum number of erase cycles per Flash sector must not exceed 100,000 cycles.

- the maximum number of erase cycles per Flash bank must not exceed 300,000 cycles.

- the maximum number of program cycles per Flash bank must not exceed 2,500,000 cycles.

- 2) If no Flash is used for data, the Program Flash size can be up to the maximum Flash size available in the device variant. Having more Data Flash will mean less Flash is available for Program Flash.

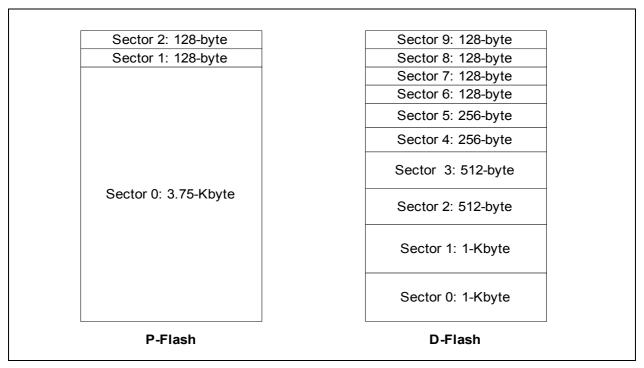

#### 3.3.1 Flash Bank Sectorization

The XC886/888 product family offers Flash devices with either 24 Kbytes or 32 Kbytes of embedded Flash memory. Each Flash device consists of Program Flash (P-Flash) and Data Flash (D-Flash) bank(s) with different sectorization shown in **Figure 11**. Both types can be used for code and data storage. The label "Data" neither implies that the D-Flash is mapped to the data memory region, nor that it can only be used for data storage. It is used to distinguish the different Flash bank sectorizations.

The 32-Kbyte Flash device consists of 6 P-Flash and 2 D-Flash banks, while the 24-Kbyte Flash device consists of also of 6 P-Flash banks but with the upper 2 banks only 2 Kbytes each, and only 1 D-Flash bank. The XC886/888 ROM devices offer a single 4-Kbyte D-Flash bank.

The P-Flash banks are always grouped in pairs. As such, the P-Flash banks are also sometimes referred to as P-Flash bank pair. Each sector in a P-Flash bank is grouped with the corresponding sector from the other bank within a bank pair to form a P-Flash bank pair sector.

Data Sheet 53 V1.2, 2009-07

Figure 11 Flash Bank Sectorization

The internal structure of each Flash bank represents a sector architecture for flexible erase capability. The minimum erase width is always a complete sector, and sectors can be erased separately or in parallel. Contrary to standard EPROMs, erased Flash memory cells contain 0s.

The D-Flash bank is divided into more physical sectors for extended erasing and reprogramming capability; even numbers for each sector size are provided to allow greater flexibility and the ability to adapt to a wide range of application requirements.

#### 3.3.2 Parallel Read Access of P-Flash

To enhance system performance, the P-Flash banks are configured for parallel read to allow two bytes of linear code to be read in 4 x CCLK cycles, compared to 6 x CCLK cycles if serial read is performed. This is achieved by reading two bytes in parallel from a P-Flash bank pair within the 3 x CCLK cycles access time and storing them in a cache. Subsequent read from the cache by the CPU does not require a wait state and can be completed within 1 x CCLK cycle. The result is the average instruction fetch time from the P-Flash banks is reduced and thus, the MIPS (Mega Instruction Per Second) of the system is increased.

However, if the parallel read feature is not desired due to certain timing constraints, it can be disabled by calling the parallel read disable subroutine.

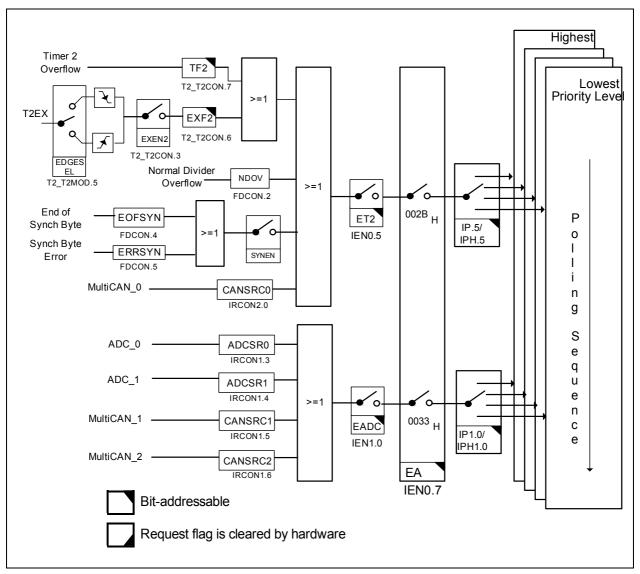

Figure 15 Interrupt Request Sources (Part 2)

Table 20 Interrupt Vector Addresses (cont'd)

| Interrupt<br>Source | Vector<br>Address                      | Assignment for XC886/888                           | Enable Bit | SFR  |  |

|---------------------|----------------------------------------|----------------------------------------------------|------------|------|--|

| XINTR6              | 0033 <sub>H</sub>                      | MultiCAN Nodes 1 and 2                             | EADC       | IEN1 |  |

|                     |                                        | ADC[1:0]                                           | 1          |      |  |

| XINTR7              | 003B <sub>H</sub>                      | SSC                                                | ESSC       |      |  |

| XINTR8              | 0043 <sub>H</sub>                      | External Interrupt 2                               | EX2        |      |  |

|                     |                                        | T21                                                |            |      |  |

|                     |                                        | CORDIC                                             |            |      |  |

|                     |                                        | UART1                                              |            |      |  |

|                     |                                        | UART1 Fractional Divider (Normal Divider Overflow) |            |      |  |

|                     |                                        | MDU[1:0]                                           | 1          |      |  |

| XINTR9              | 004B <sub>H</sub>                      | External Interrupt 3                               | EXM        |      |  |

|                     |                                        | External Interrupt 4                               |            |      |  |

|                     |                                        | External Interrupt 5                               |            |      |  |

|                     |                                        | External Interrupt 6                               |            |      |  |

|                     |                                        | MultiCAN Node 3                                    |            |      |  |

| XINTR10             | 0053 <sub>H</sub>                      | CCU6 INP0                                          | ECCIP0     |      |  |

|                     |                                        | MultiCAN Node 4                                    |            |      |  |

| XINTR11             | R11 005B <sub>H</sub> CCU6 INP1 ECCIP1 |                                                    | ECCIP1     |      |  |

|                     |                                        | MultiCAN Node 5                                    |            |      |  |

| XINTR12             | 0063 <sub>H</sub>                      | CCU6 INP2                                          | ECCIP2     |      |  |

|                     |                                        | MultiCAN Node 6                                    |            |      |  |

| XINTR13             | 006B <sub>H</sub>                      | CCU6 INP3                                          | ECCIP3     |      |  |

|                     |                                        | MultiCAN Node 7                                    |            |      |  |

### 3.4.3 Interrupt Priority

An interrupt that is currently being serviced can only be interrupted by a higher-priority interrupt, but not by another interrupt of the same or lower priority. Hence, an interrupt of the highest priority cannot be interrupted by any other interrupt request.

If two or more requests of different priority levels are received simultaneously, the request of the highest priority is serviced first. If requests of the same priority are received simultaneously, then an internal polling sequence determines which request is serviced first. Thus, within each priority level, there is a second priority structure determined by the polling sequence shown in **Table 21**.

Table 21 Priority Structure within Interrupt Level

| Source                                                                                      | Level     |

|---------------------------------------------------------------------------------------------|-----------|

| Non-Maskable Interrupt (NMI)                                                                | (highest) |

| External Interrupt 0                                                                        | 1         |

| Timer 0 Interrupt                                                                           | 2         |

| External Interrupt 1                                                                        | 3         |

| Timer 1 Interrupt                                                                           | 4         |

| UART Interrupt                                                                              | 5         |

| Timer 2,UART Normal Divider Overflow,<br>MultiCAN, LIN Interrupt                            | 6         |

| ADC, MultiCAN Interrupt                                                                     | 7         |

| SSC Interrupt                                                                               | 8         |

| External Interrupt 2, Timer 21, UART1, UART1 Normal Divider Overflow, MDU, CORDIC Interrupt | 9         |

| External Interrupt [6:3], MultiCAN Interrupt                                                | 10        |

| CCU6 Interrupt Node Pointer 0, MultiCAN interrupt                                           | 11        |

| CCU6 Interrupt Node Pointer 1, MultiCAN Interrupt                                           | 12        |

| CCU6 Interrupt Node Pointer 2, MultiCAN Interrupt                                           | 13        |

| CCU6 Interrupt Node Pointer 3, MultiCAN Interrupt                                           | 14        |

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

Table 26 System frequency ( $f_{sys} = 96 \text{ MHz}$ )

| Power Saving Mode | Action                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| Idle              | Clock to the CPU is disabled.                                                                                            |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |

Data Sheet 78 V1.2, 2009-07

### 3.22 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- Use the built-in debug functionality of the XC800 Core

- Add a minimum of hardware overhead

- Provide support for most of the operations by a Monitor Program

- Use standard interfaces to communicate with the Host (a Debugger)

#### **Features**

- Set breakpoints on instruction address and on address range within the Program Memory

- Set breakpoints on internal RAM address range

- Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks via JTAG and upon activating a dedicated pin

- Step through the program code

The OCDS functional blocks are shown in **Figure 37**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals.

After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack).

The OCDS system is accessed through the JTAG<sup>1)</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after XC886/888 has been started in OCDS mode.

<sup>1)</sup> The pins of the JTAG port can be assigned to either the primary port (Port 0) or either of the secondary ports (Ports 1 and 2/Port 5).

User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

### **Electrical Parameters**

Table 40 ADC Characteristics (Operating Conditions apply;  $V_{\text{DDP}}$  = 5V Range)

| Parameter                                             | Symbol           |    | Limit Values |      |                           | Unit | Test Conditions/        |

|-------------------------------------------------------|------------------|----|--------------|------|---------------------------|------|-------------------------|

|                                                       |                  |    | min.         | typ. | max.                      |      | Remarks                 |

| Overload current coupling factor for digital I/O pins | $K_{OVD}$        | CC | _            | _    | 5.0 x<br>10 <sup>-3</sup> | _    | $I_{\rm OV} > 0^{1)3)}$ |

|                                                       |                  |    | _            | _    | 1.0 x<br>10 <sup>-2</sup> | _    | $I_{\rm OV} < 0^{1)3)}$ |

| Switched capacitance at the reference voltage input   | $C_{AREFSW}$     | CC | _            | 10   | 20                        | pF   | 1)4)                    |

| Switched capacitance at the analog voltage inputs     | $C_{AINSW}$      | CC | _            | 5    | 7                         | pF   | 1)5)                    |

| Input resistance of the reference input               | $R_{AREF}$       | CC | _            | 1    | 2                         | kΩ   | 1)                      |

| Input resistance of the selected analog channel       | R <sub>AIN</sub> | CC | _            | 1    | 1.5                       | kΩ   | 1)                      |

- 1) Not subjected to production test, verified by design/characterization

- 2) TUE is tested at  $V_{\rm AREF}$  = 5.0 V,  $V_{\rm AGND}$  = 0 V,  $V_{\rm DDP}$  = 5.0 V.

- 3) An overload current  $(I_{\text{OV}})$  through a pin injects a certain error current  $(I_{\text{INJ}})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{\text{OZ}})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{\text{OV}}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{\text{TOT}}| = |I_{\text{OZ1}}| + (|I_{\text{OV}}| \times K_{\text{OV}})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{\mathsf{AREF}}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{\mathsf{AREF}}/2$ .

Data Sheet 117 V1.2, 2009-07

#### **Electrical Parameters**

Table 43 Power Supply Current Parameters (Operating Conditions apply;  $V_{\text{DDP}} = 3.3 \text{V range}$ )

| Parameter                     | Symbol    | Limit  | Values             | Unit | <b>Test Condition</b>      |

|-------------------------------|-----------|--------|--------------------|------|----------------------------|

|                               |           | typ.1) | max. <sup>2)</sup> |      |                            |

| $V_{\text{DDP}}$ = 3.3V Range | <u> </u>  |        |                    |      |                            |

| Active Mode                   | $I_{DDP}$ | 25.6   | 31.0               | mA   | Flash Device <sup>3)</sup> |

|                               |           | 23.4   | 28.6               | mA   | ROM Device <sup>3)</sup>   |

| Idle Mode                     | $I_{DDP}$ | 19.9   | 24.7               | mA   | Flash Device <sup>4)</sup> |

|                               |           | 17.5   | 20.7               | mA   | ROM Device <sup>4)</sup>   |

| Active Mode with slow-down    | $I_{DDP}$ | 13.3   | 16.2               | mA   | Flash Device <sup>5)</sup> |

| enabled                       |           | 11.5   | 13.7               | mA   | ROM Device <sup>5)</sup>   |

| Idle Mode with slow-down      | $I_{DDP}$ | 11.1   | 14.4               | mA   | Flash Device <sup>6)</sup> |

| enabled                       |           | 9.3    | 11.4               | mA   | ROM Device <sup>6)</sup>   |

- 1) The typical  $I_{\rm DDP}$  values are periodically measured at  $T_{\rm A}$  = + 25 °C and  $V_{\rm DDP}$  = 3.3 V.

- 2) The maximum  $I_{\rm DDP}$  values are measured under worst case conditions ( $T_{\rm A}$  = + 125 °C and  $V_{\rm DDP}$  = 3.6 V).

- 3)  $I_{\text{DDP}}$  (active mode) is measured with: CPU clock and input clock to all peripherals running at 24 MHz(set by on-chip oscillator of 9.6 MHz and NDIV in PLL\_CON to 1001<sub>B</sub>),  $\overline{\text{RESET}} = V_{\text{DDP}}$ , no load on ports.

- 4)  $I_{\text{DDP}}$  (idle mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 24 MHz,  $\overline{\text{RESET}} = V_{\text{DDP}}$ , no load on ports.

- 5)  $I_{\text{DDP}}$  (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 8 MHz by setting CLKREL in CMCON to 0110<sub>B</sub>,  $\overline{\text{RESET}}$  =  $V_{\text{DDP}}$ , no load on ports.

- 6)  $I_{\rm DDP}$  (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 8 MHz by setting CLKREL in CMCON to 0110<sub>B</sub>,, RESET =  $V_{\rm DDP}$ , no load on ports.

Data Sheet 122 V1.2, 2009-07

### **Electrical Parameters**

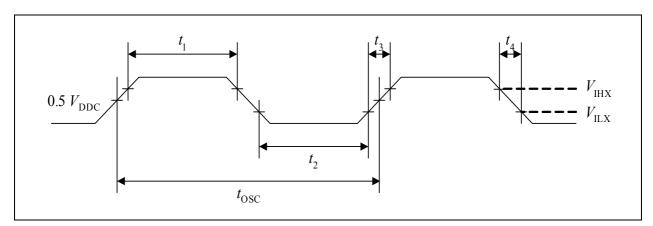

### 4.3.5 External Clock Drive XTAL1

**Table 48** shows the parameters that define the external clock supply for XC886/888. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

Table 48 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter         | Symbol        |    | Limit Values |      | Unit | Test Conditions |

|-------------------|---------------|----|--------------|------|------|-----------------|

|                   |               |    | Min.         | Max. |      |                 |

| Oscillator period | $t_{\rm osc}$ | SR | 83.3         | 250  | ns   | 1)2)            |

| High time         | $t_1$         | SR | 25           | -    | ns   | 2)3)            |

| Low time          | $t_2$         | SR | 25           | -    | ns   | 2)3)            |

| Rise time         | $t_3$         | SR | -            | 20   | ns   | 2)3)            |

| Fall time         | $t_4$         | SR | -            | 20   | ns   | 2)3)            |

- 1) The clock input signals with 45-55% duty cycle are used.

- 2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

- 3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 45 External Clock Drive XTAL1

## **Package and Quality Declaration**

# 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

**Table 2** Quality Parameters

| Parameter                                                       | Symbol    | Limit V | 'alues | Unit | Notes                                                |

|-----------------------------------------------------------------|-----------|---------|--------|------|------------------------------------------------------|

|                                                                 |           | Min.    | Max.   |      |                                                      |

| ESD susceptibility according to Human Body Model (HBM)          | $V_{HBM}$ | -       | 2000   | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility according to Charged Device Model (CDM) pins | $V_{CDM}$ | -       | 500    | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

<sup>1)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Data Sheet 136 V1.2, 2009-07