Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Discontinued at Digi-Key                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 24MHz                                                                          |

| Connectivity               | SSI, UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 48                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1.75K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | PG-TQFP-64                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc8888ffi5vacfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 8-Bit

# XC886/888CLM

8-Bit Single Chip Microcontroller

Data Sheet V1.2 2009-07

### Microcontrollers

#### **General Device Information**

### 2.4 Pin Definitions and Functions

The functions and default states of the XC886/888 external pins are provided in Table 3.

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                                   |                                                                                                                                                                                                      |

|--------|----------------------------|------|----------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                            | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, UART1, Timer 2,<br>ultiCAN and SSC.                                                                       |

| P0.0   | 11/17                      |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1           | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input<br>Input/Output of<br>Capture/Compare channel 1<br>Clock Output<br>UART Transmit Data Output                                                 |

| P0.1   | 13/21                      |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1 | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |

| P0.2   | 12/18                      |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                       | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |

| P0.3   | 48/63                      |      | Hi-Z           | SCK_1<br>COUT63_1<br>RXDO1_0                               | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3<br>UART1 Transmit Data Output                                                                                                       |

Table 3

Pin Definitions and Functions

| Addr            | Register Name                                                     | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0         |

|-----------------|-------------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|-----------|

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                       | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0       |

|                 | Interrupt Enable Register 0                                       | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                         | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0       |

|                 | Interrupt Priority Register                                       | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                        | Bit Field | (           | )           | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H      |

|                 | Interrupt Priority High Register                                  | Туре      |             | r           | rw          | rw          | rw   | rw   | rw        | rw        |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                        | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р         |

|                 | Program Status Word Register                                      | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh        |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub>                                        | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0      |

|                 | Accumulator Register                                              | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub><br>Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                          | Bit Field | B7          | B6          | B5          | B4          | B3   | B2   | B1        | B0        |

|                 | B Register                                                        | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F8 <sub>H</sub> | IP1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 Register       | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC      |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub><br>Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H |

|                 |                                                                   | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw        |

#### Table 5CPU Register Overview (cont'd)

#### 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 6MDU Register Overview

| Addr            | Register Name                                         | Bit       | 7  | 6  | 5    | 4         | 3  | 2   | 1    | 0    |

|-----------------|-------------------------------------------------------|-----------|----|----|------|-----------|----|-----|------|------|

| RMAP =          | = 1                                                   | •         |    | •  | •    | •         | •  | •   | •    |      |

| в0 <sub>Н</sub> | MDUSTAT Reset: 00 <sub>H</sub>                        | Bit Field |    |    | 0    |           |    | BSY | IERR | IRDY |

|                 | MDU Status Register                                   | Туре      |    |    | r    |           |    | rh  | rwh  | rwh  |

| в1 <sub>Н</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field | IE | IR | RSEL | STAR<br>T |    | OPC | ODE  |      |

|                 |                                                       | Туре      | rw | rw | rw   | rwh       |    | r   | w    |      |

| B2 <sub>H</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA |     |      |      |

|                 | MDU Operand Register 0                                | Туре      |    |    |      | r         | W  |     |      |      |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA |     |      |      |

|                 | MDU Result Register 0                                 | Туре      |    |    |      | r         | h  |     |      |      |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA |     |      |      |

|                 | MDU Operand Register 1                                | Туре      |    |    |      | r         | W  |     |      |      |

#### Table 7CORDIC Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7         | 6         | 5           | 4           | 3          | 2   | 1         | 0   |

|-----------------|-----------------------------------------------------------|-----------|-----------|-----------|-------------|-------------|------------|-----|-----------|-----|

| A0 <sub>H</sub> | CD_STATC Reset: 00 <sub>H</sub><br>CORDIC Status and Data | Bit Field | KEEP<br>Z | KEEP<br>Y | KEEP<br>X   | DMAP        | INT_E<br>N | EOC | ERRO<br>R | BSY |

|                 | Control Register                                          | Туре      | rw        | rw        | rw          | rw          | rw         | rwh | rh        | rh  |

| А1 <sub>Н</sub> | CD_CON Reset: 00 <sub>H</sub><br>CORDIC Control Register  | Bit Field | MI        | PS        | X_USI<br>GN | ST_M<br>ODE | ROTV<br>EC | MC  | DE        | ST  |

|                 |                                                           | Туре      | r         | N         | rw          | rw          | rw         | r   | v         | rwh |

#### 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

#### Addr Bit 7 3 2 1 **Register Name** 6 5 4 0 RMAP = 0 or 1 IMOD 8F<sub>H</sub> SYSCON0 Reset: 04<sub>H</sub> Bit Field 0 0 1 0 RMAP System Control Register 0 F r r r r rw Туре rw RMAP = 0 SCU\_PAGE STNR PAGE BFH Reset: 00<sub>H</sub> Bit Field OP 0 Page Register Туре w w r rw RMAP = 0, PAGE 0 Reset: 00<sub>H</sub> Bit Field URRIS JTAGT JTAGT EXINT EXINT EXINT URRIS MODPISEL 0 B3<sub>H</sub> Peripheral Input Select Register Н DIS CKS 2IS 1IS 0IS rw Туре r rw rw rw rw rw rw Reset: 00<sub>H</sub> B4<sub>H</sub> **IRCON0** Bit Field 0 **EXINT** EXINT EXINT EXINT EXINT EXINT EXINT Interrupt Request Register 0 4 3 0 6 5 2 1 rwh Туре r rwh rwh rwh rwh rwh rwh Reset: 00<sub>H</sub> в5<sub>Н</sub> CANS **IRCON1** Bit Field 0 CANS ADCS ADCS RIR TIR EIR Interrupt Request Register 1 RC2 RC1 R0 R1 Туре r rwh rwh rwh rwh rwh rwh rwh B6<sub>H</sub> Reset: 00<sub>H</sub> 0 CANS 0 CANS **IRCON2** Bit Field Interrupt Request Register 2 RC3 RC0 Туре rwh rwh r r B7<sub>H</sub> EXICON0 EXINT3 EXINT2 EXINT1 EXINT0 Reset: F0µ Bit Field External Interrupt Control Туре rw rw rw rw Register 0 Reset: 3F<sub>H</sub> BAH EXICON1 Bit Field 0 EXINT6 EXINT5 EXINT4 External Interrupt Control rw rw rw Туре r Register 1 ввн NMICON Reset: 00<sub>H</sub> Bit Field 0 NMI NMI NMI NMI NMI NMI NMI NMI Control Register ECC VDDP VDD OCDS FLASH PLL WDT Туре r rw rw rw rw rw rw rw

#### Table 8SCU Register Overview

#### Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|-----------------|-----------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00 <sub>H</sub>                                     | Bit Field |            |            |            | RES        | ESULT      |            |            |            |  |

|                 | Result Register 3 High                                                | Туре      |            |            |            | r          | 'n         |            |            |            |  |

| RMAP =          | 0, PAGE 3                                                             |           |            |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 0, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |  |

| св <sub>Н</sub> | ADC_RESRA0H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 0, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |  |

| сс <sub>Н</sub> | ADC_RESRA1L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 1, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |  |

| CD <sub>H</sub> | ADC_RESRA1H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 1, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |  |

| Ce <sub>H</sub> | ADC_RESRA2L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 2, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |  |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | SULT       |            |            |            |  |

|                 | Result Register 2, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |  |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00 <sub>H</sub>                                    | Bit Field |            | RESULT     |            | VF         | DRC        |            | CHNR       |            |  |

|                 | Result Register 3, View A Low                                         | Туре      |            | rh         |            | rh         | rh         |            | rh         |            |  |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00 <sub>H</sub>                                    | Bit Field |            |            |            | RES        | ULT        |            |            |            |  |

|                 | Result Register 3, View A High                                        | Туре      |            |            |            | r          | h          |            |            |            |  |

| RMAP =          | = 0, PAGE 4                                                           |           |            |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub><br>Result Control Register 0          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |  |

| св <sub>Н</sub> | ADC_RCR1 Reset: 00 <sub>H</sub><br>Result Control Register 1          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |  |

| сс <sup>н</sup> | ADC_RCR2 Reset: 00 <sub>H</sub><br>Result Control Register 2          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |  |

| CDH             | ADC_RCR3 Reset: 00 <sub>H</sub><br>Result Control Register 3          | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |  |

|                 |                                                                       | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |  |

| Ce <sub>H</sub> | ADC_VFCR Reset: 00 <sub>H</sub>                                       | Bit Field |            |            | ט          |            | VFC3       | VFC2       | VFC1       | VFC0       |  |

|                 | Valid Flag Clear Register                                             | Туре      |            |            | r          |            | w          | w          | w          | w          |  |

| RMAP =          | = 0, PAGE 5                                                           |           |            |            |            |            |            |            |            |            |  |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register  | Bit Field | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |  |

|                 |                                                                       | Туре      | rh         |  |

| св <sub>Н</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register | Bit Field | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |  |

|                 |                                                                       | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |  |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                             | Bit               | 7          | 6           | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|---------------------------------------------------------------------------|-------------------|------------|-------------|------------|------------|------------|------------|------------|------------|

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub>                                        | Bit Field         |            |             | 0          | 1          | T13F       | RSEL       | T12F       | RSEL       |

|                 | Timer Control Register 2 High                                             | Туре              |            |             | r          |            | r          | w          | r          | w          |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub><br>Modulation Control Register Low    | Bit Field         | MCM<br>EN  | 0           |            |            | T12M       | ODEN       |            |            |

|                 |                                                                           | Туре              | rw         | r           |            |            | r          | w          |            |            |

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub><br>Modulation Control Register High   | Bit Field         | ECT1<br>30 | 0           |            |            | T13M       | ODEN       |            |            |

|                 |                                                                           | Туре              | rw         | r           |            |            | r          | w          |            |            |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub><br>Trap Control Register Low          | Bit Field         |            |             | 0          |            |            | TRPM<br>2  | TRPM<br>1  | TRPM<br>0  |

|                 |                                                                           | Туре              |            |             | r          |            |            | rw         | rw         | rw         |

| FFH             | CCU6_TRPCTRH Reset: 00 <sub>H</sub><br>Trap Control Register High         | Bit Field         | TRPP<br>EN | TRPE<br>N13 |            |            | TRI        | PEN        |            |            |

|                 |                                                                           | Туре              | rw         | rw          |            |            | r          | W          |            |            |

|                 | = 0, PAGE 3                                                               | 1                 |            |             | -          |            |            |            |            |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field         | 0          | R           |            |            | MC         | MP         |            |            |

|                 | Low                                                                       | Туре              | r          | rh          |            |            | r          | h          |            |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Register | Bit Field         | (          | 0           |            | CURH       |            |            | EXPH       |            |

|                 | High                                                                      | Туре              |            | r           |            | rh         |            |            | rh         |            |

| 9CH             | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field         | T12<br>PM  | T12<br>OM   | ICC62<br>F | ICC62<br>R | ICC61<br>F | ICC61<br>R | ICC60<br>F | ICC60<br>R |

|                 | Register Low                                                              | Туре              | rh         | rh          | rh         | rh         | rh         | rh         | rh         | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status       | Bit Field         | STR        | IDLE        | WHE        | CHE        | TRPS       | TRPF       | T13<br>PM  | T13<br>CM  |

|                 | Register High                                                             | Туре              | rh         | rh          | rh         | rh         | rh         | rh         | rh         | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub><br>Port Input Select Register 0 Low   | Bit Field         | IST        | RP          | ISC        | C62        | ISC        | C61        | ISC        | C60        |

|                 |                                                                           | Туре              | r          | w           | r          | W          | r          | W          | r          | W          |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High  | Bit Field         | IST1       | 2HR         | ISP        | OS2        | ISP        | OS1        | ISP        | OS0        |

|                 |                                                                           | Туре              | r          | W           | r          | W          | r          | W          |            | W          |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub><br>Port Input Select Register 2        | Bit Field         |            |             |            | 0          |            |            | IST1       | 3HR        |

|                 |                                                                           | Туре              |            |             |            | r          |            |            | r          | W          |

| FA <sub>H</sub> | CCU6_T12L Reset: 00 <sub>H</sub><br>Timer T12 Counter Register Low        | Bit Field         |            |             |            |            | CVL        |            |            |            |

|                 |                                                                           | Туре              |            |             |            |            | vh         |            |            |            |

| FB <sub>H</sub> | CCU6_T12HReset: 00HTimer T12 Counter Register High                        | Bit Field         |            |             |            |            | CVH        |            |            |            |

| EC.             | CCU6 T13L Reset: 00u                                                      | Type<br>Bit Field |            |             |            |            | wh         |            |            |            |

| FC <sub>H</sub> | CCU6_T13LReset: 00HTimer T13 Counter Register Low                         | Bit Field         |            |             |            |            |            |            |            |            |

| ED              | CCU6 T13H Reset: 00µ                                                      | Type<br>Bit Field |            |             |            |            | vh<br>CVH  |            |            |            |

| FD <sub>H</sub> | CCU6_T13HReset: 00HTimer T13 Counter Register High                        |                   |            |             |            |            |            |            |            |            |

|                 |                                                                           | Туре              |            |             |            | íV         | vh         |            |            |            |

#### XC886/888CLM

#### **Functional Description**

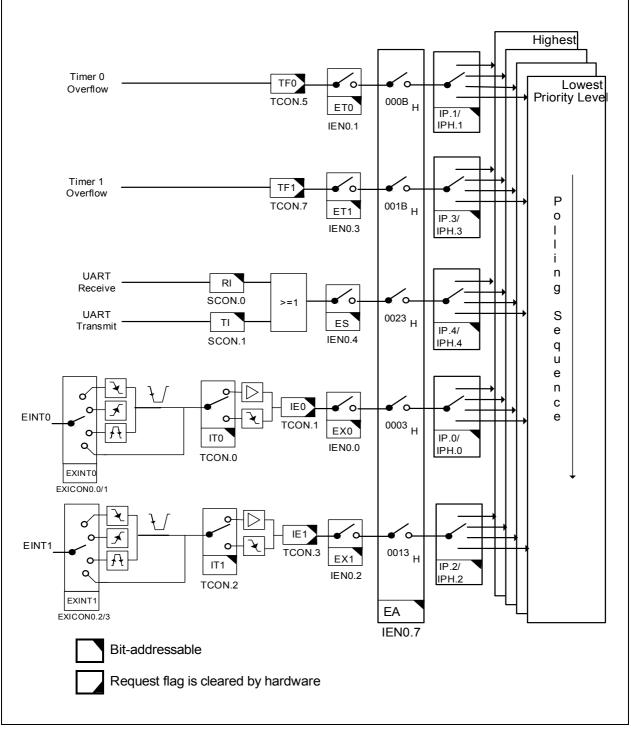

Figure 14 Interrupt Request Sources (Part 1)

#### 3.5 Parallel Ports

The XC886 has 34 port pins organized into five parallel ports, Port 0 (P0) to Port 4 (P4), while the XC888 has 48 port pins organized into six parallel ports, Port 0 (P0) to Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. Ports P0, P1, P3, P4 and P5 are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected. Port P2 is an input-only port, providing general purpose input functions, alternate input functions for the on-chip peripherals. Converter (ADC).

#### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

#### **Input Port Features**

- Configurable input driver

- Configurable pull-up/pull-down devices

- Receive of data through digital input (general purpose input)

- Alternate input for on-chip peripherals

- Analog input for ADC module

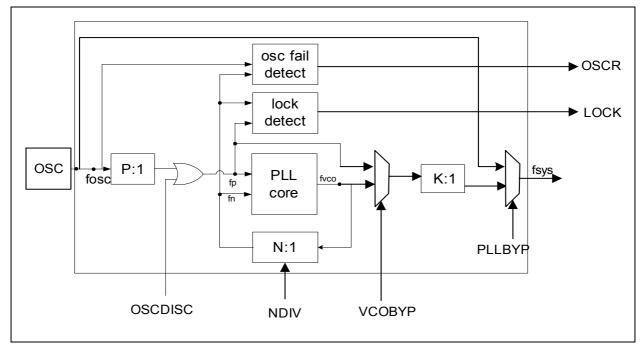

#### Figure 24 CGU Block Diagram

#### **PLL Base Mode**

When the oscillator is disconnected from the PLL, the system clock is derived from the VCO base (free running) frequency clock (**Table 25**) divided by the K factor.

$$f_{SYS} = f_{VCObase} \times \frac{1}{K}$$

(3.1)

#### Prescaler Mode (VCO Bypass Operation)

In VCO bypass operation, the system clock is derived from the oscillator clock, divided by the P and K factors.

$$f_{SYS} = f_{OSC} \times \frac{1}{P \times K}$$

(3.2)

- Interrupt enabling and corresponding flag

#### 3.13 UART and UART1

The XC886/888 provides two Universal Asynchronous Receiver/Transmitter (UART and UART1) modules for full-duplex asynchronous reception/transmission. Both are also receive-buffered, i.e., they can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

#### Features

- Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- Fixed or variable baud rate

- Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART modules can operate in the four modes shown in **Table 29**.

| f <sub>PCLK</sub> /2                               |

|----------------------------------------------------|

| Variable                                           |

| $f_{\rm PCLK}/32 \text{ or } f_{\rm PCLK}/64^{1)}$ |

| Variable                                           |

|                                                    |

#### Table 29UART Modes

1) For UART1 module, the baud rate is fixed at  $f_{PCLK}/64$ .

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{\rm PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{\rm PCLK}/32$  or  $f_{\rm PCLK}/64$ . For UART1 module, only  $f_{\rm PCLK}/64$  is available. The variable baud rate is set by the underflow rate on the dedicated baud-rate generator. For UART module, the variable baud rate alternatively can be set by the overflow rate on Timer 1.

#### 3.13.1 Baud-Rate Generator

Both UART modules have their own dedicated baud-rate generator, which is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

STEP 2: Wait for an incoming LIN frame from host

STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

#### 3.18 Timer 2 and Timer 21

Timer 2 and Timer 21 are 16-bit general purpose timers (THL2) that are fully compatible and have two modes of operation, a 16-bit auto-reload mode and a 16-bit one channel capture mode, see **Table 33**. As a timer, the timers count with an input clock of PCLK/12 (if prescaler is disabled). As a counter, they count 1-to-0 transitions on pin T2. In the counter mode, the maximum resolution for the count is PCLK/24 (if prescaler is disabled).

| Table 33           | Timer 2 Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Auto-reload        | <ul> <li>Up/Down Count Disabled</li> <li>Count up only</li> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event configurable for trigger by overflow condition only, or by negative/positive edge at input pin T2EX as well</li> <li>Programmble reload value in register RC2</li> <li>Interrupt is generated with reload event</li> </ul>                                                                                                                                                                                                                                                                                                |

|                    | <ul> <li>Up/Down Count Enabled</li> <li>Count up or down, direction determined by level at input pin T2EX</li> <li>No interrupt is generated</li> <li>Count up <ul> <li>Start counting from 16-bit reload value, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Programmble reload value in register RC2</li> </ul> </li> <li>Count down <ul> <li>Start counting from FFFF<sub>H</sub>, underflow at value defined in register RC2</li> <li>Reload event triggered by underflow condition <ul> <li>Reload event triggered by underflow condition</li> <li>Reload event triggered by underflow condition</li> </ul> </li> </ul></li></ul> |

| Channel<br>capture | <ul> <li>Count up only</li> <li>Start counting from 0000<sub>H</sub>, overflow at FFFF<sub>H</sub></li> <li>Reload event triggered by overflow condition</li> <li>Reload value fixed at 0000<sub>H</sub></li> <li>Capture event triggered by falling/rising edge at pin T2EX</li> <li>Captured timer value stored in register RC2</li> <li>Interrupt is generated with reload or capture event</li> </ul>                                                                                                                                                                                                                                                                             |

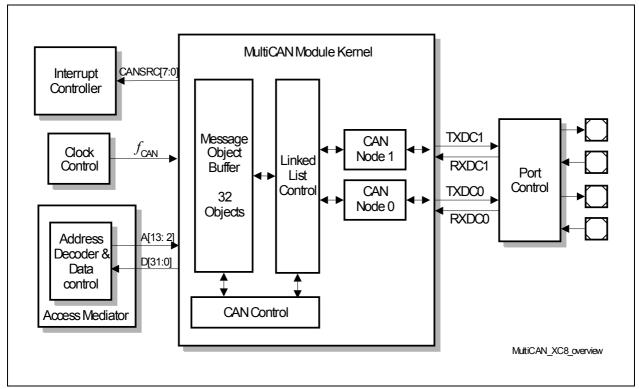

#### 3.20 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 34 Overview of the MultiCAN

#### Features

Compliant to ISO 11898.

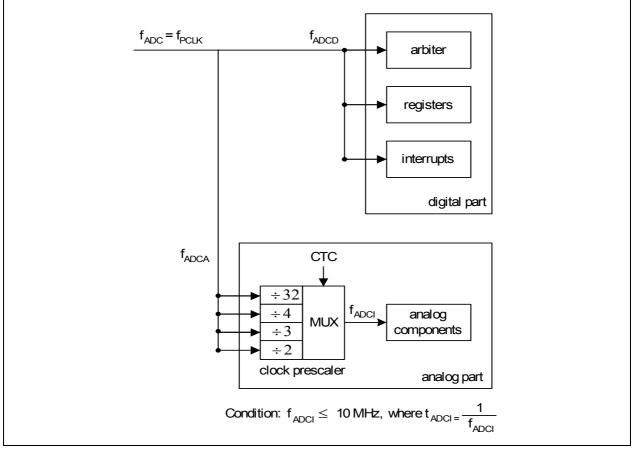

GLOBCTR. A prescaling ratio of 32 can be selected when the maximum performance of the ADC is not required.

#### Figure 35 ADC Clocking Scheme

For module clock  $f_{ADC}$  = 24 MHz, the analog clock  $f_{ADCI}$  frequency can be selected as shown in **Table 34**.

| Table 34 | f <sub>ADCI</sub> Frequency Selection |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Module Clock $f_{ADC}$ | СТС                       | Prescaling Ratio | Analog Clock $f_{ADCI}$ |

|------------------------|---------------------------|------------------|-------------------------|

| 24 MHz                 | 00 <sub>B</sub>           | ÷ 2              | 12 MHz (N.A)            |

|                        | 01 <sub>B</sub>           | ÷ 3              | 8 MHz                   |

|                        | 10 <sub>B</sub>           | ÷ 4              | 6 MHz                   |

|                        | 11 <sub>B</sub> (default) | ÷ 32             | 750 kHz                 |

As  $f_{\rm ADCI}$  cannot exceed 10 MHz, bit field CTC should not be set to  $00_{\rm B}$  when  $f_{\rm ADC}$  is 24 MHz. During slow-down mode where  $f_{\rm ADC}$  may be reduced to 12 MHz, 6 MHz etc., CTC can be set to  $00_{\rm B}$  as long as the divided analog clock  $f_{\rm ADCI}$  does not exceed 10 MHz.

#### Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>H</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>H</sub> | 0B951503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>Н</sub> | 0B951522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>H</sub> | 0B951523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |  |

| ROM Devices       |                            |                       |                       |  |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |

#### **Electrical Parameters**

| Parameter                                                      | Symbol            |    | Limit Values                |                             | Unit | Test Conditions           |  |

|----------------------------------------------------------------|-------------------|----|-----------------------------|-----------------------------|------|---------------------------|--|

|                                                                |                   |    | min.                        | max.                        |      |                           |  |

| Maximum current out of $V_{\rm SS}$                            | I <sub>MVSS</sub> | SR | -                           | 120                         | mA   | 3)                        |  |

| $V_{\text{DDP}}$ = 3.3 V Range                                 |                   |    |                             |                             |      |                           |  |

| Output low voltage                                             | $V_{OL}$          | CC | _                           | 1.0                         | V    | I <sub>OL</sub> = 8 mA    |  |

|                                                                |                   |    | -                           | 0.4                         | V    | I <sub>OL</sub> = 2.5 mA  |  |

| Output high voltage                                            | V <sub>OH</sub>   | CC | V <sub>DDP</sub> -<br>1.0   | -                           | V    | I <sub>OH</sub> = -8 mA   |  |

|                                                                |                   |    | V <sub>DDP</sub> - 0.4      | -                           | V    | I <sub>ОН</sub> = -2.5 mA |  |

| Input low voltage on<br>port pins<br>(all except P0.0 & P0.1)  | V <sub>ILP</sub>  | SR | _                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on P0.0 & P0.1                               | V <sub>ILP0</sub> | SR | -0.2                        | $0.3 \times V_{ m DDP}$     | V    | CMOS Mode                 |  |

| Input low voltage on RESET pin                                 | $V_{ILR}$         | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input low voltage on<br>TMS pin                                | V <sub>ILT</sub>  | SR | -                           | $0.3 \times V_{\text{DDP}}$ | V    | CMOS Mode                 |  |

| Input high voltage on<br>port pins<br>(all except P0.0 & P0.1) | V <sub>IHP</sub>  | SR | $0.7 \times V_{\text{DDP}}$ | -                           | V    | CMOS Mode                 |  |

| Input high voltage on P0.0 & P0.1                              | V <sub>IHP0</sub> | SR | $0.7 \times V_{\text{DDP}}$ | V <sub>DDP</sub>            | V    | CMOS Mode                 |  |

| Input high voltage on RESET pin                                | $V_{IHR}$         | SR | $0.7 \times V_{ m DDP}$     | -                           | V    | CMOS Mode                 |  |

| Input high voltage on<br>TMS pin                               | V <sub>IHT</sub>  | SR | $0.75 \times V_{ m DDP}$    | -                           | V    | CMOS Mode                 |  |

| Input Hysteresis                                               | HYS               | CC | $0.03 \times V_{ m DDP}$    | _                           | V    | CMOS Mode <sup>1)</sup>   |  |

| Input Hysteresis on XTAL1                                      | HYSX              | CC | $0.07 \times V_{ m DDC}$    | -                           | V    | 1)                        |  |

| Input low voltage at XTAL1                                     | V <sub>ILX</sub>  | SR | V <sub>SS</sub> -<br>0.5    | $0.3 \times V_{ m DDC}$     | V    |                           |  |

#### **Electrical Parameters**

#### 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$

#### **Electrical Parameters**

### Table 44Power Down Current (Operating Conditions apply; $V_{DDP} = 3.3V$ <br/>range)

| Parameter                     | Symbol           | Limit Values       |                    | Unit | <b>Test Condition</b>                 |

|-------------------------------|------------------|--------------------|--------------------|------|---------------------------------------|

|                               |                  | typ. <sup>1)</sup> | max. <sup>2)</sup> | 1    |                                       |

| $V_{\text{DDP}}$ = 3.3V Range |                  | ·                  |                    |      |                                       |

| Power-Down Mode               | I <sub>PDP</sub> | 1                  | 10                 | μA   | $T_{\rm A}$ = + 25 °C <sup>3)4)</sup> |

|                               |                  | -                  | 30                 | μA   | $T_{\rm A}$ = + 85 °C <sup>4)5)</sup> |

1) The typical  $I_{PDP}$  values are measured at  $V_{DDP}$  = 3.3 V.

2) The maximum  $I_{\rm PDP}$  values are measured at  $V_{\rm DDP}$  = 3.6 V.

3)  $I_{PDP}$  has a maximum value of 200  $\mu$ A at  $T_A$  = + 125 °C.

4)  $I_{PDP}$  is measured with:  $\overline{RESET} = V_{DDP}$ ,  $V_{AGND} = V_{SS}$ , RXD/INT0 =  $V_{DDP}$ ; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

5) Not subjected to production test, verified by design/characterization.

#### Package and Quality Declaration

#### 5.3 Quality Declaration

Table 2 shows the characteristics of the quality parameters in the XC886/888.

#### Table 2Quality Parameters

| Parameter                                                             | Symbol           | Limit Values |      | Unit | Notes                                                |

|-----------------------------------------------------------------------|------------------|--------------|------|------|------------------------------------------------------|

|                                                                       |                  | Min.         | Max. |      |                                                      |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub> | -            | 2000 | V    | Conforming to<br>EIA/JESD22-<br>A114-B <sup>1)</sup> |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub> | -            | 500  | V    | Conforming to JESD22-C101-C <sup>1)</sup>            |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

www.infineon.com

Published by Infineon Technologies AG