Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                        |

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CANbus, SSI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 48                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.75K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | PG-TQFP-64                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc888c8ffa5vackxuma1 |

#### XC886/888 Data Sheet

Revision History: V1.2 2009-07

| Previous V | ersions: V1.0, V1.1                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------|

| Page       | Subjects (major changes since last revision)                                                                 |

| Changes fr | om V1.1 2009-01 to V1.2 2009-07                                                                              |

| 89         | Note on LIN baud rate detection is added.                                                                    |

| 92         | RXD slave line in SSC block diagram is updated.                                                              |

| 108        | Electrical parameters are now valid for all variants, previous note on exclusion of ROM variants is removed. |

| 116        | Symbol for ADC error parameters are updated.                                                                 |

| 120        | Power supply current parameters for ROM variants are updated.                                                |

| 128        | Test condition for the on-chip oscillator short term deviation is updated.                                   |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

|            |                                                                                                              |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.2, 2009-07

#### **Summary of Features**

Table 2Device Profile (cont'd)

| Sales Type               | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|--------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 3V3 | Flash          | 32                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 3V3 | Flash          | 24                            | 3.3                    | -40 to 85                | Industrial         |

Note: The asterisk (\*) above denotes the device configuration letters from **Table 1**. Corresponding ROM derivatives will be available on request.

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC886/888 throughout this document.

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC886/888, please refer to your responsible sales representative or your local distributor.

Note: The ordering codes for the Mask-ROM versions are defined for each product after verification of the respective ROM code.

Data Sheet 4 V1.2, 2009-07

#### **General Device Information**

## 2.2 Logic Symbol

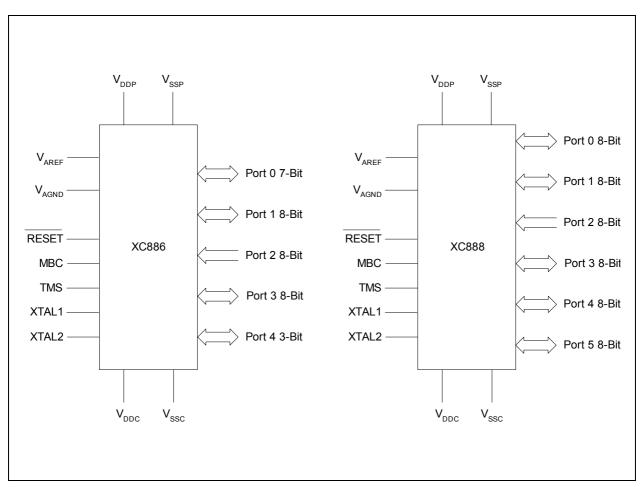

The logic symbols of the XC886/888 are shown in Figure 3.

Figure 3 XC886/888 Logic Symbol

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                |                                                                                                                                                                        |

|--------|----------------------------|------|----------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.4   | 1/64                       |      | Hi-Z           | MTSR_1                                  | SSC Master Transmit Output/<br>Slave Receive Input                                                                                                                     |

|        |                            |      |                | CC62_1                                  | Input/Output of Capture/Compare channel 2                                                                                                                              |

|        |                            |      |                | TXD1_0                                  | UART1 Transmit Data Output/Clock Output                                                                                                                                |

| P0.5   | 2/1                        |      | Hi-Z           | MRST_1 EXINT0_0 T2EX1_1 RXD1_0 COUT62_1 | SSC Master Receive Input/Slave Transmit Output External Interrupt Input 0 Timer 21 External Trigger Input UART1 Receive Data Input Output of Capture/Compare channel 2 |

| P0.6   | <b>-/2</b>                 |      | PU             | GPIO                                    |                                                                                                                                                                        |

| P0.7   | 47/62                      |      | PU             | CLKOUT_1                                | Clock Output                                                                                                                                                           |

Data Sheet 10 V1.2, 2009-07

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                 |                                                                                                                                         |

|--------|----------------------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| P3     |                            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose an be used as alternate functions ART1, Timer 21 and MultiCAN.                                      |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1 Input/Output of Capture/Compare channel 0 UART1 Transmit Data Output                                                  |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0 Input/Output of Capture/Compare channel 1 Output of Capture/Compare channel 0 UART1 Transmit Data Output/Clock Output |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2 MultiCAN Node 1 Receiver Input UART1 Receive Data Input Input/Output of Capture/Compare channel 1                     |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare channel 1 MultiCAN Node 1 Transmitter Output                                                                  |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of Capture/Compare channel 2 MultiCAN Node 0 Receiver Input Timer 21 External Trigger Input                                |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                        |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                         |

## 3 Functional Description

Chapter 3 provides an overview of the XC886/888 functional description.

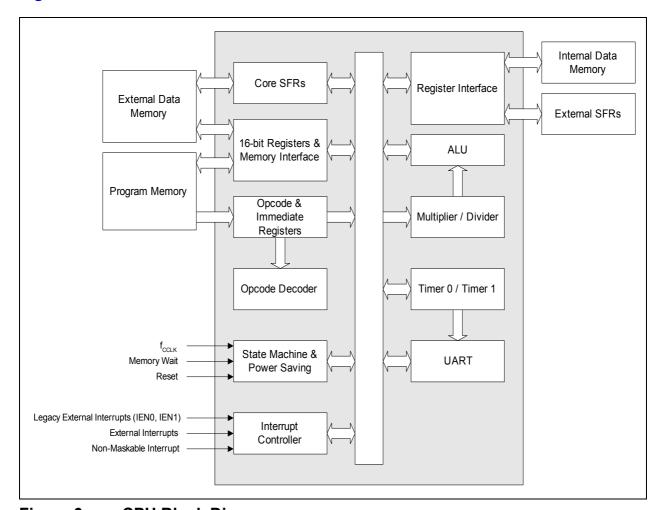

#### 3.1 Processor Architecture

The XC886/888 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC886/888 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The XC886/888 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and Special Function Registers (SFRs).

Figure 6 shows the CPU functional blocks.

Figure 6 CPU Block Diagram

#### 3.2.2 Special Function Register

The Special Function Registers (SFRs) occupy direct internal data memory space in the range  $80_H$  to  $FF_H$ . All registers, except the program counter, reside in the SFR area. The SFRs include pointers and registers that provide an interface between the CPU and the on-chip peripherals. As the 128-SFR range is less than the total number of registers required, address extension mechanisms are required to increase the number of addressable SFRs. The address extension mechanisms include:

- Mapping

- Paging

## 3.2.2.1 Address Extension by Mapping

Address extension is performed at the system level by mapping. The SFR area is extended into two portions: the standard (non-mapped) SFR area and the mapped SFR area. Each portion supports the same address range  $80_{\rm H}$  to FF<sub>H</sub>, bringing the number of addressable SFRs to 256. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit RMAP in the system control register SYSCON0 at address  $8F_{\rm H}$ . To access SFRs in the mapped area, bit RMAP in SFR SYSCON0 must be set. Alternatively, the SFRs in the standard area can be accessed by clearing bit RMAP. The SFR area can be selected as shown in **Figure 8**.

As long as bit RMAP is set, the mapped SFR area can be accessed. This bit is not cleared automatically by hardware. Thus, before standard/mapped registers are accessed, bit RMAP must be cleared/set, respectively, by software.

Data Sheet 23 V1.2, 2009-07

Reset Value: 04 L

#### **Functional Description**

# SYSCON0 System Control Register 0

| 7 | 6 5 |   | 4     | 3 | 2 | 1 | 0    |  |  |

|---|-----|---|-------|---|---|---|------|--|--|

|   | 0   |   | IMODE | 0 | 1 | 0 | RMAP |  |  |

|   | r   | • | r\n/  | r | r | r | r\n/ |  |  |

| Field | Bits          | Type | Description                                                                                                                  |

|-------|---------------|------|------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 0             | rw   | Interrupt Node XINTR0 Enable  O The access to the standard SFR area is enabled  The access to the mapped SFR area is enabled |

| 1     | 2             | r    | Reserved Returns 1 if read; should be written with 1.                                                                        |

| 0     | [7:5],<br>3,1 | r    | Reserved Returns 0 if read; should be written with 0.                                                                        |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions.

## 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC886/888 has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in Figure 9.

Table 7

CORDIC Register Overview (cont'd)

| Addr            | Register Name                                          | Bit       | 7         | 6         | 5         | 4           | 3          | 2    | 1         | 0   |

|-----------------|--------------------------------------------------------|-----------|-----------|-----------|-----------|-------------|------------|------|-----------|-----|

| "               | CD_STATC Reset: 00 <sub>H</sub> CORDIC Status and Data | Bit Field | KEEP<br>Z | KEEP<br>Y | KEEP<br>X | DMAP        | INT_E<br>N | EOC  | ERRO<br>R | BSY |

|                 | Control Register                                       | Туре      | rw        | rw        | rw        | rw          | rw         | rwh  | rh        | rh  |

| A1 <sub>H</sub> | CD_CON Reset: 00 <sub>H</sub> CORDIC Control Register  | Bit Field | MF        | MPS       |           | ST_M<br>ODE | ROTV<br>EC | MODE |           | ST  |

|                 |                                                        | Туре      | rw        |           | rw        | rw          | rw         | rw   |           | rwh |

## 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

Table 8 SCU Register Overview

| Addr            | Register Name                                                       | Bit       | 7   | 6           | 5            | 4            | 3            | 2            | 1            | 0           |

|-----------------|---------------------------------------------------------------------|-----------|-----|-------------|--------------|--------------|--------------|--------------|--------------|-------------|

| RMAP =          | : 0 or 1                                                            | I         |     |             |              |              |              | I            | I            |             |

| <sup>8F</sup> H | SYSCON0 Reset: 04 <sub>H</sub><br>System Control Register 0         | Bit Field |     | 0           |              | IMOD<br>E    | 0            | 1            | 0            | RMAP        |

|                 |                                                                     | Туре      |     | r           |              | rw           | r            | r            | r            | rw          |

| RMAP =          | : 0                                                                 |           |     |             |              |              |              |              |              |             |

| BF <sub>H</sub> | SCU_PAGE Reset: 00H                                                 | Bit Field | C   | )P          | ST           | NR           | 0            |              | PAGE         |             |

|                 | Page Register                                                       | Туре      | ,   | W           | ٧            | V            | r            |              | rw           |             |

| RMAP =          | 0, PAGE 0                                                           |           |     |             |              |              |              |              |              |             |

| вз <sub>Н</sub> | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | 0   | URRIS<br>H  | JTAGT<br>DIS | JTAGT<br>CKS | EXINT<br>2IS | EXINT<br>1IS | EXINT<br>0IS | URRIS       |

|                 |                                                                     | Туре      | r   | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub> Interrupt Request Register 0          | Bit Field | 0   | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2   | EXINT<br>1   | EXINT<br>0  |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в5 <sub>Н</sub> | IRCON1 Reset: 00 <sub>H</sub> Interrupt Request Register 1          | Bit Field | 0   | CANS<br>RC2 | CANS<br>RC1  | ADCS<br>R1   | ADCS<br>R0   | RIR          | TIR          | EIR         |

|                 |                                                                     | Туре      | r   | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в6 <sub>Н</sub> | IRCON2 Reset: 00 <sub>H</sub> Interrupt Request Register 2          | Bit Field |     | 0           |              | CANS<br>RC3  | = -          |              |              | CANS<br>RC0 |

|                 |                                                                     | Туре      |     | r           |              | rwh          |              | r            |              | rwh         |

| в7 <sub>Н</sub> | EXICON0 Reset: F0H                                                  | Bit Field | EXI | NT3         | EXI          | NT2          | EXI          | NT1          | EXI          | NT0         |

|                 | External Interrupt Control Register 0                               | Туре      | r   | W           | n            | W            | r            | w            | r            | W           |

| BA <sub>H</sub> | EXICON1 Reset: 3F <sub>H</sub>                                      | Bit Field |     | 0           | EXI          | NT6          | EXI          | NT5          | EXI          | NT4         |

|                 | External Interrupt Control Register 1                               |           | r   |             | rw           |              | rw           |              | rw           |             |

| ввн             | NMICON Reset: 00 <sub>H</sub><br>NMI Control Register               | Bit Field | 0   | NMI<br>ECC  | NMI<br>VDDP  | NMI<br>VDD   | NMI<br>OCDS  | NMI<br>FLASH | NMI<br>PLL   | NMI<br>WDT  |

|                 |                                                                     | Туре      | r   | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

Table 8 SCU Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7            | 6     | 5           | 4           | 3          | 2             | 1             | 0             |  |  |

|-----------------|----------------------------------------------------------------------|-----------|--------------|-------|-------------|-------------|------------|---------------|---------------|---------------|--|--|

| BE <sub>H</sub> | COCON Reset: 00 <sub>H</sub><br>Clock Output Control Register        | Bit Field |              | 0     | TLEN        | COUT        |            | СО            | REL           |               |  |  |

|                 |                                                                      | Туре      |              | r     | rw          | rw          | rw rw      |               |               |               |  |  |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register    | Bit Field |              |       |             | 0           |            |               |               | DFLAS<br>HEN  |  |  |

|                 |                                                                      | Туре      | r            |       |             |             |            |               |               |               |  |  |

| RMAP =          | = 0, PAGE 3                                                          |           |              |       |             |             |            |               |               |               |  |  |

| B3 <sub>H</sub> | XADDRH Reset: F0H                                                    | Bit Field | ADDRH        |       |             |             |            |               |               |               |  |  |

|                 | On-chip XRAM Address Higher<br>Order                                 |           | rw           |       |             |             |            |               |               |               |  |  |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub> Interrupt Request Register 3           | Bit Field |              |       | CANS<br>RC5 | CCU6<br>SR1 |            |               | CANS<br>RC4   | CCU6<br>SR0   |  |  |

|                 |                                                                      | Туре      | r            |       | rwh         | rwh         | r          |               | rwh           | rwh           |  |  |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub> Interrupt Request Register 4           | Bit Field |              | 0     | CANS<br>RC7 | CCU6<br>SR3 | 0          |               | CANS<br>RC6   | CCU6<br>SR2   |  |  |

|                 |                                                                      | Туре      |              | r rwh |             | rwh         | r          |               | rwh           | rwh           |  |  |

| В7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register | Bit Field | EXINT<br>6IS |       | 0           | UR1RIS      |            | T21EX<br>IS   | JTAGT<br>DIS1 | JTAGT<br>CKS1 |  |  |

|                 | 1                                                                    | Туре      | rw           |       | r           | r           | W          | rw            | rw            | rw            |  |  |

| BA <sub>H</sub> | MODPISEL2 Reset: 00H                                                 | Bit Field |              | (     | 0           |             | T21IS      | T2IS          | T1IS          | TOIS          |  |  |

|                 | Peripheral Input Select Register 2                                   | Туре      |              |       | r           |             | rw         | rw            | rw            | rw            |  |  |

| ввн             | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2       | Bit Field |              |       |             |             |            | UART<br>1_DIS | T21_D<br>IS   |               |  |  |

|                 |                                                                      | Туре      |              |       |             | r           | rw         |               |               | rw            |  |  |

| BD <sub>H</sub> | MODSUSP Reset: 01 <sub>H</sub> Module Suspend Control                | Bit Field |              | 0     |             | T21SU<br>SP | T2SUS<br>P | T13SU<br>SP   | T12SU<br>SP   | WDTS<br>USP   |  |  |

|                 | Register                                                             | Туре      |              | r     |             | rw          | rw         | rw            | rw            | rw            |  |  |

# 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 9 WDT Register Overview

| Addr   | Register Name                                        | Bit       | 7       | 6  | 5          | 4         | 3 | 2         | 1         | 0         |  |  |

|--------|------------------------------------------------------|-----------|---------|----|------------|-----------|---|-----------|-----------|-----------|--|--|

| RMAP = | : 1                                                  |           |         |    |            |           |   |           |           |           |  |  |

| ''     | WDTCON Reset: 00 <sub>H</sub> Watchdog Timer Control | Bit Field | 0       |    | WINB<br>EN | WDTP<br>R | 0 | WDTE<br>N | WDTR<br>S | WDTI<br>N |  |  |

|        | Register                                             | Туре      | r       |    | rw         | rh        | r | rw        | rwh       | rw        |  |  |

| всн    | WDTREL Reset: 00 <sub>H</sub>                        | Bit Field | WDTREL  |    |            |           |   |           |           |           |  |  |

|        | Watchdog Timer Reload<br>Register                    | Туре      | rw      |    |            |           |   |           |           |           |  |  |

| вDН    | WDTWINB Reset: 00 <sub>H</sub>                       | Bit Field | WDTWINB |    |            |           |   |           |           |           |  |  |

|        | Watchdog Window-Boundary Count Register              | Туре      |         | rw |            |           |   |           |           |           |  |  |

Table 9 WDT Register Overview (cont'd)

| Addr            | Register Name                | Bit       | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------------|------------------------------|-----------|-----|---|---|---|---|---|---|---|--|

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>  | Bit Field | WDT |   |   |   |   |   |   |   |  |

|                 | Watchdog Timer Register Low  | Туре      | rh  |   |   |   |   |   |   |   |  |

| BF <sub>H</sub> | H WDTH Reset: 00H            |           | WDT |   |   |   |   |   |   |   |  |

|                 | Watchdog Timer Register High | Туре      | rh  |   |   |   |   |   |   |   |  |

## 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

Table 10 Port Register Overview

| Addr            | Register Name                  | Bit       | 7    | 6  | 5    | 4  | 3  | 2    | 1  | 0  |  |

|-----------------|--------------------------------|-----------|------|----|------|----|----|------|----|----|--|

| RMAP = 0        |                                |           |      |    |      |    |    |      |    |    |  |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00H           | Bit Field | d OP |    | STNR |    | 0  | PAGE |    |    |  |

|                 | Page Register                  | Туре      | \    | V  | V    | V  | r  |      | rw |    |  |

| RMAP =          | = 0, PAGE 0                    |           |      |    |      |    |    |      |    |    |  |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P0 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P0 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P1 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| 91 <sub>H</sub> | P1_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P1 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P5 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| 93 <sub>H</sub> | P5_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P5 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| A0 <sub>H</sub> | P2_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P2 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| A1 <sub>H</sub> | P2_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P2 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P3 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| В1 <sub>Н</sub> | P3_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P3 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| C8H             | P4_DATA Reset: 00 <sub>H</sub> | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P4 Data Register               | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

| C9 <sub>H</sub> | P4_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7   | P6 | P5   | P4 | P3 | P2   | P1 | P0 |  |

|                 | P4 Direction Register          | Туре      | rw   | rw | rw   | rw | rw | rw   | rw | rw |  |

# Table 14 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                      | Bit       | 7                                 | 6             | 5    | 4    | 3        | 2    | 1    | 0    |  |  |

|-----------------|--------------------------------------------------------------------|-----------|-----------------------------------|---------------|------|------|----------|------|------|------|--|--|

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                | Bit Field |                                   |               | 1    | CC6  | i<br>0SL |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC60 Low               | Туре      | rwh                               |               |      |      |          |      |      |      |  |  |

| FB <sub>H</sub> | BH CCU6_CC60SRH Reset: 00H                                         |           | CC60SH                            |               |      |      |          |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC60 High              | Туре      | rwh                               |               |      |      |          |      |      |      |  |  |

| FCH             | CCU6_CC61SRL Reset: 00H                                            | Bit Field |                                   |               |      | CC6  | 1SL      |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC61 Low               | Туре      |                                   |               |      | rw   | vh       |      |      |      |  |  |

| FDH             | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                | Bit Field |                                   |               |      | CC6  | 1SH      |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC61 High              | Туре      |                                   |               |      | rw   | vh       |      |      |      |  |  |

| FEH             | CCU6_CC62SRL Reset: 00H                                            | Bit Field |                                   |               |      | CC6  | S2SL     |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC62 Low               | Туре      |                                   |               |      | rw   | vh       |      |      |      |  |  |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00H                                            | Bit Field |                                   |               |      | CC6  | 2SH      |      |      |      |  |  |

|                 | Capture/Compare Shadow Register for Channel CC62 High              | Туре      |                                   |               |      | rw   | vh       |      |      |      |  |  |

| RMAP =          | = 0, PAGE 1                                                        |           |                                   |               |      |      |          |      |      |      |  |  |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00H                                             | Bit Field | CC63VL                            |               |      |      |          |      |      |      |  |  |

|                 | Capture/Compare Register for Channel CC63 Low                      | Туре      | rh                                |               |      |      |          |      |      |      |  |  |

| 9B <sub>H</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                 | Bit Field | CC63VH                            |               |      |      |          |      |      |      |  |  |

|                 | Capture/Compare Register for Channel CC63 High                     | Туре      | rh                                |               |      |      |          |      |      |      |  |  |

| 9CH             | CCU6_T12PRL Reset: 00H                                             | Bit Field | T12PVL                            |               |      |      |          |      |      |      |  |  |

|                 | Timer T12 Period Register Low                                      | Туре      | rwh                               |               |      |      |          |      |      |      |  |  |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub> Timer T12 Period Register High  | Bit Field | T12PVH                            |               |      |      |          |      |      |      |  |  |

|                 | Timer 112 Feriod Register High                                     | Туре      |                                   |               |      | rw   | vh       |      |      |      |  |  |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub> Timer T13 Period Register Low   | Bit Field | T13PVL                            |               |      |      |          |      |      |      |  |  |

|                 |                                                                    | Туре      | rwh                               |               |      |      |          |      |      |      |  |  |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub> Timer T13 Period Register High  | Bit Field | T13PVH                            |               |      |      |          |      |      |      |  |  |

|                 | -                                                                  | Type      |                                   |               |      |      | vh       |      |      |      |  |  |

| <sup>A4</sup> H | CCU6_T12DTCL Reset: 00 <sub>H</sub> Dead-Time Control Register for | Bit Field |                                   |               |      |      |          |      |      |      |  |  |

|                 | Timer T12 Low                                                      | Туре      |                                   |               |      |      | W        |      |      |      |  |  |

| A5 <sub>H</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub> Dead-Time Control Register for | Bit Field | 0                                 | DTR2          | DTR1 | DTR0 | 0        | DTE2 | DTE1 | DTE0 |  |  |

|                 | Timer T12 High                                                     | Туре      | r                                 | rh            | rh   | rh   | r        | rw   | rw   | rw   |  |  |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub> Timer Control Register 0 Low    | Bit Field | CTM CDIR STE1 T12R T12 T12CLK PRE |               |      |      |          |      |      |      |  |  |

|                 |                                                                    | Туре      | rw rh rh rw rw                    |               |      |      |          |      |      |      |  |  |

| A7 <sub>H</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub> Timer Control Register 0 High   | Bit Field | 0 STE1 T13R T13 T13CLK<br>3 PRE   |               |      |      |          |      |      |      |  |  |

|                 |                                                                    | Туре      |                                   | r rh rh rw rw |      |      |          |      |      |      |  |  |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00H                                             | Bit Field |                                   |               |      | CC6  | 60VL     |      |      |      |  |  |

|                 | Capture/Compare Register for Channel CC60 Low                      | Туре      |                                   |               |      | r    | h        |      |      |      |  |  |

Table 17 CAN Register Overview (cont'd)

| Addr            | Register Name                | Bit                           |      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------|------------------------------|-------------------------------|------|-------|---|---|---|---|---|---|---|--|--|

| DB <sub>H</sub> |                              |                               |      | CD    |   |   |   |   |   |   |   |  |  |

|                 | CAN Data Register 0          | Туре                          |      | rwh   |   |   |   |   |   |   |   |  |  |

| DCH             | DATA1 Reset                  | : <b>00<sub>H</sub></b> Bit F | ield | CD    |   |   |   |   |   |   |   |  |  |

|                 | CAN Data Register 1          | Туре                          |      | rwh   |   |   |   |   |   |   |   |  |  |

| DDH             | DATA2 Reset: 00 <sub>H</sub> |                               | ield | CD    |   |   |   |   |   |   |   |  |  |

|                 | CAN Data Register 2          | Туре                          | ,    | rwh   |   |   |   |   |   |   |   |  |  |

| DE <sub>H</sub> | DATA3 Reset: 00 <sub>H</sub> |                               | ield | ld CD |   |   |   |   |   |   |   |  |  |

|                 | CAN Data Register 3          | Туре                          | )    | rwh   |   |   |   |   |   |   |   |  |  |

## 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 18 OCDS Register Overview

| Addr            | Register Name                                                                       | Bit       | 7           | 6         | 5          | 4           | 3           | 2         | 1          | 0         |  |

|-----------------|-------------------------------------------------------------------------------------|-----------|-------------|-----------|------------|-------------|-------------|-----------|------------|-----------|--|

| RMAP =          | : 1                                                                                 |           |             | •         |            | •           |             | •         |            |           |  |

| E9 <sub>H</sub> | MMCR2 Reset: 1U <sub>H</sub><br>Monitor Mode Control 2                              | Bit Field | STMO<br>DE  | EXBC      | DSUS<br>P  | MBCO<br>N   | ALTDI       | MMEP      | MMOD<br>E  | JENA      |  |

|                 | Register                                                                            | Туре      | rw          | rw        | rw         | rwh         | rw          | rwh       | rh         | rh        |  |

| F1 <sub>H</sub> | MMCR Reset: 00 <sub>H</sub> Monitor Mode Control Register                           | Bit Field | MEXIT<br>_P | MEXIT     | 0          | MSTE<br>P   | MRAM<br>S_P | MRAM<br>S | TRF        | RRF       |  |

|                 |                                                                                     | Туре      | w           | rwh       | r          | rw          | w           | rwh       | rh         | rh        |  |

| F2 <sub>H</sub> | F2 <sub>H</sub> MMSR Reset: 00 <sub>H</sub> Monitor Mode Status Register            | Bit Field | MBCA<br>M   | MBCIN     | EXBF       | SWBF        | HWB3<br>F   | HWB2<br>F | HWB1<br>F  | HWB0<br>F |  |

|                 |                                                                                     | Туре      | rw          | rwh       | rwh        | rwh         | rwh         | rwh       | rwh        | rwh       |  |

| F3 <sub>H</sub> | F3 <sub>H</sub> MMBPCR Reset: 00 <sub>H</sub> Breakpoints Control Register          |           | SWBC        | WBC HWB3C |            | HWB2C       |             | HWB1<br>C | HWB0C      |           |  |

|                 |                                                                                     | Туре      | rw          | rw rw     |            | rw          |             | rw        | rw         |           |  |

| F4 <sub>H</sub> | 4 <sub>H</sub> MMICR Reset: 00 <sub>H</sub> Monitor Mode Interrupt Control Register | Bit Field | DVEC<br>T   | DRET<br>R | COMR<br>ST | MSTS<br>EL  | MMUI<br>E_P | MMUI<br>E | RRIE_<br>P | RRIE      |  |

|                 |                                                                                     | Туре      | rwh         | rwh       | rwh        | rh          | w           | rw        | w          | rw        |  |

| F5 <sub>H</sub> | MMDR Reset: 00 <sub>H</sub>                                                         | Bit Field | MMRR        |           |            |             |             |           |            |           |  |

|                 | Monitor Mode Data Transfer<br>Register<br>Receive                                   | Туре      | rh          |           |            |             |             |           |            |           |  |

| F6 <sub>H</sub> | HWBPSR Reset: 00 <sub>H</sub> Hardware Breakpoints Select                           |           | 0           |           |            | BPSEL<br>_P |             |           |            |           |  |

|                 | Register                                                                            | Туре      | r w rw      |           |            |             |             |           |            |           |  |

| F7 <sub>H</sub> | 7 <sub>H</sub> HWBPDR Reset: 00 <sub>H</sub>                                        |           |             |           |            | HWE         | ЗРхх        |           |            |           |  |

|                 | Hardware Breakpoints Data<br>Register                                               | Туре      | rw          |           |            |             |             |           |            |           |  |

| EBH             | MMWR1 Reset: 00 <sub>H</sub>                                                        | Bit Field |             |           |            | MM          | WR1         |           |            |           |  |

|                 | Monitor Work Register 1                                                             | Туре      |             |           |            | r           | W           |           |            |           |  |

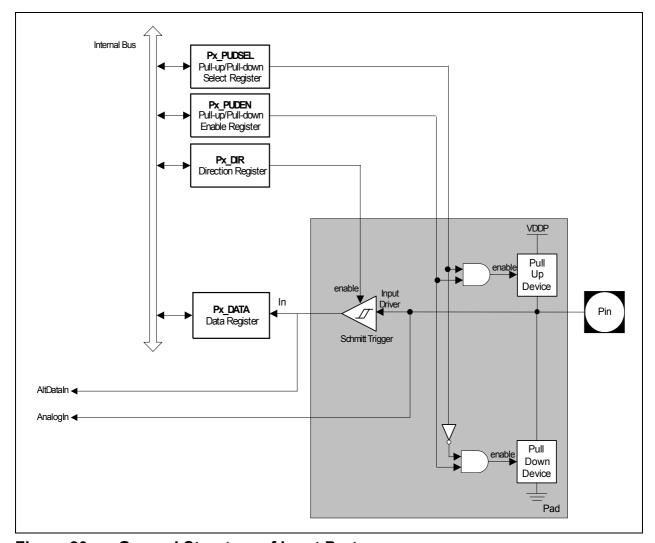

Figure 20 shows the structure of an input-only port pin.

Figure 20 General Structure of Input Port

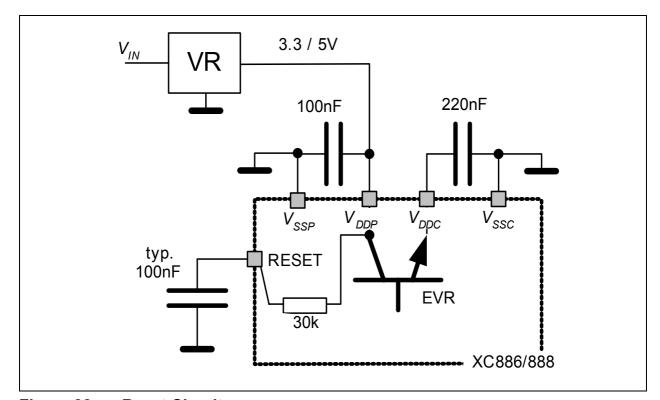

#### 3.7 Reset Control

The XC886/888 has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC886/888 is first powered up, the status of certain pins (see **Table 23**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

In order to power up the system properly, the external reset pin RESET must be asserted until  $V_{\rm DDC}$  reaches 0.9\* $V_{\rm DDC}$ . The delay of external reset can be realized by an external capacitor at RESET pin. This capacitor value must be selected so that  $V_{\rm RESET}$  reaches 0.4 V, but not before  $V_{\rm DDC}$  reaches 0.9\*  $V_{\rm DDC}$

A typical application example is shown in Figure 22. The  $V_{\rm DDP}$  capacitor value is 100 nF while the  $V_{\rm DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{\rm DDC}$  to reach  $0.9^*V_{\rm DDC}$  is less than 50  $\mu s$  once  $V_{\rm DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{\rm DDP}$  (slew rate) is less than 500  $\mu s$ , the RESET pin should be held low for 500  $\mu s$  typically. See Figure 23.

Figure 22 Reset Circuitry

## 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC886/888 Core in real-time control applications, which require fast mathematical computations.

#### **Features**

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

**Table 28** specifies the number of clock cycles used for calculation in various operations.

**Table 28** MDU Operation Characteristics

| Operation                | Result | Remainder | No. of Clock Cycles used for calculation |

|--------------------------|--------|-----------|------------------------------------------|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                       |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                       |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                       |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                       |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                       |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                       |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)              |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)              |

## 3.23 Chip Identification Number

The XC886/888 identity (ID) register is located at Page 1 of address  $B3_H$ . The value of ID register is  $09_H$  for Flash devices and  $22_H$  for ROM devices. However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

Table 36 lists the chip identification numbers of available XC886/888 Flash and ROM device variants.

Table 36 Chip Identification Number

| <b>Product Variant</b> | Chip Identification Number |                       |                       |  |  |  |  |  |

|------------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                        | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |

| Flash Devices          |                            |                       |                       |  |  |  |  |  |

| XC886CLM-8FFA 3V3      | -                          | 09500102 <sub>H</sub> | 0B500102 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-8FFA 3V3      | -                          | 09500103 <sub>H</sub> | 0B500103 <sub>H</sub> |  |  |  |  |  |

| XC886LM-8FFA 3V3       | -                          | 09500122 <sub>H</sub> | 0B500122 <sub>H</sub> |  |  |  |  |  |

| XC888LM-8FFA 3V3       | -                          | 09500123 <sub>H</sub> | 0B500123 <sub>H</sub> |  |  |  |  |  |

| XC886CLM-6FFA 3V3      | -                          | 09551502 <sub>H</sub> | 0B551502 <sub>H</sub> |  |  |  |  |  |

| XC888CLM-6FFA 3V3      | -                          | 09551503 <sub>H</sub> | 0B551503 <sub>H</sub> |  |  |  |  |  |

| XC886LM-6FFA 3V3       | -                          | 09551522 <sub>H</sub> | 0B551522 <sub>H</sub> |  |  |  |  |  |

| XC888LM-6FFA 3V3       | -                          | 09551523 <sub>H</sub> | 0B551523 <sub>H</sub> |  |  |  |  |  |

| XC886CM-8FFA 3V3       | -                          | 09580102 <sub>H</sub> | 0B580102 <sub>H</sub> |  |  |  |  |  |

| XC888CM-8FFA 3V3       | -                          | 09580103 <sub>H</sub> | 0B580103 <sub>H</sub> |  |  |  |  |  |

| XC886C-8FFA 3V3        | -                          | 09580142 <sub>H</sub> | 0B580142 <sub>H</sub> |  |  |  |  |  |

| XC888C-8FFA 3V3        | -                          | 09580143 <sub>H</sub> | 0B580143 <sub>H</sub> |  |  |  |  |  |

| XC886-8FFA 3V3         | -                          | 09580162 <sub>H</sub> | 0B580162 <sub>H</sub> |  |  |  |  |  |

| XC888-8FFA 3V3         | -                          | 09580163 <sub>H</sub> | 0B580163 <sub>H</sub> |  |  |  |  |  |

| XC886CM-6FFA 3V3       | -                          | 095D1502 <sub>H</sub> | 0B5D1502 <sub>H</sub> |  |  |  |  |  |

| XC888CM-6FFA 3V3       | -                          | 095D1503 <sub>H</sub> | 0B5D1503 <sub>H</sub> |  |  |  |  |  |

| XC886C-6FFA 3V3        | -                          | 095D1542 <sub>H</sub> | 0B5D1542 <sub>H</sub> |  |  |  |  |  |

| XC888C-6FFA 3V3        | -                          | 095D1543 <sub>H</sub> | 0B5D1543 <sub>H</sub> |  |  |  |  |  |

#### **Electrical Parameters**

Table 40 ADC Characteristics (Operating Conditions apply;  $V_{\text{DDP}}$  = 5V Range)

| Parameter                                           | Symbol           |    | Limit Values |      |                           | Unit |                         |

|-----------------------------------------------------|------------------|----|--------------|------|---------------------------|------|-------------------------|

|                                                     |                  |    | min.         | typ. | max.                      |      | Remarks                 |

| Overload current coupling factor for                | $K_{OVD}$        | CC | _            | _    | 5.0 x<br>10 <sup>-3</sup> | _    | $I_{\rm OV} > 0^{1)3)}$ |

| digital I/O pins                                    |                  |    | _            | _    | 1.0 x<br>10 <sup>-2</sup> | _    | $I_{\rm OV} < 0^{1)3)}$ |

| Switched capacitance at the reference voltage input | $C_{AREFSW}$     | CC | _            | 10   | 20                        | pF   | 1)4)                    |

| Switched capacitance at the analog voltage inputs   | $C_{AINSW}$      | CC | _            | 5    | 7                         | pF   | 1)5)                    |

| Input resistance of the reference input             | $R_{AREF}$       | CC | _            | 1    | 2                         | kΩ   | 1)                      |

| Input resistance of the selected analog channel     | R <sub>AIN</sub> | CC | _            | 1    | 1.5                       | kΩ   | 1)                      |

- 1) Not subjected to production test, verified by design/characterization

- 2) TUE is tested at  $V_{\rm AREF}$  = 5.0 V,  $V_{\rm AGND}$  = 0 V,  $V_{\rm DDP}$  = 5.0 V.

- 3) An overload current  $(I_{\text{OV}})$  through a pin injects a certain error current  $(I_{\text{INJ}})$  into the adjacent pins. This error current adds to the respective pin's leakage current  $(I_{\text{OZ}})$ . The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{\text{OV}}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{\text{TOT}}| = |I_{\text{OZ1}}| + (|I_{\text{OV}}| \times K_{\text{OV}})$ . The additional error current may distort the input voltage on analog inputs.

- 4) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- 5) The sampling capacity of the conversion C-Network is pre-charged to  $V_{\mathsf{AREF}}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{\mathsf{AREF}}/2$ .

Data Sheet 117 V1.2, 2009-07

#### **Package and Quality Declaration**

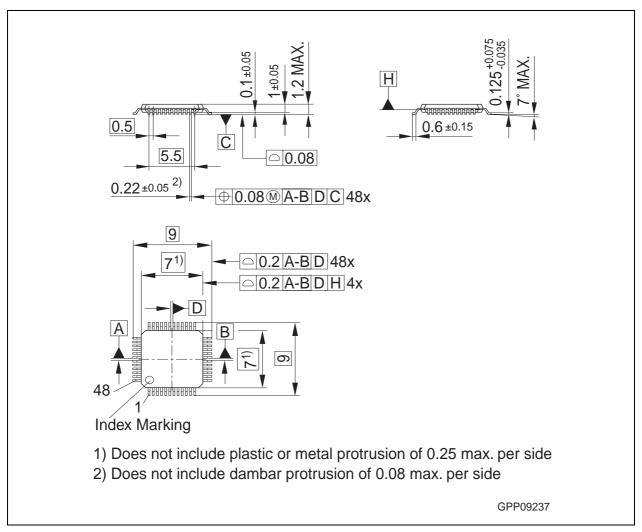

## 5.2 Package Outline

Figure 48 shows the package outlines of the XC886.

Figure 48 PG-TQFP-48 Package Outline

Data Sheet 134 V1.2, 2009-07

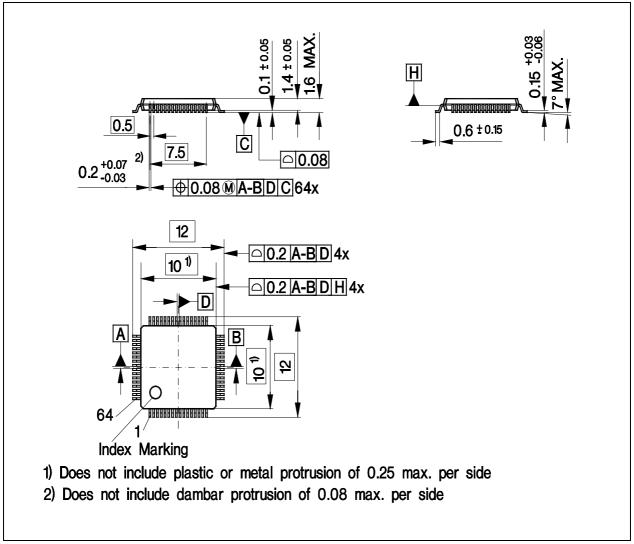

## **Package and Quality Declaration**

Figure 49 shows the package outlines of the XC888.

Figure 49 PG-TQFP-64 Package Outline

Data Sheet 135 V1.2, 2009-07