Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                    |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                            |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 24MHz                                                                            |

| Connectivity               | CANbus, SSI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1.75K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 8x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-TQFP-64                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc888cm8ffi5vacfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

#### XC886/888 Variant Devices

The XC886/888 product family features devices with different configurations, program memory sizes, package options, power supply voltage, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC886/888 device configurations are summarized in **Table 1**. For each configuration, 2 types of packages are available:

- PG-TQFP-48, which is denoted by XC886 and;

- PG-TQFP-64, which is denoted by XC888.

| Device Name  | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

|--------------|---------------|--------------------|---------------|

| XC886/888    | No            | No                 | No            |

| XC886/888C   | Yes           | No                 | No            |

| XC886/888CM  | Yes           | No                 | Yes           |

| XC886/888LM  | No            | Yes                | Yes           |

| XC886/888CLM | Yes           | Yes                | Yes           |

#### Table 1Device Configuration

Note: For variants with LIN BSL support, only LIN BSL is available regardless of the availability of the CAN module.

From these 10 different combinations of configuration and package type, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profile (Automotive or Industrial), as shown in Table 2.

#### Table 2Device Profile

| Sales Type              | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|-------------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAK-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC886*/888*-8FFA 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-6FFA 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC886*/888*-8FFI 5V | Flash          | 32                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC886*/888*-6FFI 5V | Flash          | 24                            | 5.0                    | -40 to 85                | Industrial         |

#### **General Device Information**

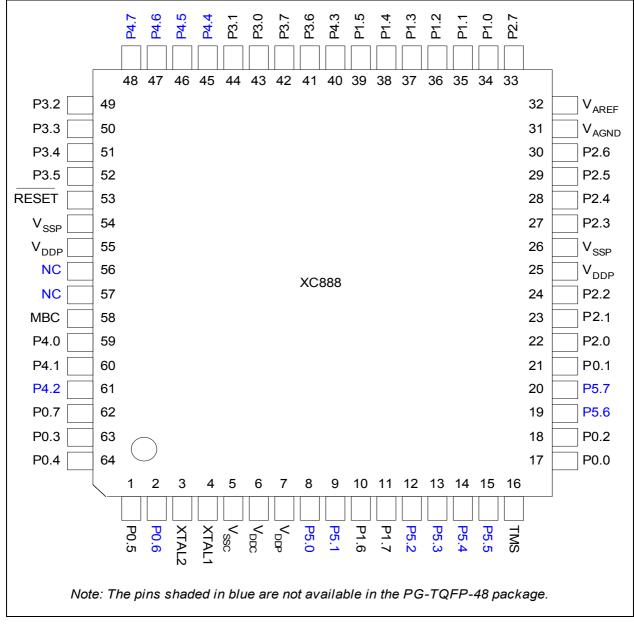

Figure 5 XC888 Pin Configuration, PG-TQFP-64 Package (top view)

### **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                       |                                                                                                                                                              |

|--------|----------------------------|------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1     |                            | I/O  |                | I/O port. It ca<br>for the JTAG                | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, Timer 0, Timer 1,<br>1, er 21, MultiCAN and SSC.                  |

| P1.0   | 26/34                      |      | PU             | RXD_0<br>T2EX<br>RXDC0_0                       | UART Receive Data Input<br>Timer 2 External Trigger Input<br>MultiCAN Node 0 Receiver Input                                                                  |

| P1.1   | 27/35                      |      | PU             | EXINT3<br>T0_1<br>TDO_1<br>TXD_0<br>TXDC0_0    | External Interrupt Input 3<br>Timer 0 Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 0 Transmitter<br>Output |

| P1.2   | 28/36                      |      | PU             | SCK_0                                          | SSC Clock Input/Output                                                                                                                                       |

| P1.3   | 29/37                      |      | PU             | MTSR_0<br>TXDC1_3                              | SSC Master Transmit<br>Output/Slave Receive Input<br>MultiCAN Node 1 Transmitter<br>Output                                                                   |

| P1.4   | 30/38                      |      | PU             | MRST_0<br>EXINT0_1<br>RXDC1_3                  | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>MultiCAN Node 1 Receiver Input                                           |

| P1.5   | 31/39                      |      | PU             | CCPOS0_1<br>EXINT5<br>T1_1<br>EXF2_0<br>RXDO_0 | CCU6 Hall Input 0<br>External Interrupt Input 5<br>Timer 1 Input<br>Timer 2 External Flag Output<br>UART Transmit Data Output                                |

### Table 3Pin Definitions and Functions (cont'd)

## XC886/888CLM

### **General Device Information**

| Symbol | Pin Number<br>(TQFP-48/64) | Туре | Reset<br>State | Function                                 |                                                                                                                                                           |

|--------|----------------------------|------|----------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р3     |                            | I/O  |                | I/O port. It ca                          | B-bit bidirectional general purpose<br>an be used as alternate functions<br>ART1, Timer 21 and MultiCAN.                                                  |

| P3.0   | 35/43                      |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1            | CCU6 Hall Input 1<br>Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                           |

| P3.1   | 36/44                      |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1 | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output |

| P3.2   | 37/49                      |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0  | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1                           |

| P3.3   | 38/50                      |      | Hi-Z           | COUT61_0<br>TXDC1_1                      | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output                                                                           |

| P3.4   | 39/51                      |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0             | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input                                         |

| P3.5   | 40/52                      |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1           | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output                                          |

| P3.6   | 33/41                      |      | PD             | CTRAP_0                                  | CCU6 Trap Input                                                                                                                                           |

### Table 3Pin Definitions and Functions (cont'd)

### **General Device Information**

### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(TQFP-48/64) | Reset<br>State | Function           |                                                                      |

|--------|----------------------------|----------------|--------------------|----------------------------------------------------------------------|

| P3.7   | 34/42                      | Hi-Z           | EXINT4<br>COUT63_0 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3 |

The page register has the following definition:

### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

### 3.2.4 XC886/888 Register Overview

The SFRs of the XC886/888 are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.14**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

### 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr            | Register Name                                            | Bit       | 7         | 6    | 5    | 4           | 3         | 2    | 1    | 0          |  |

|-----------------|----------------------------------------------------------|-----------|-----------|------|------|-------------|-----------|------|------|------------|--|

| RMAP =          | = 0 or 1                                                 | I.        |           |      |      |             |           |      |      |            |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                                | Bit Field |           |      |      | S           | P         |      |      |            |  |

|                 | Stack Pointer Register                                   | Туре      |           |      |      | r           | W         |      |      |            |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                               | Bit Field | DPL7      | DPL6 | DPL5 | DPL4        | DPL3      | DPL2 | DPL1 | DPL0       |  |

|                 | Data Pointer Register Low                                | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                               | Bit Field | DPH7      | DPH6 | DPH5 | DPH4        | DPH3      | DPH2 | DPH1 | DPH0       |  |

|                 | Data Pointer Register High                               | Туре      | rw        | rw   | rw   | rw          | rw        | rw   | rw   | rw         |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                              | Bit Field | SMOD      |      | 0    |             | GF1       | GF0  | 0    | IDLE       |  |

|                 | Power Control Register                                   | Туре      | rw        |      | r    |             | rw        | rw   | r    | rw         |  |

| <sup>88</sup> H | TCON Reset: 00 <sub>H</sub>                              | Bit Field | TF1       | TR1  | TF0  | TR0         | IE1       | IT1  | IE0  | IT0        |  |

|                 | Timer Control Register                                   | Туре      | rwh       | rw   | rwh  | rw          | rwh       | rw   | rwh  | rw         |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register       | Bit Field | GATE<br>1 | T1S  | T1M  |             | GATE<br>0 | TOS  | ТОМ  |            |  |

| <b> </b>        |                                                          | Туре      | rw        | rw   | r    | rw          |           | rw   | r    | w          |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                               | Bit Field |           | •    |      | V           | AL        | •    |      |            |  |

|                 | Timer 0 Register Low                                     | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                               | Bit Field | VAL       |      |      |             |           |      |      |            |  |

|                 | Timer 1 Register Low                                     | Туре      |           |      | rwh  |             |           |      |      |            |  |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Timer 0 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                               | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Timer 1 Register High                                    | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                              | Bit Field | SM0       | SM1  | SM2  | REN         | TB8       | RB8  | TI   | RI         |  |

|                 | Serial Channel Control Register                          | Туре      | rw        | rw   | rw   | rw          | rw        | rwh  | rwh  | rwh        |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                              | Bit Field |           |      |      | V           | AL        |      |      |            |  |

|                 | Serial Data Buffer Register                              | Туре      |           |      |      | rv          | vh        |      |      |            |  |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub><br>Extended Operation Register | Bit Field |           | 0    |      | TRAP_<br>EN |           | 0    |      | DPSE<br>L0 |  |

|                 |                                                          | Туре      |           | r    |      | rw          |           | r    |      | rw         |  |

### Table 5 CPU Register Overview

| Addr            | Register Name              | Bit       | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-----------------|----------------------------|-----------|------|---|---|----|----|---|---|---|--|

| B3 <sub>H</sub> | MR1 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 1      | Туре      | rh   |   |   |    |    |   |   |   |  |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 2     | Туре      | rw   |   |   |    |    |   |   |   |  |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 2      | Туре      |      |   |   | r  | h  |   |   |   |  |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub> | Bit Field | DATA |   |   |    |    |   |   |   |  |

|                 | MDU Operand Register 3     | Туре      | rw   |   |   |    |    |   |   |   |  |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub> | Bit Field | DATA |   |   |    |    |   |   |   |  |

|                 | MDU Result Register 3      | Туре      | rh   |   |   |    |    |   |   |   |  |

| B6 <sub>H</sub> | MD4 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Operand Register 4     | Туре      |      |   |   | r  | w  |   |   |   |  |

| B6 <sub>H</sub> | MR4 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 4      | Туре      |      |   |   | r  | h  |   |   |   |  |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub> | Bit Field | DATA |   |   |    |    |   |   |   |  |

|                 | MDU Operand Register 5     | Туре      | rw   |   |   |    |    |   |   |   |  |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub> | Bit Field |      |   |   | DA | TA |   |   |   |  |

|                 | MDU Result Register 5      | Туре      |      |   |   | r  | 'n |   |   |   |  |

### Table 6MDU Register Overview (cont'd)

## 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7     | 6 | 5 | 4  | 3   | 2 | 1 | 0 |  |

|-----------------|----------------------------------|-----------|-------|---|---|----|-----|---|---|---|--|

| RMAP =          | = 1                              |           |       |   |   |    |     | 1 |   |   |  |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |  |

|                 | CORDIC X Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |

|                 | CORDIC X Data High Byte          | Туре      | rw    |   |   |    |     |   |   |   |  |

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub> | Bit Field | DATAL |   |   |    |     |   |   |   |  |

|                 | CORDIC Y Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAH |   |   |   |  |

|                 | CORDIC Y Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | TAL |   |   |   |  |

|                 | CORDIC Z Data Low Byte           | Туре      | rw    |   |   |    |     |   |   |   |  |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub> | Bit Field |       |   |   | DA | ТАН |   |   |   |  |

| C               | CORDIC Z Data High Byte          | Туре      |       |   |   | r  | W   |   |   |   |  |

### Table 9WDT Register Overview (cont'd)

| Addr            | Register Name                              | Bit       | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------------|--------------------------------------------|-----------|--------|---|---|---|---|---|---|---|--|

| ве <sub>Н</sub> | WDTL Reset: 00 <sub>H</sub>                | Bit Field | WDT    |   |   |   |   |   |   |   |  |

|                 | Watchdog Timer Register Low                | Туре      | rh     |   |   |   |   |   |   |   |  |

| bf <sub>h</sub> | F <sub>H</sub> WDTH Reset: 00 <sub>H</sub> | Bit Field | ld WDT |   |   |   |   |   |   |   |  |

|                 | Watchdog Timer Register High               | Туре      | rh     |   |   |   |   |   |   |   |  |

### 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

### Table 10Port Register Overview

| Addr            | Register Name                  | Bit       | 7        | 6  | 5  | 4  | 3  | 2  | 1    | 0        |

|-----------------|--------------------------------|-----------|----------|----|----|----|----|----|------|----------|

| RMAP =          | = 0                            |           |          |    |    |    |    |    |      | <u>.</u> |

| B2 <sub>H</sub> |                                |           | Field OP |    | ST | NR | 0  |    | PAGE |          |

|                 | Page Register                  | Туре      | ١        | N  | ١  | N  | r  |    | rw   |          |

| RMAP =          | = 0, PAGE 0                    |           |          |    | •  |    | •  |    |      |          |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P0 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P0 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P1 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| 91 <sub>H</sub> | P1_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P1 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P5 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| 93 <sub>H</sub> | P5_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P5 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| A0 <sub>H</sub> | P2_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P2 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| A1 <sub>H</sub> | P2_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P2 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P3 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| в1 <sub>Н</sub> | P3_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P3 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| C8 <sub>H</sub> | P4_DATA Reset: 00 <sub>H</sub> | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P4 Data Register               | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

| C9 <sub>H</sub> | P4_DIR Reset: 00 <sub>H</sub>  | Bit Field | P7       | P6 | P5 | P4 | P3 | P2 | P1   | P0       |

|                 | P4 Direction Register          | Туре      | rw       | rw | rw | rw | rw | rw | rw   | rw       |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                       | Bit       | 7     | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|---------------------------------------------------------------------|-----------|-------|--------------|--------------|------------|--------------|------------|--------------|------------|

| Fe <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low  | Bit Field | 0     | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                     | Туре      | r     | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High | Bit Field | T13IM | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                     | Туре      | rwh   | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

### 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

### Table 15 UART1 Register Overview

| Addr            | Register Name                                | Bit       | 7        | 6   | 5   | 4   | 3    | 2     | 1   | 0    |  |

|-----------------|----------------------------------------------|-----------|----------|-----|-----|-----|------|-------|-----|------|--|

| RMAP =          | = 1                                          | 1         |          |     |     |     |      |       |     | 1    |  |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                  |           | SM0      | SM1 | SM2 | REN | TB8  | RB8   | TI  | RI   |  |

|                 | Serial Channel Control Register              | Туре      | rw       | rw  | rw  | rw  | rw   | rwh   | rwh | rwh  |  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                  | Bit Field |          |     |     | V   | AL   |       |     |      |  |

|                 | Serial Data Buffer Register                  | Туре      |          |     |     | rv  | vh   |       |     |      |  |

| са <sub>Н</sub> | BCON Reset: 00 <sub>H</sub>                  | Bit Field |          | (   | )   |     |      | BRPRE |     | R    |  |

|                 | Baud Rate Control Register                   | Туре      |          |     | r   |     |      | rw    |     | rw   |  |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>                    | Bit Field | BR_VALUE |     |     |     |      |       |     |      |  |

|                 | Baud Rate Timer/Reload<br>Register           | Туре      |          |     |     | rv  | vh   |       |     |      |  |

| сс <sub>Н</sub> | FDCON Reset: 00 <sub>H</sub>                 | Bit Field |          |     | 0   |     |      | NDOV  | FDM | FDEN |  |

|                 | Fractional Divider Control<br>Register       | Туре      |          |     | r   |     |      | rwh   | rw  | rw   |  |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                | Bit Field |          |     |     | ST  | ΈP   |       |     |      |  |

|                 | Fractional Divider Reload<br>Register        | Туре      | rw       |     |     |     |      |       |     |      |  |

| Ceh             | CE <sub>H</sub> FDRES Reset: 00 <sub>H</sub> |           |          |     |     | RES | SULT |       |     |      |  |

|                 | Fractional Divider Result<br>Register        | Туре      |          |     |     | r   | h    |       |     |      |  |

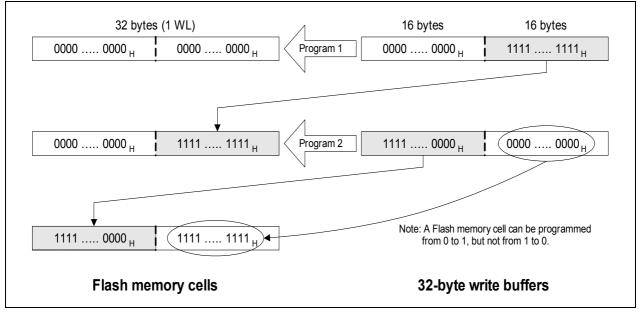

## 3.3.3 Flash Programming Width

For the P-Flash banks, a programmed wordline (WL) must be erased before it can be reprogrammed as the Flash cells can only withstand one gate disturb. This means that the entire sector containing the WL must be erased since it is impossible to erase a single WL.

For the D-Flash bank, the same WL can be programmed twice before erasing is required as the Flash cells are able to withstand two gate disturbs. This means if the number of data bytes that needs to be written is smaller than the 32-byte minimum programming width, the user can opt to program this number of data bytes (x; where x can be any integer from 1 to 31) first and program the remaining bytes (32 - x) later. Hence, it is possible to program the same WL, for example, with 16 bytes of data two times (see **Figure 12**)

#### Figure 12 D-Flash Programming

Note: When programming a D-Flash WL the second time, the previously programmed Flash memory cells (whether 0s or 1s) should be reprogrammed with 0s to retain its original contents and to prevent "over-programming".

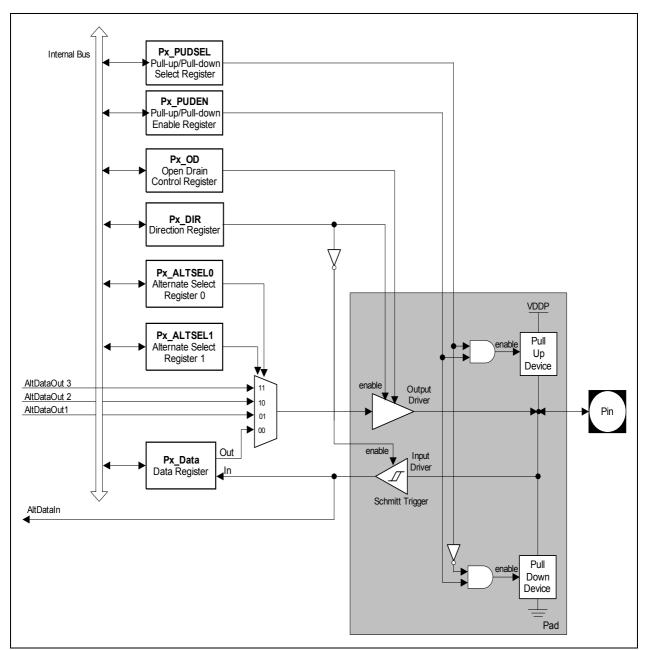

Figure 19 General Structure of Bidirectional Port

For power saving purposes, the clocks may be disabled or slowed down according to **Table 26**.

# Table 26System frequency ( $f_{sys}$ = 96 MHz)

| Power Saving Mode | Action                                                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| Idle              | Clock to the CPU is disabled.                                                                                            |

| Slow-down         | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |

| Power-down        | Oscillator and PLL are switched off.                                                                                     |

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

STEP 2: Wait for an incoming LIN frame from host

STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

### 3.23 Chip Identification Number

The XC886/888 identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $09_{H}$  for Flash devices and  $22_{H}$  for ROM devices. However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

**Table 36** lists the chip identification numbers of available XC886/888 Flash and ROM device variants.

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |  |

| Flash Devices     |                            |                       |                       |  |  |  |  |  |  |

| XC886CLM-8FFA 3V3 | -                          | 09500102 <sub>H</sub> | 0B500102 <sub>H</sub> |  |  |  |  |  |  |

| XC888CLM-8FFA 3V3 | -                          | 09500103 <sub>H</sub> | 0B500103 <sub>H</sub> |  |  |  |  |  |  |

| XC886LM-8FFA 3V3  | -                          | 09500122 <sub>H</sub> | 0B500122 <sub>H</sub> |  |  |  |  |  |  |

| XC888LM-8FFA 3V3  | -                          | 09500123 <sub>H</sub> | 0B500123 <sub>H</sub> |  |  |  |  |  |  |

| XC886CLM-6FFA 3V3 | -                          | 09551502 <sub>H</sub> | 0B551502 <sub>H</sub> |  |  |  |  |  |  |

| XC888CLM-6FFA 3V3 | -                          | 09551503 <sub>H</sub> | 0B551503 <sub>H</sub> |  |  |  |  |  |  |

| XC886LM-6FFA 3V3  | -                          | 09551522 <sub>H</sub> | 0B551522 <sub>H</sub> |  |  |  |  |  |  |

| XC888LM-6FFA 3V3  | -                          | 09551523 <sub>н</sub> | 0B551523 <sub>H</sub> |  |  |  |  |  |  |

| XC886CM-8FFA 3V3  | -                          | 09580102 <sub>H</sub> | 0B580102 <sub>H</sub> |  |  |  |  |  |  |

| XC888CM-8FFA 3V3  | -                          | 09580103 <sub>H</sub> | 0B580103 <sub>H</sub> |  |  |  |  |  |  |

| XC886C-8FFA 3V3   | -                          | 09580142 <sub>H</sub> | 0B580142 <sub>H</sub> |  |  |  |  |  |  |

| XC888C-8FFA 3V3   | -                          | 09580143 <sub>H</sub> | 0B580143 <sub>H</sub> |  |  |  |  |  |  |

| XC886-8FFA 3V3    | -                          | 09580162 <sub>H</sub> | 0B580162 <sub>H</sub> |  |  |  |  |  |  |

| XC888-8FFA 3V3    | -                          | 09580163 <sub>H</sub> | 0B580163 <sub>H</sub> |  |  |  |  |  |  |

| XC886CM-6FFA 3V3  | -                          | 095D1502 <sub>H</sub> | 0B5D1502 <sub>H</sub> |  |  |  |  |  |  |

| XC888CM-6FFA 3V3  | -                          | 095D1503 <sub>H</sub> | 0B5D1503 <sub>H</sub> |  |  |  |  |  |  |

| XC886C-6FFA 3V3   | -                          | 095D1542 <sub>H</sub> | 0B5D1542 <sub>H</sub> |  |  |  |  |  |  |

| XC888C-6FFA 3V3   | -                          | 095D1543 <sub>H</sub> | 0B5D1543 <sub>H</sub> |  |  |  |  |  |  |

#### Table 36 Chip Identification Number

### Table 36Chip Identification Number (cont'd)

| Product Variant   | Chip Identification Number |                       |                       |  |  |  |  |  |  |

|-------------------|----------------------------|-----------------------|-----------------------|--|--|--|--|--|--|

|                   | AA-Step                    | AB-Step               | AC-Step               |  |  |  |  |  |  |

| XC886-6FFA 3V3    | -                          | 095D1562 <sub>H</sub> | 0B5D1562 <sub>H</sub> |  |  |  |  |  |  |

| XC888-6FFA 3V3    | -                          | 095D1563 <sub>H</sub> | 0B5D1563 <sub>H</sub> |  |  |  |  |  |  |

| XC886CLM-8FFA 5V  | -                          | 09900102 <sub>H</sub> | 0B900102 <sub>H</sub> |  |  |  |  |  |  |

| XC888CLM-8FFA 5V  | -                          | 09900103 <sub>H</sub> | 0B900103 <sub>H</sub> |  |  |  |  |  |  |

| XC886LM-8FFA 5V   | -                          | 09900122 <sub>H</sub> | 0B900122 <sub>H</sub> |  |  |  |  |  |  |

| XC888LM-8FFA 5V   | -                          | 09900123 <sub>H</sub> | 0B900123 <sub>H</sub> |  |  |  |  |  |  |

| XC886CLM-6FFA 5V  | -                          | 09951502 <sub>H</sub> | 0B951502 <sub>H</sub> |  |  |  |  |  |  |

| XC888CLM-6FFA 5V  | -                          | 09951503 <sub>H</sub> | 0B951503 <sub>H</sub> |  |  |  |  |  |  |

| XC886LM-6FFA 5V   | -                          | 09951522 <sub>Н</sub> | 0B951522 <sub>H</sub> |  |  |  |  |  |  |

| XC888LM-6FFA 5V   | -                          | 09951523 <sub>H</sub> | 0B951523 <sub>H</sub> |  |  |  |  |  |  |

| XC886CM-8FFA 5V   | -                          | 09980102 <sub>H</sub> | 0B980102 <sub>H</sub> |  |  |  |  |  |  |

| XC888CM-8FFA 5V   | -                          | 09980103 <sub>H</sub> | 0B980103 <sub>H</sub> |  |  |  |  |  |  |

| XC886C-8FFA 5V    | -                          | 09980142 <sub>H</sub> | 0B980142 <sub>H</sub> |  |  |  |  |  |  |

| XC888C-8FFA 5V    | -                          | 09980143 <sub>H</sub> | 0B980143 <sub>H</sub> |  |  |  |  |  |  |

| XC886-8FFA 5V     | -                          | 09980162 <sub>H</sub> | 0B980162 <sub>H</sub> |  |  |  |  |  |  |

| XC888-8FFA 5V     | -                          | 09980163 <sub>H</sub> | 0B980163 <sub>H</sub> |  |  |  |  |  |  |

| XC886CM-6FFA 5V   | -                          | 099D1502 <sub>H</sub> | 0B9D1502 <sub>H</sub> |  |  |  |  |  |  |

| XC888CM-6FFA 5V   | -                          | 099D1503 <sub>H</sub> | 0B9D1503 <sub>H</sub> |  |  |  |  |  |  |

| XC886C-6FFA 5V    | -                          | 099D1542 <sub>H</sub> | 0B9D1542 <sub>H</sub> |  |  |  |  |  |  |

| XC888C-6FFA 5V    | -                          | 099D1543 <sub>H</sub> | 0B9D1543 <sub>H</sub> |  |  |  |  |  |  |

| XC886-6FFA 5V     | -                          | 099D1562 <sub>H</sub> | 0B9D1562 <sub>H</sub> |  |  |  |  |  |  |

| XC888-6FFA 5V     | -                          | 099D1563 <sub>H</sub> | 0B9D1563 <sub>H</sub> |  |  |  |  |  |  |

| ROM Devices       |                            |                       |                       |  |  |  |  |  |  |

| XC886CLM-8RFA 3V3 | 22400502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

| XC888CLM-8RFA 3V3 | 22400503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

| XC886LM-8RFA 3V3  | 22400522 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

| XC888LM-8RFA 3V3  | 22400523 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

| XC886CLM-6RFA 3V3 | 22411502 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

| XC888CLM-6RFA 3V3 | 22411503 <sub>H</sub>      | -                     | -                     |  |  |  |  |  |  |

#### Table 38 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                 | Symbol                |    | Limit                   | Values                 | Unit | Test Conditions                                        |

|---------------------------------------------------------------------------|-----------------------|----|-------------------------|------------------------|------|--------------------------------------------------------|

|                                                                           |                       |    | min.                    | max.                   | 1    |                                                        |

| Input high voltage at XTAL1                                               | V <sub>IHX</sub>      | SR | $0.7 \times V_{ m DDC}$ | V <sub>DDC</sub> + 0.5 | V    |                                                        |

| Pull-up current                                                           | I <sub>PU</sub>       | SR | _                       | -5                     | μA   | $V_{\mathrm{IHP,min}}$                                 |

|                                                                           |                       |    | -50                     | _                      | μA   | $V_{ILP,max}$                                          |

| Pull-down current                                                         | $I_{\rm PD}$          | SR | -                       | 5                      | μA   | $V_{ILP,max}$                                          |

|                                                                           |                       |    | 50                      | -                      | μA   | V <sub>IHP,min</sub>                                   |

| Input leakage current                                                     | I <sub>OZ1</sub>      | СС | -1                      | 1                      | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 125^{\circ}C^{2)}$ |

| Input current at XTAL1                                                    | $I_{ILX}$             | CC | - 10                    | 10                     | μA   |                                                        |

| Overload current on any pin                                               | I <sub>OV</sub>       | SR | -5                      | 5                      | mA   |                                                        |

| Absolute sum of<br>overload currents                                      | $\Sigma  I_{\rm OV} $ | SR | -                       | 25                     | mA   | 3)                                                     |

| Voltage on any pin during $V_{\rm DDP}$ power off                         | V <sub>PO</sub>       | SR | -                       | 0.3                    | V    | 4)                                                     |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | I <sub>M</sub> SR     | SR | -                       | 15                     | mA   |                                                        |

| Maximum current for all pins (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )  | $\Sigma  I_{M} $      | SR | -                       | 90                     | mA   |                                                        |

| Maximum current into $V_{\text{DDP}}$                                     | I <sub>mvddp</sub>    | SR | -                       | 120                    | mA   | 3)                                                     |

| Maximum current out of $V_{SS}$                                           | I <sub>MVSS</sub>     | SR | -                       | 120                    | mA   | 3)                                                     |

Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

2) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.

3) Not subjected to production test, verified by design/characterization.

4) Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when  $V_{\text{DDP}}$  is powered off.

## 4.3.3 Power-on Reset and PLL Timing

**Table 49** provides the characteristics of the power-on reset and PLL timing in the XC886/888.

| Table 46 | Power-On Reset and PLL Timing (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|          |                                                            |

| Parameter                           | Symbol             |    | Lir  | Limit Values |      |    | Test Conditions                                                              |

|-------------------------------------|--------------------|----|------|--------------|------|----|------------------------------------------------------------------------------|

|                                     |                    |    | min. | typ.         | max. |    |                                                                              |

| Pad operating voltage               | $V_{PAD}$          | CC | 2.3  | -            | -    | V  | 1)                                                                           |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | CC | -    | -            | 500  | ns | 1)                                                                           |

| Flash initialization time           | t <sub>FINIT</sub> | CC | _    | 160          | -    | μS | 1)                                                                           |

| RESET hold time                     | t <sub>RST</sub>   | SR | -    | 500          | _    | μS | $V_{\rm DDP}$ rise time<br>(10% – 90%) $\leq$<br>500 $\mu$ s <sup>1)2)</sup> |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -    | -            | 200  | μS | 1)                                                                           |

| PLL accumulated jitter              | D <sub>P</sub>     |    | _    | _            | 0.7  | ns | 1)3)                                                                         |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5 V).

3) PLL lock at 96 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 48 and P = 1.

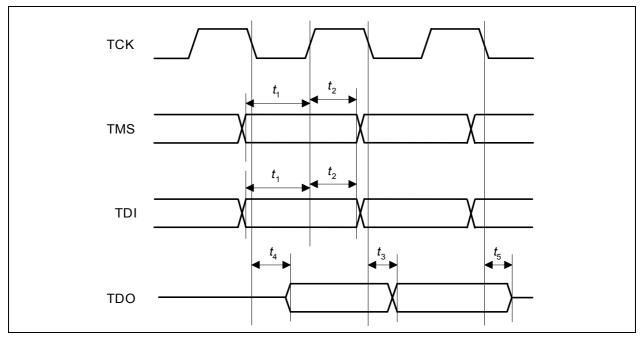

| Table 50JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd) |                       |    |     |      |      |                           |  |  |

|-----------------------------------------------------------------------|-----------------------|----|-----|------|------|---------------------------|--|--|

| Parameter                                                             | Symbol                |    | Lir | nits | Unit | Test                      |  |  |

|                                                                       |                       |    | min | max  |      | Conditions                |  |  |

| TDO high impedance to valid                                           | <i>t</i> <sub>4</sub> | CC | -   | 27   | ns   | 5V Device <sup>1)</sup>   |  |  |

| output from TCK                                                       |                       |    | -   | 36   | ns   | 3.3V Device <sup>1)</sup> |  |  |

| TDO valid output to high                                              | <i>t</i> <sub>5</sub> | CC | -   | 22   | ns   | 5V Device <sup>1)</sup>   |  |  |

| impedance from TCK                                                    |                       |    | -   | 28   | ns   | 3.3V Device <sup>1)</sup> |  |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

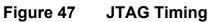

### 4.3.7 SSC Master Mode Timing

Table 51 provides the characteristics of the SSC timing in the XC886/888.

| Table 51 | SSC Master Mode Timing (Operating Conditions apply; CL = 50 pF) |

|----------|-----------------------------------------------------------------|

|----------|-----------------------------------------------------------------|

| Parameter            | Syn                   | nbol | Limi               | t Values | Unit | Test       |  |

|----------------------|-----------------------|------|--------------------|----------|------|------------|--|

|                      |                       |      | min.               | max.     |      | Conditions |  |

| SCLK clock period    | t <sub>0</sub>        | CC   | 2*T <sub>SSC</sub> | -        | ns   | 1)2)       |  |

| MTSR delay from SCLK | t <sub>1</sub>        | CC   | 0                  | 8        | ns   | 2)         |  |

| MRST setup to SCLK   | <i>t</i> <sub>2</sub> | SR   | 24                 | -        | ns   | 2)         |  |

| MRST hold from SCLK  | t <sub>3</sub>        | SR   | 0                  | -        | ns   | 2)         |  |

1)  $T_{SSCmin} = T_{CPU} = 1/f_{CPU}$ . When  $f_{CPU} = 24$  MHz,  $t_0 = 83.3$  ns.  $T_{CPU}$  is the CPU clock period.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 52 SSC Master Mode Timing