Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 13x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-UFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f098ccu6 |

#### **Description** 2

The STM32F098CC/RC/VC microcontrollers incorporate the high-performance ARM® Cortex®-M0 32-bit RISC core operating at up to 48 MHz frequency, high-speed embedded memories (256 Kbytes of Flash memory and 32 Kbytes of SRAM), and an extensive range of enhanced peripherals and I/Os. The device offers standard communication interfaces (two I<sup>2</sup>Cs, two SPIs/one I<sup>2</sup>S, one HDMI CEC and up to eight USARTs), one CAN, one 12-bit ADC, one 12-bit DAC with two channels, seven 16-bit timers, one 32-bit timer and an advanced-control PWM timer.

The STM32F098CC/RC/VC microcontrollers operate in the -40 to +85 °C and -40 to +105 °C temperature ranges, at a 1.8 V ± 8% power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

The STM32F098CC/RC/VC microcontrollers include devices in seven different package ranging from 48 pins to 100 pins with a die form also available upon request. Depending on the device chosen, different sets of peripherals are included.

These features make the STM32F098CC/RC/VC microcontrollers suitable for a wide range of applications such as application control and user interfaces, hand-held equipment, A/V receivers and digital TV, PC peripherals, gaming and GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms and HVACs.

DocID026967 Rev 4 10/128

### 3 Functional overview

Figure 1 shows the general block diagram of the STM32F098CC/RC/VC devices.

# 3.1 ARM®-Cortex®-M0 core

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 is a generation of ARM 32-bit RISC processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M0 processors feature exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The STM32F098CC/RC/VC devices embed ARM core and are compatible with all ARM tools and software.

#### 3.2 Memories

The device has the following features:

- 32 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.

- The non-volatile memory is divided into two arrays:

- 256 Kbytes of embedded Flash memory for programs and data

- Option bytes

The option bytes are used to write-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex<sup>®</sup>-M0 serial wire) and boot in RAM selection disabled

#### 3.3 Boot modes

At startup, the boot pin and boot selector option bits are used to select one of the three boot options:

- boot from User Flash memory

- boot from System Memory

- boot from embedded SRAM

The boot pin is shared with the standard GPIO and can be disabled through the boot selector option bits. The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART on pins PA14/PA15 or PA9/PA10 or I<sup>2</sup>C on pins PB6/PB7.

### 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the  $V_{BAT}$  battery voltage using the internal ADC channel ADC\_IN18. As the  $V_{BAT}$  voltage may be higher than  $V_{DDA}$ , and thus outside the ADC input range, the  $V_{BAT}$  pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the  $V_{BAT}$  voltage.

### 3.11 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This digital Interface supports the following features:

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

Six DAC trigger inputs are used in the device. The DAC is triggered through the timer trigger outputs and the DAC interface is generating its own DMA requests.

# 3.12 Comparators (COMP)

The device embeds two fast rail-to-rail low-power comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pins

- Internal reference voltage or submultiple (1/4, 1/2, 3/4). Refer to *Table 25: Embedded internal reference voltage* for the value and precision of the internal reference voltage.

Both comparators can wake up from STOP mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

# 3.13 Touch sensing controller (TSC)

The STM32F098CC/RC/VC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation

introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists in charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate. For operation, one capacitive sensing GPIO in each group is connected to an external capacitor and cannot be used as effective touch sensing channel.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

Table 4. Capacitive sensing GPIOs available on STM32F098CC/RC/VC devices

| Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |

| 1     | TSC_G1_IO2                     | PA1         |

| Į     | TSC_G1_IO3                     | PA2         |

|       | TSC_G1_IO4                     | PA3         |

|       | TSC_G2_IO1                     | PA4         |

| 2     | TSC_G2_IO2                     | PA5         |

| 2     | TSC_G2_IO3                     | PA6         |

|       | TSC_G2_IO4                     | PA7         |

|       | TSC_G3_IO1                     | PC5         |

| 3     | TSC_G3_IO2                     | PB0         |

|       | TSC_G3_IO3                     | PB1         |

|       | TSC_G4_IO1                     | PA9         |

| 4     | TSC_G4_IO2                     | PA10        |

| 4     | TSC_G4_IO3                     | PA11        |

|       | TSC_G4_IO4                     | PA12        |

| Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|-------------|

|       | TSC_G5_IO1                     | PB3         |

| 5     | TSC_G5_IO2                     | PB4         |

| 3     | TSC_G5_IO3                     | PB6         |

|       | TSC_G5_IO4                     | PB7         |

|       | TSC_G6_IO1                     | PB11        |

| 6     | TSC_G6_IO2                     | PB12        |

| 0     | TSC_G6_IO3                     | PB13        |

|       | TSC_G6_IO4                     | PB14        |

|       | TSC_G7_IO1                     | PE2         |

| 7     | TSC_G7_IO2                     | PE3         |

| ,     | TSC_G7_IO3                     | PE4         |

|       | TSC_G7_IO4                     | PE5         |

|       | TSC_G8_IO1                     | PD12        |

| 8     | TSC_G8_IO2                     | PD13        |

| 0     | TSC_G8_IO3                     | PD14        |

|       | TSC_G8_IO4                     | PD15        |

Table 5. Number of capacitive sensing channels available on STM32F098CC/RC/VC devices

| Amala a 1/O amana | Number of capacitive sensing channels |             |             |  |  |  |  |  |

|-------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|

| Analog I/O group  | STM32F098Vx                           | STM32F098Rx | STM32F098Cx |  |  |  |  |  |

| G1                | 3                                     | 3           | 3           |  |  |  |  |  |

| G2                | 3                                     | 3           | 3           |  |  |  |  |  |

| G3                | 2                                     | 2           | 1           |  |  |  |  |  |

| G4                | 3                                     | 3           | 3           |  |  |  |  |  |

Table 5. Number of capacitive sensing channels available on STM32F098CC/RC/VC devices (continued)

| Analog I/O group                      | Number of capacitive sensing channels |             |             |  |  |  |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|--|

| Analog I/O group                      | STM32F098Vx                           | STM32F098Rx | STM32F098Cx |  |  |  |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G6                                    | 3                                     | 3           | 3           |  |  |  |  |  |

| G7                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| G8                                    | 3                                     | 0           | 0           |  |  |  |  |  |

| Number of capacitive sensing channels | 23                                    | 17          | 16          |  |  |  |  |  |

# 3.14 Timers and watchdogs

The STM32F098CC/RC/VC devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 6 compares the features of the different timers.

Table 6. Timer feature comparison

| Timer<br>type    | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare channels | Complementary outputs |

|------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|--------------------------|-----------------------|

| Advanced control | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | 3                     |

|                  | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | -                     |

|                  | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | -                     |

| General purpose  | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                        | -                     |

|                  | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                        | 1                     |

|                  | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                        | 1                     |

| Basic            | TIM6<br>TIM7   | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                        | -                     |

### 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI\_CEC controller to wakeup the MCU from Stop mode on data reception.

## 3.20 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

# 3.21 Clock recovery system (CRS)

The STM32F098CC/RC/VC embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.22 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

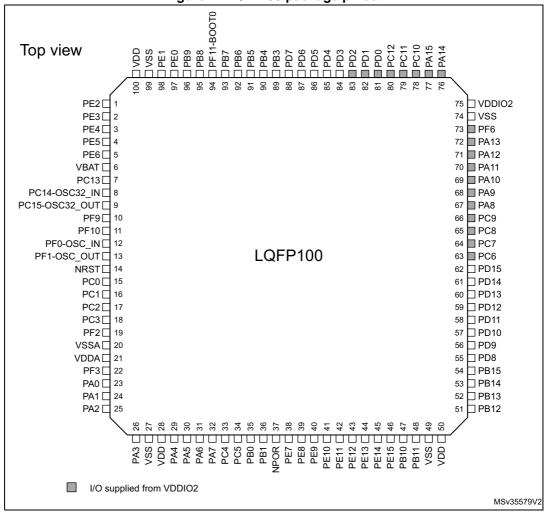

Figure 4. LQFP100 package pinout

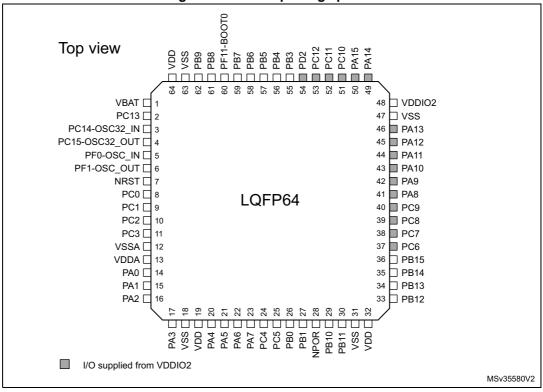

Figure 6. LQFP64 package pinout

Table 12. STM32F098CC/RC/VC pin definitions (continued)

|          | Pi      | n nui   | nber   | s       |                 |                                      |          | -             |       | Pin function                                                                     | ns                                             |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------|------------------------------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                              | Additional<br>functions                        |

| H1       | 15      | E3      | 8      | E7      | -               | PC0                                  | I/O      | TTa           |       | EVENTOUT,<br>USART6_TX,<br>USART7_TX                                             | ADC_IN10                                       |

| J2       | 16      | E2      | 9      | F8      | ı               | PC1                                  | I/O      | ТТа           |       | EVENTOUT,<br>USART6_RX,<br>USART7_RX                                             | ADC_IN11                                       |

| J3       | 17      | F2      | 10     | D6      | ı               | PC2                                  | I/O      | ТТа           |       | SPI2_MISO, I2S2_MCK,<br>EVENTOUT, USART8_TX                                      | ADC_IN12                                       |

| K2       | 18      | G1      | 11     | E6      | į               | PC3                                  | I/O      | TTa           |       | SPI2_MOSI, I2S2_SD,<br>EVENTOUT, USART8_RX                                       | ADC_IN13                                       |

| J1       | 19      | ı       | ı      | -       | ı               | PF2                                  | I/O      | FT            |       | EVENTOUT,<br>USART7_TX,<br>USART7_CK_RTS                                         | WKUP8                                          |

| K1       | 20      | F1      | 12     | G8      | 8               | VSSA                                 | S        | i             |       | Analog groui                                                                     | nd                                             |

| M1       | 21      | H1      | 13     | Н8      | 9               | VDDA                                 | S        | -             |       | Analog power s                                                                   | upply                                          |

| L1       | 22      | 1       | -      | -       | 1               | PF3                                  | I/O      | FT            |       | EVENTOUT,<br>USART7_RX,<br>USART6_CK_RTS                                         |                                                |

| L2       | 23      | G2      | 14     | F7      | 10              | PA0                                  | I/O      | TTa           |       | USART2_CTS,<br>TIM2_CH1_ETR,<br>TSC_G1_IO1,<br>USART4_TX<br>COMP1_OUT            | RTC_TAMP2,<br>WKUP1,<br>ADC_IN0,<br>COMP1_INM6 |

| M2       | 24      | H2      | 15     | F6      | 11              | PA1                                  | I/O      | ТТа           |       | USART2_RTS,<br>TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX,<br>EVENTOUT | ADC_IN1,<br>COMP1_INP                          |

| K3       | 25      | F3      | 16     | E5      | 12              | PA2                                  | I/O      | ТТа           |       | USART2_TX, TIM2_CH3,<br>TIM15_CH1,<br>TSC_G1_IO3<br>COMP2_OUT                    | ADC_IN2,<br>WKUP4,<br>COMP2_INM6               |

| L3       | 26      | G3      | 17     | Н7      | 13              | PA3                                  | I/O      | TTa           |       | USART2_RX,TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4                                  | ADC_IN3,<br>COMP2_INP                          |

| D3       | 27      | C2      | 18     | G7      | -               | VSS                                  | S        | -             |       | Ground                                                                           |                                                |

Table 19. STM32F098CC/RC/VC peripheral register boundary addresses (continued)

| Bus | Boundary address          | Size  | Peripheral    |

|-----|---------------------------|-------|---------------|

|     | 0x4001 5C00 - 0x4001 7FFF | 9 KB  | Reserved      |

|     | 0x4001 5800 - 0x4001 5BFF | 1 KB  | DBGMCU        |

|     | 0x4001 4C00 - 0x4001 57FF | 3 KB  | Reserved      |

|     | 0x4001 4800 - 0x4001 4BFF | 1 KB  | TIM17         |

|     | 0x4001 4400 - 0x4001 47FF | 1 KB  | TIM16         |

|     | 0x4001 4000 - 0x4001 43FF | 1 KB  | TIM15         |

|     | 0x4001 3C00 - 0x4001 3FFF | 1 KB  | Reserved      |

|     | 0x4001 3800 - 0x4001 3BFF | 1 KB  | USART1        |

|     | 0x4001 3400 - 0x4001 37FF | 1 KB  | Reserved      |

|     | 0x4001 3000 - 0x4001 33FF | 1 KB  | SPI1/I2S1     |

| APB | 0x4001 2C00 - 0x4001 2FFF | 1 KB  | TIM1          |

|     | 0x4001 2800 - 0x4001 2BFF | 1 KB  | Reserved      |

|     | 0x4001 2400 - 0x4001 27FF | 1 KB  | ADC           |

|     | 0x4001 2000 - 0x4001 23FF | 1 KB  | Reserved      |

|     | 0x4001 1C00 – 0x4001 1FFF | 1 KB  | USART8        |

|     | 0x4001 1800 – 0x4001 1BFF | 1 KB  | USART7        |

|     | 0x4001 1400 – 0x4001 17FF | 1 KB  | USART6        |

|     | 0x4001 0800 - 0x4001 13FF | 3 KB  | Reserved      |

|     | 0x4001 0400 - 0x4001 07FF | 1 KB  | EXTI          |

|     | 0x4001 0000 - 0x4001 03FF | 1 KB  | SYSCFG + COMP |

|     | 0x4000 8000 - 0x4000 FFFF | 32 KB | Reserved      |

1. Data based on characterization results, not tested in production unless otherwise specified.

Table 27. Typical and maximum current consumption in Stop mode

|                 | <u>_</u>       | S                   |         | Тур     | @ V <sub>D</sub> | <sub>DA</sub> (V | <sub>DD</sub> = 1 | l.8 V)  |         |                        | Max                    |                         |      |

|-----------------|----------------|---------------------|---------|---------|------------------|------------------|-------------------|---------|---------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter      | Condition           | = 1.8 V | = 2.0 V | = 2.4 V          | = 2.7 V          | = 3.0 V           | = 3.3 V | = 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

| I <sub>DD</sub> | Supply current | All oscillators OFF |         |         |                  | 0.6              |                   |         |         | 2.4                    | 33                     | 78                      | μA   |

| I <sub>DD</sub> | in Stop mode   | All Oscillators OFF | 0.9     | 0.9     | 1.0              | 1.0              | 1.0               | 1.1     | 1.2     | 2.5                    | 3.0                    | 3.7                     | μΑ   |

Table 28. Typical and maximum current consumption from the  $\mathrm{V}_{\mathrm{DDA}}$  supply

|                  | e.                |                       |                    |                      | V <sub>DDA</sub> | = 2.4 V             | 1      |     | V <sub>DDA</sub> | = 3.6 \ |                  |      |     |     |     |  |

|------------------|-------------------|-----------------------|--------------------|----------------------|------------------|---------------------|--------|-----|------------------|---------|------------------|------|-----|-----|-----|--|

| Symbol           | Para-meter        | Conditions (1)        | f <sub>HCLK</sub>  |                      | М                | ax @ T <sub>A</sub> | (2)    |     | M                | ax @ T  | A <sup>(2)</sup> | Unit |     |     |     |  |

|                  | Para              |                       |                    | Тур                  | 25 °C            | 85 °C               | 105 °C | Тур | 25 °C            | 85 °C   | 105 °C           |      |     |     |     |  |

|                  |                   | HSI48                 | 48 MHz             | 311                  | 332              | 337                 | 346    | 315 | 333              | 340     | 349              |      |     |     |     |  |

|                  |                   | HSE                   | 48 MHz             | 146                  | 167              | 177                 | 180    | 159 | 180              | 191     | 196              |      |     |     |     |  |

|                  | Supply current in | bypass,               | 32 MHz             | 100                  | 118              | 124                 | 126    | 108 | 126              | 134     | 137              |      |     |     |     |  |

|                  | Run or            | PLL on                | 24 MHz             | 79                   | 95               | 98                  | 99     | 85  | 100              | 105     | 108              |      |     |     |     |  |

|                  | Sleep<br>mode,    | HSE                   | 8 MHz              | 2                    | 3                | 3                   | 4      | 3   | 3                | 4       | 4                |      |     |     |     |  |

| I <sub>DDA</sub> |                   | executing from Flash  | bypass,<br>PLL off | 1 MHz                | 2                | 2                   | 3      | 3   | 2                | 3       | 3                | 4    | μΑ  |     |     |  |

|                  |                   |                       | from Flash         | from                 | from             |                     | 48 MHz | 212 | 242              | 253     | 257              | 234  | 261 | 274 | 280 |  |

|                  |                   |                       |                    | HSI clock,<br>PLL on | 32 MHz           | 165                 | 193    | 202 | 203              | 183     | 206              | 215  | 219 |     |     |  |

|                  |                   | -                     | 24 MHz             | 143                  | 170              | 176                 | 177    | 160 | 179              | 186     | 189              |      |     |     |     |  |

|                  |                   | HSI clock,<br>PLL off | 8 MHz              | 64                   | 82               | 84                  | 85     | 76  | 88               | 91      | 92               |      |     |     |     |  |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

<sup>2.</sup> Data based on characterization results, not tested in production unless otherwise specified.

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 32: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\mbox{\scriptsize SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

V<sub>DDIOx</sub> is the I/O supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

Table 31. Switching output I/O current consumption

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                                | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур                        | Unit                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|-----------------|-------------|------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------|------|----|

|                 |             |                                                                                          | 2 MHz                                        | 0.09                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 4 MHz                                        | 0.17                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $V_{DDIOx} = 1.8 \text{ V}$                                                              | 8 MHz                                        | 0.34                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$                              | 18 MHz                                       | 0.79                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | IIVI EXI S                                                                               | 36 MHz                                       | 1.50                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | V <sub>DDIOx</sub> = 1.8 V<br>C <sub>EXT</sub> = 10 pF                                   | 48 MHz                                       | 2.06                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 2 MHz                                        | 0.13                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 4 MHz                                        | 0.26                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 8 MHz                                        | 0.50                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 | I/O current | $C_{\text{EXT}} - 10 \text{ pr}$<br>$C = C_{\text{INT}} + C_{\text{EXT}} + C_{\text{S}}$ | 18 MHz                                       | 1.18                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | IIII EXI O                                                                               | 36 MHz                                       | 2.27                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 48 MHz                                       | 3.03                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 2 MHz                                        | 0.18                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

| I <sub>SW</sub> | consumption | V <sub>DDIOx</sub> = 1.8 V<br>C <sub>EXT</sub> = 22 pF                                   | V <sub>DDIOx</sub> = 1.8 V                   | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | V <sub>DDIOx</sub> = 1.8 V | 4 MHz | 0.36 | mA |

|                 |             |                                                                                          | 8 MHz                                        | 0.69                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                                                          | 18 MHz                                       | 1.60                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 36 MHz                                       | 3.27                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 2 MHz                                        | 0.23                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | V <sub>DDIOx</sub> = 1.8 V                                                               | 4 MHz                                        | 0.45                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | C <sub>EXT</sub> = 33 pF                                                                 | 8 MHz                                        | 0.87                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                                                          | 18 MHz                                       | 2.0                        |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 36 MHz                                       | 3.7                        |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             |                                                                                          | 2 MHz                                        | 0.29                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $V_{DDIOx} = 1.8 \text{ V}$                                                              | 4 MHz                                        | 0.55                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | $C_{EXT} = 47 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$                             | 8 MHz                                        | 1.09                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |             | INT EXT O                                                                                | 18 MHz                                       | 2.43                       |                            |                            |                            |                            |                            |                            |                            |                            |       |      |    |

<sup>1.</sup>  $C_S = 5 pF$  (estimated value).

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 32*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in Table 20: Voltage characteristics

Table 32. Peripheral current consumption

|     | Peripheral               | Typical consumption at 25 °C | Unit       |  |  |

|-----|--------------------------|------------------------------|------------|--|--|

|     | BusMatrix <sup>(1)</sup> | 3.1                          |            |  |  |

|     | CRC                      | 2.0                          |            |  |  |

|     | DMA1                     | 5.5                          |            |  |  |

|     | DMA2                     | 5.1                          |            |  |  |

|     | Flash memory interface   | 15.4                         |            |  |  |

|     | GPIOA                    | 5.5                          |            |  |  |

| AHB | GPIOB                    | 5.4                          | μΑ/MHz     |  |  |

| AHD | GPIOC                    | 3.2                          | μΑνίνιι 12 |  |  |

|     | GPIOD                    | 3.1                          |            |  |  |

|     | GPIOE                    | 4.0                          |            |  |  |

|     | GPIOF                    | 2.5                          |            |  |  |

|     | SRAM                     | 0.8                          |            |  |  |

|     | TSC                      | SC 5.5                       |            |  |  |

|     | All AHB peripherals      | 61.0                         |            |  |  |

**Functional** susceptibility **Symbol Description** Unit **Positive** Negative injection injection Injected current on BOOT0 -0 NA Injected current on PF1 pin (FTf pin) -0 NA Injected current on PC0 pin (TTA pin) -0 +5 mΑ  $I_{IN,I}$ Injected current on PA4, PA5 pins with induced leakage -5 NA current on adjacent pins less than -20 µA Injected current on other FT and FTf pins, and on NPOR pin -5 NA Injected current on all other TC, TTa and RST pins -5 +5

Table 49. I/O current injection susceptibility

#### 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 23: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant.

Symbol **Parameter Conditions** Min Unit Тур Max TC and TTa I/O  $0.3 V_{DDIOx} + 0.07^{(1)}$ Low level input FT and FTf I/O 0.475 V<sub>DDIOx</sub>-0.2<sup>(1)</sup> V  $V_{IL}$ voltage All I/Os 0.3 V<sub>DDIOx</sub> TC and TTa I/O 0.445 V<sub>DDIOx</sub>+0.398<sup>(1)</sup> High level input  $0.5 V_{DDIOx} + 0.2^{(1)}$ FT and FTf I/O V  $V_{IH}$ voltage All I/Os 0.7 V<sub>DDIOx</sub> 200(1) TC and TTa I/O Schmitt trigger  $V_{\text{hys}}$ mV hysteresis  $100^{(1)}$ FT and FTf I/O TC, FT and FTf I/O TTa in digital mode ± 0.1  $V_{SS} \le V_{IN} \le V_{DDIOx}$ TTa in digital mode 1 Input leakage  $V_{\text{DDIOx}} \le V_{\text{IN}} \le V_{\text{DDA}}$ μΑ  $I_{lkq}$ current<sup>(2)</sup> TTa in analog mode ± 0.2  $V_{SS} \le V_{IN} \le V_{DDA}$ FT and FTf I/O 10  $V_{DDIOx} \le V_{IN} \le 5 V$

Table 50. I/O static characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOX</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 20: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see Table 20: Voltage characteristics).

#### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

Table 51. Output voltage characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                               | Conditions                                                 | Min                     | Max   | Unit |  |

|-----------------------------------|---------------------------------------------------------|------------------------------------------------------------|-------------------------|-------|------|--|

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | CMOS port <sup>(2)</sup>                                   | -                       | 0.4   | .,   |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | $ I_{IO}  = 8 \text{ mA}$<br>$V_{DDIOx} \ge 2.7 \text{ V}$ | V <sub>DDIOx</sub> -0.4 | -     | V    |  |

| V <sub>OL</sub>                   | Output low level voltage for an I/O pin                 | TTL port <sup>(2)</sup>                                    | -                       | 0.4   | .,   |  |

| V <sub>OH</sub>                   | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 8 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V     | 2.4                     | -     | V    |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 20 mA                                  | -                       | 1.3   | V    |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2.7 V                                 | V <sub>DDIOx</sub> -1.3 | -     |      |  |

| V <sub>OL</sub> <sup>(3)</sup>    | Output low level voltage for an I/O pin                 | I <sub>IO</sub>   = 6 mA                                   | -                       | - 0.4 |      |  |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin                | V <sub>DDIOx</sub> ≥ 2 V                                   | V <sub>DDIOx</sub> -0.4 | -     | \ \  |  |

| V <sub>OL</sub> <sup>(4)</sup>    | Output low level voltage for an I/O pin                 | II I = 4 m A                                               | -                       | 0.4   | V    |  |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub>   = 4 mA                                   | V <sub>DDIOx</sub> -0.4 | -     | V    |  |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in Fm+ mode | I <sub>IO</sub>   = 20 mA<br>V <sub>DDIOx</sub> ≥ 2.7 V    | -                       | 0.4   | ٧    |  |

|                                   | Thir mode                                               | I <sub>IO</sub>   = 10 mA                                  | -                       | 0.4   | V    |  |

The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in Table 20:

Voltage characteristics, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings ΣI<sub>IO</sub>.

- 2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

- 3. Data based on characterization results. Not tested in production.

- 4. Data based on characterization results. Not tested in production.

| Symbol                 | Parameter                                       | Conditions        | Min                                       | Тур                | Мах                                         | Unit |

|------------------------|-------------------------------------------------|-------------------|-------------------------------------------|--------------------|---------------------------------------------|------|

| V <sub>IL(NPOR)</sub>  | NPOR Input low level voltage                    | -                 | -                                         | -                  | 0.475 V <sub>DDA</sub> - 0.2 <sup>(1)</sup> |      |

| V <sub>IH(NPOR)</sub>  | NPOR Input high level voltage                   | -                 | 0.5 V <sub>DDA</sub> + 0.2 <sup>(1)</sup> | -                  | -                                           | V    |

| V <sub>hys(NPOR)</sub> | NPOR Schmitt trigger voltage hysteresis         | -                 | -                                         | 100 <sup>(1)</sup> | -                                           | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$ | 25                                        | 40                 | 55                                          | kΩ   |

Table 54. NPOR pin characteristics

#### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under the conditions summarized in *Table 23: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

**Table 55. ADC characteristics**

| Symbol                             | Parameter                                     | Conditions Min                                  |       | Тур | Max       | Unit               |

|------------------------------------|-----------------------------------------------|-------------------------------------------------|-------|-----|-----------|--------------------|

| $V_{DDA}$                          | Analog supply voltage for ADC ON              | -                                               | 2.4   | -   | 3.6       | V                  |

| I <sub>DDA (ADC)</sub>             | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V                        | -     | 0.9 | -         | mA                 |

| f <sub>ADC</sub>                   | ADC clock frequency                           | -                                               | 0.6   | -   | 14        | MHz                |

| f <sub>S</sub> <sup>(2)</sup>      | Sampling rate                                 | 12-bit resolution                               | 0.043 | -   | 1         | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup>   | External trigger frequency                    | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | -     | -   | 823       | kHz                |

|                                    |                                               | 12-bit resolution                               | -     | -   | 17        | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range                      | -                                               | 0     | -   | $V_{DDA}$ | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>    | External input impedance                      | See Equation 1 and Table 56 for details         | -     | -   | 50        | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>    | Sampling switch resistance                    | -                                               | -     | 1   | 1         | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>    | Internal sample and hold capacitor            | -                                               | -     | -   | 8         | pF                 |

| t <sub>CAL</sub> <sup>(2)(3)</sup> | Calibration times                             | f <sub>ADC</sub> = 14 MHz                       |       | 5.9 |           | μs                 |

| CAL` '\''                          | Calibration time                              | -                                               | 83    |     |           | 1/f <sub>ADC</sub> |

<sup>1.</sup> Guaranteed by design, not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

| Symbol                                 | Parameter                        | Conditions                                      | Min                                                                        | Тур | Max                                               | Unit                       |

|----------------------------------------|----------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | ADC_DR register ready latency    | ADC clock = HSI14                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

|                                        |                                  | ADC clock = PCLK/2                              | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | ADC clock = PCLK/4                              | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$         | 0.196                                                                      |     |                                                   | μs                         |

|                                        | Trigger conversion latency       | $f_{ADC} = f_{PCLK}/2$                          | 5.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| $t_{latr}^{(2)}$                       |                                  | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$         | 0.219                                                                      |     |                                                   | μs                         |

|                                        |                                  | $f_{ADC} = f_{PCLK}/4$                          | 10.5                                                                       |     |                                                   | 1/f <sub>PCLK</sub>        |

|                                        |                                  | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz  | 0.179                                                                      | -   | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion | f <sub>ADC</sub> = f <sub>HSI14</sub>           | -                                                                          | 1   | -                                                 | 1/f <sub>HSI14</sub>       |

| t <sub>S</sub> <sup>(2)</sup>          | Sampling time                    | f <sub>ADC</sub> = 14 MHz                       | 0.107                                                                      | -   | 17.1                                              | μs                         |

|                                        |                                  | -                                               | 1.5                                                                        | -   | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> (2)                  | Stabilization time               | -                                               | 14                                                                         |     |                                                   | 1/f <sub>ADC</sub>         |

| t <sub>CONV</sub> <sup>(2)</sup>       | Total conversion time            | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | 1                                                                          | -   | 18                                                | μs                         |

|                                        | (including sampling time)        | 12-bit resolution                               | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                                                   | 1/f <sub>ADC</sub>         |

Table 55. ADC characteristics (continued)

- 2. Guaranteed by design, not tested in production.

- 3. Specified value includes only ADC timing. It does not include the latency of the register access.

- 4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

# Equation 1: $R_{AIN}$ max formula

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

Table 56.  $R_{AIN}$  max for  $f_{ADC} = 14$  MHz

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |

|-------------------------|---------------------|------------------------------------------|

| 1.5                     | 0.11                | 0.4                                      |

| 7.5                     | 0.54                | 5.9                                      |

| 13.5                    | 0.96                | 11.4                                     |

<sup>1.</sup> During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on IDD should be taken into account.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

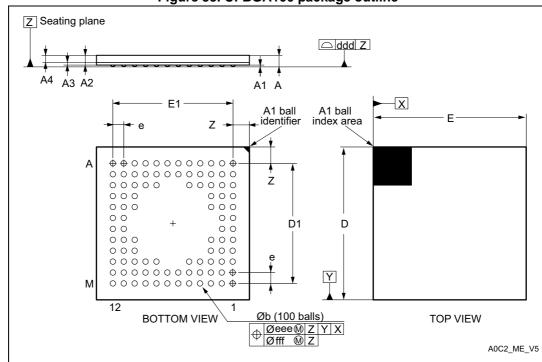

# 7.1 UFBGA100 package information

UFBGA100 is a 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra-fine-profile ball grid array package.

Figure 33. UFBGA100 package outline

1. Drawing is not to scale.

Table 68. UFBGA100 package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min.        | Тур.  | Max.  | Min.                  | Тур.   | Max.   |  |

| Α      | -           | -     | 0.600 | -                     | -      | 0.0236 |  |

| A1     | -           | -     | 0.110 | -                     | -      | 0.0043 |  |

| A2     | -           | 0.450 | -     | -                     | 0.0177 | -      |  |

| A3     | -           | 0.130 | -     | -                     | 0.0051 | 0.0094 |  |

| A4     | -           | 0.320 | -     | -                     | 0.0126 | -      |  |

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 53. UFQFPN48 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.