Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | ·                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-UFBGA                                                              |

| Supplier Device Package    | 64-UFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f098rch6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Orde | ering int | ormation                                    |     |

|---|------|-----------|---------------------------------------------|-----|

| 0 | Orde |           |                                             |     |

|   |      | 7.8.2     | Selecting the product temperature range     |     |

|   | 7.0  | 7.8.1     | Reference document                          |     |

|   | 7.8  |           | al characteristics                          |     |

|   | 7.7  |           | PN48 package information                    |     |

|   | 7.6  |           | 8 package information                       |     |

|   | 7.5  | LQFP6     | 4 package information                       |     |

|   | 7.4  | WLCSI     | <sup>D</sup> 64 package information         | 109 |

|   | 7.3  | UFBGA     | A64 package information                     | 106 |

|   | 7.2  | LQFP1     | 00 package information                      | 103 |

|   | 7.1  | UFBGA     | A100 package information                    | 100 |

| 7 | Pack | age info  | ormation                                    | 100 |

|   |      | 6.3.21    | Communication interfaces                    | 94  |

|   |      | 6.3.20    |                                             |     |

|   |      | 6.3.19    | V <sub>BAT</sub> monitoring characteristics |     |

|   |      | 6.3.18    | Temperature sensor characteristics          |     |

|   |      | 6.3.17    | Comparator characteristics                  |     |

|   |      | 6.3.16    | DAC electrical specifications               | 89  |

|   |      | 6.3.15    | 12-bit ADC characteristics                  | 85  |

|   |      | 6.3.14    | NRST and NPOR pin characteristics           | 83  |

|   |      | 6.3.13    | I/O port characteristics                    |     |

|   |      | 6.3.12    | I/O current injection characteristics       |     |

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F098CC/RC/VC microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website *www.st.com*.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

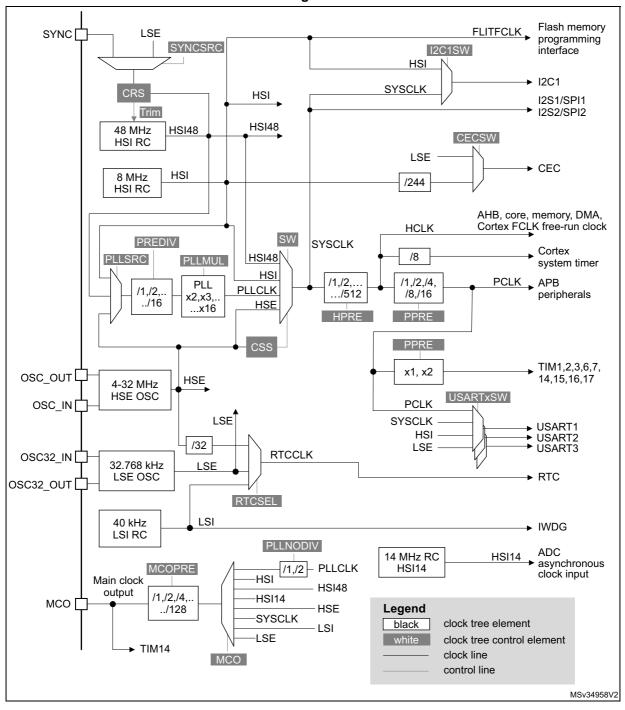

Figure 2. Clock tree

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

DocID026967 Rev 4

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

## 3.8 Direct memory access controller (DMA)

The 12-channel general-purpose DMAs (seven channels for DMA1 and five channels for DMA2) manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMAs support circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

## 3.9 Interrupts and events

#### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 87 GPIOs can be connected to the 16 external interrupt lines.

## 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC\_IN18. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

## 3.11 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This digital Interface supports the following features:

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

Six DAC trigger inputs are used in the device. The DAC is triggered through the timer trigger outputs and the DAC interface is generating its own DMA requests.

# 3.12 Comparators (COMP)

The device embeds two fast rail-to-rail low-power comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output pins

- Internal reference voltage or submultiple (1/4, 1/2, 3/4). Refer to *Table 25: Embedded internal reference voltage* for the value and precision of the internal reference voltage.

Both comparators can wake up from STOP mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

# 3.13 Touch sensing controller (TSC)

The STM32F098CC/RC/VC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation

DocID026967 Rev 4

can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

#### 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F098CC/RC/VC devices (see *Table 6* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

#### TIM2, TIM3

STM32F098CC/RC/VC devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### **TIM14**

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop mode capability

- Periodic wakeup unit with programmable resolution and period.

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- Three anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop mode on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop mode on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s), Fast mode (up to 400 kbit/s) and Fast Mode Plus (up to 1 Mbit/s) with extra output drive on most of the associated I/Os.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

| Table 7. 0 | Comparison of | I <sup>2</sup> C analog a | and digital filters |

|------------|---------------|---------------------------|---------------------|

|            |               |                           |                     |

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts

| USART modes/features <sup>(1)</sup>         | USART1<br>USART2<br>USART3 | USART4 | USART5<br>USART6<br>USART7<br>USART8 |  |

|---------------------------------------------|----------------------------|--------|--------------------------------------|--|

| Single-wire half-duplex communication       | Х                          | Х      | Х                                    |  |

| IrDA SIR ENDEC block                        | Х                          | -      | -                                    |  |

| LIN mode                                    | Х                          | -      | -                                    |  |

| Dual clock domain and wakeup from Stop mode | Х                          | -      | -                                    |  |

| Receiver timeout interrupt                  | Х                          | -      | -                                    |  |

| Modbus communication                        | Х                          | -      | -                                    |  |

| Auto baud rate detection                    | Х                          | -      | -                                    |  |

| Driver Enable                               | Х                          | Х      | Х                                    |  |

| Table 9. STM32F098CC/RC/VC USART im | plementation | (continued)  |  |

|-------------------------------------|--------------|--------------|--|

|                                     |              | (0011011000) |  |

1. X = supported.

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI1 and SPI2 respectively) supporting four different audio standards can operate as master or slave at half-duplex communication mode. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, they can output a clock for an external audio component at 256 times the sampling frequency.

| SPI features <sup>(1)</sup> | SPI1 and SPI2 |

|-----------------------------|---------------|

| Hardware CRC calculation    | Х             |

| Rx/Tx FIFO                  | Х             |

| NSS pulse mode              | Х             |

| I <sup>2</sup> S mode       | Х             |

| TI mode                     | Х             |

Table 10. STM32F098CC/RC/VC SPI/I<sup>2</sup>S implementation

1. X = supported.

| Table 15. Alternate functions selected through GPIOC_AFR registers for port C |                    |                     |           |  |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------|---------------------|-----------|--|--|--|--|--|

| Pin name                                                                      | AF0                | AF1                 | AF2       |  |  |  |  |  |

| PC0                                                                           | EVENTOUT USART7_TX |                     | USART6_TX |  |  |  |  |  |

| PC1                                                                           | EVENTOUT           | USART7_RX           | USART6_RX |  |  |  |  |  |

| PC2                                                                           | EVENTOUT           | SPI2_MISO, I2S2_MCK | USART8_TX |  |  |  |  |  |

| PC3                                                                           | EVENTOUT           | SPI2_MOSI, I2S2_SD  | USART8_RX |  |  |  |  |  |

| PC4                                                                           | EVENTOUT           | USART3_TX           | -         |  |  |  |  |  |

| PC5                                                                           | TSC_G3_IO1         | USART3_RX           | -         |  |  |  |  |  |

| PC6                                                                           | TIM3_CH1           | USART7_TX           | -         |  |  |  |  |  |

| PC7                                                                           | TIM3_CH2           | USART7_RX           | -         |  |  |  |  |  |

| PC8                                                                           | TIM3_CH3           | USART8_TX           | -         |  |  |  |  |  |

| PC9                                                                           | TIM3_CH4           | USART8_RX           | -         |  |  |  |  |  |

| PC10                                                                          | USART4_TX          | USART3_TX           | -         |  |  |  |  |  |

| PC11                                                                          | USART4_RX          | USART3_RX           | -         |  |  |  |  |  |

| PC12                                                                          | USART4_CK          | USART3_CK           | USART5_TX |  |  |  |  |  |

| PC13                                                                          | -                  | -                   | -         |  |  |  |  |  |

| PC14                                                                          |                    |                     | -         |  |  |  |  |  |

| PC15                                                                          | -                  | -                   | -         |  |  |  |  |  |

Table 15. Alternate functions selected through GPIOC\_AFR registers for port C

#### Table 16. Alternate functions selected through GPIOD\_AFR registers for port D

| Pin name | AF0        | AF1                 | AF2           |

|----------|------------|---------------------|---------------|

| PD0      | CAN_RX     | SPI2_NSS, I2S2_WS   | -             |

| PD1      | CAN_TX     | SPI2_SCK, I2S2_CK   | -             |

| PD2      | TIM3_ETR   | USART3_RTS          | USART5_RX     |

| PD3      | USART2_CTS | SPI2_MISO, I2S2_MCK | -             |

| PD4      | USART2_RTS | SPI2_MOSI, I2S2_SD  | -             |

| PD5      | USART2_TX  | -                   | -             |

| PD6      | USART2_RX  | -                   | -             |

| PD7      | USART2_CK  | -                   | -             |

| PD8      | USART3_TX  | -                   | -             |

| PD9      | USART3_RX  | -                   | -             |

| PD10     | USART3_CK  | -                   | -             |

| PD11     | USART3_CTS | -                   | -             |

| PD12     | USART3_RTS | TSC_G8_IO1          | USART8_CK_RTS |

| PD13     | USART8_TX  | TSC_G8_IO2          | -             |

| PD14     | USART8_RX  | TSC_G8_IO3          | -             |

| PD15     | CRS_SYNC   | TSC_G8_IO4          | USART7_CK_RTS |

| Bus | Boundary address          | Size  | Peripheral    |

|-----|---------------------------|-------|---------------|

|     | 0x4001 5C00 - 0x4001 7FFF | 9 KB  | Reserved      |

|     | 0x4001 5800 - 0x4001 5BFF | 1 KB  | DBGMCU        |

|     | 0x4001 4C00 - 0x4001 57FF | 3 KB  | Reserved      |

|     | 0x4001 4800 - 0x4001 4BFF | 1 KB  | TIM17         |

|     | 0x4001 4400 - 0x4001 47FF | 1 KB  | TIM16         |

|     | 0x4001 4000 - 0x4001 43FF | 1 KB  | TIM15         |

|     | 0x4001 3C00 - 0x4001 3FFF | 1 KB  | Reserved      |

|     | 0x4001 3800 - 0x4001 3BFF | 1 KB  | USART1        |

|     | 0x4001 3400 - 0x4001 37FF | 1 KB  | Reserved      |

|     | 0x4001 3000 - 0x4001 33FF | 1 KB  | SPI1/I2S1     |

| APB | 0x4001 2C00 - 0x4001 2FFF | 1 KB  | TIM1          |

|     | 0x4001 2800 - 0x4001 2BFF | 1 KB  | Reserved      |

|     | 0x4001 2400 - 0x4001 27FF | 1 KB  | ADC           |

|     | 0x4001 2000 - 0x4001 23FF | 1 KB  | Reserved      |

|     | 0x4001 1C00 – 0x4001 1FFF | 1 KB  | USART8        |

|     | 0x4001 1800 – 0x4001 1BFF | 1 KB  | USART7        |

|     | 0x4001 1400 – 0x4001 17FF | 1 KB  | USART6        |

|     | 0x4001 0800 - 0x4001 13FF | 3 KB  | Reserved      |

|     | 0x4001 0400 - 0x4001 07FF | 1 KB  | EXTI          |

|     | 0x4001 0000 - 0x4001 03FF | 1 KB  | SYSCFG + COMP |

|     | 0x4000 8000 - 0x4000 FFFF | 32 KB | Reserved      |

## Table 19. STM32F098CC/RC/VC peripheral register boundary addresses (continued)

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Symbol             | Parameter                                                     | Conditions                                      | Min      | Max                                  | Unit |  |  |

|--------------------|---------------------------------------------------------------|-------------------------------------------------|----------|--------------------------------------|------|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                  | -                                               | 0        | 48                                   | MHz  |  |  |

| f <sub>PCLK</sub>  | Internal APB clock frequency                                  | -                                               | 0        | 48                                   | MILZ |  |  |

| $V_{DD}$           | Standard operating voltage                                    | -                                               | 1.65     | 1.95                                 | V    |  |  |

| V <sub>DDIO2</sub> | I/O supply voltage                                            | Must not be supplied if $V_{DD}$ is not present | 1.65     | 3.6                                  | V    |  |  |

| V                  | Analog operating voltage<br>(ADC and DAC not used)            | Must have a potential equal                     | $V_{DD}$ | 3.6                                  | V    |  |  |

| V <sub>DDA</sub>   | Analog operating voltage<br>(ADC and DAC used)                | to or higher than V <sub>DD</sub>               | 2.4      | 3.6                                  | v    |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                                      | -                                               | 1.65     | 3.6                                  | V    |  |  |

|                    |                                                               | TC and RST I/O                                  | -0.3     | V <sub>DDIOx</sub> +0.3              |      |  |  |

| V <sub>IN</sub>    | I/O input voltage                                             | TTa and POR I/O                                 | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V    |  |  |

|                    |                                                               | FT and FTf I/O                                  | -0.3     | 5.2 <sup>(1)</sup>                   |      |  |  |

|                    |                                                               | UFBGA100                                        | -        | 364                                  |      |  |  |

|                    | LQFP100                                                       |                                                 | -        | 476                                  |      |  |  |

|                    | Power dissipation at $T_A = 85 \degree C$                     | LQFP64                                          | -        | 455                                  |      |  |  |

| $P_{D}$            | for suffix 6 or $T_A = 105$ °C for<br>suffix 7 <sup>(2)</sup> | WLCSP64                                         | - SP64 - |                                      | mW   |  |  |

|                    | suffix 7 <sup>(2)</sup>                                       | UFBGA64                                         | -        | 308                                  |      |  |  |

|                    |                                                               | LQFP48 - 37                                     |          | 370                                  |      |  |  |

|                    |                                                               | UFQFPN48                                        | -        | 625                                  |      |  |  |

|                    | Ambient temperature for the                                   | Maximum power dissipation                       | -40      | 85                                   | °C   |  |  |

| Та                 | suffix 6 version                                              | Low power dissipation <sup>(3)</sup>            | -40      | 105                                  | C    |  |  |

| IA                 | Ambient temperature for the                                   | Maximum power dissipation                       | -40      | 105                                  | °C   |  |  |

|                    | suffix 7 version                                              | Low power dissipation <sup>(3)</sup>            | -40      | 125                                  | Ĵ    |  |  |

#### Table 23. General operating conditions

1. For operation with a voltage higher than  $V_{DDIOX}$  + 0.3 V, the internal pull-up resistor must be disabled.

2. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $\mathsf{T}_J$  does not exceed  $\mathsf{T}_{Jmax}.$  See

In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.8: Thermal characteristics).

## 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 24* are derived from tests performed under the ambient temperature condition summarized in *Table 23*.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 26* to *Table 29* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

1. Data based on characterization results, not tested in production unless otherwise specified.

|                  | -s s           |                     |         | Тур     | @ V <sub>D</sub> | <sub>DA</sub> (V <sub>I</sub> | <sub>DD</sub> = 1 | .8 V)   |         |                          | Max                      |                            |      |

|------------------|----------------|---------------------|---------|---------|------------------|-------------------------------|-------------------|---------|---------|--------------------------|--------------------------|----------------------------|------|

| Symbol           | Parameter      | Conditions          | = 1.8 V | = 2.0 V | = 2.4 V          | = 2.7 V                       | = 3.0 V           | = 3.3 V | = 3.6 V | T <sub>A</sub> =<br>25 ℃ | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD</sub>  | Supply current |                     |         |         |                  | 0.6                           |                   |         |         | 2.4                      | 33                       | 78                         |      |

| I <sub>DDA</sub> | in Ston mode   | All oscillators OFF | 0.9     | 0.9     | 1.0              | 1.0                           | 1.0               | 1.1     | 1.2     | 2.5                      | 3.0                      | 3.7                        | μA   |

Table 27. Typical and maximum current consumption in Stop mode

#### Table 28. Typical and maximum current consumption from the $V_{\mbox{\scriptsize DDA}}$ supply

|                  | er                                                                    |                                               | V <sub>DDA</sub> = 2.4 V |     |       |                     | V <sub>DDA</sub> = 3.6 V |     |                                     |       |        |      |

|------------------|-----------------------------------------------------------------------|-----------------------------------------------|--------------------------|-----|-------|---------------------|--------------------------|-----|-------------------------------------|-------|--------|------|

| Symbol           | Para-meter                                                            | Conditions                                    | f <sub>HCLK</sub>        |     | м     | ax @ T <sub>A</sub> | (2)                      |     | Max @ T <sub>A</sub> <sup>(2)</sup> |       |        | Unit |

|                  | Para                                                                  |                                               |                          | Тур | 25 °C | 85 °C               | 105 °C                   | Тур | 25 °C                               | 85 °C | 105 °C |      |

|                  |                                                                       | HSI48                                         | 48 MHz                   | 311 | 332   | 337                 | 346                      | 315 | 333                                 | 340   | 349    |      |

|                  |                                                                       | HSE                                           | 48 MHz                   | 146 | 167   | 177                 | 180                      | 159 | 180                                 | 191   | 196    | -    |

|                  | Supply<br>current in<br>Run or<br>Sleep<br>mode,<br>code<br>executing | Supply bypass,<br>current in PLL on<br>Run or | 32 MHz                   | 100 | 118   | 124                 | 126                      | 108 | 126                                 | 134   | 137    |      |

|                  |                                                                       |                                               | 24 MHz                   | 79  | 95    | 98                  | 99                       | 85  | 100                                 | 105   | 108    |      |

|                  |                                                                       | mode, hypass                                  | 8 MHz                    | 2   | 3     | 3                   | 4                        | 3   | 3                                   | 4     | 4      |      |

| I <sub>DDA</sub> |                                                                       |                                               | 1 MHz                    | 2   | 2     | 3                   | 3                        | 2   | 3                                   | 3     | 4      | μA   |

|                  | from                                                                  |                                               | 48 MHz                   | 212 | 242   | 253                 | 257                      | 234 | 261                                 | 274   | 280    |      |

|                  | Flash<br>memorv                                                       | Flash HSI clock,<br>memory PLL on             | 32 MHz                   | 165 | 193   | 202                 | 203                      | 183 | 206                                 | 215   | 219    |      |

|                  | or RAM                                                                |                                               | 24 MHz                   | 143 | 170   | 176                 | 177                      | 160 | 179                                 | 186   | 189    |      |

|                  |                                                                       | HSI clock,<br>PLL off                         | 8 MHz                    | 64  | 82    | 84                  | 85                       | 76  | 88                                  | 91    | 92     |      |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

|                      |                                    |                                                                                  | Тур @ V <sub>BAT</sub> |       |       |       |       |       |                           |                           |                            |      |

|----------------------|------------------------------------|----------------------------------------------------------------------------------|------------------------|-------|-------|-------|-------|-------|---------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                          | Conditions                                                                       | 1.65 V                 | 1.8 V | 2.4 V | 2.7 V | 3.3 V | 3.6 V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

| I <sub>DD_VBAT</sub> | RTC<br>domain<br>supply<br>current | LSE & RTC ON; "Xtal<br>mode": lower driving<br>capability;<br>LSEDRV[1:0] = '00' | 0.5                    | 0.5   | 0.6   | 0.7   | 0.9   | 1.0   | 1.0                       | 1.3                       | 1.8                        | μA   |

|                      |                                    | LSE & RTC ON; "Xtal<br>mode" higher driving<br>capability;<br>LSEDRV[1:0] = '11' | 0.8                    | 0.8   | 0.9   | 1.0   | 1.2   | 1.3   | 1.4                       | 1.7                       | 2.2                        |      |

Table 29. Typical and maximum current consumption from the  $\rm V_{BAT}$  supply

1. Data based on characterization results, not tested in production.

## Typical current consumption

The MCU is placed under the following conditions:

- V<sub>DD</sub> = V<sub>DDA</sub> = 1.8 V

- All I/O pins are in analog input configuration

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency:

- 0 wait state and Prefetch OFF from 0 to 24 MHz

- 1 wait state and Prefetch ON above 24 MHz

- When the peripherals are enabled, f<sub>PCLK</sub> = f<sub>HCLK</sub>

- PLL is used for frequencies greater than 8 MHz

- AHB prescaler of 2, 4, 8 and 16 is used for the frequencies 4 MHz, 2 MHz, 1 MHz and 500 kHz respectively

| Symbol                 | Parameter                                       | Conditions                        | Min                                         | Тур | Max                                      | Unit |  |

|------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|-----|------------------------------------------|------|--|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                    | -                                 | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | V    |  |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                   | -                                 | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | v    |  |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                                           | 200 | -                                        | mV   |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                          | 40  | 55                                       | kΩ   |  |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                                           | -   | 100 <sup>(1)</sup>                       | ns   |  |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | -                                 | 700 <sup>(1)</sup>                          | -   | -                                        | ns   |  |

Table 53. NRST pin characteristics

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series

resistance is minimal (~10% order).

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 53: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

#### **NPOR pin characteristics**

The NPOR pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor to the  $V_{\text{DDA}},\,R_{\text{PU}}.$

Unless otherwise specified, the parameters given in *Table 54* below are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

## 6.3.18 Temperature sensor characteristics

| Symbol                             | Parameter                                      | Min  | Тур  | Max  | Unit  |

|------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature  | -    | ± 1  | ± 2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                  | 4.0  | 4.3  | 4.6  | mV/°C |

| V <sub>30</sub>                    | Voltage at 30 °C (± 5 °C) <sup>(2)</sup>       | 1.34 | 1.43 | 1.52 | V     |

| t <sub>START</sub> <sup>(1)</sup>  | ADC_IN16 buffer startup time                   | -    | -    | 10   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup> | ADC sampling time when reading the temperature | 4    | -    | -    | μs    |

Table 60. TS characteristics

1. Guaranteed by design, not tested in production.

2. Measured at  $V_{DDA}$  = 3.3 V ± 10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to Table 2: Temperature sensor calibration values.

## 6.3.19 V<sub>BAT</sub> monitoring characteristics

| Symbol                             | Parameter                                    |    | Тур    | Мах | Unit |

|------------------------------------|----------------------------------------------|----|--------|-----|------|

| R                                  | Resistor bridge for V <sub>BAT</sub>         | -  | 2 x 50 | -   | kΩ   |

| Q                                  | Ratio on V <sub>BAT</sub> measurement        | -  | 2      | -   | -    |

| Er <sup>(1)</sup>                  | Error on Q                                   | -1 | -      | +1  | %    |

| t <sub>S_vbat</sub> <sup>(1)</sup> | ADC sampling time when reading the $V_{BAT}$ | 4  | -      | -   | μs   |

#### Table 61. V<sub>BAT</sub> monitoring characteristics

1. Guaranteed by design, not tested in production.

## 6.3.20 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                                | Parameter                  | Conditions                    | Min             | Тур                     | Max                                                                                | Unit                 |

|---------------------------------------|----------------------------|-------------------------------|-----------------|-------------------------|------------------------------------------------------------------------------------|----------------------|

| t <sub>ere</sub> (TIM)                | Timer resolution time      | -                             | -               | 1                       | - t <sub>TIMxCLI</sub><br>- ns<br>- MHz<br>- MHz<br>- t <sub>TIMxCLI</sub><br>- μs | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>                 |                            | f <sub>TIMxCLK</sub> = 48 MHz | -               | 20.8                    | -                                                                                  | ns                   |

| f                                     | Timer external clock       | -                             | -               | f <sub>TIMxCLK</sub> /2 | -                                                                                  | MHz                  |

| f <sub>EXT</sub>                      | frequency on CH1 to<br>CH4 | f <sub>TIMxCLK</sub> = 48 MHz | -               | 24                      | -                                                                                  | MHz                  |

|                                       | 16-bit timer maximum       | -                             | -               | 2 <sup>16</sup>         | -                                                                                  | t <sub>TIMxCLK</sub> |

| t                                     | period                     | f <sub>TIMxCLK</sub> = 48 MHz | -               | 1365                    | -                                                                                  | μs                   |

| t <sub>MAX_COUNT</sub> 32-bit counter | -                          | -                             | 2 <sup>32</sup> | -                       | t <sub>TIMxCLK</sub>                                                               |                      |

|                                       | maximum period             | f <sub>TIMxCLK</sub> = 48 MHz | -               | 89.48                   | -                                                                                  | S                    |

Table 62. TIMx characteristics

| Symbol          | Parameter                                                        | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 65. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

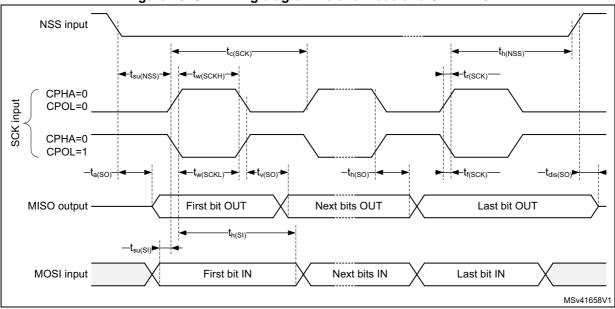

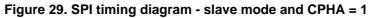

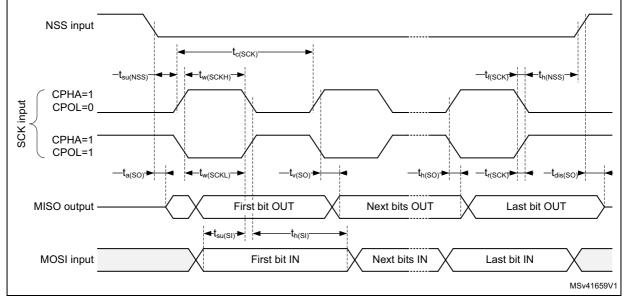

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 66* for SPI or in *Table 67* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 23: General operating conditions*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                        | Conditions                                            | Min         | Max         | Unit  |

|----------------------------------------------|----------------------------------|-------------------------------------------------------|-------------|-------------|-------|

| f <sub>SCK</sub>                             | SPI clock frequency              | Master mode                                           | -           | 18          | MHz   |

| 1/t <sub>c(SCK)</sub>                        | SPI Clock frequency              | Slave mode                                            | -           | 18          | IVITZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time     | Capacitive load: C = 15 pF                            | -           | 6           | ns    |

| t <sub>su(NSS)</sub>                         | NSS setup time                   | Slave mode                                            | 4Tpclk      | -           |       |

| t <sub>h(NSS)</sub>                          | NSS hold time                    | Slave mode                                            | 2Tpclk + 10 | -           |       |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |       |

| t <sub>su(MI)</sub>                          | Data input setup time            | Master mode                                           | 4           | -           |       |

| t <sub>su(SI)</sub>                          | Data input setup time            | Slave mode                                            | 5           | -           |       |

| t <sub>h(MI)</sub>                           | Data input hold time             | Master mode                                           | 4           | -           |       |

| t <sub>h(SI)</sub>                           |                                  | Slave mode                                            | 5           | -           | ns    |

| t <sub>a(SO)</sub> <sup>(2)</sup>            | Data output access time          | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |       |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time         | Slave mode                                            | 0           | 18          |       |

| t <sub>v(SO)</sub>                           | Data output valid time           | Slave mode (after enable edge)                        | -           | 22.5        |       |

| t <sub>v(MO)</sub>                           | Data output valid time           | Master mode (after enable edge)                       | -           | 6           |       |

| t <sub>h(SO)</sub>                           | Data output hold time            | Slave mode (after enable edge)                        | 11.5        | -           |       |

| t <sub>h(MO)</sub>                           |                                  | Master mode (after enable edge)                       | 2           | -           |       |

| DuCy(SCK)                                    | SPI slave input clock duty cycle | Slave mode                                            | 25          | 75          | %     |

| Table 6 | 6. SPI | characteristics( | 1) |

|---------|--------|------------------|----|

|---------|--------|------------------|----|

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 28. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

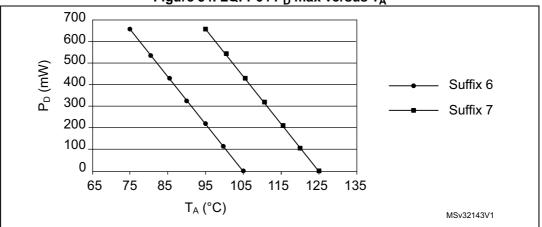

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F098CC/RC/VC at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in *Table 78* T<sub>Jmax</sub> is calculated as follows:

- For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Ordering information*).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum temperature  $T_{Amax} = 100 \degree C$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}$ ,  $V_{DD} = 3.5 \text{ V}$ , maximum 20 I/Os used at the same time in output at low level with  $I_{OL} = 8 \text{ mA}$ ,  $V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW

DocID026967 Rev 4

Using the values obtained in *Table* 78  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- $T_{Jmax} = 100 \text{ °C} + (45 \text{ °C/W} \times 134 \text{ mW}) = 100 \text{ °C} + 6.03 \text{ °C} = 106.03 \text{ °C}$

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Ordering information*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to the figure below to select the required temperature range (suffix 6 or 7) according to your temperature or power requirements.

Figure 54. LQFP64 P<sub>D</sub> max versus T<sub>A</sub>