Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f098rct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8 | Orde | ering int | ormation                                    |     |

|---|------|-----------|---------------------------------------------|-----|

| 0 | Orde |           |                                             |     |

|   |      | 7.8.2     | Selecting the product temperature range     |     |

|   | 7.0  | 7.8.1     | Reference document                          |     |

|   | 7.8  |           | al characteristics                          |     |

|   | 7.7  |           | PN48 package information                    |     |

|   | 7.6  |           | 8 package information                       |     |

|   | 7.5  | LQFP6     | 4 package information                       |     |

|   | 7.4  | WLCSI     | <sup>D</sup> 64 package information         | 109 |

|   | 7.3  | UFBGA     | A64 package information                     | 106 |

|   | 7.2  | LQFP1     | 00 package information                      | 103 |

|   | 7.1  | UFBGA     | A100 package information                    | 100 |

| 7 | Pack | age info  | ormation                                    | 100 |

|   |      | 6.3.21    | Communication interfaces                    | 94  |

|   |      | 6.3.20    | Timer characteristics                       |     |

|   |      | 6.3.19    | V <sub>BAT</sub> monitoring characteristics |     |

|   |      | 6.3.18    | Temperature sensor characteristics          |     |

|   |      | 6.3.17    | Comparator characteristics                  |     |

|   |      | 6.3.16    | DAC electrical specifications               | 89  |

|   |      | 6.3.15    | 12-bit ADC characteristics                  | 85  |

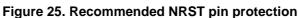

|   |      | 6.3.14    | NRST and NPOR pin characteristics           | 83  |

|   |      | 6.3.13    | I/O port characteristics                    |     |

|   |      | 6.3.12    | I/O current injection characteristics       |     |

# 4 Pinouts and pin descriptions

| Тор | Top view              |             |       |                  |       |       |       |        |        |        |        |        |

|-----|-----------------------|-------------|-------|------------------|-------|-------|-------|--------|--------|--------|--------|--------|

| r   | 1                     | 2           | 3     | 4                | 5     | 6     | 7     | 8      | 9      | 10     | 11     | 12     |

| А   | PE3                   | ) (PE1)     | (PB8) | (PF11-)<br>BOOT0 | (PD7) | (PD5) | (PB4) | РВЗ    | PA15   | PA14   | PA13   | (PA12) |

| В   | PE4                   | ) (PE2)     | (PB9) | (РВ7)            | (PB6) | (PD6) | (PD4) | (PD3)  | PD1    | PC12   | PC10   | PA11   |

| С   | (PC13                 | ) (PE5)     | (PE0) |                  | (PB5) |       |       | PD2    | PD0    | PC11   | PF6    | PA10   |

| D   | PC14-<br>OSC32<br>IN  | ) (PE6)     | vss   |                  |       |       |       |        |        | PA9    | PA8    | PC9    |

| Е   | PC15-<br>OSC32<br>OUT |             | NC    |                  |       |       |       |        |        | PC8    | PC7    | PC6    |

| F   | (PF0-)<br>OSC_<br>IN  | ) (PF9)     |       |                  |       |       |       |        |        |        | vss    | vss    |

| G   | (PF1-<br>(OSC_<br>OUT | ) (PF10)    |       |                  |       |       |       |        |        |        | VDDIO2 | VDD    |

| н   | PC0                   |             | VDD   |                  |       |       |       |        |        | (PD15) | (PD14) | (PD13) |

| J   | (PF2)                 | ) (PC1)     | PC2   |                  |       |       |       |        |        | (PD12) | (PD11) | (PD10) |

| к   | VSSA                  | ) (PC3)     | (PA2) | (PA5)            | (PC4) |       |       | (PD9)  | (PD8)  | (PB15) | (PB14) | (PB13) |

| L   | (PF3                  | ) (PA0)     | (PA3) | PA6              | (PC5) |       | (PE8) | (PE10) | (PE12) | (PB10) | (PB11) | (PB12) |

| М   | VDDA                  | ) (PA1)     | (PA4) | PA7              | РВО   | (PB1) | (PE7) | PE9    | (PE11) | (PE13) | (PE14) | (PE15) |

| Į   | I/O eu                | pplied from |       |                  |       | UFBG  | GA100 |        |        |        |        |        |

|     |                       |             |       |                  |       |       |       |        |        |        |        | MSv364 |

#### Figure 3. UFBGA100 package pinout

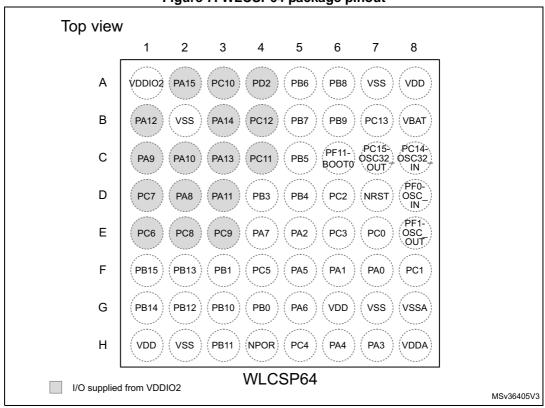

Figure 7. WLCSP64 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

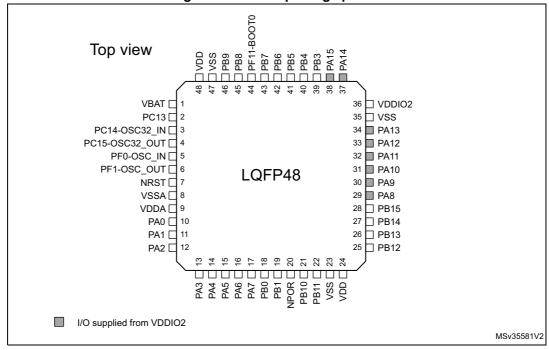

Figure 8. LQFP48 package pinout

Г

| Name      |                        | Abbreviation       | Definition                                    |

|-----------|------------------------|--------------------|-----------------------------------------------|

| Pin       | Alternate<br>functions | Functions selected | I through GPIOx_AFR registers                 |

| functions | Additional functions   | Functions directly | selected/enabled through peripheral registers |

### Table 11. Legend/abbreviations used in the pinout table (continued)

|          | Pi      | n nui   | mber   | S       |                 |                                      |          |               |            | Pin functions                                              |                                            |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|---------------|------------|------------------------------------------------------------|--------------------------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes      | Alternate functions                                        | Additional<br>functions                    |  |

| B2       | 1       | -       | -      | -       | -               | PE2                                  | I/O      | FT            |            | TSC_G7_IO1, TIM3_ETR                                       | -                                          |  |

| A1       | 2       | -       | -      | -       | -               | PE3                                  | I/O      | FT            |            | TSC_G7_IO2, TIM3_CH1                                       | -                                          |  |

| B1       | 3       | -       | -      | -       | -               | PE4                                  | I/O      | FT            |            | TSC_G7_IO3, TIM3_CH2                                       | -                                          |  |

| C2       | 4       | -       | -      | -       | -               | PE5                                  | I/O      | FT            |            | TSC_G7_IO4, TIM3_CH3                                       | -                                          |  |

| D2       | 5       | -       | -      | -       | -               | PE6                                  | I/O      | FT            |            | TIM3_CH4                                                   | WKUP3,<br>RTC_TAMP3                        |  |

| E2       | 6       | B2      | 1      | B8      | 1               | VBAT                                 | S        | -             | -          | Backup power supply                                        |                                            |  |

| C1       | 7       | A2      | 2      | B7      | 2               | PC13                                 | I/O      | тс            | (1)<br>(2) | -                                                          | WKUP2,<br>RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT |  |

| D1       | 8       | A1      | 3      | C8      | 3               | PC14-<br>OSC32_IN<br>(PC14)          | I/O      | тс            | (1)<br>(2) | -                                                          | OSC32_IN                                   |  |

| E1       | 9       | B1      | 4      | C7      | 4               | PC15-<br>OSC32_OUT<br>(PC15)         | I/O      | тс            | (1)<br>(2) | -                                                          | OSC32_OUT                                  |  |

| F2       | 10      | -       | -      | -       | -               | PF9                                  | I/O      | FT            |            | TIM15_CH1, USART6_TX                                       | -                                          |  |

| G2       | 11      | -       | -      | -       | -               | PF10                                 | I/O      | FT            |            | TIM15_CH2, USART6_RX                                       | -                                          |  |

| F1       | 12      | C1      | 5      | D8      | 5               | PF0-OSC_IN<br>(PF0)                  | I/O      | FTf           |            | CRS_SYNC, I2C1_SDA                                         | OSC_IN                                     |  |

| G1       | 13      | D1      | 6      | E8      | 6               | PF1-OSC_OUT<br>(PF1)                 | I/O      | FTf           |            | I2C1_SCL                                                   | OSC_OUT                                    |  |

| H2       | 14      | E1      | 7      | D7      | 7               | NRST                                 | I/O      | RST           |            | Device reset input / internal reset output<br>(active low) |                                            |  |

#### Table 12. STM32F098CC/RC/VC pin definitions

|          | Pi      | n nui   | nber   |         |                 | . 5111321 03000                      |          | •                      |     | Pin functions                                                                                                      |                                                    |  |

|----------|---------|---------|--------|---------|-----------------|--------------------------------------|----------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | WLCSP64 | LQFP48/UFQFPN48 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure<br>Notes |     | Alternate functions                                                                                                | Additional<br>functions                            |  |

| H3       | 28      | D2      | 19     | G6      | -               | VDD                                  | S        | -                      |     | Digital power su                                                                                                   | upply                                              |  |

| М3       | 29      | H3      | 20     | H6      | 14              | PA4                                  | I/O      | ТТа                    |     | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK,<br>USART6_TX                                         | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |  |

| K4       | 30      | F4      | 21     | F5      | 15              | PA5                                  | I/O      | ТТа                    |     | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2,<br>USART6_RX                                            | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |  |

| L4       | 31      | G4      | 22     | G5      | 16              | PA6                                  | I/O      | TTa                    |     | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>COMP1_OUT,<br>TSC_G2_IO3,<br>EVENTOUT,<br>USART3_CTS | ADC_IN6                                            |  |

| M4       | 32      | H4      | 23     | E4      | 17              | PA7                                  | I/O      | TTa                    |     | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N, TIM17_CH1,<br>COMP2_OUT,<br>TSC_G2_IO4,<br>EVENTOUT      | ADC_IN7                                            |  |

| K5       | 33      | H5      | 24     | H5      | -               | PC4                                  | I/O      | ТТа                    |     | EVENTOUT, USART3_TX                                                                                                | ADC_IN14                                           |  |

| L5       | 34      | H6      | 25     | F4      | -               | PC5                                  | I/O      | TTa                    |     | TSC_G3_IO1,<br>USART3_RX                                                                                           | ADC_IN15,<br>WKUP5                                 |  |

| M5       | 35      | F5      | 26     | G4      | 18              | PB0                                  | I/O      | ТТа                    |     | TIM3_CH3, TIM1_CH2N,<br>TSC_G3_IO2,<br>EVENTOUT,<br>USART3_CK                                                      | ADC_IN8                                            |  |

| M6       | 36      | G5      | 27     | F3      | 19              | PB1                                  | I/O      | ТТа                    |     | TIM3_CH4,<br>USART3_RTS,<br>TIM14_CH1, TIM1_CH3N,<br>TSC_G3_IO3                                                    | ADC_IN9                                            |  |

| L6       | 37      | G6      | 28     | H4      | 20              | NPOR                                 | Ι        | POR                    | (3) | Device power-on reset in                                                                                           | out (active low)                                   |  |

| M7       | 38      | -       | -      | -       | -               | PE7                                  | I/O      | FT                     |     | TIM1_ETR,<br>USART5_CK_RTS                                                                                         | -                                                  |  |

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_IO2          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | USART5_CK_RTS       |

| PE8      | TIM1_CH1N | USART4_TX           |

| PE9      | TIM1_CH1  | USART4_RX           |

| PE10     | TIM1_CH2N | USART5_TX           |

| PE11     | TIM1_CH2  | USART5_RX           |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

#### Table 17. Alternate functions selected through GPIOE\_AFR registers for port E

#### Table 18. Alternate functions selected through GPIOF\_AFR registers for port F

| Pin<br>name | AF0       | AF1       | AF2           |

|-------------|-----------|-----------|---------------|

| PF0         | CRS_SYNC  | I2C1_SDA  | -             |

| PF1         | -         | I2C1_SCL  | -             |

| PF2         | EVENTOUT  | USART7_TX | USART7_CK_RTS |

| PF3         | EVENTOUT  | USART7_RX | USART6_CK_RTS |

| PF6         | -         | -         | -             |

| PF9         | TIM15_CH1 | USART6_TX | -             |

| PF10        | TIM15_CH2 | USART6_RX | -             |

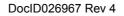

# 5 Memory mapping

Figure 10. STM32F098CC/RC/VC memory map

## 6 Electrical characteristics

### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V and  $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

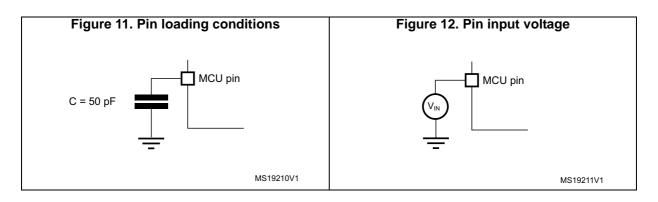

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

| Peripheral         Typical consumption at 25 °C         Unit           APB-Bridge <sup>[2]</sup> 3.6         ADC <sup>(3)</sup> 4.3           CAN         12.4         CEC         0.4           CEC         0.4         CRS         0.0           DAC <sup>(3)</sup> 4.2         DBG (MCU Debug Support)         0.2           I2C1         2.9         I2C2         2.4           PWR         0.6         SP11         8.8           SPI2         7.8         SYSCFG and COMP         1.9           TIM1         15.2         TIM14         2.6           TIM15         8.7         TIM14         16.2           TIM2         16.2         TIM3         11.9           TIM6         11.8         TIM7         2.5           USART1         17.6         USART3         16.2           USART5         4.4         USART6         5.5           USART6         5.5         USART6         5.5           USART8         5.1         WWDG         1.1           APB         1.1         1.1 |     |                         | Typical consumption (continued<br>Typical consumption at 25 °C | unit   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|----------------------------------------------------------------|--------|--|

| ADC <sup>(3)</sup> 4.3 CAN 12.4 CEC 0.4 CRS 0.0 DAC <sup>(3)</sup> 4.2 DBG (MCU Debug Support) 0.2 I2C1 2.2 2.4 PWR 0.6 SPI1 8.8 SPI2 7.8 SYSCFG and COMP 1.9 TIM1 15.2 TIM14 2.6 TIM15 8.7 TIM16 5.8 TIM17 7.0 TIM2 16.2 TIM3 11.9 TIM6 11.8 TIM7 2.5 USART1 17.6 USART2 16.3 USART3 16.2 USART4 4.7 USART5 4.4 USART5 4.4 USART5 5.1 WWDG 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                         |                                                                | Unit   |  |

| CAN         12.4           CEC         0.4           CRS         0.0           DAC <sup>(3)</sup> 4.2           DBG (MCU Debug Support)         0.2           I2C1         2.9           I2C2         2.4           PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                    |     |                         |                                                                |        |  |

| CEC         0.4           CRS         0.0           DAC <sup>(3)</sup> 4.2           DBG (MCU Debug Support)         0.2           I2C1         2.9           I2C2         2.4           PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                          |     |                         |                                                                |        |  |

| CRS         0.0           DAC <sup>(3)</sup> 4.2           DBG (MCU Debug Support)         0.2           I2C1         2.9           I2C2         2.4           PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                               |     |                         |                                                                |        |  |

| DAC <sup>(3)</sup> 4.2           DBG (MCU Debug Support)         0.2           I2C1         2.9           I2C2         2.4           PWR         0.6           SP11         8.8           SP12         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WVDG         1.1                                                                                                                                                                                                                                                                   |     |                         |                                                                |        |  |

| DBG (MCU Debug Support)         0.2           I2C1         2.9           I2C2         2.4           PWR         0.6           SP11         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WVDG         1.1                                                                                                                                                                                                                                                                                                    |     |                         |                                                                |        |  |

| I2C1         2.9           I2C2         2.4           PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                      |     |                         |                                                                |        |  |

| I2C2         2.4           PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                 |     | DBG (MCU Debug Support) | 0.2                                                            |        |  |

| PWR         0.6           SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                              |     | I2C1                    | 2.9                                                            |        |  |

| SPI1         8.8           SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART3         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                        |     | I2C2                    | 2.4                                                            |        |  |

| SPI2         7.8           SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | PWR                     | 0.6                                                            |        |  |

| SYSCFG and COMP         1.9           TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART6         5.5           USART7         5.2           USART8         5.1           WVDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                              |     | SPI1                    | 8.8                                                            |        |  |

| TIM1         15.2           TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | SPI2                    | 7.8                                                            |        |  |

| TIM14         2.6           TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | SYSCFG and COMP         | 1.9                                                            |        |  |

| APB         TIM15         8.7           TIM16         5.8           TIM17         7.0           TIM2         16.2           TIM3         11.9           TIM6         11.8           TIM7         2.5           USART1         17.6           USART2         16.3           USART3         16.2           USART4         4.7           USART5         4.4           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | TIM1                    | 15.2                                                           |        |  |

| APB       TIM16       5.8         TIM17       7.0         TIM2       16.2         TIM3       11.9         TIM6       11.8         TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | TIM14                   | 2.6                                                            |        |  |

| TIM16       5.8         TIM17       7.0         TIM2       16.2         TIM3       11.9         TIM6       11.8         TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | TIM15                   | 8.7                                                            |        |  |

| TIM2       16.2         TIM3       11.9         TIM6       11.8         TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | APB | TIM16                   | 5.8                                                            | μΑ/MHZ |  |

| TIM3       11.9         TIM6       11.8         TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | TIM17                   | 7.0                                                            |        |  |

| TIM6       11.8         TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | TIM2                    | 16.2                                                           |        |  |

| TIM7       2.5         USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | TIM3                    | 11.9                                                           |        |  |

| USART1       17.6         USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | TIM6                    | 11.8                                                           |        |  |

| USART2       16.3         USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | TIM7                    | 2.5                                                            |        |  |

| USART3       16.2         USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | USART1                  | 17.6                                                           |        |  |

| USART4       4.7         USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | USART2                  | 16.3                                                           |        |  |

| USART5       4.4         USART6       5.5         USART7       5.2         USART8       5.1         WWDG       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | USART3                  | 16.2                                                           |        |  |

| USART6         5.5           USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | USART4                  | 4.7                                                            |        |  |

| USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | USART5                  | 4.4                                                            |        |  |

| USART7         5.2           USART8         5.1           WWDG         1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | USART6                  | 5.5                                                            |        |  |

| USART8 5.1<br>WWDG 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |                         |                                                                |        |  |

| WWDG 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                         |                                                                |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                         |                                                                |        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                         |                                                                |        |  |

Table 32. Peripheral current consumption (continued)

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

2. The APB Bridge is automatically active when at least one peripheral is ON on the Bus.

The power consumption of the analog part (I<sub>DDA</sub>) of peripherals such as ADC, DAC, comparators, is not included. Refer to the tables of characteristics in the subsequent sections.

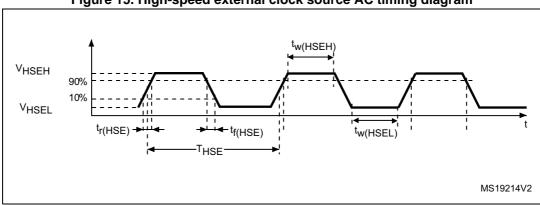

Figure 15. High-speed external clock source AC timing diagram

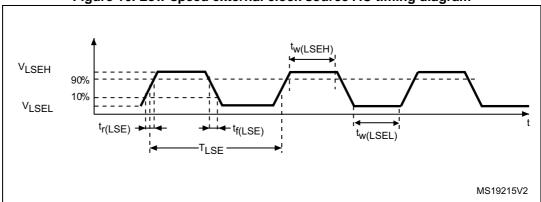

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.13. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 35. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

Figure 16. Low-speed external clock source AC timing diagram

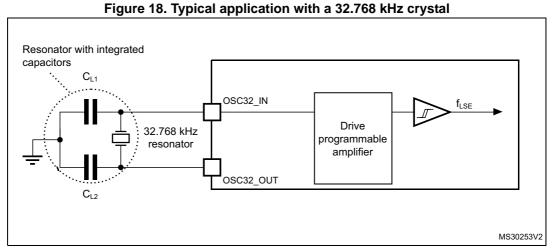

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

#### 6.3.7 Internal clock source characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*. The provided curves are characterization results, not tested in production.

| Symbol          | Parameter                                               | Conditions                             | Min | Тур | Max | Unit |

|-----------------|---------------------------------------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>PU</sub> | Weak pull-up<br>equivalent resistor<br>(3)              | V <sub>IN</sub> = V <sub>SS</sub>      | 25  | 40  | 55  | kΩ   |

| R <sub>PD</sub> | Weak pull-down<br>equivalent<br>resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub> | 25  | 40  | 55  | kΩ   |

| C <sub>IO</sub> | I/O pin capacitance                                     | -                                      | -   | 5   | -   | pF   |

Table 50. I/O static characteristics (continued)

1. Data based on design simulation only. Not tested in production.

2. The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 49: I/O current injection susceptibility.*

3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* for standard I/Os, and in *Figure 23* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 52*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                        | Conditions                                                                                         | Min | Max  | Unit |  |

|----------------------------------------|-------------------------|----------------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|--|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                                    | -   | 2    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$<br>$C_L = 50 \text{ pF}, V_{DDIOx} < 2 \text{ V}$ |     | 125  | ne   |  |

| x0                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                                    |     | 125  | ns   |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                                    |     | 1    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 |                                                                                                    |     | 125  | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                                    |     | 125  | 115  |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                                    | -   | 10   | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$                                                   | -   | 25   | ns   |  |

| 01                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                                    | -   | 25   |      |  |

| 01                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                                                                    |     | 4    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                                   | -   | 62.5 | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                                                                    |     | 62.5 | 113  |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$                                                               | -   | 50   | MHz  |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$                                                               | -   | 30   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V                                                           | -   | 20   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                                   | -   | 10   |      |  |

|                                        |                         |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$                                                               | -   | 5    |      |  |

| 11                                     | t                       | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$                                                               | -   | 8    |      |  |

|                                        | t <sub>f(IO)out</sub>   |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V                                                           | -   | 12   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                                   | -   | 25   | - ns |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 | C <sub>L</sub> = 30 pF, V <sub>DDIOx</sub> ≥ 2.7 V                                                 | -   | 5    |      |  |

|                                        |                         |                                  | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2.7 V                                                 | -   | 8    |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V                                                           | -   | 12   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                                                                   | -   | 25   |      |  |

| Table 52. I/O | AC | characteristics <sup>(1)(2)</sup> |

|---------------|----|-----------------------------------|

|---------------|----|-----------------------------------|

| Symbol                 | Parameter                                       | Conditions                        | Conditions Min                              |     | Max                                      | Unit |

|------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|-----|------------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                    | -                                 | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | V    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                   | -                                 | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                                           | 200 | -                                        | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                          | 40  | 55                                       | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                                           | -   | 100 <sup>(1)</sup>                       | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | -                                 | 700 <sup>(1)</sup>                          | -   | -                                        | ns   |

Table 53. NRST pin characteristics

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series

resistance is minimal (~10% order).

1. The external capacitor protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 53: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

#### **NPOR pin characteristics**

The NPOR pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor to the  $V_{\text{DDA}},\,R_{\text{PU}}.$

Unless otherwise specified, the parameters given in *Table 54* below are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

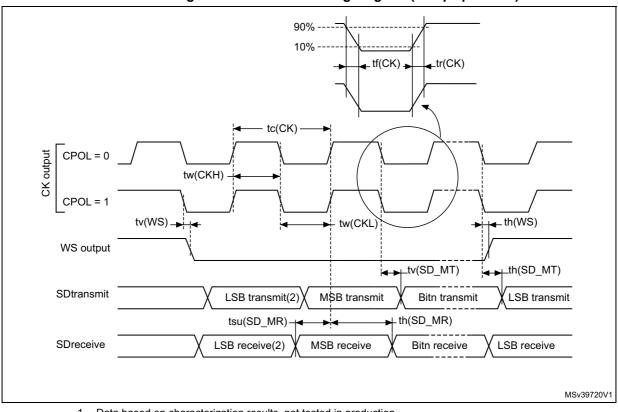

#### Figure 32. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### CAN (controller area network) interface

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

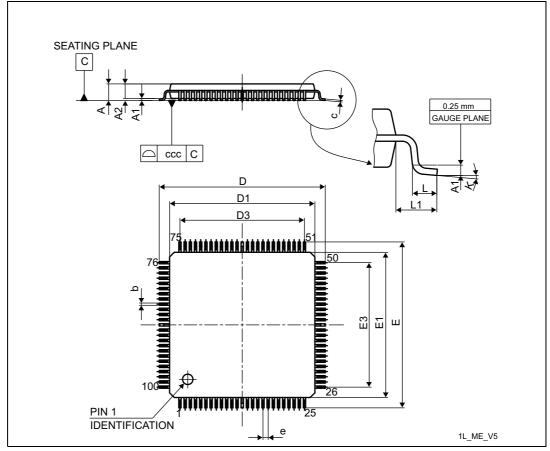

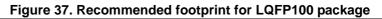

## 7.2 LQFP100 package information

LQFP100 is a100-pin, 14 x 14 mm low-profile quad flat package.

1. Drawing is not to scale.

| Table 70 | ). LQPF100 | package | mechanical data |  |

|----------|------------|---------|-----------------|--|

|----------|------------|---------|-----------------|--|

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Max    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| Cumhal | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

Table 70. LQPF100 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

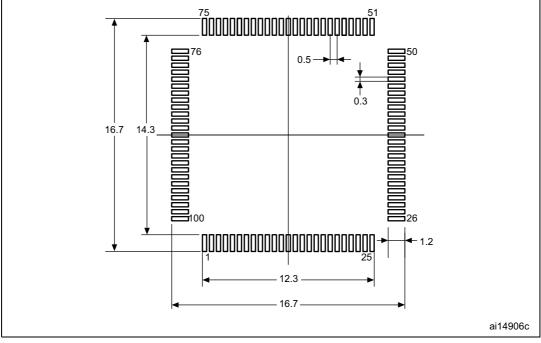

#### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

### 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 23: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{I\!/\!O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                 | Value | Unit |

|---------------|---------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 × 7 mm         | 55    |      |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm               | 42    |      |

|               | Thermal resistance junction-ambient<br>UFBGA64 - 5 × 5 mm / 0.5 mm pitch  | 65    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 44    | °C/W |

|               | Thermal resistance junction-ambient<br>WLCSP64 - 0.4 mm pitch             | 53    |      |

|               | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm                  | 54    |      |

|               | <b>Thermal resistance junction-ambient</b><br>UFQFPN48 - 7 × 7 mm         | 32    |      |

Table 78. Package thermal characteristics

#### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

#### 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

# 9 Revision history