Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Active                                                                |  |

|-------------------------------|-----------------------------------------------------------------------|--|

|                               |                                                                       |  |

| Core Processor                | ARM® Cortex®-M0                                                       |  |

| Core Size                     | 32-Bit Single-Core                                                    |  |

| Speed                         | 48MHz                                                                 |  |

| Connectivity                  | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |  |

| Peripherals                   | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |  |

| Number of I/O                 | 87                                                                    |  |

| Program Memory Size           | 256KB (256K x 8)                                                      |  |

| Program Memory Type           | FLASH                                                                 |  |

| EEPROM Size                   | -                                                                     |  |

| RAM Size                      | 32K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd)    | 1.65V ~ 3.6V                                                          |  |

| Data Converters               | A/D 19x12b; D/A 2x12b                                                 |  |

| Oscillator Type               | Internal                                                              |  |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                     |  |

| Mounting Type                 | Surface Mount                                                         |  |

| Package / Case                | 100-LQFP                                                              |  |

| Supplier Device Package       | 100-LQFP (14x14)                                                      |  |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f098vct6 |  |

|   | 3.15  | Real-tii            | me clock (RTC) and backup registers                                              | . 23 |

|---|-------|---------------------|----------------------------------------------------------------------------------|------|

|   | 3.16  | Inter-in            | tegrated circuit interface (I <sup>2</sup> C)                                    | . 24 |

|   | 3.17  | Univers             | sal synchronous/asynchronous receiver/transmitter (USART)                        | . 25 |

|   | 3.18  | Serial              | peripheral interface (SPI) / Inter-integrated sound interface (I <sup>2</sup> S) | . 26 |

|   | 3.19  |                     | efinition multimedia interface (HDMI) - consumer nics control (CEC)              | . 27 |

|   | 3.20  | Contro              | ller area network (CAN)                                                          | . 27 |

|   | 3.21  | Clock r             | recovery system (CRS)                                                            | . 27 |

|   | 3.22  |                     | wire debug port (SW-DP)                                                          |      |

| 4 | Pino  | uts and             | pin descriptions                                                                 | . 28 |

| 5 | Mem   | ory ma <sub>l</sub> | pping                                                                            | . 46 |

| 6 | Elect | trical ch           | aracteristics                                                                    | . 50 |

|   | 6.1   | Param               | eter conditions                                                                  | . 50 |

|   |       | 6.1.1               | Minimum and maximum values                                                       | . 50 |

|   |       | 6.1.2               | Typical values                                                                   | . 50 |

|   |       | 6.1.3               | Typical curves                                                                   | . 50 |

|   |       | 6.1.4               | Loading capacitor                                                                | . 50 |

|   |       | 6.1.5               | Pin input voltage                                                                |      |

|   |       | 6.1.6               | Power supply scheme                                                              |      |

|   |       | 6.1.7               | Current consumption measurement                                                  |      |

|   | 6.2   | Absolu              | te maximum ratings                                                               | . 53 |

|   | 6.3   | Operat              | ing conditions                                                                   | . 55 |

|   |       | 6.3.1               | General operating conditions                                                     | . 55 |

|   |       | 6.3.2               | Operating conditions at power-up / power-down                                    | . 55 |

|   |       | 6.3.3               | Embedded reference voltage                                                       | . 56 |

|   |       | 6.3.4               | Supply current characteristics                                                   | . 56 |

|   |       | 6.3.5               | Wakeup time from low-power mode                                                  | . 66 |

|   |       | 6.3.6               | External clock source characteristics                                            | . 66 |

|   |       | 6.3.7               | Internal clock source characteristics                                            | 70   |

|   |       | 6.3.8               | PLL characteristics                                                              | . 74 |

|   |       | 6.3.9               | Memory characteristics                                                           | . 74 |

|   |       | 6.3.10              | EMC characteristics                                                              | . 75 |

|   |       | 6.3.11              | Electrical sensitivity characteristics                                           | . 76 |

# List of tables

| Table 1.  | STM32F098CC/RC/VC family device features and peripheral counts                                 | 11 |

|-----------|------------------------------------------------------------------------------------------------|----|

| Table 2.  | Temperature sensor calibration values                                                          |    |

| Table 3.  | Internal voltage reference calibration values                                                  |    |

| Table 4.  | Capacitive sensing GPIOs available on STM32F098CC/RC/VC devices                                | 20 |

| Table 5.  | Number of capacitive sensing channels available                                                |    |

|           | on STM32F098CC/RC/VC devices                                                                   | 20 |

| Table 6.  | Timer feature comparison                                                                       | 21 |

| Table 7.  | Comparison of I <sup>2</sup> C analog and digital filters                                      |    |

| Table 8.  | STM32F098CC/RC/VC I <sup>2</sup> C implementation                                              | 25 |

| Table 9.  | STM32F098CC/RC/VC USART implementation                                                         |    |

| Table 10. | STM32F098CC/RC/VC SPI/I <sup>2</sup> S implementation                                          | 26 |

| Table 11. | Legend/abbreviations used in the pinout table                                                  | 33 |

| Table 12. | STM32F098CC/RC/VC pin definitions                                                              | 34 |

| Table 13. | Alternate functions selected through GPIOA_AFR registers for port A                            | 42 |

| Table 14. | Alternate functions selected through GPIOB_AFR registers for port B                            | 43 |

| Table 15. | Alternate functions selected through GPIOC_AFR registers for port C                            | 44 |

| Table 16. | Alternate functions selected through GPIOD_AFR registers for port D                            |    |

| Table 17. | Alternate functions selected through GPIOE_AFR registers for port E                            |    |

| Table 18. | Alternate functions selected through GPIOF_AFR registers for port F                            | 45 |

| Table 19. | STM32F098CC/RC/VC peripheral register boundary addresses                                       |    |

| Table 20. | Voltage characteristics                                                                        |    |

| Table 21. | Current characteristics                                                                        | 54 |

| Table 22. | Thermal characteristics                                                                        | 54 |

| Table 23. | General operating conditions                                                                   | 55 |

| Table 24. | Operating conditions at power-up / power-down                                                  | 56 |

| Table 25. | Embedded internal reference voltage                                                            |    |

| Table 26. | Typical and maximum current consumption from $V_{DD}$ supply at $V_{DD} = 1.8 \text{ V} \dots$ | 58 |

| Table 27. | Typical and maximum current consumption in Stop mode                                           |    |

| Table 28. | Typical and maximum current consumption from the V <sub>DDA</sub> supply                       | 59 |

| Table 29. | Typical and maximum current consumption from the V <sub>BAT</sub> supply                       |    |

| Table 30. | Typical current consumption, code executing from Flash memory,                                 |    |

|           | running from HSE 8 MHz crystal                                                                 | 61 |

| Table 31. | Switching output I/O current consumption                                                       | 63 |

| Table 32. | Peripheral current consumption                                                                 | 64 |

| Table 33. | Low-power mode wakeup timings                                                                  | 66 |

| Table 34. | High-speed external user clock characteristics                                                 | 66 |

| Table 35. | Low-speed external user clock characteristics                                                  |    |

| Table 36. | HSE oscillator characteristics                                                                 | 68 |

| Table 37. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                 | 69 |

| Table 38. | HSI oscillator characteristics                                                                 |    |

| Table 39. | HSI14 oscillator characteristics                                                               | 72 |

| Table 40. | HSI48 oscillator characteristics                                                               | 73 |

| Table 41. | LSI oscillator characteristics                                                                 | 74 |

| Table 42. | PLL characteristics                                                                            | 74 |

| Table 43. | Flash memory characteristics                                                                   | 74 |

| Table 44. | Flash memory endurance and data retention                                                      |    |

| Table 45. | EMS characteristics                                                                            |    |

| Table 46. | EMI characteristics                                                                            | 76 |

# List of figures

## STM32F098CC STM32F098RC STM32F098VC

| Figure 49. | Recommended footprint for LQFP48 package        | 116 |

|------------|-------------------------------------------------|-----|

| Figure 50. | LQFP48 package marking example                  | 117 |

| Figure 51. | UFQFPN48 package outline                        | 118 |

| Figure 52. | Recommended footprint for UFQFPN48 package      | 119 |

| Figure 53. | UFQFPN48 package marking example                | 120 |

| Figure 54. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 123 |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F098CC/RC/VC microcontrollers.

This document should be read in conjunction with the STM32F0xxxx reference manual (RM0091). The reference manual is available from the STMicroelectronics website <a href="https://www.st.com">www.st.com</a>.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core, please refer to the Cortex<sup>®</sup>-M0 Technical Reference Manual, available from the www.arm.com website.

introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists in charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate. For operation, one capacitive sensing GPIO in each group is connected to an external capacitor and cannot be used as effective touch sensing channel.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

Table 4. Capacitive sensing GPIOs available on STM32F098CC/RC/VC devices

| Group                                                                                                                               | Capacitive sensing signal name | Pin<br>name |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|

| 1                                                                                                                                   | TSC_G1_IO1                     | PA0         |

|                                                                                                                                     | TSC_G1_IO2                     | PA1         |

|                                                                                                                                     | TSC_G1_IO3                     | PA2         |

|                                                                                                                                     | TSC_G1_IO4                     | PA3         |

|                                                                                                                                     | TSC_G2_IO1                     | PA4         |

| 2                                                                                                                                   | TSC_G2_IO2                     | PA5         |

| TSC_G1_IO1 TSC_G1_IO2 TSC_G1_IO3 TSC_G1_IO4 TSC_G2_IO1 TSC_G2_IO3 TSC_G2_IO4 TSC_G3_IO1 TSC_G3_IO3 TSC_G3_IO3 TSC_G4_IO1 TSC_G4_IO3 | TSC_G2_IO3                     | PA6         |

|                                                                                                                                     | TSC_G2_IO4                     | PA7         |

|                                                                                                                                     | TSC_G3_IO1                     | PC5         |

| 3                                                                                                                                   | TSC_G3_IO2                     | PB0         |

|                                                                                                                                     | TSC_G3_IO3                     | PB1         |

|                                                                                                                                     | TSC_G4_IO1                     | PA9         |

| 4                                                                                                                                   | TSC_G4_IO2                     | PA10        |

| 4                                                                                                                                   | TSC_G4_IO3                     | PA11        |

|                                                                                                                                     | TSC_G4_IO4                     | PA12        |

| Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|-------------|

|       | TSC_G5_IO1                     | PB3         |

| 5     | TSC_G5_IO2                     | PB4         |

| 3     | TSC_G5_IO3                     | PB6         |

|       | TSC_G5_IO4                     | PB7         |

|       | TSC_G6_IO1                     | PB11        |

| 6     | TSC_G6_IO2                     | PB12        |

| 0     | TSC_G6_IO3                     | PB13        |

|       | TSC_G6_IO4                     | PB14        |

|       | TSC_G7_IO1                     | PE2         |

| 7     | TSC_G7_IO2                     | PE3         |

| ,     | TSC_G7_IO3                     | PE4         |

|       | TSC_G7_IO4                     | PE5         |

|       | TSC_G8_IO1                     | PD12        |

| 8     | TSC_G8_IO2                     | PD13        |

| 0     | TSC_G8_IO3                     | PD14        |

|       | TSC_G8_IO4                     | PD15        |

Table 5. Number of capacitive sensing channels available on STM32F098CC/RC/VC devices

| Amala a 1/O amana | Number of capacitive sensing channels |             |             |  |  |  |  |

|-------------------|---------------------------------------|-------------|-------------|--|--|--|--|

| Analog I/O group  | STM32F098Vx                           | STM32F098Rx | STM32F098Cx |  |  |  |  |

| G1                | 3                                     | 3           | 3           |  |  |  |  |

| G2                | 3                                     | 3           | 3           |  |  |  |  |

| G3                | 2                                     | 2           | 1           |  |  |  |  |

| G4                | 3                                     | 3           | 3           |  |  |  |  |

can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

### 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F098CC/RC/VC devices (see *Table 6* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

#### TIM2, TIM3

STM32F098CC/RC/VC devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advanced-control timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### **TIM14**

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### **TIM15, TIM16 and TIM17**

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

Top view 1 2 3 5 7 8 6 0 PC14-OSC32 IN (PC13 PB9 PB4 PB3 (PA15) PA14 PA13 Α PC15-OSC32 PF11-BOOT0 PC10 PA12 В VBAT PB8 PD2 PC11 PF0-OSC\_ IN С vss PB7 PB5 PC12 PA10 PA9 PA11 PF1-\ OSC\_ OUT D PB6 VDD VSS VSS VSS PA8 PC9 Ε (NRST) PC1 PC0 VDD VDD VDDIO2 PC7 PC8 F VSSA PC2 PA2 PA5 PB0 PC6 PB15 PB14 G PC3 PA0 PA3 PA6 PB1 (NPOR PB10 PB13 Н VDDA PA1 PA4 PA7 PC4 PC5 PB11 PB12 UFBGA64 I/O supplied from VDDIO2 MSv35569V2

Figure 5. UFBGA64 package pinout

Pin numbers Pin functions LQFP48/UFQFPN48 /O structure Pin type Pin name Notes UFBGA100 **UFBGA64** WLCSP64 LQFP100 LQFP64 (function upon **Additional Alternate functions** reset) **functions VSS** S Ground D3 99 D4 63 Α7 47 100 **A8** 48 VDD S C4 E4 64 Digital power supply

Table 12. STM32F098CC/RC/VC pin definitions (continued)

- PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These GPIOs must not be used as current sources (e.g. to drive an LED).

- 2. After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the system reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

- 3. This pin is powered by VDDA.

- 4. PC6, PC7, PC8, PC9, PA8, PA9, PA10, PA11, PA12, PA13, PF6, PA14, PA15, PC10, PC11, PC12, PD0, PD1 and PD2 I/Os are supplied by VDDIO2

- 5. After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

1. Data based on characterization results, not tested in production unless otherwise specified.

Table 27. Typical and maximum current consumption in Stop mode

|                 | <u>_</u>       | Parameter           |         | Typ @ V <sub>DDA</sub> (V <sub>DD</sub> = 1.8 V) |         |         |         |         | Max     |                        |                        |                         |      |

|-----------------|----------------|---------------------|---------|--------------------------------------------------|---------|---------|---------|---------|---------|------------------------|------------------------|-------------------------|------|

| Symbol          |                |                     | = 1.8 V | = 2.0 V                                          | = 2.4 V | = 2.7 V | = 3.0 V | = 3.3 V | = 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

| I <sub>DD</sub> | Supply current | All oscillators OFF |         |                                                  |         | 0.6     |         |         |         | 2.4                    | 33                     | 78                      | μA   |

| I <sub>DD</sub> | in Stop mode   | All Oscillators OFF | 0.9     | 0.9                                              | 1.0     | 1.0     | 1.0     | 1.1     | 1.2     | 2.5                    | 3.0                    | 3.7                     | μΑ   |

Table 28. Typical and maximum current consumption from the  $\mathrm{V}_{\mathrm{DDA}}$  supply

|                  | er                | [a]                    |                   | $V_{DDA} = 2.4 \text{ V}$ |                                     |       |        | V <sub>DDA</sub> = 3.6 V |        |                  |        |     |     |     |     |     |  |

|------------------|-------------------|------------------------|-------------------|---------------------------|-------------------------------------|-------|--------|--------------------------|--------|------------------|--------|-----|-----|-----|-----|-----|--|

| Symbol           | Para-meter        | Conditions (1)         | f <sub>HCLK</sub> |                           | Max @ T <sub>A</sub> <sup>(2)</sup> |       |        | M                        | ax @ T | A <sup>(2)</sup> | Unit   |     |     |     |     |     |  |

|                  | Para              |                        |                   | Тур                       | 25 °C                               | 85 °C | 105 °C | Тур                      | 25 °C  | 85 °C            | 105 °C |     |     |     |     |     |  |

|                  |                   | HSI48                  | 48 MHz            | 311                       | 332                                 | 337   | 346    | 315                      | 333    | 340              | 349    |     |     |     |     |     |  |

|                  |                   | HSE                    | 48 MHz            | 146                       | 167                                 | 177   | 180    | 159                      | 180    | 191              | 196    |     |     |     |     |     |  |

| Supply           | Supply current in | bypass,<br>t in PLL on | 32 MHz            | 100                       | 118                                 | 124   | 126    | 108                      | 126    | 134              | 137    |     |     |     |     |     |  |

|                  | Run or            |                        | 24 MHz            | 79                        | 95                                  | 98    | 99     | 85                       | 100    | 105              | 108    |     |     |     |     |     |  |

|                  | Sleep<br>mode,    | HSE                    | 8 MHz             | 2                         | 3                                   | 3     | 4      | 3                        | 3      | 4                | 4      |     |     |     |     |     |  |

| I <sub>DDA</sub> | code<br>executing | bypass,<br>PLL off     | 1 MHz             | 2                         | 2                                   | 3     | 3      | 2                        | 3      | 3                | 4      | μΑ  |     |     |     |     |  |

|                  | from              | from                   | from              | from                      | from                                | from  |        | 48 MHz                   | 212    | 242              | 253    | 257 | 234 | 261 | 274 | 280 |  |

|                  | memory            | HSI clock,<br>PLL on   | 32 MHz            | 165                       | 193                                 | 202   | 203    | 183                      | 206    | 215              | 219    |     |     |     |     |     |  |

|                  | or RAM            | -                      | 24 MHz            | 143                       | 170                                 | 176   | 177    | 160                      | 179    | 186              | 189    |     |     |     |     |     |  |

|                  |                   | HSI clock,<br>PLL off  | 8 MHz             | 64                        | 82                                  | 84    | 85     | 76                       | 88     | 91               | 92     |     |     |     |     |     |  |

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

<sup>2.</sup> Data based on characterization results, not tested in production unless otherwise specified.

trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

Caution:

Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 32: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

$I_{\mbox{\scriptsize SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{\text{DDIOx}}$  is the I/O supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{EXT} + C_{S}$

C<sub>S</sub> is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

Table 31. Switching output I/O current consumption

| Symbol          | Parameter               | Conditions <sup>(1)</sup>                                             | I/O toggling<br>frequency (f <sub>SW</sub> )                              | Тур                        | Unit                       |                            |                            |                            |                            |                            |                            |       |      |    |

|-----------------|-------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------|------|----|

|                 |                         |                                                                       | 2 MHz                                                                     | 0.09                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       |                                                                           | 4 MHz                      | 0.17                       |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $V_{DDIOx} = 1.8 \text{ V}$                                           | 8 MHz                                                                     | 0.34                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$           | 18 MHz                                                                    | 0.79                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | IIVI EXI S                                                            | 36 MHz                                                                    | 1.50                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 48 MHz                                                                    | 2.06                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 2 MHz                                                                     | 0.13                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 4 MHz                                                                     | 0.26                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $V_{DDIOx} = 1.8 \text{ V}$                                           | 8 MHz                                                                     | 0.50                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 | I/O current consumption | $C_{EXT} = 10 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$             | 18 MHz                                                                    | 1.18                       | _                          |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 36 MHz                                                                    | 2.27                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 48 MHz                                                                    | 3.03                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $V_{DDIOx} = 1.8 V$ $C_{EXT} = 22 pF$ $C = C_{INT} + C_{EXT} + C_{S}$ | 2 MHz                                                                     | 0.18                       | m Λ                        |                            |                            |                            |                            |                            |                            |       |      |    |

| I <sub>SW</sub> |                         |                                                                       | $V_{\text{DDIOx}} = 1.8 \text{ V}$ $C_{\text{EXT}} = 22 \text{ pF}$ 8 MHz | V <sub>DDIOx</sub> = 1.8 V | 4 MHz | 0.36 | mA |

|                 |                         |                                                                       |                                                                           | 0.69                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 18 MHz                                                                    | 1.60                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 36 MHz                                                                    | 3.27                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 2 MHz                                                                     | 0.23                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | V <sub>DDIOx</sub> = 1.8 V                                            | 4 MHz                                                                     | 0.45                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | C <sub>EXT</sub> = 33 pF                                              | 8 MHz                                                                     | 0.87                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $C = C_{INT} + C_{EXT} + C_{S}$                                       | 18 MHz                                                                    | 2.0                        | 1                          |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 36 MHz                                                                    | 3.7                        |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         |                                                                       | 2 MHz                                                                     | 0.29                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $V_{DDIOx} = 1.8 \text{ V}$                                           | 4 MHz                                                                     | 0.55                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | $C_{EXT} = 47 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_{S}$          | 8 MHz                                                                     | 1.09                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

|                 |                         | INT EXT O                                                             | 18 MHz                                                                    | 2.43                       |                            |                            |                            |                            |                            |                            |                            |       |      |    |

<sup>1.</sup>  $C_S = 5 pF$  (estimated value).

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 32*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in Table 20: Voltage characteristics

Table 32. Peripheral current consumption

|     | Peripheral               | Typical consumption at 25 °C | Unit       |

|-----|--------------------------|------------------------------|------------|

|     | BusMatrix <sup>(1)</sup> | 3.1                          |            |

|     | CRC                      | 2.0                          |            |

|     | DMA1                     | 5.5                          |            |

|     | DMA2                     | 5.1                          |            |

|     | Flash memory interface   | 15.4                         |            |

|     | GPIOA                    | 5.5                          |            |

| AHB | GPIOB                    | 5.4                          | μΑ/MHz     |

| AHD | GPIOC                    | 3.2                          | μΑνίνιι 12 |

|     | GPIOD                    | 3.1                          |            |

|     | GPIOE                    | 4.0                          |            |

|     | GPIOF                    | 2.5                          |            |

|     | SRAM                     | 0.8                          |            |

|     | TSC                      | 5.5                          |            |

|     | All AHB peripherals      | 61.0                         |            |

Table 50. I/O static characteristics (continued)

| Symbol          | Parameter                                         | Conditions                             | Min | Тур | Max | Unit |

|-----------------|---------------------------------------------------|----------------------------------------|-----|-----|-----|------|

| R <sub>PU</sub> | Weak pull-up<br>equivalent resistor<br>(3)        | V <sub>IN</sub> = V <sub>SS</sub>      | 25  | 40  | 55  | kΩ   |

| R <sub>PD</sub> | Weak pull-down equivalent resistor <sup>(3)</sup> | V <sub>IN</sub> = - V <sub>DDIOx</sub> | 25  | 40  | 55  | kΩ   |

| C <sub>IO</sub> | I/O pin capacitance                               | -                                      | -   | 5   | -   | pF   |

- 1. Data based on design simulation only. Not tested in production.

- 2. The leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to *Table 49: I/O current injection susceptibility*.

- 3. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 22* for standard I/Os, and in *Figure 23* for 5 V-tolerant I/Os. The following curves are design simulation results, not tested in production.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                       | Min | Max | Unit |

|----------------------------------------|-------------------------|-----------------------------------------------------------------|--------------------------------------------------|-----|-----|------|

| Fm+<br>configuration<br>(4)            | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> ≥ 2 V |     | 2   | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                                                |                                                  |     | 12  | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                  |     | 34  |      |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 50 pF, V <sub>DDIOx</sub> < 2 V |     | 0.5 | MHz  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                                                |                                                  |     | 16  | ns   |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                                                |                                                  |     | 44  |      |

| -                                      | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller | -                                                | 10  | -   | ns   |

Table 52. I/O AC characteristics<sup>(1)(2)</sup> (continued)

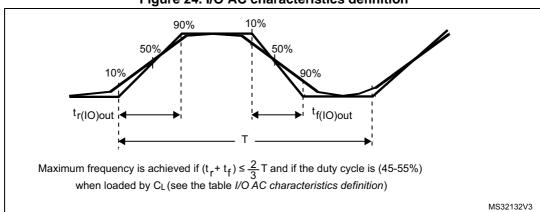

- The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the STM32F0xxxx RM0091 reference manual for a description of GPIO Port configuration register.

- 2. Guaranteed by design, not tested in production.

- 3. The maximum frequency is defined in Figure 24.

- 4. When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the STM32F0xxxx reference manual RM0091 for a detailed description of Fm+ I/O configuration.

Figure 24. I/O AC characteristics definition

## 6.3.14 NRST and NPOR pin characteristics

### **NRST** pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $R_{\text{PU}}$ .

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 23: General operating conditions*.

| Symbol                                 | Parameter                        | Conditions                                      | Min                                               | Тур                 | Max                                               | Unit                       |

|----------------------------------------|----------------------------------|-------------------------------------------------|---------------------------------------------------|---------------------|---------------------------------------------------|----------------------------|

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | 400.00                           | ADC clock = HSI14                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles | -                   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

|                                        | ADC_DR register ready latency    | ADC clock = PCLK/2                              | -                                                 | 4.5                 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | ADC clock = PCLK/4                              | -                                                 | 8.5                 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$         | 0.196                                             |                     |                                                   | μs                         |

|                                        | Trigger conversion latency       | $f_{ADC} = f_{PCLK}/2$                          |                                                   | 1/f <sub>PCLK</sub> |                                                   |                            |

| $t_{latr}^{(2)}$                       |                                  | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$         |                                                   | μs                  |                                                   |                            |

|                                        |                                  | $f_{ADC} = f_{PCLK}/4$                          | 10.5                                              |                     |                                                   | 1/f <sub>PCLK</sub>        |

|                                        |                                  | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz  | 0.179                                             | -                   | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion | f <sub>ADC</sub> = f <sub>HSI14</sub>           | -                                                 | 1                   | -                                                 | 1/f <sub>HSI14</sub>       |

| t <sub>S</sub> <sup>(2)</sup>          | Sampling time                    | f <sub>ADC</sub> = 14 MHz                       | 0.107                                             | -                   | 17.1                                              | μs                         |

|                                        | Sampling time                    | -                                               | 1.5                                               | -                   | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> (2)                  | Stabilization time               | -                                               | 14                                                |                     |                                                   | 1/f <sub>ADC</sub>         |

| t <sub>CONV</sub> <sup>(2)</sup>       | Total conversion time            | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | 1                                                 | -                   | 18                                                | μs                         |

|                                        | (including sampling time)        | 12-bit resolution                               | 14 to 252 (t <sub>S</sub> for successive ap       | 1/f <sub>ADC</sub>  |                                                   |                            |

Table 55. ADC characteristics (continued)

- 2. Guaranteed by design, not tested in production.

- 3. Specified value includes only ADC timing. It does not include the latency of the register access.

- 4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

## Equation 1: $R_{AIN}$ max formula

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

Table 56.  $R_{AIN}$  max for  $f_{ADC} = 14$  MHz

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |

|-------------------------|---------------------|------------------------------------------|

| 1.5                     | 0.11                | 0.4                                      |

| 7.5                     | 0.54                | 5.9                                      |

| 13.5                    | 0.96                | 11.4                                     |

<sup>1.</sup> During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on IDD should be taken into account.

Table 58. DAC characteristics (continued)

| Symbol                        | Parameter                                                                                                                                           | Min | Тур | Max  | Unit | Comments                                                                                               |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------------------------|

| Gain error <sup>(3)</sup>     | Gain error                                                                                                                                          | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                              |

| t <sub>SETTLING</sub> (3)     | Settling time (full scale: for a 10-bit input code transition between the lowest and the highest input codes when DAC_OUT reaches final value ±1LSB | -   | 3   | 4    | μs   | $C_{LOAD}$ ≤ 50 pF, $R_{LOAD}$ ≥ 5 kΩ                                                                  |

| Update<br>rate <sup>(3)</sup> | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                           | -   | -   | 1    | MS/s | $C_{LOAD}$ ≤ 50 pF, $R_{LOAD}$ ≥ 5 kΩ                                                                  |

| t <sub>WAKEUP</sub> (3)       | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                  | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. |

| PSRR+ (1)                     | Power supply rejection ratio (to V <sub>DDA</sub> ) (static DC measurement                                                                          | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       |

<sup>1.</sup> Guaranteed by design, not tested in production.

**577**

<sup>2.</sup> The DAC is in "quiescent mode" when it keeps the value steady on the output so no dynamic consumption is involved.

<sup>3.</sup> Data based on characterization results, not tested in production.

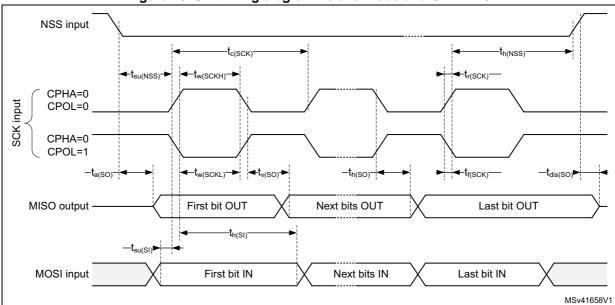

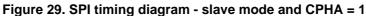

Figure 28. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\rm DD}$  and 0.7  $V_{\rm DD}$ .

57/

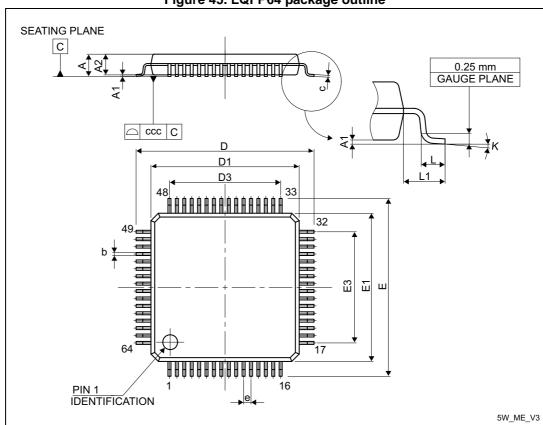

# 7.5 LQFP64 package information

LQFP64 is a 64-pin, 10 x 10 mm low-profile quad flat package.

Figure 45. LQFP64 package outline

1. Drawing is not to scale.

Table 75. LQFP64 package mechanical data

| Table 101 Eq. 1 04 package incomanical data |             |        |       |                       |        |        |  |

|---------------------------------------------|-------------|--------|-------|-----------------------|--------|--------|--|

| Symbol                                      | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|                                             | Min         | Тур    | Max   | Min                   | Тур    | Max    |  |

| Α                                           | -           | -      | 1.600 | -                     | -      | 0.0630 |  |

| A1                                          | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2                                          | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b                                           | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С                                           | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |

| D                                           | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| D1                                          | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

| D3                                          | -           | 7.500  | -     | -                     | 0.2953 | -      |  |

| E                                           | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| E1                                          | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

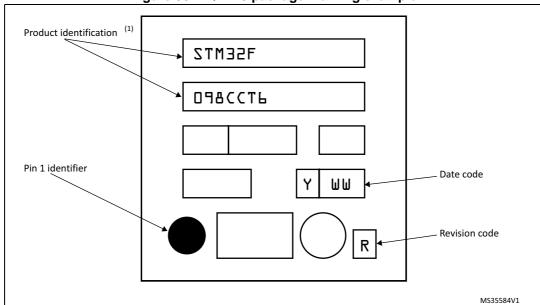

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 50. LQFP48 package marking example

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved