Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                  |

| Core Processor             | ARM® Cortex®-M3                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 100MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT             |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                               |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-LQFP                                                                   |

| Supplier Device Package    | 80-LQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1752fbd80-551  |

- ◆ WatchDog Timer (WDT). The WDT can be clocked from the internal RC oscillator, the RTC oscillator, or the APB clock.

- ◆ ARM Cortex-M3 system tick timer, including an external clock input option.

- Repetitive Interrupt Timer (RIT) provides programmable and repeating timed interrupts.

- ◆ Each peripheral has its own clock divider for further power savings.

- Standard JTAG debug interface for compatibility with existing tools. Serial Wire Debug and Serial Wire Trace Port options. Boundary scan Description Language (BSDL) is not available for this device.

- Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution.

- Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes.

- Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Single 3.3 V power supply (2.4 V to 3.6 V).

- One external interrupt input configurable as edge/level sensitive. All pins on Port 0 and Port 2 can be used as edge sensitive interrupt sources.

- Non-maskable Interrupt (NMI) input.

- The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in Deep sleep, Power-down, and Deep power-down modes.

- Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet wake-up interrupt (LPC1758 only), CAN bus activity, Port 0/2 pin interrupt, and NMI).

- Brownout detect with separate threshold for interrupt and forced reset.

- Power-On Reset (POR).

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock.

- PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator.

- USB PLL for added flexibility.

- Code Read Protection (CRP) with different security levels.

- Unique device serial number for identification purposes.

- Available as 80-pin LQFP package (12 mm × 12 mm × 1.4 mm).

# 3. Applications

- eMetering

- Lighting

- Industrial networking

- Alarm systems

- White goods

- Motor control

# 4. Ordering information

Table 1. Ordering information

| Type number  | Package |                                                                   |          |  |  |  |  |  |

|--------------|---------|-------------------------------------------------------------------|----------|--|--|--|--|--|

|              | Name    | Description                                                       | Version  |  |  |  |  |  |

| LPC1759FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

| LPC1758FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

| LPC1756FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

| LPC1754FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

| LPC1752FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

| LPC1751FBD80 | LQFP80  | plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm | SOT315-1 |  |  |  |  |  |

# 4.1 Ordering options

Table 2. Ordering options

|              |                             |            |     |           | SRA       | M ir  | ı kB     |                 |     |                      |     |      |                                     |  | ncy |

|--------------|-----------------------------|------------|-----|-----------|-----------|-------|----------|-----------------|-----|----------------------|-----|------|-------------------------------------|--|-----|

| Type number  | Device order<br>part number | Flash (kB) | CPU | AHB SRAMO | AHB SRAM1 | Total | Ethernet | USB             | CAN | l <sup>2</sup> S-bus | DAC | GPIO | Maximum CPU operating frequen (MHz) |  |     |

| LPC1759FBD80 | LPC1759FBD80,551            | 512        | 32  | 16        | 16        | 64    | no       | Device/Host/OTG | 2   | yes                  | yes | 52   | 120                                 |  |     |

| LPC1758FBD80 | LPC1758FBD80Y               | 512        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes                  | yes | 52   | 100                                 |  |     |

| LPC1756FBD80 | LPC1756FBD80/CP327          | 256        | 16  | 16        | -         | 32    | no       | Device/Host/OTG | 2   | yes                  | yes | 52   | 100                                 |  |     |

| LPC1754FBD80 | LPC1754FBD80,551            | 128        | 16  | 16        | -         | 32    | no       | Device/Host/OTG | 1   | no                   | yes | 52   | 100                                 |  |     |

| LPC1752FBD80 | LPC1752FBD80,551            | 64         | 16  | -         | -         | 16    | no       | Device only     | 1   | no                   | no  | 52   | 100                                 |  |     |

| LPC1751FBD80 | LPC1751FBD80,551            | 32         | 8   | -         | -         | 8     | no       | Device only     | 1   | no                   | no  | 52   | 100                                 |  |     |

# 5. Marking

The LPC175x devices typically have the following top-side marking:

LPC175xxxx

XXXXXX

xxYYWWR[x]

The last/second to last letter in the third line (field 'R') will identify the device revision. This data sheet covers the following revisions of the LPC175x:

Table 3. Device revision table

| Revision identifier (R) | Revision description    |

|-------------------------|-------------------------|

| Q                       | Initial device revision |

| 'A'                     | Second device revision  |

Field 'YY' states the year the device was manufactured. Field 'WW' states the week the device was manufactured during that year.

Table 4. Pin description ... continued

| Symbol                    | Pin                          | Туре | Description                                                                                                                                                                                                                                                                   |

|---------------------------|------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1                     | 19[9][10]                    | I    | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                                                                                        |

| XTAL2                     | 20[9][10]                    | 0    | Output from the oscillator amplifier.                                                                                                                                                                                                                                         |

| RTCX1                     | 13[9][11]                    | I    | Input to the RTC oscillator circuit.                                                                                                                                                                                                                                          |

| RTCX2                     | 15 <sup>[9]</sup>            | 0    | Output from the RTC oscillator circuit.                                                                                                                                                                                                                                       |

| V <sub>SS</sub>           | 24, 33,<br>43, 57,<br>66, 78 | I    | ground: 0 V reference.                                                                                                                                                                                                                                                        |

| V <sub>SSA</sub>          | 9                            | I    | <b>analog ground:</b> 0 V reference. This should nominally be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                                                                              |

| V <sub>DD(3V3)</sub>      | 21, 42,<br>56, 77            | I    | 3.3 V supply voltage: This is the power supply voltage for the I/O ports.                                                                                                                                                                                                     |

| V <sub>DD(REG)(3V3)</sub> | 34, 67                       | I    | <b>3.3 V voltage regulator supply voltage:</b> This is the supply voltage for the on-chip voltage regulator only.                                                                                                                                                             |

| $V_{DDA}$                 | 8                            | I    | analog 3.3 V pad supply voltage: This should be nominally the same voltage as $V_{DD(3V3)}$ but should be isolated to minimize noise and error. This voltage is used to power the ADC and DAC. This pin should be tied to 3.3 V if the ADC and DAC are not used.              |

| VREFP                     | 10                           | I    | <b>ADC positive reference voltage:</b> This should be nominally the same voltage as $V_{DDA}$ but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC and DAC. This pin should be tied to 3.3 V if the ADC and DAC are not used. |

| VREFN                     | 12                           | I    | <b>ADC negative reference voltage:</b> This should be nominally the same voltage as V <sub>SS</sub> but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC and DAC.                                                             |

| VBAT                      | 16 <sup>[11]</sup>           | I    | RTC pin power supply: 3.3 V on this pin supplies the power to the RTC peripheral.                                                                                                                                                                                             |

- [1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [2] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [3] 5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output, digital section of the pad is disabled. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [4] Pad provides digital I/O and USB functions. It is designed in accordance with the *USB specification, revision 2.0* (Full-speed and Low-speed mode only). This pad is not 5 V tolerant.

- [5] 5 V tolerant pad with 10 ns glitch filter providing digital I/O functions with TTL levels and hysteresis. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [6] 5 V tolerant pad with TTL levels and hysteresis. Internal pull-up and pull-down resistors disabled.

- [7] 5 V tolerant pad with TTL levels and hysteresis and internal pull-up resistor.

- [8] 5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

- [9] Pad provides special analog functionality. 32 kHz crystal oscillator must be used with the RTC.

- [10] When the system oscillator is not used, connect XTAL1 and XTAL2 as follows: XTAL1 can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTAL2 should be left floating.

- [11] When the RTC is not used, connect VBAT to V<sub>DD(REG)(3V3)</sub> and leave RTCX1 floating.

# 8. Functional description

#### 8.1 Architectural overview

The ARM Cortex-M3 includes three AHB-Lite buses: the system bus, the I-code bus, and the D-code bus (see <u>Figure 1</u>). The I-code and D-code core buses are faster than the system bus and are used similarly to Tightly Coupled Memory (TCM) interfaces: one bus dedicated for instruction fetch (I-code) and one bus for data access (D-code). The use of two core buses allows for simultaneous operations if concurrent operations target different devices.

The LPC1759/58/56/54/52/51 use a multi-layer AHB matrix to connect the ARM Cortex-M3 buses and other bus masters to peripherals in a flexible manner that optimizes performance by allowing peripherals that are on different slaves ports of the matrix to be accessed simultaneously by different bus masters.

## 8.2 ARM Cortex-M3 processor

The ARM Cortex-M3 is a general purpose, 32-bit microprocessor, which offers high performance and very low power consumption. The ARM Cortex-M3 offers many new features, including a Thumb-2 instruction set, low interrupt latency, hardware division, hardware single-cycle multiply, interruptable/continuable multiple load and store instructions, automatic state save and restore for interrupts, tightly integrated interrupt controller with wakeup interrupt controller, and multiple core buses capable of simultaneous accesses.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM Cortex-M3 processor is described in detail in the Cortex-M3 Technical Reference Manual that can be found on official ARM website.

### 8.3 On-chip flash program memory

The LPC1759/58/56/54/52/51 contain up to 512 kB of on-chip flash memory. A new two-port flash accelerator maximizes performance for use with the two fast AHB-Lite buses.

# 8.4 On-chip SRAM

The LPC1759/58/56/54/52/51 contain a total of up to 64 kB on-chip static RAM memory. This includes the main 32/16/8 kB SRAM, accessible by the CPU and DMA controller on a higher-speed bus, and up to two additional 16 kB each SRAM blocks situated on a separate slave port on the AHB multilayer matrix.

This architecture allows CPU and DMA accesses to be spread over three separate RAMs that can be accessed simultaneously.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

#### 8.22 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC1759/58/56/54/52/51. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

# 8.22.1 Features

- LPC1759/58/56/54/52/51 has one PWM block with Counter or Timer operation (may use the peripheral clock or one of the capture inputs as the clock source).

- Seven match registers allow up to 6 single edge controlled or 3 double edge controlled PWM outputs, or a mix of both types. The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Supports single edge controlled and/or double edge controlled PWM outputs. Single

edge controlled PWM outputs all go high at the beginning of each cycle unless the

output is a constant low. Double edge controlled PWM outputs can have either edge

occur at any position within a cycle. This allows for both positive going and negative

going pulses.

# 8.28 RTC and backup registers

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. The RTC on the LPC1759/58/56/54/52/51 is designed to have extremely low power consumption, i.e. less than 1  $\mu$ A. The RTC will typically run from the main chip power supply, conserving battery power while the rest of the device is powered up. When operating from a battery, the RTC will continue working down to 2.1 V. Battery power can be provided from a standard 3 V Lithium button cell.

An ultra-low power 32 kHz oscillator will provide a 1 Hz clock to the time counting portion of the RTC, moving most of the power consumption out of the time counting function.

The RTC includes a calibration mechanism to allow fine-tuning the count rate in a way that will provide less than 1 second per day error when operated at a constant voltage and temperature.

The RTC contains a small set of backup registers (20 bytes) for holding data while the main part of the LPC1759/58/56/54/52/51 is powered off.

The RTC includes an alarm function that can wake up the LPC1759/58/56/54/52/51 from all reduced power modes with a time resolution of 1 s.

#### 8.28.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- Periodic interrupts can be generated from increments of any field of the time registers.

- Backup registers (20 bytes) powered by VBAT.

- RTC power supply is isolated from the rest of the chip.

## 8.29 Clocking and power control

## 8.29.1 Crystal oscillators

The LPC1759/58/56/54/52/51 include three independent oscillators. These are the main oscillator, the IRC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the main PLL and ultimately the CPU.

Following reset, the LPC1759/58/56/54/52/51 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

See Figure 4 for an overview of the LPC1759/58/56/54/52/51 clock generation.

electrical characteristics (if a quartz crystal is used), as well as any other external circuitry (e.g., capacitors), and the characteristics of the oscillator itself under the existing ambient conditions.

#### 8.29.5 Power control

The LPC1759/58/56/54/52/51 support a variety of power control features. There are four special modes of processor power reduction: Sleep mode, Deep-sleep mode, Power-down mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, Peripheral Power Control allows shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Each of the peripherals has its own clock divider which provides even better power control.

Integrated PMU (Power Management Unit) automatically adjust internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes.

The LPC1759/58/56/54/52/51 also implement a separate power domain to allow turning off power to the bulk of the device while maintaining operation of the RTC and a small set of registers for storing data during any of the power-down modes.

#### 8.29.5.1 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a Reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

#### 8.29.5.2 Deep-sleep mode

In Deep-sleep mode, the oscillator is shut down and the chip receives no internal clocks. The processor state and registers, peripheral registers, and internal SRAM values are preserved throughout Deep-sleep mode and the logic levels of chip pins remain static. The output of the IRC is disabled but the IRC is not powered down for a fast wake-up later. The RTC oscillator is not stopped because the RTC interrupts may be used as the wake-up source. The PLL is automatically turned off and disconnected. The CCLK and USB clock dividers automatically get reset to zero.

The Deep-sleep mode can be terminated and normal operation resumed by either a Reset or certain specific interrupts that are able to function without clocks. Since all dynamic operation of the chip is suspended, Deep-sleep mode reduces chip power consumption to a very low value. Power to the flash memory is left on in Deep-sleep mode, allowing a very quick wake-up.

**Table 7. Static characteristics** ...continued  $T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol               | Parameter                               | Conditions                                                                                                  |                  | Min                        | Typ[1] | Max                     | Unit |

|----------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------|----------------------------|--------|-------------------------|------|

| I <sub>DD(ADC)</sub> | ADC supply current                      | active mode;                                                                                                | [16][17]         | -                          | 1.95   | -                       | mΑ   |

|                      |                                         | ADC powered                                                                                                 |                  |                            |        |                         |      |

|                      |                                         | ADC in Power-down mode                                                                                      | [16][18]         | -                          | <0.2   | -                       | μΑ   |

|                      |                                         | Deep sleep mode                                                                                             | [16]             | -                          | 38     | -                       | nΑ   |

|                      |                                         | Power-down mode                                                                                             | [16]             | -                          | 38     | -                       | nA   |

|                      |                                         | Deep power-down mode                                                                                        | [16]             | -                          | 24     | -                       | nA   |

| I <sub>I(ADC)</sub>  | ADC input current                       | on pin VREFP                                                                                                |                  |                            |        |                         |      |

|                      |                                         | Deep sleep mode                                                                                             | [19]             | -                          | 100    | -                       | nΑ   |

|                      |                                         | Power-down mode                                                                                             | [19]             | -                          | 100    | -                       | nA   |

|                      |                                         | Deep power-down mode                                                                                        | [19]             | -                          | 100    | -                       | nA   |

| Standard po          | ort pins, RESET                         |                                                                                                             |                  | •                          |        |                         |      |

| I <sub>IL</sub>      | LOW-level input current                 | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled                                                     |                  | -                          | 0.5    | 10                      | nA   |

| I <sub>IH</sub>      | HIGH-level input current                | V <sub>I</sub> = V <sub>DD(3V3)</sub> ; on-chip<br>pull-down resistor<br>disabled                           |                  | -                          | 0.5    | 10                      | nA   |

| l <sub>OZ</sub>      | OFF-state output current                | V <sub>O</sub> = 0 V; V <sub>O</sub> = V <sub>DD(3V3)</sub> ;<br>on-chip pull-up/down<br>resistors disabled |                  | -                          | 0.5    | 10                      | nA   |

| VI                   | input voltage                           | pin configured to provide a digital function                                                                | [20][21]<br>[22] | 0                          | -      | 5.0                     | V    |

| Vo                   | output voltage                          | output active                                                                                               |                  | 0                          | -      | V <sub>DD(3V3)</sub>    | V    |

| V <sub>IH</sub>      | HIGH-level input voltage                |                                                                                                             |                  | 0.7V <sub>DD(3V3)</sub>    | -      | -                       | V    |

| V <sub>IL</sub>      | LOW-level input voltage                 |                                                                                                             |                  | -                          | -      | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>     | hysteresis voltage                      |                                                                                                             |                  | 0.4                        | -      | -                       | V    |

| V <sub>OH</sub>      | HIGH-level output voltage               | $I_{OH} = -4 \text{ mA}$                                                                                    |                  | V <sub>DD(3V3)</sub> - 0.4 | -      | -                       | V    |

| V <sub>OL</sub>      | LOW-level output voltage                | I <sub>OL</sub> = 4 mA                                                                                      |                  | -                          | -      | 0.4                     | V    |

| I <sub>OH</sub>      | HIGH-level output current               | $V_{OH} = V_{DD(3V3)} - 0.4 \text{ V}$                                                                      |                  | -4                         | -      | -                       | mA   |

| I <sub>OL</sub>      | LOW-level output current                | V <sub>OL</sub> = 0.4 V                                                                                     |                  | 4                          | -      | -                       | mA   |

| I <sub>OHS</sub>     | HIGH-level short-circuit output current | V <sub>OH</sub> = 0 V                                                                                       | [23]             | -                          | -      | -45                     | mA   |

| I <sub>OLS</sub>     | LOW-level short-circuit output current  | $V_{OL} = V_{DD(3V3)}$                                                                                      | [23]             | -                          | -      | 50                      | mA   |

| I <sub>pd</sub>      | pull-down current                       | V <sub>I</sub> = 5 V                                                                                        |                  | 10                         | 50     | 150                     | μΑ   |

| I <sub>pu</sub>      | pull-up current                         | V <sub>I</sub> = 0 V                                                                                        |                  | -15                        | -50    | -85                     | μΑ   |

|                      |                                         | $V_{DD(3V3)} < V_{I} < 5 V$                                                                                 |                  | 0                          | 0      | 0                       | μΑ   |

# 11.2 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the PCONP register. All other blocks are disabled and no code is executed. Measured on a typical sample at  $T_{amb} = 25$  °C. The peripheral clock PCLK = CCLK/4.

Table 8. Power consumption for individual analog and digital blocks

| Peripheral                    | Conditions                                                                           | Typical s | upply curr | ent in mA; | Notes                                    |  |  |

|-------------------------------|--------------------------------------------------------------------------------------|-----------|------------|------------|------------------------------------------|--|--|

|                               |                                                                                      | 12 MHz    | 48 MHz     | 100 MHz    |                                          |  |  |

| Timer                         |                                                                                      | 0.03      | 0.11       | 0.23       | Average current per timer                |  |  |

| UART                          |                                                                                      | 0.07      | 0.26       | 0.53       | Average current per UART                 |  |  |

| PWM                           |                                                                                      | 0.05      | 0.20       | 0.41       |                                          |  |  |

| Motor control<br>PWM          |                                                                                      | 0.05      | 0.21       | 0.42       |                                          |  |  |

| I2C                           |                                                                                      | 0.02      | 0.08       | 0.16       | Average current per I2C                  |  |  |

| SPI                           |                                                                                      | 0.02      | 0.06       | 0.13       |                                          |  |  |

| SSP1                          |                                                                                      | 0.04      | 0.16       | 0.32       |                                          |  |  |

| ADC                           | PCLK = 12 MHz for CCLK = 12 MHz<br>and 48 MHz; PCLK = 12.5 MHz for<br>CCLK = 100 MHz | 2.12      | 2.09       | 2.07       |                                          |  |  |

| CAN                           | PCLK = CCLK/6                                                                        | 0.13      | 0.49       | 1.00       | Average current per CAN                  |  |  |

| CAN0, CAN1, acceptance filter | PCLK = CCLK/6                                                                        | 0.22      | 0.85       | 1.73       | Both CAN blocks and acceptance filter[1] |  |  |

| DMA                           | PCLK = CCLK                                                                          | 1.33      | 5.10       | 10.36      |                                          |  |  |

| QEI                           |                                                                                      | 0.05      | 0.20       | 0.41       |                                          |  |  |

| GPIO                          |                                                                                      | 0.33      | 1.27       | 2.58       |                                          |  |  |

| I2S                           |                                                                                      | 0.09      | 0.34       | 0.70       |                                          |  |  |

| USB and PLL1                  |                                                                                      | 0.94      | 1.32       | 1.94       |                                          |  |  |

| Ethernet                      | Ethernet block enabled in the PCONP register; Ethernet not connected.                | 0.49      | 1.87       | 3.79       |                                          |  |  |

| Ethernet connected            | Ethernet initialized, connected to network, and running web server example.          | -         | -          | 5.19       |                                          |  |  |

<sup>[1]</sup> The combined current of several peripherals running at the same time can be less than the sum of each individual peripheral current measured separately.

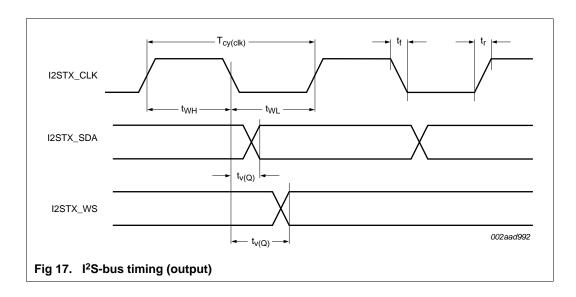

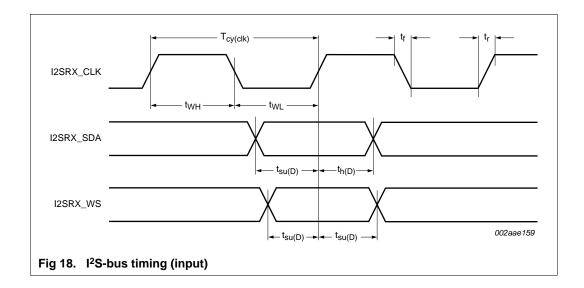

# 12.6 I<sup>2</sup>S-bus interface (LPC1759/58/56 only)

Table 14. Dynamic characteristics: I2S-bus interface pins

$T_{amb} = -40$  °C to +85 °C.

| Symbol             | Parameter              | Conditions                      |            | Min                        | Тур | Max                        | Unit |

|--------------------|------------------------|---------------------------------|------------|----------------------------|-----|----------------------------|------|

| common             | to input and output    |                                 | <b>'</b>   |                            |     |                            |      |

| t <sub>r</sub>     | rise time              |                                 | <u>[1]</u> | -                          | -   | 35                         | ns   |

| t <sub>f</sub>     | fall time              |                                 | [1]        | -                          | -   | 35                         | ns   |

| t <sub>WH</sub>    | pulse width HIGH       | on pins I2STX_CLK and I2SRX_CLK | [1]        | $0.495 \times T_{cy(clk)}$ | -   | -                          | -    |

| t <sub>WL</sub>    | pulse width LOW        | on pins I2STX_CLK and I2SRX_CLK | [1]        | -                          | -   | $0.505 \times T_{cy(clk)}$ | ns   |

| output             |                        |                                 |            |                            |     |                            |      |

| t <sub>v(Q)</sub>  | data output valid time | on pin I2STX_SDA;               | [1]        | -                          | -   | 30                         | ns   |

|                    |                        | on pin I2STX_WS                 | [1]        | -                          | -   | 30                         | ns   |

| input              |                        |                                 |            |                            |     |                            |      |

| t <sub>su(D)</sub> | data input set-up time | on pin I2SRX_SDA                | [1]        | 3.5                        | -   | -                          | ns   |

| t <sub>h(D)</sub>  | data input hold time   | on pin I2SRX_SDA                | [1]        | 4.0                        | -   | -                          | ns   |

[1] CCLK = 20 MHz; peripheral clock to the I<sup>2</sup>S-bus interface PCLK =  $^{CCLK}$ /<sub>4</sub>;  $T_{cy(clk)}$  = 1600 ns, corresponds to the SCK signal in the  $^{\ell}$ S-bus specification.

# 15. Application information

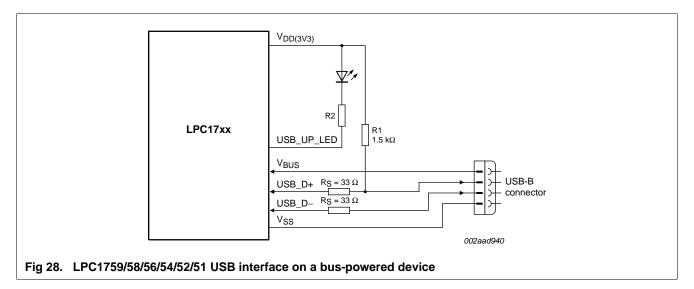

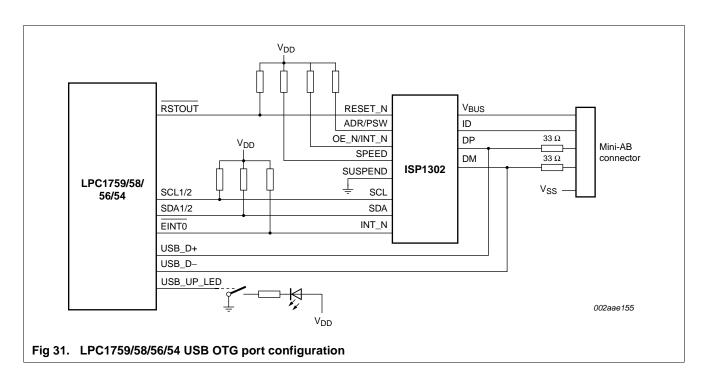

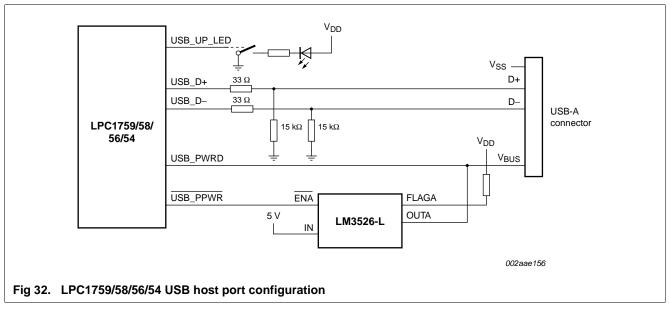

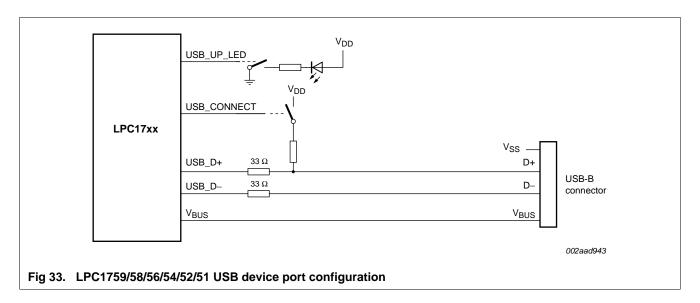

# 15.1 Suggested USB interface solutions

If the LPC1759/58/56/54/52/51  $V_{DD}$  is always greater than 0 V while  $V_{BUS}$  = 5 V, the  $V_{BUS}$  pin can be connected directly to the  $V_{BUS}$  pin on the USB connector.

This applies to bus powered devices where the USB cable supplies the system power. For systems where  $V_{DD}$  can be 0 V and  $V_{BUS}$  is directly applied to the  $V_{BUS}$  pin, precautions must be taken to reduce the voltage to below 3.6 V.

The maximum allowable voltage on the  $V_{BUS}$  pin is 3.6 V. One method is to use a voltage divider to connect the  $V_{BUS}$  pin to the  $V_{BUS}$  on the USB connector.

The voltage divider ratio should be such that the  $V_{BUS}$  pin will be greater than  $0.7V_{DD}$  to indicate a logic HIGH while below the 3.6 V allowable maximum voltage.

Use the following operating conditions:

$$VBUS_{max} = 5.25 V$$

$$V_{DD} = 3.6 V$$

The voltage divider would need to provide a reduction of 3.6 V/5.25 V or ~0.686 V.

## 15.2 Crystal oscillator XTAL input and component selection

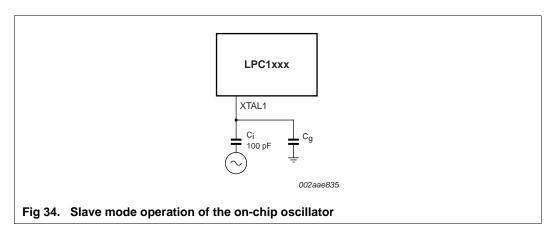

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i$  = 100 pF. To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (<u>Figure 34</u>), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in <u>Figure 35</u> and in <u>Table 22</u> and <u>Table 23</u>. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in <u>Figure 35</u> represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{x1}$  and  $C_{x2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

# 15.4 Standard I/O pin configuration

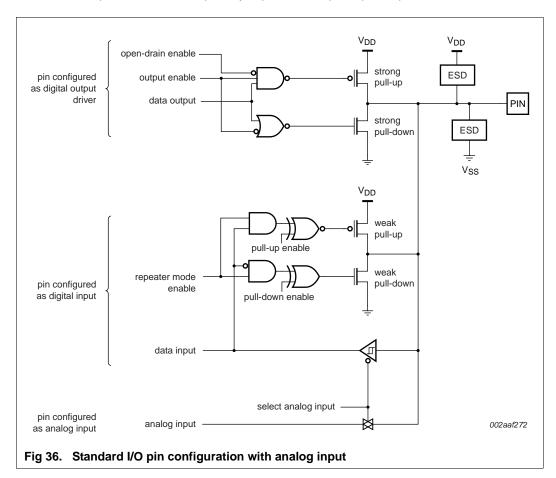

Figure 36 shows the possible pin modes for standard I/O pins with analog input function:

- · Digital output driver: Open-drain mode enabled/disabled

- · Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Analog input

The default configuration for standard I/O pins is input with pull-up enabled. The weak MOS devices provide a drive capability equivalent to pull-up and pull-down resistors.

# 15.6 ElectroMagnetic Compatibility (EMC)

Radiated emission measurements according to the IEC61967-2 standard using the TEM-cell method are shown for part LPC1768.

Table 24. ElectroMagnetic Compatibility (EMC) for part LPC1768 (TEM-cell method)  $V_{DD} = 3.3~V;~T_{amb} = 25~^{\circ}C.$

| Parameter    | Frequency band           | System clock = |        |        |        |         | Unit      |

|--------------|--------------------------|----------------|--------|--------|--------|---------|-----------|

|              |                          | 12 MHz         | 24 MHz | 48 MHz | 72 MHz | 100 MHz |           |

| Input clock: | IRC (4 MHz)              |                |        |        |        |         |           |

| maximum      | 150 kHz to 30 MHz        | -7             | -6     | -4     | -7     | -7      | $dB\mu V$ |

| peak level   | 30 MHz to 150 MHz        | +1             | +5     | +11    | +16    | +9      | dBμV      |

|              | 150 MHz to 1 GHz         | -2             | +4     | +11    | +12    | +19     | dBμV      |

| IEC level[1] | -                        | 0              | 0      | N      | М      | L       | -         |

| Input clock: | crystal oscillator (12 l | MHz)           |        | •      |        |         |           |

| maximum      | 150 kHz to 30 MHz        | -5             | -4     | -4     | -7     | -8      | dBμV      |

| peak level   | 30 MHz to 150 MHz        | -1             | +5     | +10    | +15    | +7      | dBμV      |

|              | 150 MHz to 1 GHz         | -1             | +6     | +11    | +10    | +16     | dBμV      |

| IEC level[1] | -                        | 0              | 0      | N      | М      | М       | -         |

<sup>[1]</sup> IEC levels refer to Appendix D in the IEC61967-2 Specification.

# 23. Contents

| 1        | General description                           | . 1 | 8.18.1   | Features                                                   | 24 |

|----------|-----------------------------------------------|-----|----------|------------------------------------------------------------|----|

| 2        | Features and benefits                         | . 1 | 8.19     | I <sup>2</sup> C-bus serial I/O controllers                | 24 |

| 3        | Applications                                  |     | 8.19.1   | Features                                                   | 24 |

| 4        | Ordering information                          |     | 8.20     | I <sup>2</sup> S-bus serial I/O controllers (LPC1759/58/56 |    |

| -        | _                                             |     |          | only)                                                      |    |

| 4.1      | Ordering options                              |     | 8.20.1   | Features                                                   | 25 |

| 5        | Marking                                       |     | 8.21     | General purpose 32-bit timers/external event               |    |

| 6        | Block diagram                                 | . 6 |          | counters                                                   |    |

| 7        | Pinning information                           | . 7 | 8.21.1   | Features                                                   |    |

| 7.1      | Pinning                                       |     | 8.22     | Pulse width modulator                                      | 26 |

| 7.2      | Pin description                               |     | 8.22.1   | Features                                                   |    |

| 8        | Functional description                        |     | 8.23     | Motor control PWM                                          |    |

| 8.1      | Architectural overview                        |     | 8.24     | Quadrature Encoder Interface (QEI)                         | 27 |

| 8.2      | ARM Cortex-M3 processor                       |     | 8.24.1   | Features                                                   |    |

| 8.3      | On-chip flash program memory                  |     | 8.25     | Repetitive Interrupt (RI) timer                            |    |

| 8.4      | On-chip SRAM                                  |     | 8.25.1   | Features                                                   |    |

| 8.5      | Memory Protection Unit (MPU)                  |     | 8.26     | ARM Cortex-M3 system tick timer                            |    |

| 8.6      | Memory map                                    |     | 8.27     | Watchdog timer                                             |    |

| 8.7      | Nested Vectored Interrupt Controller (NVIC) . |     | 8.27.1   | Features                                                   |    |

| 8.7.1    | Features                                      |     | 8.28     | RTC and backup registers                                   |    |

| 8.7.2    | Interrupt sources                             |     | 8.28.1   | Features                                                   |    |

| 8.8      | Pin connect block                             |     | 8.29     | Clocking and power control                                 |    |

| 8.9      | General purpose DMA controller                |     | 8.29.1   | Crystal oscillators                                        |    |

| 8.9.1    | Features                                      |     | 8.29.1.1 | Internal RC oscillator                                     |    |

| 8.10     | Fast general purpose parallel I/O             |     | 8.29.1.2 |                                                            |    |

| 8.10.1   | Features                                      |     | 8.29.1.3 |                                                            |    |

| 8.11     | Ethernet (LPC1758 only)                       |     | 8.29.2   | Main PLL (PLL0)                                            |    |

| 8.11.1   | Features                                      |     | 8.29.3   | USB PLL (PLL1)                                             |    |

| 8.12     | USB interface                                 |     | 8.29.4   | Wake-up timer                                              |    |

| 8.12.1   | USB device controller                         |     | 8.29.5   | Power control                                              |    |

| 8.12.1.1 |                                               |     | 8.29.5.1 | Sleep mode                                                 |    |

| 8.12.2   | USB host controller (LPC1759/58/56/54 only).  |     | 8.29.5.2 | •                                                          |    |

| 8.12.2.1 |                                               |     | 8.29.5.3 |                                                            |    |

| 8.12.3   | USB OTG controller (LPC1759/58/56/54 only).   |     | 8.29.5.4 | • •                                                        |    |

|          | 21                                            |     | 8.29.5.5 | •                                                          |    |

| 8.12.3.1 | Features                                      | 21  | 8.29.6   | Peripheral power control                                   |    |

| 8.13     | CAN controller and acceptance filters         |     | 8.29.7   | Power domains                                              |    |

| 8.13.1   | Features                                      |     | 8.30     | System control                                             |    |

| 8.14     | 12-bit ADC                                    | 22  | 8.30.1   | Reset                                                      |    |

| 8.14.1   | Features                                      |     | 8.30.2   | Brownout detection                                         |    |

| 8.15     | 10-bit DAC (LPC1759/58/56/54 only)            |     | 8.30.3   | Code security (Code Read Protection - CRP)                 |    |

| 8.15.1   | Features                                      |     | 8.30.4   | APB interface                                              | 36 |

| 8.16     | UARTs                                         | 23  | 8.30.5   | AHB multilayer matrix                                      |    |

| 8.16.1   | Features                                      |     | 8.30.6   | External interrupt inputs                                  |    |

| 8.17     | SPI serial I/O controller                     |     | 8.30.7   | Memory mapping control                                     |    |

| 8.17.1   | Features                                      |     | 8.31     | Emulation and debugging                                    |    |

| 8.18     | SSP serial I/O controller                     |     |          | Limiting values                                            |    |

|          |                                               |     | 10       | Thormal characteristics                                    | 20 |

continued >>

# LPC1759/58/56/54/52/51

## **NXP Semiconductors**

#### 32-bit ARM Cortex-M3 microcontroller

| 10.1         | Thermal characteristics                                     | 39       |

|--------------|-------------------------------------------------------------|----------|

| 11           | Static characteristics                                      | 40       |

| 11.1         | Power consumption                                           | 43       |

| 11.2         | Peripheral power consumption                                | 46       |

| 11.3         | Electrical pin characteristics                              | 47       |

| 12           | Dynamic characteristics                                     | 49       |

| 12.1         | Flash memory                                                | 49       |

| 12.2         | External clock                                              | 49       |

| 12.3         | Internal oscillators                                        | 50       |

| 12.4         | I/O pins                                                    | 50       |

| 12.5         | I <sup>2</sup> C-bus                                        | 51       |

| 12.6         | I <sup>2</sup> S-bus interface (LPC1759/58/56 only)         | 53       |

| 12.7         | SSP interface                                               | 55       |

| 12.8         | USB interface                                               | 57       |

| 12.9         | SPI                                                         | 58       |

| 13           | ADC electrical characteristics                              | 60       |

| 14           | DAC electrical characteristics                              |          |

| _            | (LPC1759/58/56/54 only)                                     | 63       |

| 15           | Application information                                     | 64       |

| 15.1         | Suggested USB interface solutions                           | 64       |

| 15.2         | Crystal oscillator XTAL input and component                 |          |

| 4=0          | selection                                                   | 67       |

| 15.3         | XTAL Printed-Circuit Board (PCB) layout                     | 00       |

| 45.4         | guidelines                                                  | 68       |

| 15.4<br>15.5 | Standard I/O pin configuration                              | 69<br>70 |

| 15.6         | Reset pin configuration ElectroMagnetic Compatibility (EMC) | 70       |

| 16           |                                                             | 72       |

| . •          | Package outline                                             |          |

| 17           | Soldering                                                   | 73       |

| 18           | Abbreviations                                               | 74       |

| 19           | References                                                  | 74       |

| 20           | Revision history                                            | 75       |

| 21           | Legal information                                           | 77       |

| 21.1         | Data sheet status                                           | 77       |

| 21.2         | Definitions                                                 | 77       |

| 21.3         | Disclaimers                                                 | 77       |

| 21.4         | Trademarks                                                  | 78       |

| 22           | Contact information                                         | 78       |

| 23           | Contents                                                    | 79       |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.