Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                               |

| Core Size                  | 32-Bit Single-Core                                                            |

| Speed                      | 100MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                 |

| Number of I/O              | 52                                                                            |

| Program Memory Size        | 128KB (128K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 32K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                   |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-LQFP                                                                       |

| Supplier Device Package    | 80-LQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1754fbd80-518      |

|                            |                                                                               |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

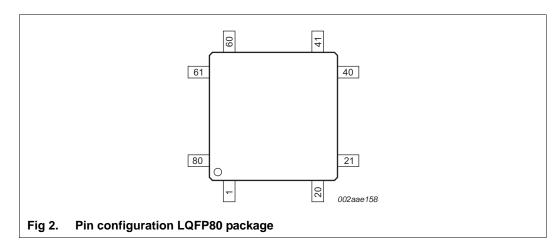

## 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

| Symbol                              | Pin           | Туре | Description                                                                                                                                                                                                                                        |

|-------------------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[0] to P0[31]                     |               | I/O  | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of Port 0 pins depends upon the pin function selected via the pin connect block. Some port pins are not available on the LQFP80 package. |

| P0[0]/RD1/TXD3/                     | 37 <u>[1]</u> | I/O  | P0[0] — General purpose digital input/output pin.                                                                                                                                                                                                  |

| SDA1                                |               | I    | RD1 — CAN1 receiver input.                                                                                                                                                                                                                         |

|                                     |               | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                               |

|                                     |               | I/O  | <b>SDA1</b> — I <sup>2</sup> C1 data input/output (this is not an I <sup>2</sup> C-bus compliant open-drain pin).                                                                                                                                  |

| P0[1]/TD1/RXD3/                     | 38 <u>[1]</u> | I/O  | P0[1] — General purpose digital input/output pin.                                                                                                                                                                                                  |

| SCL1                                |               | 0    | TD1 — CAN1 transmitter output.                                                                                                                                                                                                                     |

|                                     |               | I    | RXD3 — Receiver input for UART3.                                                                                                                                                                                                                   |

|                                     |               | I/O  | SCL1 — $I^2C1$ clock input/output (this is not an $I^2C$ -bus compliant open-drain pin).                                                                                                                                                           |

| P0[2]/TXD0/AD0[7]                   | 79 <u>[2]</u> | I/O  | P0[2] — General purpose digital input/output pin.                                                                                                                                                                                                  |

|                                     |               | 0    | TXD0 — Transmitter output for UART0.                                                                                                                                                                                                               |

|                                     |               | I    | AD0[7] — A/D converter 0, input 7.                                                                                                                                                                                                                 |

| P0[3]/RXD0/AD0[6] 80 <sup>[2]</sup> |               | I/O  | P0[3] — General purpose digital input/output pin.                                                                                                                                                                                                  |

|                                     |               | I    | RXD0 — Receiver input for UART0.                                                                                                                                                                                                                   |

|                                     |               | I    | AD0[6] — A/D converter 0, input 6.                                                                                                                                                                                                                 |

| P0[6]/                              | 64 <u>[1]</u> | I/O  | P0[6] — General purpose digital input/output pin.                                                                                                                                                                                                  |

| I2SRX_SDA/<br>SSEL1/MAT2[0]         | 1/            | I/O  | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification. (LPC1759/58/56 only).                                                                    |

|                                     |               | I/O  | SSEL1 — Slave Select for SSP1.                                                                                                                                                                                                                     |

|                                     |               | 0    | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                                                     |

32-bit ARM Cortex-M3 microcontroller

| Symbol                    | Pin           | Туре | Description                                                                                                                                        |

|---------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| P1[28]/MCOA2/             | 35 <u>[1]</u> | I/O  | P1[28] — General purpose digital input/output pin.                                                                                                 |

| PCAP1[0]/<br>MAT0[0]      |               | 0    | MCOA2 — Motor control PWM channel 2, output A.                                                                                                     |

|                           |               | I    | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                      |

|                           |               | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                     |

| P1[29]/MCOB2/             | 36 <u>[1]</u> | I/O  | P1[29] — General purpose digital input/output pin.                                                                                                 |

| PCAP1[1]/                 |               | 0    | MCOB2 — Motor control PWM channel 2, output B.                                                                                                     |

| MAT0[1]                   |               | I    | PCAP1[1] — Capture input for PWM1, channel 1.                                                                                                      |

|                           |               | 0    | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                     |

| P1[30]/V <sub>BUS</sub> / | 18 <u>[2]</u> | I/O  | P1[30] — General purpose digital input/output pin.                                                                                                 |

| AD0[4]                    |               | I    | V <sub>BUS</sub> — Monitors the presence of USB bus power.                                                                                         |

|                           |               |      | Note: This signal must be HIGH for USB reset to occur.                                                                                             |

|                           |               | I    | AD0[4] — A/D converter 0, input 4.                                                                                                                 |

| P1[31]/SCK1/              | 17 <u>[2]</u> | I/O  | P1[31] — General purpose digital input/output pin.                                                                                                 |

| AD0[5]                    |               | I/O  | SCK1 — Serial Clock for SSP1.                                                                                                                      |

|                           |               | I    | AD0[5] — A/D converter 0, input 5.                                                                                                                 |

| P2[0] to P2[31]           |               | I/O  | Port 2: Port 2 is a 32-bit I/O port with individual direction controls for each bit. The                                                           |

|                           |               |      | operation of port 2 pins depends upon the pin function selected via the pin connect block. Some port pins are not available on the LQFP80 package. |

| P2[0]/PWM1[1]/            | 60 <u>[1]</u> | I/O  | P2[0] — General purpose digital input/output pin.                                                                                                  |

| TXD1                      |               | 0    | PWM1[1] — Pulse Width Modulator 1, channel 1 output.                                                                                               |

|                           |               | 0    | TXD1 — Transmitter output for UART1.                                                                                                               |

| P2[1]/PWM1[2]/            | 59 <u>[1]</u> | I/O  | P2[1] — General purpose digital input/output pin.                                                                                                  |

| RXD1                      |               | 0    | PWM1[2] — Pulse Width Modulator 1, channel 2 output.                                                                                               |

|                           |               | I    | <b>RXD1</b> — Receiver input for UART1.                                                                                                            |

| P2[2]/PWM1[3]/            |               |      | P2[2] — General purpose digital input/output pin.                                                                                                  |

| CTS1/                     |               | 0    | PWM1[3] — Pulse Width Modulator 1, channel 3 output.                                                                                               |

| TRACEDATA[3]              |               | I    | CTS1 — Clear to Send input for UART1.                                                                                                              |

|                           |               | 0    | TRACEDATA[3] — Trace data, bit 3.                                                                                                                  |

| P2[3]/PWM1[4]/            | 55 <u>[1]</u> | I/O  | P2[3] — General purpose digital input/output pin.                                                                                                  |

| DCD1/                     |               | 0    | PWM1[4] — Pulse Width Modulator 1, channel 4 output.                                                                                               |

| TRACEDATA[2]              |               | I    | DCD1 — Data Carrier Detect input for UART1.                                                                                                        |

|                           |               | 0    | TRACEDATA[2] — Trace data, bit 2.                                                                                                                  |

| P2[4]/PWM1[5]/            | 54 <u>[1]</u> | I/O  | P2[4] — General purpose digital input/output pin.                                                                                                  |

| DSR1/                     |               | 0    | PWM1[5] — Pulse Width Modulator 1, channel 5 output.                                                                                               |

| TRACEDATA[1]              |               | I    | DSR1 — Data Set Ready input for UART1.                                                                                                             |

|                           |               | 0    | TRACEDATA[1] — Trace data, bit 1.                                                                                                                  |

| P2[5]/PWM1[6]/            | 53 <u>[1]</u> | I/O  | P2[5] — General purpose digital input/output pin.                                                                                                  |

| DTR1/                     |               | 0    | <b>PWM1[6]</b> — Pulse Width Modulator 1, channel 6 output.                                                                                        |

| TRACEDATA[0]              |               | 0    | <b>DTR1</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal.                           |

|                           |               | 0    | TRACEDATA[0] — Trace data, bit 0.                                                                                                                  |

#### Table 4. Pin description ...continued

Τ

32-bit ARM Cortex-M3 microcontroller

Product data sheet

rformation provided in this document is subject to lega Rev. 8.6 — 18 August 2015

16 of 80

### 8.9.1 Features

- Eight DMA channels. Each channel can support an unidirectional transfer.

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- One AHB bus master for transferring data. The interface transfers data when a DMA request goes active.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

### 8.10 Fast general purpose parallel I/O

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of outputs simultaneously. The value of the output register may be read back as well as the current state of the port pins.

LPC1759/58/56/54/52/51 use accelerated GPIO functions:

- GPIO registers are accessed through the AHB multilayer bus so that the fastest possible I/O timing can be achieved.

- Mask registers allow treating sets of port bits as a group, leaving other bits unchanged.

- All GPIO registers are byte and half-word addressable.

- Entire port value can be written in one instruction.

- Support for Cortex-M3 bit banding.

- Support for use with the GPDMA controller.

### 32-bit ARM Cortex-M3 microcontroller

### 8.13.1 Features

- One or two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes standard (11-bit) and extended-frame (29-bit) receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

### 8.14 12-bit ADC

The LPC1759/58/56/54/52/51 contain one ADC. It is a single 12-bit successive approximation ADC with six channels and DMA support.

### 8.14.1 Features

- 12-bit successive approximation ADC.

- Input multiplexing among 6 pins.

- Power-down mode.

- Measurement range VREFN to VREFP.

- 12-bit conversion rate: 200 kHz.

- Individual channels can be selected for conversion.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- DMA support.

### 8.15 10-bit DAC (LPC1759/58/56/54 only)

The DAC allows to generate a variable analog output. The maximum output value of the DAC is VREFP.

### 8.15.1 Features

- 10-bit DAC

- Resistor string architecture

- Buffered output

- Power-down mode

- Selectable output drive

- Dedicated conversion timer

- DMA support

© NXP Semiconductors N.V. 2015. All rights reserved.

### 8.25 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 32-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

### 8.25.1 Features

- 32-bit counter running from PCLK. Counter can be free-running or be reset by a generated interrupt.

- 32-bit compare value.

- 32-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This allows for combinations not possible with a simple compare.

### 8.26 ARM Cortex-M3 system tick timer

The ARM Cortex-M3 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval. In the LPC1759/58/56/54/52/51, this timer can be clocked from the internal AHB clock or from a device pin.

### 8.27 Watchdog timer

The purpose of the watchdog is to reset the microcontroller within a reasonable amount of time if it enters an erroneous state. When enabled, the watchdog will generate a system reset if the user program fails to 'feed' (or reload) the watchdog within a predetermined amount of time.

### 8.27.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{32} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC (IRC) oscillator, the RTC oscillator, or the APB peripheral clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

- Includes lock/safe feature.

### 32-bit ARM Cortex-M3 microcontroller

On wake-up from Deep-sleep mode, the code execution and peripherals activities will resume after 4 cycles expire if the IRC was used before entering Deep-sleep mode. If the main external oscillator was used, the code execution will resume when 4096 cycles expire. PLL and clock dividers need to be reconfigured accordingly.

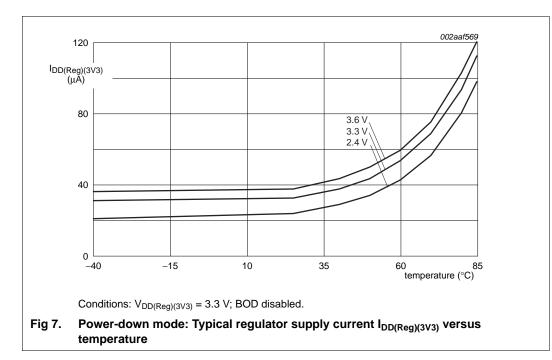

#### 8.29.5.3 Power-down mode

Power-down mode does everything that Deep-sleep mode does, but also turns off the power to the IRC oscillator and the flash memory. This saves more power but requires waiting for resumption of flash operation before execution of code or data access in the flash memory can be accomplished.

On the wake-up of Power-down mode, if the IRC was used before entering Power-down mode, it will take IRC 60  $\mu$ s to start-up. After this 4 IRC cycles will expire before the code execution can then be resumed if the code was running from SRAM. In the meantime, the flash wake-up timer then counts 4 MHz IRC clock cycles to make the 100  $\mu$ s flash start-up time. When it times out, access to the flash will be allowed. Users need to reconfigure the PLL and clock dividers accordingly.

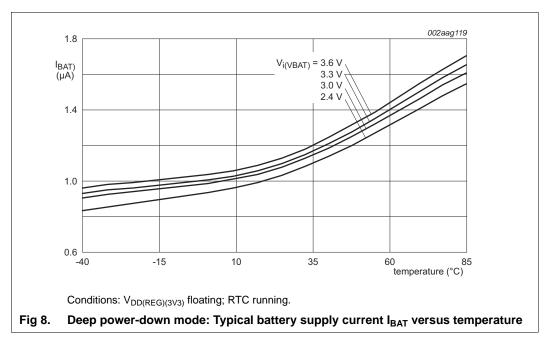

### 8.29.5.4 Deep power-down mode

The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

The LPC1759/58/56/54/52/51 can wake up from Deep power-down mode via the RESET pin or an alarm match event of the RTC.

### 8.29.5.5 Wakeup interrupt controller

The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep sleep, Power-down, and Deep power-down modes.

The Wakeup Interrupt Controller (WIC) works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The Wakeup Interrupt Controller (WIC) eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

### 8.29.6 Peripheral power control

A power control for peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

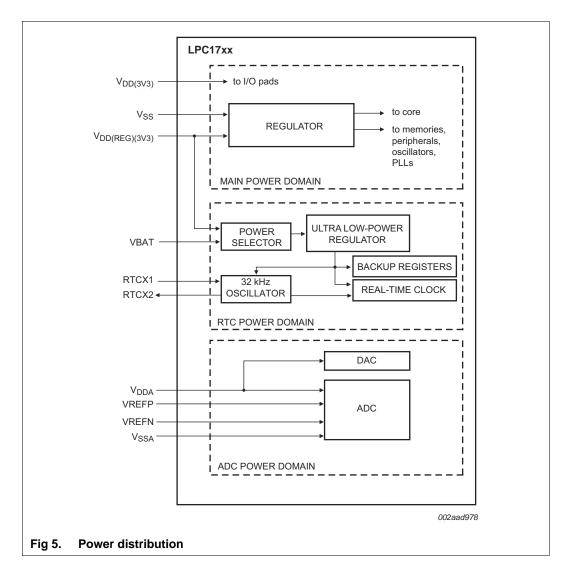

### 8.29.7 Power domains

The LPC1759/58/56/54/52/51 provide two independent power domains that allow the bulk of the device to have power removed while maintaining operation of the RTC and the backup Registers.

32-bit ARM Cortex-M3 microcontroller

### 8.30 System control

### 8.30.1 Reset

Reset has four sources on the LPC17xx: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once the operating voltage attains a usable level, causes the RSTOUT pin to go LOW and starts the wake-up timer (see description in Section 8.29.4). The wake-up timer ensures that reset remains asserted until the external Reset is de-asserted, the oscillator is running, a fixed number of clocks have passed, and the flash controller has completed its initialization. Once reset is de-asserted, or, in case of a BOD-triggered reset, once the voltage rises above the BOD threshold, the RSTOUT pin goes HIGH.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the boot block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

LPC1759 58 56 54 52 51

32-bit ARM Cortex-M3 microcontroller

## 9. Limiting values

#### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                    | Parameter                             | Conditions                                                                                            |        | Min   | Max   | Unit |

|---------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|--------|-------|-------|------|

| V <sub>DD(3V3)</sub>      | supply voltage (3.3 V)                | external rail                                                                                         | [2]    | -0.5  | +4.6  | V    |

| V <sub>DD(REG)(3V3)</sub> | regulator supply voltage (3.3 V)      |                                                                                                       | [2]    | -0.5  | +4.6  | V    |

| V <sub>DDA</sub>          | analog 3.3 V pad supply voltage       |                                                                                                       | [2]    | -0.5  | +4.6  | V    |

| V <sub>i(VBAT)</sub>      | input voltage on pin VBAT             | for the RTC                                                                                           | [2]    | -0.5  | +4.6  | V    |

| V <sub>i(VREFP)</sub>     | input voltage on pin VREFP            |                                                                                                       | [2]    | -0.5  | +4.6  | V    |

| V <sub>IA</sub>           | analog input voltage                  | on ADC related pins                                                                                   | [2][3] | -0.5  | +5.1  | V    |

| VI                        | input voltage                         | 5 V tolerant digital I/O pins; $V_{DD} \ge 2.4 \text{ V}$                                             | [2][4] | -0.5  | +5.5  | V    |

|                           |                                       | V <sub>DD</sub> = 0 V                                                                                 |        | -0.5  | +3.6  |      |

| I <sub>DD</sub>           | supply current                        | per supply pin                                                                                        |        | -     | 100   | mA   |

| I <sub>SS</sub>           | ground current                        | per ground pin                                                                                        |        | -     | 100   | mA   |

| l <sub>latch</sub>        | I/O latch-up current                  | –(0.5V <sub>DD(3V3)</sub> ) < V <sub>I</sub> <<br>(1.5V <sub>DD(3V3)</sub> ); T <sub>j</sub> < 125 °C |        | -     | 100   | mA   |

| T <sub>stg</sub>          | storage temperature                   |                                                                                                       | [5]    | -65   | +150  | °C   |

| T <sub>j(max)</sub>       | maximum junction temperature          |                                                                                                       |        |       | 150   | °C   |

| P <sub>tot(pack)</sub>    | total power dissipation (per package) | based on package heat<br>transfer, not device power<br>consumption                                    |        | -     | 1.5   | W    |

| V <sub>ESD</sub>          | electrostatic discharge voltage       | human body model; all pins                                                                            | [6]    | -4000 | +4000 | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

c) The limiting values are stress ratings only. Operating the part at these values is not recommended, and proper operation is not guaranteed. The conditions for functional operation are specified in <u>Table 7</u>.

[2] Maximum/minimum voltage above the maximum operating voltage (see <u>Table 7</u>) and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter lifetime of the device.

[3] See Table 18 for maximum operating voltage.

- [4] Including voltage on outputs in 3-state mode.

- [5] The maximum non-operating storage temperature is different than the temperature for required shelf life which should be determined based on required shelf lifetime. Please refer to the JEDEC spec (J-STD-033B.1) for further details.

- [6] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor.

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

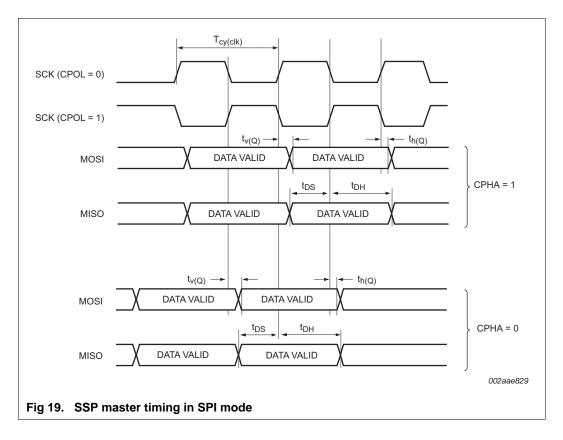

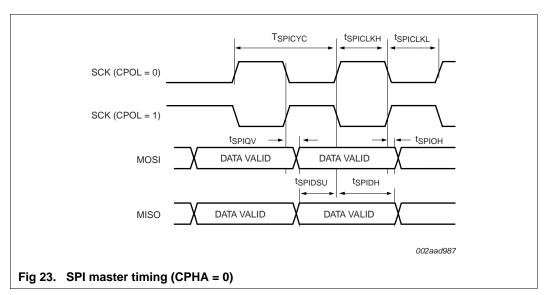

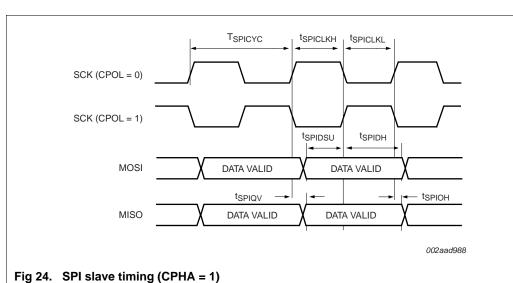

### 12.7 SSP interface

The maximum SSP speed is 33 Mbit/s in master mode or 8 Mbit/s in slave mode. In slave mode, the maximum SSP clock rate must be 1/12 of the SSP PCLK clock rate.

### Table 15. Dynamic characteristics: SSP pins in SPI mode

$C_L = 30 \text{ pF}$  on all SSP pins;  $T_{amb} = -40 \text{ °C}$  to 85 °C;  $V_{DD(3V3)} = 3.3 \text{ V}$  to 3.6 V; input slew = 1 ns; sampled at 10 % and 90 % of the signal level. Values guaranteed by design.

| Symbol            | Parameter              | Conditions  | Min      | Max                           | Unit |

|-------------------|------------------------|-------------|----------|-------------------------------|------|

| SSP mast          | er                     | .1          | <b>I</b> |                               |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1     | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0        | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -        | 2.5                           | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0        | -                             | ns   |

| SSP slave         | )                      |             |          |                               |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1     | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0        | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -        | 3*T <sub>cy(PCLK)</sub> + 2.5 | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0        | -                             | ns   |

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

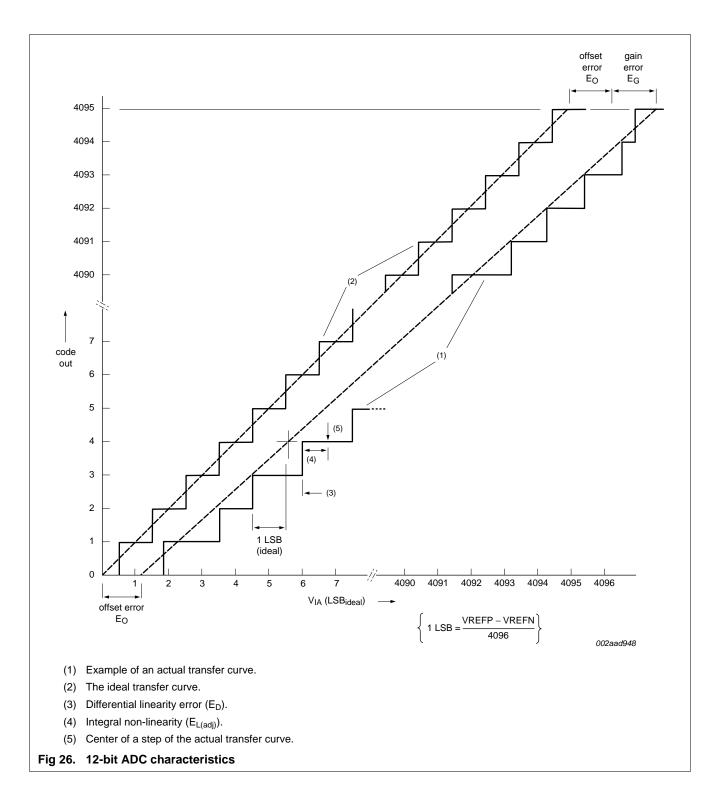

| Symbol                | Parameter                    | Conditions                                                 |        | Min | Тур  | Max | Unit |

|-----------------------|------------------------------|------------------------------------------------------------|--------|-----|------|-----|------|

| E <sub>D</sub>        | differential linearity error |                                                            | [2][3] | -   | ±1   | -   | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity       |                                                            | [4]    | -   | ±1.5 | -   | LSB  |

| Eo                    | offset error                 |                                                            | [5]    | -   | ±2   | -   | LSB  |

| E <sub>G</sub>        | gain error                   |                                                            | [6]    | -   | ±2   | -   | LSB  |

| f <sub>clk(ADC)</sub> | ADC clock frequency          | $3.0~V \leq V_{DDA} \leq 3.6~V$                            |        | -   | -    | 33  | MHz  |

|                       |                              | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} < 3.0 \text{ V}$ |        | -   | -    | 25  | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency     | $3~V \leq V_{DDA} \leq 3.6~V$                              | [7]    | -   | -    | 500 | kHz  |

|                       |                              | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} < 3.0 \text{ V}$ | [7]    | -   | -    | 400 | kHz  |

#### Table 19. ADC characteristics (lower resolution) $T_{1} = 40\%$ to 185% unless otherwise specified: 12-bit ADC

$f_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  unless otherwise specified; 12-bit ADC used as 10-bit resolution ADC.[1]

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[2] The ADC is monotonic, there are no missing codes.

[3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 26.

[4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 26</u>.

[5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See Figure 26.

[6] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 26</u>.

[7] The conversion frequency corresponds to the number of samples per second.

### **NXP Semiconductors**

# LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

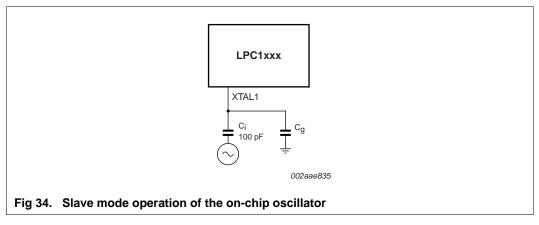

### 15.2 Crystal oscillator XTAL input and component selection

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (Figure 34), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in Figure 35 and in Table 22 and Table 23. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L, C<sub>L</sub> and R<sub>S</sub>). Capacitance C<sub>P</sub> in Figure 35 represents the parallel package capacitance and should not be larger than 7 pF. Parameters F<sub>OSC</sub>, C<sub>L</sub>, R<sub>S</sub> and C<sub>P</sub> are supplied by the crystal manufacturer.

LPC1759 58 56 54 52 51

### 15.6 ElectroMagnetic Compatibility (EMC)

Radiated emission measurements according to the IEC61967-2 standard using the TEM-cell method are shown for part LPC1768.

| Table 24.      | ElectroMagnetic Compatibility (EMC) for part LPC1768 (TEM-cell method) |

|----------------|------------------------------------------------------------------------|

| $V_{DD} = 3.3$ | $V; T_{amb} = 25 \ ^{\circ}C.$                                         |

| Parameter                | Frequency band           | System clock = |        |        |        |         | Unit |

|--------------------------|--------------------------|----------------|--------|--------|--------|---------|------|

|                          |                          | 12 MHz         | 24 MHz | 48 MHz | 72 MHz | 100 MHz |      |

| Input clock:             | RC (4 MHz)               |                |        |        |        |         |      |

| maximum                  | 150 kHz to 30 MHz        | -7             | -6     | -4     | -7     | -7      | dBμV |

| peak level               | 30 MHz to 150 MHz        | +1             | +5     | +11    | +16    | +9      | dBμV |

|                          | 150 MHz to 1 GHz         | -2             | +4     | +11    | +12    | +19     | dBμV |

| IEC level <sup>[1]</sup> | -                        | 0              | 0      | Ν      | М      | L       | -    |

| Input clock:             | crystal oscillator (12 l | MHz)           |        |        |        |         |      |

| maximum<br>peak level    | 150 kHz to 30 MHz        | -5             | -4     | -4     | -7     | -8      | dBμV |

|                          | 30 MHz to 150 MHz        | -1             | +5     | +10    | +15    | +7      | dBμV |

|                          | 150 MHz to 1 GHz         | -1             | +6     | +11    | +10    | +16     | dBμV |

| IEC level <sup>[1]</sup> | -                        | 0              | 0      | Ν      | М      | М       | -    |

[1] IEC levels refer to Appendix D in the IEC61967-2 Specification.

### **NXP Semiconductors**

# LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

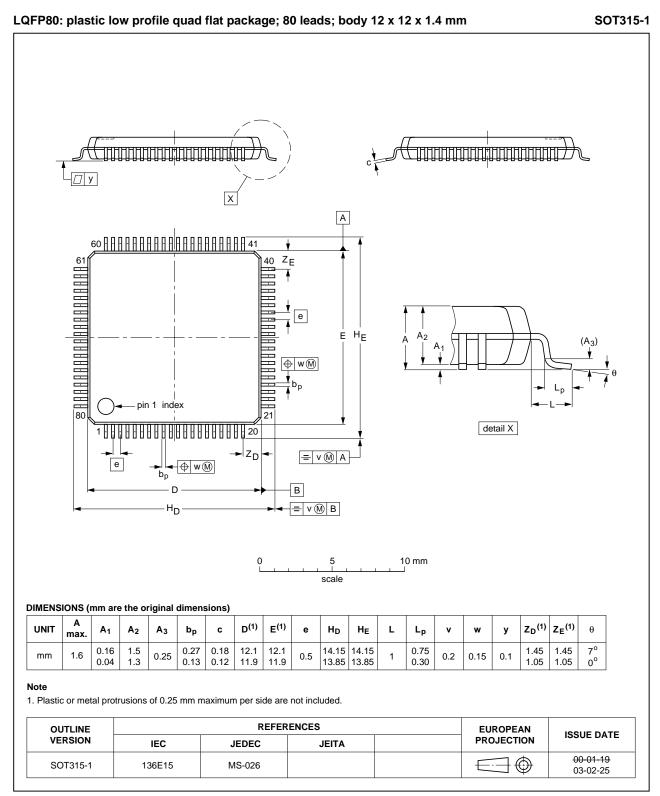

## 16. Package outline

Fig 38. Package outline (LQFP80)

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M3 microcontroller

| Document ID                  | Release date                                                                                                                                                                                 | Data sheet status                                                                                        | Change<br>notice                     | Supersedes                                                     |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|--|--|--|

| LPC1759_58_56_54_52_51 v.8.1 | 20130912                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1759_58_56_54_52_51 v.8                                     |  |  |  |

| Modifications:               | Added Table 6 "Thermal resistance".                                                                                                                                                          |                                                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Table 5 "Limiting values":</li> </ul>                                                                                                                                               |                                                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Updated r</li> </ul>                                                                                                                                                                | nin/max values for V <sub>DD(3</sub>                                                                     | $_{\rm V3)}$ and $\rm V_{\rm D}$     | DD(REG)(3V3)·                                                  |  |  |  |

|                              | <ul> <li>Updated of</li> </ul>                                                                                                                                                               | conditions for V <sub>I</sub> .                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Updated t</li> </ul>                                                                                                                                                                | able notes.                                                                                              |                                      |                                                                |  |  |  |

|                              | <ul> <li>Table 7 "Stati<br/>be externally</li> </ul>                                                                                                                                         |                                                                                                          | I Table not                          | e 14 "TCK/SWDCLK pin needs to                                  |  |  |  |

|                              | Updated Sec                                                                                                                                                                                  | tion 15.1 "Suggested US                                                                                  | B interface                          | e solutions".                                                  |  |  |  |

|                              | Added Section                                                                                                                                                                                | n 5 "Marking".                                                                                           |                                      |                                                                |  |  |  |

|                              |                                                                                                                                                                                              | of Figure 29 from "USB soft-connect".                                                                    | interface of                         | on a self-powered device" to "USB                              |  |  |  |

| LPC1759_58_56_54_52_51 v.8   | 20120809                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1759_58_56_54_52_51 v.7                                     |  |  |  |

| Modifications:               |                                                                                                                                                                                              | e note "The peak current<br>rrent." from Table 4 "Limi                                                   |                                      | to 25 times the corresponding s".                              |  |  |  |

|                              | Change V <sub>DD(</sub>                                                                                                                                                                      | <sub>3V3)</sub> to V <sub>DD(REG)(3V3)</sub> in S                                                        | ection 11.3                          | 3 "Internal oscillators".                                      |  |  |  |

|                              | Glitch filter co                                                                                                                                                                             | onstant changed to 10 ns                                                                                 | s in Table r                         | note 5 in Table 3.                                             |  |  |  |

|                              | <ul> <li>Description o</li> </ul>                                                                                                                                                            | f RESET function update                                                                                  | ed in Table                          | 3.                                                             |  |  |  |

|                              | <ul> <li>Pull-up value added for GPIO pins in Table 3.</li> </ul>                                                                                                                            |                                                                                                          |                                      |                                                                |  |  |  |

|                              | -                                                                                                                                                                                            | tion diagram for LQFP80                                                                                  |                                      |                                                                |  |  |  |

|                              | -                                                                                                                                                                                            | on of USB_UP_LED pin u                                                                                   | -                                    | Table 3.                                                       |  |  |  |

|                              |                                                                                                                                                                                              | bels in Figure 26 update                                                                                 | ed.                                  |                                                                |  |  |  |

|                              | Table note 9 updated in Table 3.                                                                                                                                                             |                                                                                                          |                                      |                                                                |  |  |  |

|                              |                                                                                                                                                                                              | updated in Table 12.                                                                                     |                                      |                                                                |  |  |  |

|                              | -                                                                                                                                                                                            | <ul> <li>Electromagnetic compatibility data added in Section 14.6.</li> <li>Destring 40 added</li> </ul> |                                      |                                                                |  |  |  |

|                              | Section 16 ac                                                                                                                                                                                |                                                                                                          |                                      |                                                                |  |  |  |

| LPC1759_58_56_54_52_51 v.7   | 20110329                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1759_58_56_54_52_51 v.6                                     |  |  |  |

| Modifications:               | • Pin description of pins P0[29] and P0[30] updated in Table note 4 of Table 3. Pins are not 5 V tolerant.                                                                                   |                                                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Typical value for Parameter N<sub>endu</sub> added in Table 8.</li> </ul>                                                                                                           |                                                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Condition 3.0 V ≤ V<sub>DD(3V3)</sub> ≤ 3.6 V added in Table 15.</li> <li>Typical values for parameters I<sub>DD(REG)(3V3)</sub> and I<sub>BAT</sub> with condition Deep</li> </ul> |                                                                                                          |                                      |                                                                |  |  |  |

|                              | <ul> <li>Typical value<br/>power-down<br/>note 11 upda</li> </ul>                                                                                                                            | mode corrected in Table                                                                                  | <sub>)(3V3)</sub> and I<br>6 and Tab | BAT with condition Deep<br>le note 9, Table note 10, and Table |  |  |  |

|                              | For Deep pov                                                                                                                                                                                 | ver-down mode, Figure 8                                                                                  | 8 updated                            | and Figure 9 added.                                            |  |  |  |

| LPC1759_58_56_54_52_51 v.6   | 20100825                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1759_58_56_54_52_51 v.5                                     |  |  |  |

| Modifications:               |                                                                                                                                                                                              | 2; BOD level corrected.                                                                                  |                                      |                                                                |  |  |  |

|                              | Added Section                                                                                                                                                                                |                                                                                                          |                                      |                                                                |  |  |  |

| LPC1759_58_56_54_52_51 v.5   | 20100716                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1759_58_56_54_52_51 v.4                                     |  |  |  |

| LPC1759_58_56_54_52_51 v.4   | 20100126                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1758_56_54_52_51 v.3                                        |  |  |  |

| LPC1758_56_54_52_51 v.3      | 20091119                                                                                                                                                                                     | Product data sheet                                                                                       | -                                    | LPC1758_56_54_52_51 v.2                                        |  |  |  |

| LPC1758_56_54_52_51 v.2      | 20090211                                                                                                                                                                                     | Objective data sheet                                                                                     | -                                    | LPC1758_56_54_52_51 v.1                                        |  |  |  |

| LPC1758_56_54_52_51 v.1      | 20090115                                                                                                                                                                                     | Objective data sheet                                                                                     | -                                    | -                                                              |  |  |  |

#### Table 26. Revision history ... continued

32-bit ARM Cortex-M3 microcontroller

| 10.1              | Thermal characteristics                                                          | 39        |

|-------------------|----------------------------------------------------------------------------------|-----------|

| 11                | Static characteristics                                                           | 40        |

| 11.1              | Power consumption                                                                | 43        |

| 11.2              | Peripheral power consumption                                                     | 46        |

| 11.3              | Electrical pin characteristics                                                   | 47        |

| 12                | Dynamic characteristics                                                          | 49        |

| 12.1              | Flash memory                                                                     | 49        |

| 12.2              | External clock                                                                   | 49        |

| 12.3              | Internal oscillators                                                             | 50        |

| 12.4              | I/O pins                                                                         | 50        |

| 12.5              | I <sup>2</sup> C-bus                                                             | 51        |

| 12.6<br>12.7      | I <sup>2</sup> S-bus interface (LPC1759/58/56 only)                              | 53        |

| 12.7              | SSP interface                                                                    | 55<br>57  |

| 12.0              | SPI                                                                              | 58        |

| 13                | ADC electrical characteristics                                                   | <b>60</b> |

| 13                |                                                                                  | 00        |

| 14                | DAC electrical characteristics<br>(LPC1759/58/56/54 only)                        | 63        |

| 45                |                                                                                  | 64        |

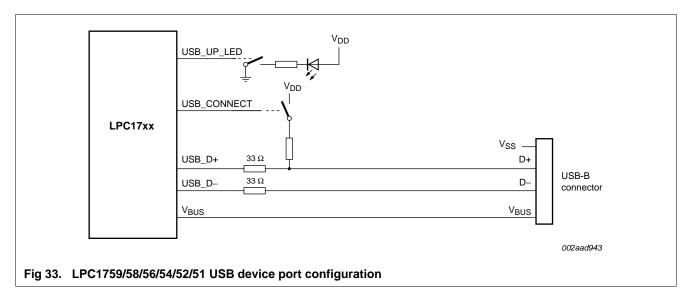

| <b>15</b><br>15.1 | Application information.                                                         | • •       |

| 15.1              | Suggested USB interface solutions<br>Crystal oscillator XTAL input and component | 04        |

| 10.2              | selection                                                                        | 67        |

| 15.3              | XTAL Printed-Circuit Board (PCB) layout                                          | 01        |

| 10.0              | guidelines                                                                       | 68        |

| 15.4              | Standard I/O pin configuration                                                   | 69        |

| 15.5              | Reset pin configuration                                                          | 70        |

| 15.6              | ElectroMagnetic Compatibility (EMC)                                              | 71        |

| 16                | Package outline                                                                  | 72        |

| 17                | Soldering                                                                        | 73        |

| 18                | Abbreviations                                                                    | 74        |

| 19                | References                                                                       | 74        |

| 20                | Revision history                                                                 | 75        |

| 21                | Legal information                                                                | 77        |

| 21.1              | Data sheet status                                                                | 77        |

| 21.2              | Definitions                                                                      | 77        |

| 21.3              | Disclaimers                                                                      | 77        |

| 21.4              | Trademarks                                                                       | 78        |

| 22                | Contact information                                                              | 78        |

| 23                | Contents                                                                         | 79        |

|                   |                                                                                  |           |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP Semiconductors N.V. 2015.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 18 August 2015 Document identifier: LPC1759\_58\_56\_54\_52\_51