Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 120MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, SSP, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT |

| Number of I/O              | 52                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1759fbd80-551        |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

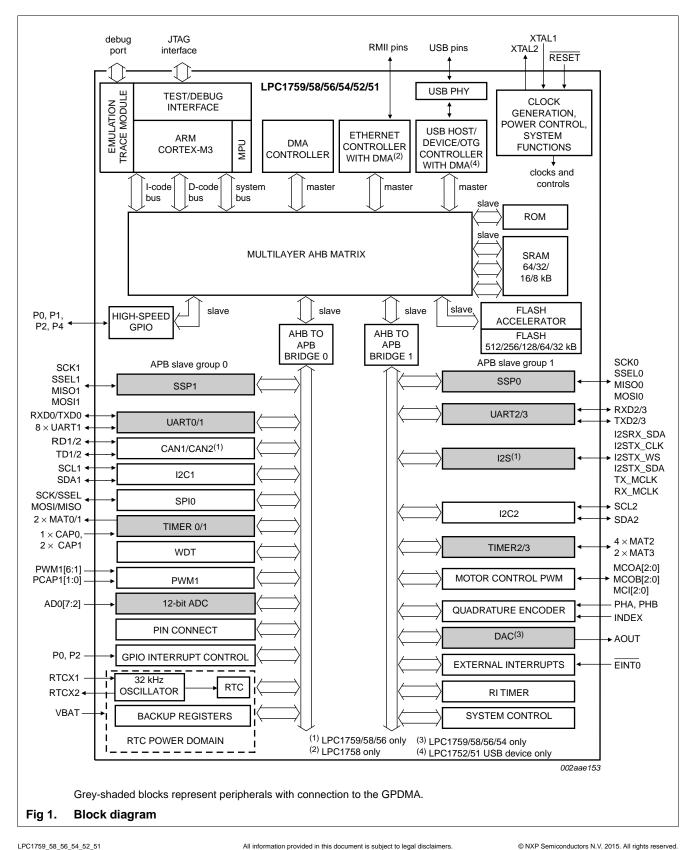

### 32-bit ARM Cortex-M3 microcontroller

# 5. Marking

The LPC175x devices typically have the following top-side marking:

LPC175xxxx

XXXXXXX

xxYYWWR[x]

The last/second to last letter in the third line (field 'R') will identify the device revision. This data sheet covers the following revisions of the LPC175x:

Table 3. Device revision table

| Revision identifier (R) | Revision description    |

|-------------------------|-------------------------|

| (_)<br>(_)              | Initial device revision |

| Ϋ́Α'                    | Second device revision  |

Field 'YY' states the year the device was manufactured. Field 'WW' states the week the device was manufactured during that year.

32-bit ARM Cortex-M3 microcontroller

# 6. Block diagram

PC1759\_58\_56\_54\_52\_51 Product data sheet

### 32-bit ARM Cortex-M3 microcontroller

| Symbol                         | Pin           | Туре                                                                                                                                                                                                | Description                                                                                                                                                                                                     |  |  |  |  |

|--------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P0[7]/I2STX_CLK/               | 63 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[7] — General purpose digital input/output pin.                                                                                                                                                               |  |  |  |  |

| SCK1/MAT2[1]                   |               | I/O                                                                                                                                                                                                 | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> <i>S</i> - <i>bus specification</i> . (LPC1759/58/56 only). |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SCK1 — Serial Clock for SSP1.                                                                                                                                                                                   |  |  |  |  |

|                                |               | 0                                                                                                                                                                                                   | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                  |  |  |  |  |

| P0[8]/I2STX_WS/                | 62 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[8] — General purpose digital input/output pin.                                                                                                                                                               |  |  |  |  |

| MISO1/MAT2[2]                  |               | I/O                                                                                                                                                                                                 | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. (LPC1759/58/56 only).      |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                                           |  |  |  |  |

|                                |               | 0                                                                                                                                                                                                   | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                                                                  |  |  |  |  |

| P0[9]/I2STX_SDA/               | 61 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[9] — General purpose digital input/output pin.                                                                                                                                                               |  |  |  |  |

| MOSI1/MAT2[3]                  |               | <ul> <li>I/O</li> <li>I2STX_SDA — Transmit data. It is driven by the transmitter and reareceiver. Corresponds to the signal SD in the <i>PS-bus specification</i>. (LPC1759/58/56 only).</li> </ul> |                                                                                                                                                                                                                 |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                                           |  |  |  |  |

|                                |               | 0                                                                                                                                                                                                   | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                                                                  |  |  |  |  |

| P0[10]/TXD2/                   | 39[1] I/O     |                                                                                                                                                                                                     | P0[10] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| SDA2/MAT3[0]                   |               | 0                                                                                                                                                                                                   | TXD2 — Transmitter output for UART2.                                                                                                                                                                            |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SDA2 — I <sup>2</sup> C2 data input/output (this is not an open-drain pin).                                                                                                                                     |  |  |  |  |

|                                |               | 0                                                                                                                                                                                                   | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                                                                  |  |  |  |  |

| P0[11]/RXD2/ 40 <sup>[1]</sup> |               | I/O                                                                                                                                                                                                 | P0[11] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| SCL2/MAT3[1]                   |               | I                                                                                                                                                                                                   | <b>RXD2</b> — Receiver input for UART2.                                                                                                                                                                         |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SCL2 — I <sup>2</sup> C2 clock input/output (this is not an open-drain pin).                                                                                                                                    |  |  |  |  |

|                                |               | 0                                                                                                                                                                                                   | MAT3[1] — Match output for Timer 3, channel 1.                                                                                                                                                                  |  |  |  |  |

| P0[15]/TXD1/                   | 47 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[15] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| SCK0/SCK                       |               | 0                                                                                                                                                                                                   | <b>TXD1</b> — Transmitter output for UART1.                                                                                                                                                                     |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SCK0 — Serial clock for SSP0.                                                                                                                                                                                   |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SCK — Serial clock for SPI.                                                                                                                                                                                     |  |  |  |  |

| P0[16]/RXD1/                   | 48 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[16] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| SSEL0/SSEL                     |               | I                                                                                                                                                                                                   | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                                         |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SSEL0 — Slave Select for SSP0.                                                                                                                                                                                  |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | SSEL — Slave Select for SPI.                                                                                                                                                                                    |  |  |  |  |

| P0[17]/CTS1/                   | 46 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[17] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| MISO0/MISO                     |               | 1                                                                                                                                                                                                   | CTS1 — Clear to Send input for UART1.                                                                                                                                                                           |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                           |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MISO — Master In Slave Out for SPI.                                                                                                                                                                             |  |  |  |  |

| P0[18]/DCD1/                   | 45 <u>[1]</u> | I/O                                                                                                                                                                                                 | P0[18] — General purpose digital input/output pin.                                                                                                                                                              |  |  |  |  |

| MOSI0/MOSI                     |               | 1                                                                                                                                                                                                   | DCD1 — Data Carrier Detect input for UART1.                                                                                                                                                                     |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                           |  |  |  |  |

|                                |               | I/O                                                                                                                                                                                                 | MOSI — Master Out Slave In for SPI.                                                                                                                                                                             |  |  |  |  |

#### Table 4. Pin description ...continued

LPC1759\_58\_56\_54\_52\_51

All information provided in this document is subject to legal disclaimers.

#### 32-bit ARM Cortex-M3 microcontroller

### 8.13.1 Features

- One or two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes standard (11-bit) and extended-frame (29-bit) receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

# 8.14 12-bit ADC

The LPC1759/58/56/54/52/51 contain one ADC. It is a single 12-bit successive approximation ADC with six channels and DMA support.

### 8.14.1 Features

- 12-bit successive approximation ADC.

- Input multiplexing among 6 pins.

- Power-down mode.

- Measurement range VREFN to VREFP.

- 12-bit conversion rate: 200 kHz.

- Individual channels can be selected for conversion.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- DMA support.

# 8.15 10-bit DAC (LPC1759/58/56/54 only)

The DAC allows to generate a variable analog output. The maximum output value of the DAC is VREFP.

### 8.15.1 Features

- 10-bit DAC

- Resistor string architecture

- Buffered output

- Power-down mode

- Selectable output drive

- Dedicated conversion timer

- DMA support

© NXP Semiconductors N.V. 2015. All rights reserved.

### 32-bit ARM Cortex-M3 microcontroller

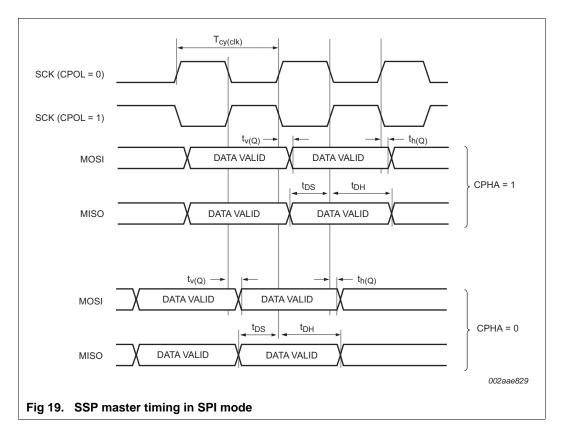

bus during a given data transfer. The SSP supports full duplex transfers, with frames of 4 bits to 16 bits of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

### 8.18.1 Features

- Maximum SSP speed of 33 Mbit/s (master) or 8 Mbit/s (slave)

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

- Master or slave operation

- 8-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

- DMA transfers supported by GPDMA

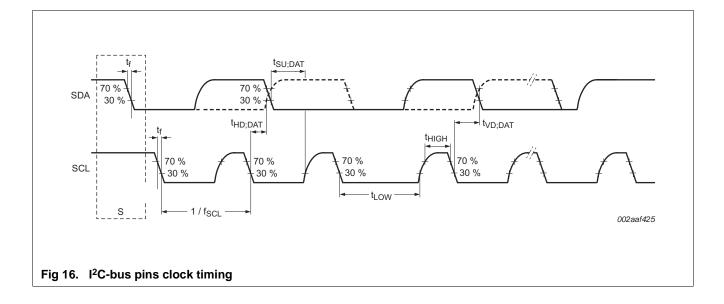

## 8.19 I<sup>2</sup>C-bus serial I/O controllers

The LPC1759/58/56/54/52/51 each contain two I<sup>2</sup>C-bus controllers.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock Line (SCL) and a Serial DAta line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

### 8.19.1 Features

- I<sup>2</sup>C1 and I<sup>2</sup>C2 use standard I/O pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus).

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- Both I<sup>2</sup>C-bus controllers support multiple address recognition and a bus monitor mode.

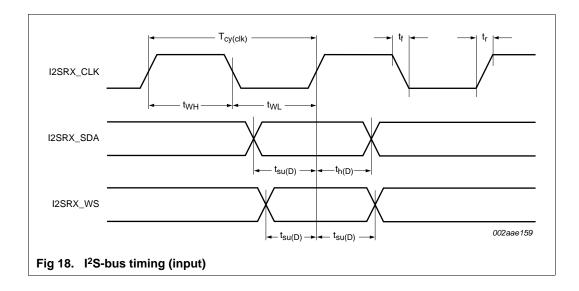

# 8.20 I<sup>2</sup>S-bus serial I/O controllers (LPC1759/58/56 only)

The I<sup>2</sup>S-bus provides a standard communication interface for digital audio applications.

### 32-bit ARM Cortex-M3 microcontroller

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

### 8.22 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC1759/58/56/54/52/51. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

### 8.22.1 Features

- LPC1759/58/56/54/52/51 has one PWM block with Counter or Timer operation (may use the peripheral clock or one of the capture inputs as the clock source).

- Seven match registers allow up to 6 single edge controlled or 3 double edge controlled PWM outputs, or a mix of both types. The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Supports single edge controlled and/or double edge controlled PWM outputs. Single

edge controlled PWM outputs all go high at the beginning of each cycle unless the

output is a constant low. Double edge controlled PWM outputs can have either edge

occur at any position within a cycle. This allows for both positive going and negative

going pulses.

### 32-bit ARM Cortex-M3 microcontroller

# 8.25 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 32-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

### 8.25.1 Features

- 32-bit counter running from PCLK. Counter can be free-running or be reset by a generated interrupt.

- 32-bit compare value.

- 32-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This allows for combinations not possible with a simple compare.

## 8.26 ARM Cortex-M3 system tick timer

The ARM Cortex-M3 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval. In the LPC1759/58/56/54/52/51, this timer can be clocked from the internal AHB clock or from a device pin.

### 8.27 Watchdog timer

The purpose of the watchdog is to reset the microcontroller within a reasonable amount of time if it enters an erroneous state. When enabled, the watchdog will generate a system reset if the user program fails to 'feed' (or reload) the watchdog within a predetermined amount of time.

### 8.27.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{32} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC (IRC) oscillator, the RTC oscillator, or the APB peripheral clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

- Includes lock/safe feature.

32-bit ARM Cortex-M3 microcontroller

| Symbol               | Parameter                                  | Conditions                                                                        |                  | Min                           | Typ <u>[1]</u> | Max                     | Unit |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------|------------------|-------------------------------|----------------|-------------------------|------|

| I <sub>DD(ADC)</sub> | ADC supply current                         | active mode;                                                                      | [16][17]         | -                             | 1.95           | -                       | mA   |

|                      |                                            | ADC powered                                                                       |                  |                               |                |                         |      |

|                      |                                            | ADC in Power-down mode                                                            | [16][18]         | -                             | <0.2           | -                       | μA   |

|                      |                                            | Deep sleep mode                                                                   | [16]             | -                             | 38             | -                       | nA   |

|                      |                                            | Power-down mode                                                                   | [16]             | -                             | 38             | -                       | nA   |

|                      |                                            | Deep power-down mode                                                              | [16]             | -                             | 24             | -                       | nA   |

| I <sub>I(ADC)</sub>  | ADC input current                          | on pin VREFP                                                                      |                  |                               |                |                         |      |

|                      |                                            | Deep sleep mode                                                                   | [19]             | -                             | 100            | -                       | nA   |

|                      |                                            | Power-down mode                                                                   | [19]             | -                             | 100            | -                       | nA   |

|                      |                                            | Deep power-down<br>mode                                                           | [19]             | -                             | 100            | -                       | nA   |

| Standard po          | rt pins, RESET                             |                                                                                   |                  |                               |                |                         |      |

| IIL                  | LOW-level input current                    | $V_I = 0 V$ ; on-chip pull-up resistor disabled                                   |                  | -                             | 0.5            | 10                      | nA   |

| Iн                   | HIGH-level input<br>current                | $V_{I} = V_{DD(3V3)}$ ; on-chip<br>pull-down resistor<br>disabled                 |                  | -                             | 0.5            | 10                      | nA   |

| l <sub>oz</sub>      | OFF-state output<br>current                | $V_O = 0 V$ ; $V_O = V_{DD(3V3)}$ ;<br>on-chip pull-up/down<br>resistors disabled |                  | -                             | 0.5            | 10                      | nA   |

| VI                   | input voltage                              | pin configured to provide a digital function                                      | [20][21]<br>[22] | 0                             | -              | 5.0                     | V    |

| Vo                   | output voltage                             | output active                                                                     |                  | 0                             | -              | V <sub>DD(3V3)</sub>    | V    |

| V <sub>IH</sub>      | HIGH-level input<br>voltage                |                                                                                   |                  | 0.7V <sub>DD(3V3)</sub>       | -              | -                       | V    |

| VIL                  | LOW-level input voltage                    |                                                                                   |                  | -                             | -              | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>     | hysteresis voltage                         |                                                                                   |                  | 0.4                           | -              | -                       | V    |

| V <sub>OH</sub>      | HIGH-level output voltage                  | $I_{OH} = -4 \text{ mA}$                                                          |                  | V <sub>DD(3V3)</sub> -<br>0.4 | -              | -                       | V    |

| V <sub>OL</sub>      | LOW-level output voltage                   | I <sub>OL</sub> = 4 mA                                                            |                  | -                             | -              | 0.4                     | V    |

| I <sub>ОН</sub>      | HIGH-level output<br>current               | $V_{OH} = V_{DD(3V3)} - 0.4 V$                                                    |                  | -4                            | -              | -                       | mA   |

| I <sub>OL</sub>      | LOW-level output<br>current                | V <sub>OL</sub> = 0.4 V                                                           |                  | 4                             | -              | -                       | mA   |

| I <sub>OHS</sub>     | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V                                                             | [23]             | -                             | -              | -45                     | mA   |

| I <sub>OLS</sub>     | LOW-level short-circuit<br>output current  | $V_{OL} = V_{DD(3V3)}$                                                            | [23]             | -                             | -              | 50                      | mA   |

| I <sub>pd</sub>      | pull-down current                          | V <sub>I</sub> = 5 V                                                              |                  | 10                            | 50             | 150                     | μΑ   |

| I <sub>pu</sub>      | pull-up current                            | V <sub>I</sub> = 0 V                                                              |                  | -15                           | -50            | -85                     | μΑ   |

|                      |                                            | $V_{DD(3V3)} < V_{I} < 5 V$                                                       |                  | 0                             | 0              | 0                       | μA   |

# Table 7. Static characteristics ... continued

# **NXP Semiconductors**

# LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

## 12.7 SSP interface

The maximum SSP speed is 33 Mbit/s in master mode or 8 Mbit/s in slave mode. In slave mode, the maximum SSP clock rate must be 1/12 of the SSP PCLK clock rate.

## Table 15. Dynamic characteristics: SSP pins in SPI mode

$C_L = 30 \text{ pF}$  on all SSP pins;  $T_{amb} = -40 \text{ °C}$  to 85 °C;  $V_{DD(3V3)} = 3.3 \text{ V}$  to 3.6 V; input slew = 1 ns; sampled at 10 % and 90 % of the signal level. Values guaranteed by design.

| Symbol            | Parameter              | Conditions  | Min      | Max                           | Unit |

|-------------------|------------------------|-------------|----------|-------------------------------|------|

| SSP master        | r                      | I           | <b>I</b> |                               |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1     | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0        | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -        | 2.5                           | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0        | -                             | ns   |

| SSP slave         |                        |             |          |                               |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1     | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0        | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -        | 3*T <sub>cy(PCLK)</sub> + 2.5 | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0        | -                             | ns   |

32-bit ARM Cortex-M3 microcontroller

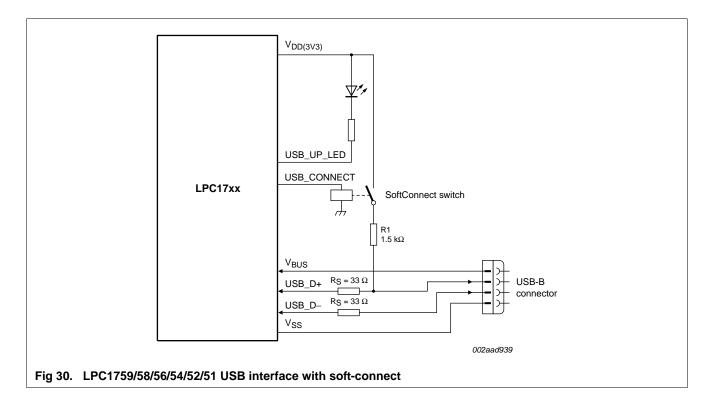

# 12.8 USB interface

#### Table 16. Dynamic characteristics: USB pins (full-speed)

$C_L = 50 \ pF; R_{pu} = 1.5 \ k\Omega \ on \ D+ to \ V_{DD(3V3)}; 3.0 \ V \le V_{DD(3V3)} \le 3.6 \ V.$

| Symbol             | Parameter                                                   | Conditions                              |     | Min   | Тур | Мах   | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------------------|-----|-------|-----|-------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |     | 8.5   | -   | 13.8  | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |     | 7.7   | -   | 13.7  | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |     | -     | -   | 109   | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |     | 1.3   | -   | 2.0   | V    |

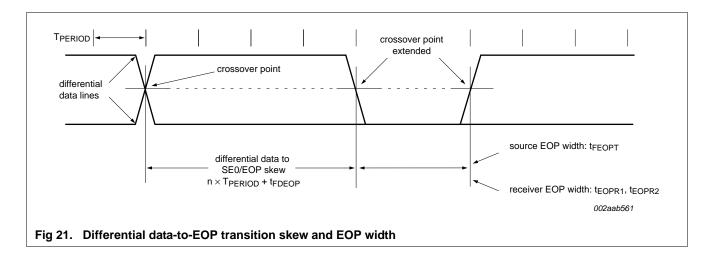

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 21                           |     | 160   | -   | 175   | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see <u>Figure 21</u>                    |     | -2    | -   | +5    | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |     | -18.5 | -   | +18.5 | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |     | -9    | -   | +9    | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 21 | [1] | 40    | -   | -     | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 21 | [1] | 82    | -   | -     | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

32-bit ARM Cortex-M3 microcontroller

| Symbol                | Parameter                    | Conditions                                                 |        | Min | Тур  | Max | Unit |

|-----------------------|------------------------------|------------------------------------------------------------|--------|-----|------|-----|------|

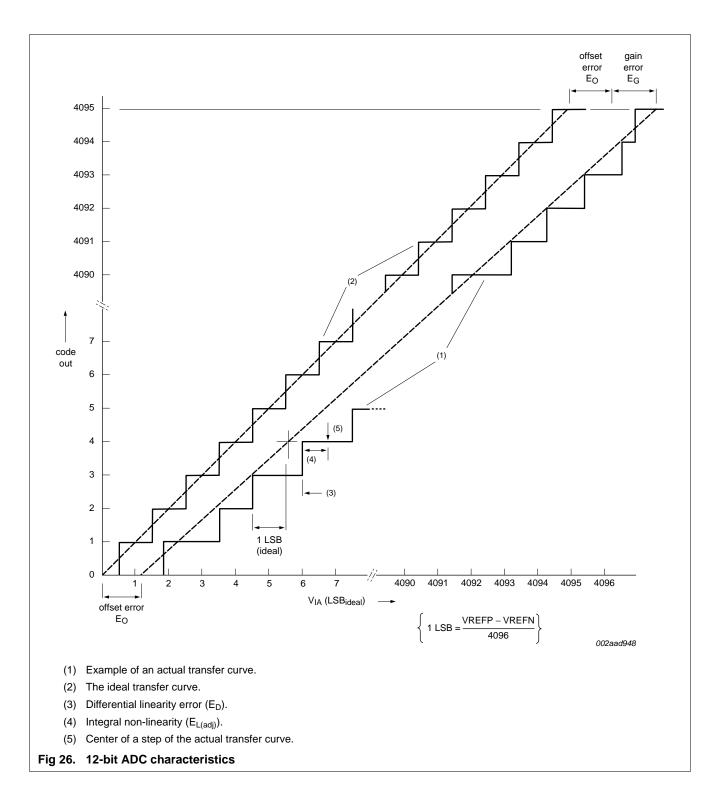

| E <sub>D</sub>        | differential linearity error |                                                            | [2][3] | -   | ±1   | -   | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity       |                                                            | [4]    | -   | ±1.5 | -   | LSB  |

| Eo                    | offset error                 |                                                            | [5]    | -   | ±2   | -   | LSB  |

| E <sub>G</sub>        | gain error                   |                                                            | [6]    | -   | ±2   | -   | LSB  |

| f <sub>clk(ADC)</sub> | ADC clock frequency          | $3.0~V \leq V_{DDA} \leq 3.6~V$                            |        | -   | -    | 33  | MHz  |

|                       |                              | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} < 3.0 \text{ V}$ |        | -   | -    | 25  | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency     | $3~V \leq V_{DDA} \leq 3.6~V$                              | [7]    | -   | -    | 500 | kHz  |

|                       |                              | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} < 3.0 \text{ V}$ | [7]    | -   | -    | 400 | kHz  |

#### Table 19. ADC characteristics (lower resolution) $T_{1} = 40\%$ to 185% unless otherwise specified: 12-bit ADC

$f_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$  unless otherwise specified; 12-bit ADC used as 10-bit resolution ADC.[1]

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[2] The ADC is monotonic, there are no missing codes.

[3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 26.

[4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 26</u>.

[5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See Figure 26.

[6] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 26</u>.

[7] The conversion frequency corresponds to the number of samples per second.

## **NXP Semiconductors**

# LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

# **15. Application information**

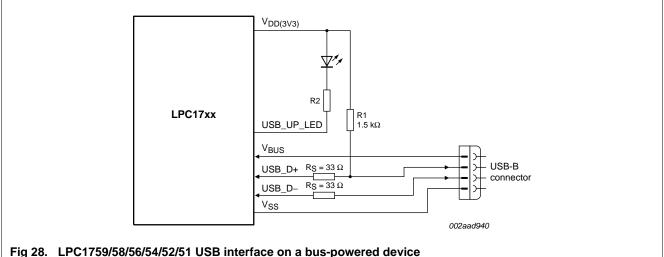

### 15.1 Suggested USB interface solutions

If the LPC1759/58/56/54/52/51 V<sub>DD</sub> is always greater than 0 V while V<sub>BUS</sub> = 5 V, the V<sub>BUS</sub> pin can be connected directly to the V<sub>BUS</sub> pin on the USB connector.

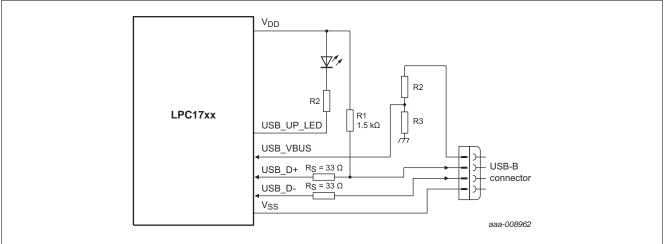

This applies to bus powered devices where the USB cable supplies the system power. For systems where  $V_{DD}$  can be 0 V and  $V_{BUS}$  is directly applied to the  $V_{BUS}$  pin, precautions must be taken to reduce the voltage to below 3.6 V.

The maximum allowable voltage on the V<sub>BUS</sub> pin is 3.6 V. One method is to use a voltage divider to connect the V<sub>BUS</sub> pin to the V<sub>BUS</sub> on the USB connector.

The voltage divider ratio should be such that the  $V_{BUS}$  pin will be greater than  $0.7V_{DD}$  to indicate a logic HIGH while below the 3.6 V allowable maximum voltage.

Use the following operating conditions:

$VBUS_{max} = 5.25 V$

$V_{DD} = 3.6 V$

The voltage divider would need to provide a reduction of 3.6 V/5.25 V or ~0.686 V.

## **NXP Semiconductors**

# LPC1759/58/56/54/52/51

### 32-bit ARM Cortex-M3 microcontroller

Fig 29. USB interface on a bus-powered device where  $V_{BUS} = 5 V$ ,  $V_{DD}$  not present

32-bit ARM Cortex-M3 microcontroller

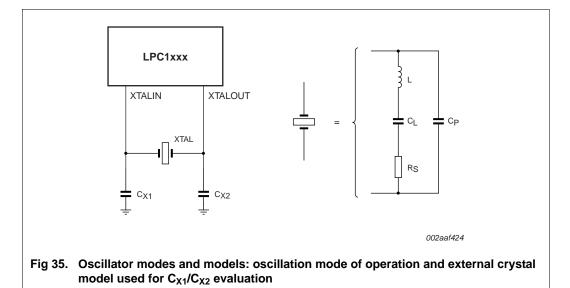

| Table 22. | Recommended values for $C_{X1}/C_{X2}$ in oscillation mode (crystal and external |

|-----------|----------------------------------------------------------------------------------|

|           | components parameters): low frequency mode                                       |

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> /C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| 1 MHz to 5 MHz                                     | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 300 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 300 Ω                                             | 57 pF, 57 pF                                                 |

| 5 MHz to 10 MHz                                    | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 200 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 100 Ω                                             | 57 pF, 57 pF                                                 |

| 10 MHz to 15 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 60 Ω                                              | 39 pF, 39 pF                                                 |

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 80 Ω                                              | 18 pF, 18 pF                                                 |

Table 23. Recommended values for  $C_{X1}/C_{X2}$  in oscillation mode (crystal and external components parameters): high frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 180 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 100 Ω                                             | 39 pF, 39 pF                                                  |

| 20 MHz to 25 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 80 Ω                                              | 39 pF, 39 pF                                                  |

# 15.3 XTAL Printed-Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in

32-bit ARM Cortex-M3 microcontroller

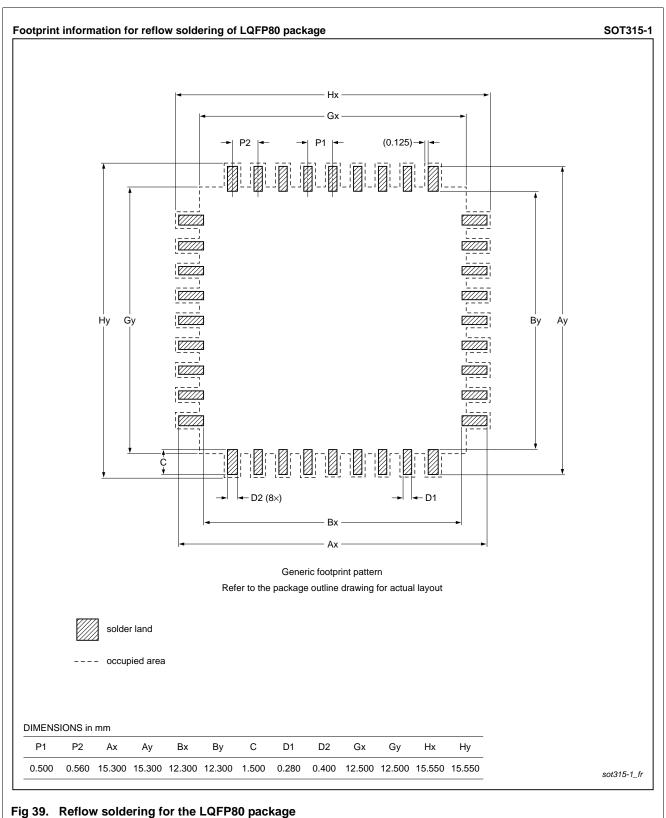

# 17. Soldering

All information provided in this document is subject to legal disclaimers.

32-bit ARM Cortex-M3 microcontroller

# 20. Revision history

#### Table 26.Revision history

| Document ID                  | Release date                                                                                                                                  | Data sheet status                                                 | Change<br>notice   | Supersedes                                                            |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------|--|--|

| LPC1759_58_56_54_52_51 v.8.6 | 20150818                                                                                                                                      | Product data sheet                                                | -                  | LPC1759_58_56_54_52_51 v.8.5                                          |  |  |

| Modifications:               |                                                                                                                                               | value of t <sub>v(Q)</sub> (data outpu<br>15 "Dynamic characteris |                    | e) in SPI mode to 3*T <sub>cy(PCLK)</sub> + 2.5<br>pins in SPI mode". |  |  |

|                              |                                                                                                                                               | ion 2 "Features and ben<br>SDL) is not available for t            |                    | ed Boundary scan Description                                          |  |  |

|                              | <ul> <li>Updated Figure 3 "LPC1759/58/56/54/52/51 memory map": APB0 slot 7<br/>(0x4001C000) was "reserved" and changed it to I2C0.</li> </ul> |                                                                   |                    |                                                                       |  |  |

|                              |                                                                                                                                               | mn for GPIO pins and de<br>See <u>Table 2 "Ordering o</u>         |                    | part number to the ordering                                           |  |  |

| LPC1759_58_56_54_52_51 v.8.5 | 20140624                                                                                                                                      | Product data sheet                                                | -                  | LPC1759_58_56_54_52_51 v.8.4                                          |  |  |

| Modifications:               |                                                                                                                                               | agram updated. SSP tim<br>ection 12.7 "SSP interfa                |                    | eters $t_{v(Q)},t_{h(Q)},t_{DS},\text{and}t_{DH}$                     |  |  |

|                              | <ul> <li>SSP maximur</li> </ul>                                                                                                               | m bit rate in master mode                                         | e corrected        | d to 33 Mbit/s.                                                       |  |  |

|                              | <ul> <li>Parameter T<sub>j</sub></li> </ul>                                                                                                   | <sub>max)</sub> added in <u>Table 5 "Li</u>                       | miting valu        | les".                                                                 |  |  |

|                              | <ul> <li>Description of</li> </ul>                                                                                                            | capture channels correct                                          | cted in <u>Sec</u> | ction 8.21.1.                                                         |  |  |

| LPC1759_58_56_54_52_51 v.8.4 | 20140404                                                                                                                                      | Product data sheet                                                | -                  | LPC1759_58_56_54_52_51 v.8.3                                          |  |  |

| Modifications:               | <ul> <li>Table 4 "Pin d<br/>OUTPUT.</li> </ul>                                                                                                | lescription": Changed R>                                          | (_MCLK a           | nd TX_MCLK type from INPUT to                                         |  |  |

| LPC1759_58_56_54_52_51 v.8.3 | 20140108                                                                                                                                      | Product data sheet                                                | -                  | LPC1759_58_56_54_52_51 v.8.2                                          |  |  |

| Modifications:               | Table 6 "There                                                                                                                                | mal resistance (±15 %)":                                          | Added ±1           | 5 % to table title.                                                   |  |  |

| LPC1759_58_56_54_52_51 v.8.2 | 20131018                                                                                                                                      | Product data sheet                                                | -                  | LPC1759_58_56_54_52_51 v.8.1                                          |  |  |

| Modifications:               | <ul> <li>Table 5 "Limit<br/>V<sub>I</sub>.</li> </ul>                                                                                         | ing values": Removed co                                           | ondition "5        | V tolerant open-drain pins" from                                      |  |  |

|                              | Table 7 "Static                                                                                                                               | c characteristics":                                               |                    |                                                                       |  |  |

|                              |                                                                                                                                               | ble note 3 "VDDA and VF<br>are not used."                         | REFP shou          | Ild be tied to VDD(3V3) if the ADC                                    |  |  |

|                              | <ul> <li>Added Tab</li> </ul>                                                                                                                 | ble note 4 "VDDA for DA                                           | C specs ar         | re from 2.7 V to 3.6 V."                                              |  |  |

|                              | – V <sub>DDA</sub> /VRE                                                                                                                       | FP spec changed from 2                                            | 2.7 V to 2.5       | 5 V.                                                                  |  |  |

|                              | • Table 18 "ADO                                                                                                                               | C characteristics (full res                                       | olution)":         |                                                                       |  |  |

|                              | <ul> <li>Added Table note 1 "VDDA and VREFP should be tied to VDD(3V3) if the ADC<br/>and DAC are not used."</li> </ul>                       |                                                                   |                    |                                                                       |  |  |

|                              | – V <sub>DDA</sub> chan                                                                                                                       | iged from 2.7 V to 2.5 V.                                         |                    |                                                                       |  |  |

|                              |                                                                                                                                               | C characteristics (lower r<br>d be tied to VDD(3V3) if            | ,                  | ": Added Table note 1 "VDDA and and DAC are not used."                |  |  |

#### 32-bit ARM Cortex-M3 microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

# 22. Contact information

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# 21.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP Semiconductors N.V.

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

LPC1759\_58\_56\_54\_52\_51

78 of 80