Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                         |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                            |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-TQFP                                                                 |

| Supplier Device Package    | 64-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg942f512-qfp64t |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1 Ordering Information**

Table 1.1 (p. 2) shows the available EFM32GG942 devices.

#### Table 1.1. Ordering Information

| Ordering Code            | Flash (kB) | RAM (kB) | Max<br>Speed<br>(MHz) | Supply<br>Voltage<br>(V) | Temperature<br>(ºC) | Package |

|--------------------------|------------|----------|-----------------------|--------------------------|---------------------|---------|

| EFM32GG942F512G-E-QFP64  | 512        | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | TQFP64  |

| EFM32GG942F1024G-E-QFP64 | 1024       | 128      | 48                    | 1.98 - 3.8               | -40 - 85            | TQFP64  |

Adding the suffix 'R' to the part number (e.g. EFM32GG942F512G-E-QFP64R) denotes tape and reel.

Visit www.silabs.com for information on global distributors and representatives.

Descriptor-Based Scatter/Gather DMA and supports up to 6 OUT endpoints and 6 IN endpoints, in addition to endpoint 0. The on-chip PHY includes all OTG features, except for the voltage booster for supplying 5V to VBUS when operating as host.

## 2.1.11 Inter-Integrated Circuit Interface (I2C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C-bus. It is capable of acting as both a master and a slave, and supports multi-master buses. Both standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates all the way from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also provided to allow implementation of an SMBus compliant system. The interface provided to software by the I<sup>2</sup>C module, allows both fine-grained control of the transmission process and close to automatic transfers. Automatic recognition of slave addresses is provided in all energy modes.

# 2.1.12 Universal Synchronous/Asynchronous Receiver/Transmitter (US-ART)

The Universal Synchronous Asynchronous serial Receiver and Transmitter (USART) is a very flexible serial I/O module. It supports full duplex asynchronous UART communication as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with ISO7816 SmartCards, IrDA and I2S devices.

## 2.1.13 Pre-Programmed USB/UART Bootloader

The bootloader presented in application note AN0042 is pre-programmed in the device at factory. The bootloader enables users to program the EFM32 through a UART or a USB CDC class virtual UART without the need for a debugger. The autobaud feature, interface and commands are described further in the application note.

# 2.1.14 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

### 2.1.15 Timer/Counter (TIMER)

The 16-bit general purpose Timer has 3 compare/capture channels for input capture and compare/Pulse-Width Modulation (PWM) output. TIMER0 also includes a Dead-Time Insertion module suitable for motor control applications.

## 2.1.16 Real Time Counter (RTC)

The Real Time Counter (RTC) contains a 24-bit counter and is clocked either by a 32.768 kHz crystal oscillator, or a 32.768 kHz RC oscillator. In addition to energy modes EM0 and EM1, the RTC is also available in EM2. This makes it ideal for keeping track of time since the RTC is enabled in EM2 where most of the device is powered down.

### 2.1.17 Backup Real Time Counter (BURTC)

The Backup Real Time Counter (BURTC) contains a 32-bit counter and is clocked either by a 32.768 kHz crystal oscillator, a 32.768 kHz RC oscillator or a 1 kHz ULFRCO. The BURTC is available in all Energy Modes and it can also run in backup mode, making it operational even if the main power should drain out.

# **3 Electrical Characteristics**

## **3.1 Test Conditions**

#### 3.1.1 Typical Values

The typical data are based on  $T_{AMB}$ =25°C and  $V_{DD}$ =3.0 V, as defined in Table 3.2 (p. 10), unless otherwise specified.

#### 3.1.2 Minimum and Maximum Values

The minimum and maximum values represent the worst conditions of ambient temperature, supply voltage and frequencies, as defined in Table 3.2 (p. 10), unless otherwise specified.

## **3.2 Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings, and functional operation under such conditions are not guaranteed. Stress beyond the limits specified in Table 3.1 (p. 10) may affect the device reliability or cause permanent damage to the device. Functional operating conditions are given in Table 3.2 (p. 10).

#### Table 3.1. Absolute Maximum Ratings

| Symbol             | Parameter                         | Condition                              | Min  | Тур | Мах                  | Unit |

|--------------------|-----------------------------------|----------------------------------------|------|-----|----------------------|------|

| T <sub>STG</sub>   | Storage tempera-<br>ture range    |                                        | -40  |     | 150                  | °C   |

| Τ <sub>S</sub>     | Maximum soldering temperature     | Latest IPC/JEDEC J-STD-020<br>Standard |      |     | 260                  | °C   |

| V <sub>DDMAX</sub> | External main sup-<br>ply voltage |                                        | 0    |     | 3.8                  | V    |

| VIOPIN             | Voltage on any I/O<br>pin         |                                        | -0.3 |     | V <sub>DD</sub> +0.3 | V    |

| 1                  | Current per I/O pin<br>(sink)     |                                        |      |     | 100                  | mA   |

| I <sub>IOMAX</sub> | Current per I/O pin<br>(source)   |                                        |      |     | -100                 | mA   |

## **3.3 General Operating Conditions**

### 3.3.1 General Operating Conditions

#### Table 3.2. General Operating Conditions

| Symbol            | Parameter                    | Min  | Тур | Max | Unit |

|-------------------|------------------------------|------|-----|-----|------|

| T <sub>AMB</sub>  | Ambient temperature range    | -40  |     | 85  | °C   |

| V <sub>DDOP</sub> | Operating supply voltage     | 1.98 |     | 3.8 | V    |

| f <sub>APB</sub>  | Internal APB clock frequency |      |     | 48  | MHz  |

| f <sub>AHB</sub>  | Internal AHB clock frequency |      |     | 48  | MHz  |

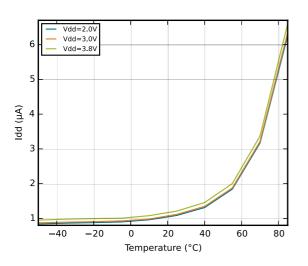

### 3.4.1 EM2 Current Consumption

Figure 3.1. EM2 current consumption. RTC<sup>1</sup> prescaled to 1 Hz, 32.768 kHz LFRCO.

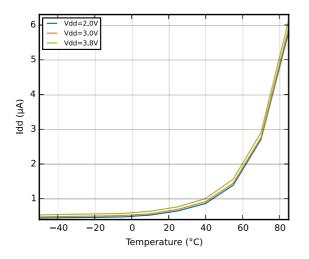

### 3.4.2 EM3 Current Consumption

Figure 3.2. EM3 current consumption.

<sup>&</sup>lt;sup>1</sup>Using backup RTC.

## 3.7 Flash

#### Table 3.6. Flash

| Symbol               | Parameter                                           | Condition               | Min   | Тур  | Max             | Unit   |

|----------------------|-----------------------------------------------------|-------------------------|-------|------|-----------------|--------|

| EC <sub>FLASH</sub>  | Flash erase cycles before failure                   |                         | 20000 |      |                 | cycles |

|                      |                                                     | T <sub>AMB</sub> <150°C | 10000 |      |                 | h      |

| RET <sub>FLASH</sub> | Flash data retention                                | T <sub>AMB</sub> <85°C  | 10    |      |                 | years  |

|                      |                                                     | T <sub>AMB</sub> <70°C  | 20    |      |                 | years  |

| t <sub>W_PROG</sub>  | Word (32-bit) pro-<br>gramming time                 |                         | 20    |      |                 | μs     |

|                      | Dago orogo timo                                     | LPERASE == 0            | 20    | 20.4 | 20.8            | ms     |

| t <sub>PERASE</sub>  | Page erase time                                     | LPERASE == 1            | 40    | 40.4 | 40.8            | ms     |

| t <sub>DERASE</sub>  | Device erase time                                   |                         |       |      | 161.6           | ms     |

|                      |                                                     | LPERASE == 0            |       |      | 14 <sup>1</sup> | mA     |

| I <sub>ERASE</sub>   | Erase current                                       | LPERASE == 1            |       |      | 7 <sup>1</sup>  | mA     |

|                      |                                                     | LPWRITE == 0            |       |      | 14 <sup>1</sup> | mA     |

| I <sub>WRITE</sub>   | Write current                                       | LPWRITE == 1            |       |      | 7 <sup>1</sup>  | mA     |

| V <sub>FLASH</sub>   | Supply voltage dur-<br>ing flash erase and<br>write |                         | 1.98  |      | 3.8             | V      |

<sup>1</sup>Measured at 25°C

## **3.8 General Purpose Input Output**

#### Table 3.7. GPIO

| Symbol            | Parameter                                     | Condition                                                                       | Min                 | Тур                 | Max                 | Unit |

|-------------------|-----------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| V <sub>IOIL</sub> | Input low voltage                             |                                                                                 |                     |                     | 0.30V <sub>DD</sub> | V    |

| V <sub>IOIH</sub> | Input high voltage                            |                                                                                 | 0.70V <sub>DD</sub> |                     |                     | V    |

|                   |                                               | Sourcing 0.1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST |                     | 0.80V <sub>DD</sub> |                     | V    |

|                   |                                               | Sourcing 0.1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST  |                     | 0.90V <sub>DD</sub> |                     | V    |

|                   | Output high volt-<br>age (Production test     | Sourcing 1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW      |                     | 0.85V <sub>DD</sub> |                     | V    |

| V <sub>IOOH</sub> | condition = 3.0V,<br>DRIVEMODE =<br>STANDARD) | Sourcing 1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW       |                     | 0.90V <sub>DD</sub> |                     | V    |

|                   |                                               | Sourcing 6 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD | 0.75V <sub>DD</sub> |                     |                     | V    |

|                   |                                               | Sourcing 6 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD  | 0.85V <sub>DD</sub> |                     |                     | V    |

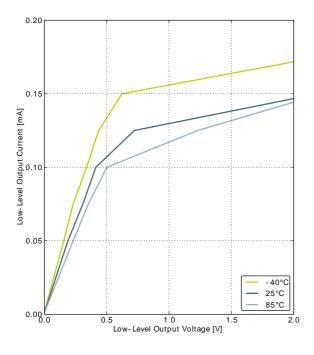

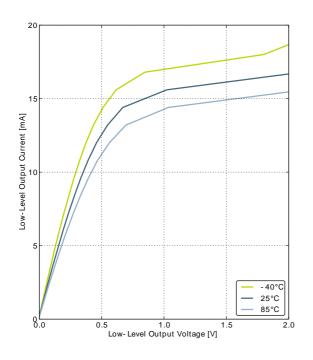

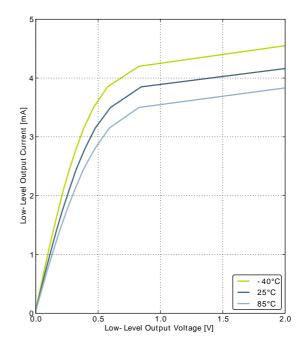

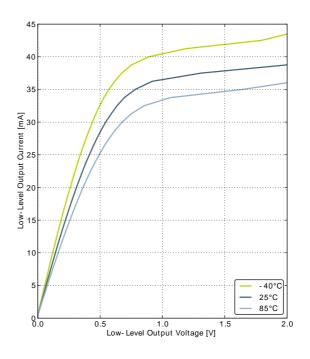

#### Figure 3.4. Typical Low-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = LOW

GPIO\_Px\_CTRL DRIVEMODE = HIGH

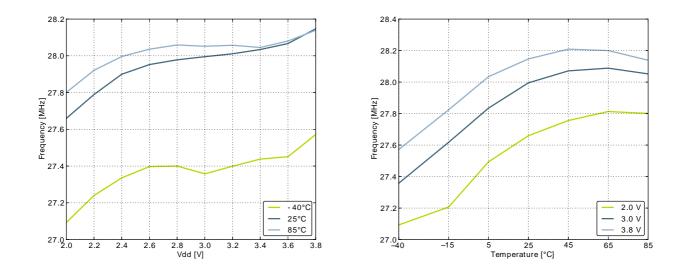

#### Figure 3.16. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

#### 3.9.5 AUXHFRCO

#### Table 3.12. AUXHFRCO

| Symbol                              | Parameter                                              | Condition                      | Min               | Тур               | Max               | Unit   |

|-------------------------------------|--------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|--------|

|                                     |                                                        | 28 MHz frequency band          | 27.5              | 28.0              | 28.5              | MHz    |

|                                     |                                                        | 21 MHz frequency band          | 20.6              | 21.0              | 21.4              | MHz    |

| £                                   | Oscillation frequen-                                   | 14 MHz frequency band          | 13.7              | 14.0              | 14.3              | MHz    |

| <sup>†</sup> AUXHFRCO               | су, V <sub>DD</sub> = 3.0 V,<br>Т <sub>АМВ</sub> =25°С | 11 MHz frequency band          | 10.8              | 11.0              | 11.2              | MHz    |

|                                     |                                                        | 7 MHz frequency band           | 6.48 <sup>1</sup> | 6.60 <sup>1</sup> | 6.72 <sup>1</sup> | MHz    |

|                                     |                                                        | 1 MHz frequency band           | 1.15 <sup>2</sup> | 1.20 <sup>2</sup> | 1.25 <sup>2</sup> | MHz    |

| t <sub>AUXHFRCO_settlir</sub>       | <sub>g</sub> Settling time after<br>start-up           | f <sub>AUXHFRCO</sub> = 14 MHz |                   | 0.6               |                   | Cycles |

| DC <sub>AUXHFRCO</sub>              | Duty cycle                                             | f <sub>AUXHFRCO</sub> = 14 MHz | 48.5              | 50                | 51                | %      |

| TUNESTEP <sub>AU&gt;</sub><br>HFRCO | Frequency step<br>for LSB change in<br>TUNING value    |                                |                   | 0.3 <sup>3</sup>  |                   | %      |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_AUXHFRCOCTRL register may be used to adjust the AUXHFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the AUXHFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

## 3.9.6 ULFRCO

#### Table 3.13. ULFRCO

| Symbol               | Parameter                       | Condition | Min  | Тур   | Мах  | Unit |

|----------------------|---------------------------------|-----------|------|-------|------|------|

| fulfrco              | Oscillation frequen-<br>cy      | 25°C, 3V  | 0.70 |       | 1.75 | kHz  |

| TC <sub>ULFRCO</sub> | Temperature coeffi-<br>cient    |           |      | 0.05  |      | %/°C |

| VC <sub>ULFRCO</sub> | Supply voltage co-<br>efficient |           |      | -18.2 |      | %/V  |

## **3.10 Analog Digital Converter (ADC)**

#### Table 3.14. ADC

| Symbol                    | Parameter                                                                             | Condition                                                                                       | Min                  | Тур  | Max                   | Unit |

|---------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------|------|-----------------------|------|

|                           |                                                                                       | Single ended                                                                                    | 0                    |      | V <sub>REF</sub>      | V    |

| V <sub>ADCIN</sub>        | Input voltage range                                                                   | Differential                                                                                    | -V <sub>REF</sub> /2 |      | V <sub>REF</sub> /2   | V    |

| V <sub>ADCREFIN</sub>     | Input range of exter-<br>nal reference volt-<br>age, single ended<br>and differential |                                                                                                 | 1.25                 |      | V <sub>DD</sub>       | V    |

| V <sub>ADCREFIN_CH7</sub> | Input range of ex-<br>ternal negative ref-<br>erence voltage on<br>channel 7          | See V <sub>ADCREFIN</sub>                                                                       | 0                    |      | V <sub>DD</sub> - 1.1 | V    |

| V <sub>ADCREFIN_CH6</sub> | Input range of ex-<br>ternal positive ref-<br>erence voltage on<br>channel 6          | See V <sub>ADCREFIN</sub>                                                                       | 0.625                |      | V <sub>DD</sub>       | V    |

| V <sub>ADCCMIN</sub>      | Common mode in-<br>put range                                                          |                                                                                                 | 0                    |      | V <sub>DD</sub>       | V    |

|                           | Input current                                                                         | 2pF sampling capacitors                                                                         |                      | <100 |                       | nA   |

| CMRR <sub>ADC</sub>       | Analog input com-<br>mon mode rejection<br>ratio                                      |                                                                                                 |                      | 65   |                       | dB   |

|                           |                                                                                       | 1 MSamples/s, 12 bit, external reference                                                        |                      | 351  |                       | μA   |

|                           |                                                                                       | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b00 |                      | 67   |                       | μA   |

| I <sub>ADC</sub>          | Average active cur-<br>rent                                                           | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b01 |                      | 63   |                       | μA   |

|                           |                                                                                       | 10 kSamples/s 12 bit, internal<br>1.25 V reference, WARMUP-<br>MODE in ADCn_CTRL set to<br>0b10 |                      | 64   |                       | μA   |

| I <sub>ADCREF</sub>       | Current consump-<br>tion of internal volt-<br>age reference                           | Internal voltage reference                                                                      |                      | 65   |                       | μA   |

## 3.10.1 Typical performance

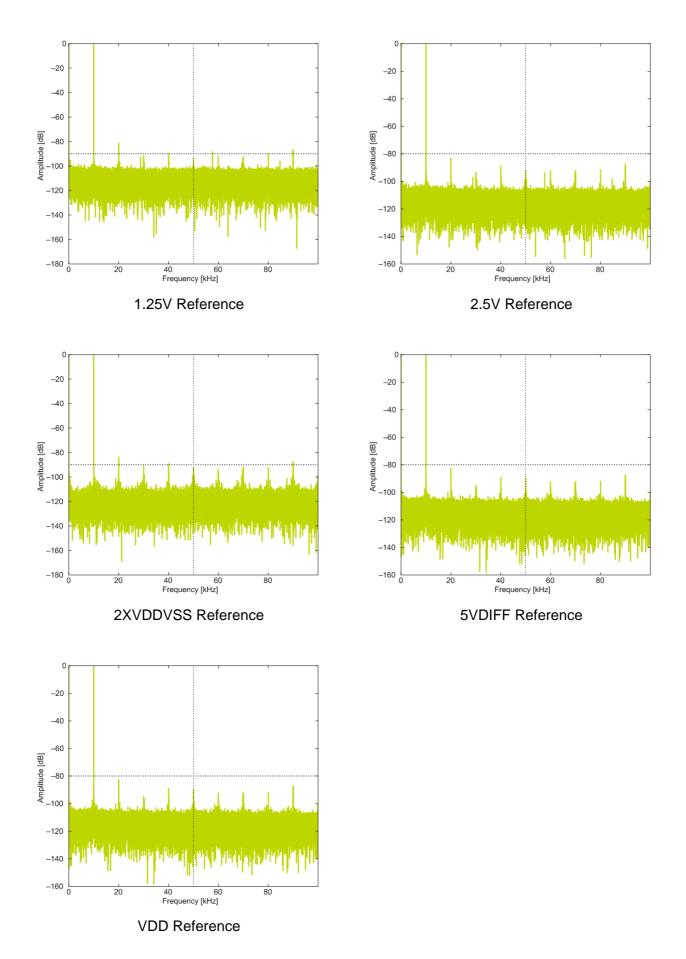

#### Figure 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

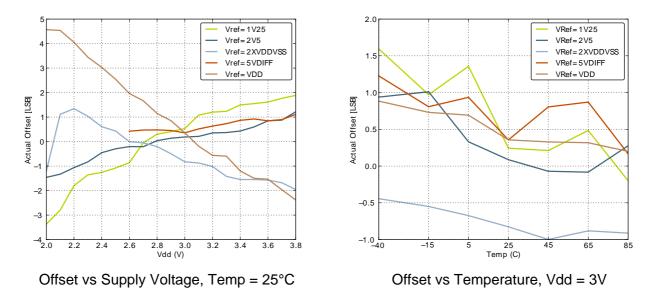

Figure 3.22. ADC Absolute Offset, Common Mode = Vdd /2

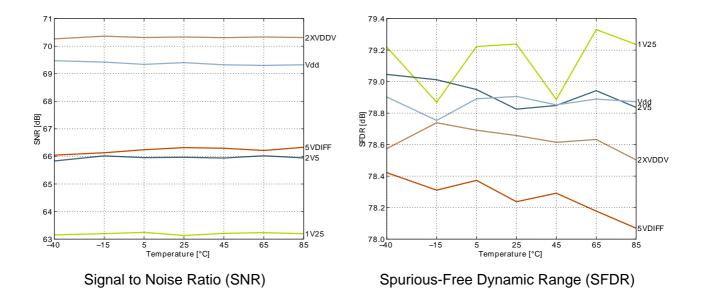

Figure 3.23. ADC Dynamic Performance vs Temperature for all ADC References, Vdd = 3V

| Symbol | Parameter | Condition                                                                                                                                  | Min | Тур  | Max | Unit              |

|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

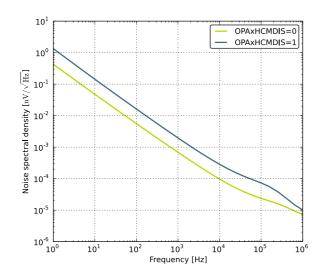

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="0&lt;/td"><td></td><td>196</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 196  |     | μV <sub>RMS</sub> |

|        |           | V <sub>out</sub> =1V, RESSEL=0, 0.1<br>Hz <f<1 mhz,="" opaxhcmdis="1&lt;/td"><td></td><td>229</td><td></td><td>μV<sub>RMS</sub></td></f<1> |     | 229  |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=0</f<10>                                                                                      |     | 1230 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<10 khz,<br="">OPAxHCMDIS=1</f<10>                                                                                      |     | 2130 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=0</f<1>                                                                                        |     | 1630 |     | μV <sub>RMS</sub> |

|        |           | RESSEL=7, 0.1 Hz <f<1 mhz,<br="">OPAxHCMDIS=1</f<1>                                                                                        |     | 2590 |     | μV <sub>RMS</sub> |

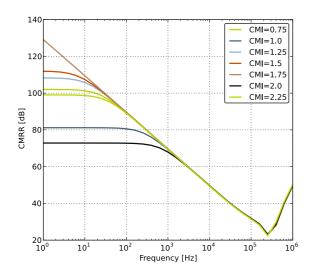

Figure 3.25. OPAMP Common Mode Rejection Ratio

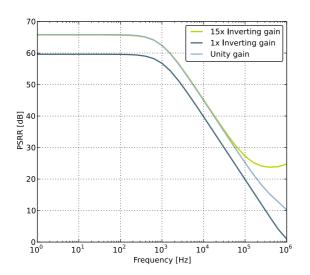

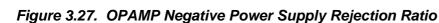

Figure 3.26. OPAMP Positive Power Supply Rejection Ratio

**EFM<sup>®</sup>32**

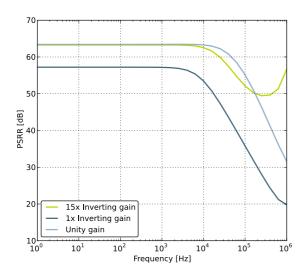

Figure 3.28. OPAMP Voltage Noise Spectral Density (Unity Gain) Vout=1V

Figure 3.29. OPAMP Voltage Noise Spectral Density (Non-Unity Gain)

# **4 Pinout and Package**

#### Note

Please refer to the application note "AN0002 EFM32 Hardware Design Considerations" for guidelines on designing Printed Circuit Boards (PCB's) for the EFM32GG942.

#### 4.1 Pinout

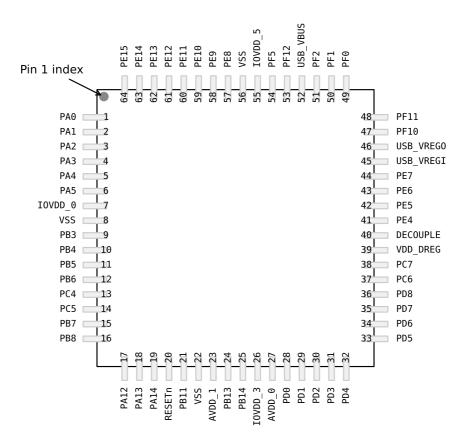

The *EFM32GG942* pinout is shown in Figure 4.1 (p. 51) and Table 4.1 (p. 51). Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

#### Figure 4.1. EFM32GG942 Pinout (top view, not to scale)

Table 4.1. Device Pinout

|       | QFP64 Pin#<br>and Name |           | Pin Alternate Functio | Inctionality / Description |                           |  |

|-------|------------------------|-----------|-----------------------|----------------------------|---------------------------|--|

| Pin # | Pin Name               | Analog    | Timers                | Communication              | Other                     |  |

| 1     | PA0                    | LCD_SEG13 | TIM0_CC0 #0/1/4       | I2C0_SDA #0<br>LEU0_RX #4  | PRS_CH0 #0<br>GPIO_EM4WU0 |  |

| 2     | PA1                    | LCD_SEG14 | TIM0_CC1 #0/1         | 12C0_SCL #0                | CMU_CLK1 #0<br>PRS_CH1 #0 |  |

| 3     | PA2                    | LCD_SEG15 | TIM0_CC2 #0/1         |                            | CMU_CLK0 #0               |  |

|       | QFP64 Pin#<br>and Name |                                  | Pin Alternate Functi                           | onality / Description                         |                                                           |

|-------|------------------------|----------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|

| Pin # | Pin Name               | Analog                           | Timers                                         | Communication                                 | Other                                                     |

| 31    | PD3                    | ADC0_CH3<br>OPAMP_N2             | TIM0_CC2 #3                                    | US1_CS #1                                     | ETM_TD1 #0/2                                              |

| 32    | PD4                    | ADC0_CH4<br>OPAMP_P2             |                                                | LEU0_TX #0                                    | ETM_TD2 #0/2                                              |

| 33    | PD5                    | ADC0_CH5<br>OPAMP_OUT2 #0        |                                                | LEU0_RX #0                                    | ETM_TD3 #0/2                                              |

| 34    | PD6                    | ADC0_CH6<br>OPAMP_P1             | LETIM0_OUT0 #0<br>TIM1_CC0 #4<br>PCNT0_S0IN #3 | US1_RX #2<br>I2C0_SDA #1                      | LES_ALTEX0 #0<br>ACMP0_O #2<br>ETM_TD0 #0                 |

| 35    | PD7                    | ADC0_CH7<br>OPAMP_N1             | LETIM0_OUT1 #0<br>TIM1_CC1 #4<br>PCNT0_S1IN #3 | US1_TX #2<br>I2C0_SCL #1                      | CMU_CLK0 #2<br>LES_ALTEX1 #0<br>ACMP1_O #2<br>ETM_TCLK #0 |

| 36    | PD8                    | BU_VIN                           |                                                |                                               | CMU_CLK1 #1                                               |

| 37    | PC6                    | ACMP0_CH6                        |                                                | I2C0_SDA #2<br>LEU1_TX #0                     | LES_CH6 #0<br>ETM_TCLK #2                                 |

| 38    | PC7                    | ACMP0_CH7                        |                                                | I2C0_SCL #2<br>LEU1_RX #0                     | LES_CH7 #0<br>ETM_TD0 #2                                  |

| 39    | VDD_DREG               | Power supply for on-chip voltage | ge regulator.                                  | 1                                             | I                                                         |

| 40    | DECOUPLE               | Decouple output for on-chip vo   | Itage regulator. An external cap               | acitance of size C <sub>DECOUPLE</sub> is rec | quired at this pin.                                       |

| 41    | PE4                    | LCD_COM0                         |                                                | US0_CS #1                                     |                                                           |

| 42    | PE5                    | LCD_COM1                         |                                                | US0_CLK #1                                    |                                                           |

| 43    | PE6                    | LCD_COM2                         |                                                | US0_RX #1                                     |                                                           |

| 44    | PE7                    | LCD_COM3                         |                                                | US0_TX #1                                     |                                                           |

| 45    | USB_VREGI              |                                  |                                                |                                               |                                                           |

| 46    | USB_VREGO              |                                  |                                                |                                               |                                                           |

| 47    | PF10                   |                                  |                                                | USB_DM                                        |                                                           |

| 48    | PF11                   |                                  |                                                | USB_DP                                        |                                                           |

| 49    | PF0                    |                                  | TIM0_CC0 #5<br>LETIM0_OUT0 #2                  | US1_CLK #2<br>I2C0_SDA #5<br>LEU0_TX #3       | DBG_SWCLK #0/1/2/3                                        |

| 50    | PF1                    |                                  | TIM0_CC1 #5<br>LETIM0_OUT1 #2                  | US1_CS #2<br>I2C0_SCL #5<br>LEU0_RX #3        | DBG_SWDIO #0/1/2/3<br>GPIO_EM4WU3                         |

| 51    | PF2                    | LCD_SEG0                         | TIM0_CC2 #5                                    | LEU0_TX #4                                    | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4                   |

| 52    | USB_VBUS               | USB 5.0 V VBUS input.            | l                                              | 1                                             | 1                                                         |

| 53    | PF12                   |                                  |                                                | USB_ID                                        |                                                           |

| 54    | PF5                    | LCD_SEG3                         | TIM0_CDTI2 #2/5                                | USB_VBUSEN #0                                 | PRS_CH2 #1                                                |

| 55    | IOVDD_5                | Digital IO power supply 5.       |                                                | 1                                             | 1                                                         |

| 56    | VSS                    | Ground.                          |                                                |                                               |                                                           |

| 57    | PE8                    | LCD_SEG4                         | PCNT2_S0IN #1                                  |                                               | PRS_CH3 #1                                                |

| 58    | PE9                    | LCD_SEG5                         | PCNT2_S1IN #1                                  |                                               |                                                           |

| 59    | PE10                   | LCD_SEG6                         | TIM1_CC0 #1                                    | US0_TX #0                                     | BOOT_TX                                                   |

| 60    | PE11                   | LCD_SEG7                         | TIM1_CC1 #1                                    | US0_RX #0                                     | LES_ALTEX5 #0<br>BOOT_RX                                  |

| 61    | PE12                   | LCD_SEG8                         | TIM1_CC2 #1                                    | US0_RX #3                                     | CMU_CLK1 #2                                               |

|       | QFP64 Pin#<br>and Name |           |             |                                       |                                            |  |  |

|-------|------------------------|-----------|-------------|---------------------------------------|--------------------------------------------|--|--|

| Pin # | Pin Name               | Analog    | Timers      | Communication                         | Other                                      |  |  |

|       |                        |           |             | US0_CLK #0<br>I2C0_SDA #6             | LES_ALTEX6 #0                              |  |  |

| 62    | PE13                   | LCD_SEG9  |             | US0_TX #3<br>US0_CS #0<br>I2C0_SCL #6 | LES_ALTEX7 #0<br>ACMP0_O #0<br>GPIO_EM4WU5 |  |  |

| 63    | PE14                   | LCD_SEG10 | TIM3_CC0 #0 | LEU0_TX #2                            |                                            |  |  |

| 64    | PE15                   | LCD_SEG11 | TIM3_CC1 #0 | LEU0_RX #2                            |                                            |  |  |

## **4.2 Alternate Functionality Pinout**

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in Table 4.2 (p. 54). The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

#### Note

Some functionality, such as analog interfaces, do not have alternate settings or a LOCA-TION bitfield. In these cases, the pinout is shown in the column corresponding to LOCA-TION 0.

#### Table 4.2. Alternate functionality overview

| Alternate     |      |     | LOC  | ATION |   |   |   |                                                           |

|---------------|------|-----|------|-------|---|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1   | 2    | 3     | 4 | 5 | 6 | Description                                               |

| ACMP0_CH4     | PC4  |     |      |       |   |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |     |      |       |   |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |     |      |       |   |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |     |      |       |   |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 |     | PD6  |       |   |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_O       | PF2  |     | PD7  |       |   |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |     |      |       |   |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |     |      |       |   |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |     |      |       |   |   |   | Bootloader TX.                                            |

| BU_VIN        | PD8  |     |      |       |   |   |   | Battery input for Backup Power Domain                     |

| CMU_CLK0      | PA2  |     | PD7  |       |   |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8 | PE12 |       |   |   |   | Clock Management Unit, clock output number 1.             |

| OPAMP_N0      | PC5  |     |      |       |   |   |   | Operational Amplifier 0 external negative input.          |

| OPAMP_N1      | PD7  |     |      |       |   |   |   | Operational Amplifier 1 external negative input.          |

## **EFM<sup>®</sup>32**

#### ...the world's most energy friendly microcontrollers

| Alternate              |      |   | LOC | ATION |   |   |   |                                                                                                                             |

|------------------------|------|---|-----|-------|---|---|---|-----------------------------------------------------------------------------------------------------------------------------|

| Functionality          | 0    | 1 | 2   | 3     | 4 | 5 | 6 | Description                                                                                                                 |

| LCD_COM0               | PE4  |   |     |       |   |   |   | LCD driver common line number 0.                                                                                            |

| LCD_COM1               | PE5  |   |     |       |   |   |   | LCD driver common line number 1.                                                                                            |

| LCD_COM2               | PE6  |   |     |       |   |   |   | LCD driver common line number 2.                                                                                            |

| LCD_COM3               | PE7  |   |     |       |   |   |   | LCD driver common line number 3.                                                                                            |

| LCD_SEG0               | PF2  |   |     |       |   |   |   | LCD segment line 0. Segments 0, 1, 2 and 3 are con-<br>trolled by SEGEN0.                                                   |

| LCD_SEG3               | PF5  |   |     |       |   |   |   | LCD segment line 3. Segments 0, 1, 2 and 3 are con-<br>trolled by SEGEN0.                                                   |

| LCD_SEG4               | PE8  |   |     |       |   |   |   | LCD segment line 4. Segments 4, 5, 6 and 7 are con-<br>trolled by SEGEN1.                                                   |

| LCD_SEG5               | PE9  |   |     |       |   |   |   | LCD segment line 5. Segments 4, 5, 6 and 7 are con-<br>trolled by SEGEN1.                                                   |

| LCD_SEG6               | PE10 |   |     |       |   |   |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                        |

| LCD_SEG7               | PE11 |   |     |       |   |   |   | LCD segment line 7. Segments 4, 5, 6 and 7 are con-<br>trolled by SEGEN1.                                                   |

| LCD_SEG8               | PE12 |   |     |       |   |   |   | LCD segment line 8. Segments 8, 9, 10 and 11 are con-<br>trolled by SEGEN2.                                                 |

| LCD_SEG9               | PE13 |   |     |       |   |   |   | LCD segment line 9. Segments 8, 9, 10 and 11 are con-<br>trolled by SEGEN2.                                                 |

| LCD_SEG10              | PE14 |   |     |       |   |   |   | LCD segment line 10. Segments 8, 9, 10 and 11 are con-<br>trolled by SEGEN2.                                                |

| LCD_SEG11              | PE15 |   |     |       |   |   |   | LCD segment line 11. Segments 8, 9, 10 and 11 are con-<br>trolled by SEGEN2.                                                |

| LCD_SEG13              | PA0  |   |     |       |   |   |   | LCD segment line 13. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                                   |

| LCD_SEG14              | PA1  |   |     |       |   |   |   | LCD segment line 14. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                                   |

| LCD_SEG15              | PA2  |   |     |       |   |   |   | LCD segment line 15. Segments 12, 13, 14 and 15 are controlled by SEGEN3.                                                   |

| LCD_SEG16              | PA3  |   |     |       |   |   |   | LCD segment line 16. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                                   |

| LCD_SEG17              | PA4  |   |     |       |   |   |   | LCD segment line 17. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                                   |

| LCD_SEG18              | PA5  |   |     |       |   |   |   | LCD segment line 18. Segments 16, 17, 18 and 19 are controlled by SEGEN4.                                                   |

| LCD_SEG20/<br>LCD_COM4 | PB3  |   |     |       |   |   |   | LCD segment line 20. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 4       |

| LCD_SEG21/<br>LCD_COM5 | PB4  |   |     |       |   |   |   | LCD segment line 21. Segments 20, 21, 22 and 23 are controlled by SEGEN5. This pin may also be used as LCD COM line 5       |

| LCD_SEG22/<br>LCD_COM6 | PB5  |   |     |       |   |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are<br>controlled by SEGEN5. This pin may also be used as LCD<br>COM line 6 |

| LCD_SEG23/<br>LCD_COM7 | PB6  |   |     |       |   |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are<br>controlled by SEGEN5. This pin may also be used as LCD<br>COM line 7 |

| LES_ALTEX0             | PD6  |   |     |       |   |   |   | LESENSE alternate exite output 0.                                                                                           |

| LES_ALTEX1             | PD7  |   |     |       |   |   |   | LESENSE alternate exite output 1.                                                                                           |

| LES_ALTEX2             | PA3  |   |     |       |   |   |   | LESENSE alternate exite output 2.                                                                                           |

| LES_ALTEX3             | PA4  |   |     |       |   |   |   | LESENSE alternate exite output 3.                                                                                           |

| LES_ALTEX4             | PA5  |   |     |       |   |   |   | LESENSE alternate exite output 4.                                                                                           |

#### Table 4.3. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin<br>9 | Pin<br>8 | Pin<br>7 | Pin<br>6 | Pin<br>5 | Pin<br>4 | Pin<br>3 | Pin<br>2 | Pin<br>1 | Pin<br>0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Port A | -         | PA14      | PA13      | PA12      | -         | -         | -        | -        | -        | -        | PA5      | PA4      | PA3      | PA2      | PA1      | PA0      |

| Port B | -         | PB14      | PB13      | -         | PB11      | -         | -        | PB8      | PB7      | PB6      | PB5      | PB4      | PB3      | -        | -        | -        |

| Port C | -         | -         | -         | -         | -         | -         | -        | -        | PC7      | PC6      | PC5      | PC4      | -        | -        | -        | -        |

| Port D | -         | -         | -         | -         | -         | -         | -        | PD8      | PD7      | PD6      | PD5      | PD4      | PD3      | PD2      | PD1      | PD0      |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9      | PE8      | PE7      | PE6      | PE5      | PE4      | -        | -        | -        | -        |

| Port F | -         | -         | -         | PF12      | PF11      | PF10      | -        | -        | -        | -        | PF5      | -        | -        | PF2      | PF1      | PF0      |

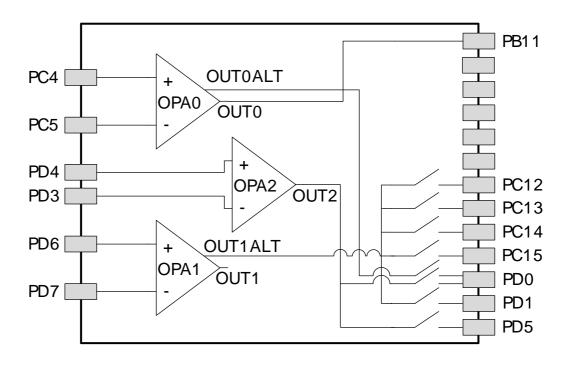

## 4.4 Opamp Pinout Overview

The specific opamp terminals available in EFM32GG942 is shown in Figure 4.2 (p. 59).

#### Figure 4.2. Opamp Pinout

# **7 Revision History**

## 7.1 Revision 1.40

March 21st, 2016

Added clarification on conditions for INL<sub>ADC</sub> and DNL<sub>ADC</sub> parameters.

Reduced maximum and typical current consumption for all EM0 entries except 48 MHz in the Current Consumption table in the Electrical Characteristics section.

Increased maximum specifications for EM2 current, EM3 current, and EM4 current in the Current Consumption table in the Electrical Characteristics section.

Increased typical specification for EM2 and EM3 current at 85 C in the Current Consumption table in the Electrical Characteristics section.

Added EM2, EM3, and EM4 current consumption vs. temperature graphs.

Added a new EM2 entry and specified the existing specification is for EM0 for the BOD threshold on falling external supply voltage in the Power Management table in the Electrical Characteristics section.

Reduced maximum input leakage current in the GPIO table in the Electrical Characteristics section.

Added a maximum current consumption specification to the LFRCO table in the Electrical Characteristics section.

Added maximum specifications for the active current including references for two channels to the DAC table in the Electrical Characteristics section.

Increased the maximum specification for DAC offset voltage in the DAC table in the Electrical Characteristics section.

Increased the typical specifications for active current with FULLBIAS=1 and capacitive sense internal resistance in the ACMP table in the Electrical Characteristics section.

Added minimum and maximum specifications and updated the typical value for the VCMP offset voltage in the VCMP table in the Electrical Characteristics section.

Removed the maximum specification and reduced the typical value for hysteresis in the VCMP table in the Electrical Characteristics section.

Updated all graphs in the Electrical Characteristics section to display data for 2.0 V as the minimum voltage.

## 7.2 Revision 1.30

May 23rd, 2014

Removed "preliminary" markings

Updated HFRCO figures.

Corrected single power supply voltage minimum value from 1.85V to 1.98V.

Updated Current Consumption information.

Updated Power Management information.

#### **EFM<sup>®</sup>32**

Updated GPIO information.

Updated LFRCO information.

Updated HFRCO information.

Updated ULFRCO information.

Updated ADC information.

Updated DAC information.

Updated OPAMP information.

Updated ACMP information.

Updated VCMP information.

Added AUXHFRCO information.

## 7.3 Revision 1.21

November 21st, 2013 Updated figures. Updated errata-link. Updated chip marking.

Added link to Environmental and Quality information.

Re-added missing DAC-data.

## 7.4 Revision 1.20

September 30th, 2013

Added I2C characterization data.

Added SPI characterization data.

Corrected the DAC and OPAMP2 pin sharing information in the Alternate Functionality Pinout section.

Corrected GPIO operating voltage from 1.8 V to 1.85 V.

Added the USB bootloader information.

Updated that the EM2 current consumption test was carried out with only one RAM block enabled.

Corrected the ADC resolution from 12, 10 and 6 bit to 12, 8 and 6 bit.

Updated Environmental information.

Updated trademark, disclaimer and contact information.

Other minor corrections.

## 7.5 Revision 1.10

June 28th, 2013

# **B** Contact Information

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

Please visit the Silicon Labs Technical Support web page: http://www.silabs.com/support/pages/contacttechnicalsupport.aspx and register to submit a technical support request.