Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                              |

| Core Processor             | 80515                                                                 |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SmartCard, UART/USART, USB                          |

| Peripherals                | LED, POR, WDT                                                         |

| Number of I/O              | 9                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | -                                                                     |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 44-QFN (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/73s1215f-44im-f-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| <ul> <li>1.1 Pin Description</li> <li>1.2 Hardware Overview</li> <li>1.3 80515 MPU Core</li> </ul>                                                                                                                                                           | Hardware Description8    |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                              | 8                        |  |  |  |  |  |  |  |

| 1.3 80515 MPU Core                                                                                                                                                                                                                                           | 11                       |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                              | 11                       |  |  |  |  |  |  |  |

| 1.3.1 80515 Overview                                                                                                                                                                                                                                         | 11                       |  |  |  |  |  |  |  |

| 1.3.2 Memory Organization                                                                                                                                                                                                                                    |                          |  |  |  |  |  |  |  |

| 1.4 Program Security                                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |

| 1.5 Special Function Registers (SFRs)                                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |

| 1.5.1 Internal Data Special Function Registers (SFRs)                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |

| 1.5.2 IRAM Special Function Registers (Generic 80515 SFRs)                                                                                                                                                                                                   |                          |  |  |  |  |  |  |  |

| 1.5.3 External Data Special Function Registers (SFRs)                                                                                                                                                                                                        | 20                       |  |  |  |  |  |  |  |

| 1.6 Instruction Set                                                                                                                                                                                                                                          | 23                       |  |  |  |  |  |  |  |

| 1.7 Peripheral Descriptions                                                                                                                                                                                                                                  | 23                       |  |  |  |  |  |  |  |

| 1.7.1 Oscillator and Clock Generation                                                                                                                                                                                                                        | 23                       |  |  |  |  |  |  |  |

| 1.7.2 Power Control Modes                                                                                                                                                                                                                                    |                          |  |  |  |  |  |  |  |

| 1.7.3 Interrupts                                                                                                                                                                                                                                             |                          |  |  |  |  |  |  |  |

| 1.7.4 UART                                                                                                                                                                                                                                                   |                          |  |  |  |  |  |  |  |

| 1.7.5 Timers and Counters                                                                                                                                                                                                                                    |                          |  |  |  |  |  |  |  |

| 1.7.6 WD Timer (Software Watchdog Timer)                                                                                                                                                                                                                     | 47                       |  |  |  |  |  |  |  |

| 1.7.7 User (USR) Ports                                                                                                                                                                                                                                       | 50                       |  |  |  |  |  |  |  |

| 1.7.8 Real-Time Clock with Hardware Watchdog (RTC)                                                                                                                                                                                                           | 52                       |  |  |  |  |  |  |  |

| 1.7.9 Analog Voltage Comparator                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |

| 1.7.10 LED Drivers                                                                                                                                                                                                                                           |                          |  |  |  |  |  |  |  |

| 1.7.11 I <sup>2</sup> C Master Interface                                                                                                                                                                                                                     | 58                       |  |  |  |  |  |  |  |

| 1.7.12 Keypad Interface                                                                                                                                                                                                                                      | 65                       |  |  |  |  |  |  |  |

| 1.7.13 Emulator Port                                                                                                                                                                                                                                         | 72                       |  |  |  |  |  |  |  |

| 1.7.14 USB Interface                                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |

| 1.7.15 Smart Card Interface Function                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |

| 1.7.16 VDD Fault Detect Function                                                                                                                                                                                                                             | 110                      |  |  |  |  |  |  |  |

| 2 Typical Application Schematic                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |

| 3.1 Absolute Maximum Ratings                                                                                                                                                                                                                                 |                          |  |  |  |  |  |  |  |

| 3.2 Recommended Operating Conditions                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |

| 3.3 Digital IO Characteristics                                                                                                                                                                                                                               |                          |  |  |  |  |  |  |  |

| 3.4 Oscillator Interface Requirements                                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |

| 3.5 DC Characteristics: Analog Input                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |

| 3.6 USB Interface Requirements                                                                                                                                                                                                                               |                          |  |  |  |  |  |  |  |

| 3.7 Smart Card Interface Requirements                                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |

| 3.7.1 DC Characteristics                                                                                                                                                                                                                                     |                          |  |  |  |  |  |  |  |

| 3.8 Voltage / Temperature Fault Detection Circuits                                                                                                                                                                                                           | 119                      |  |  |  |  |  |  |  |

| 4 Equivalent Circuits                                                                                                                                                                                                                                        | 120                      |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                            |                          |  |  |  |  |  |  |  |

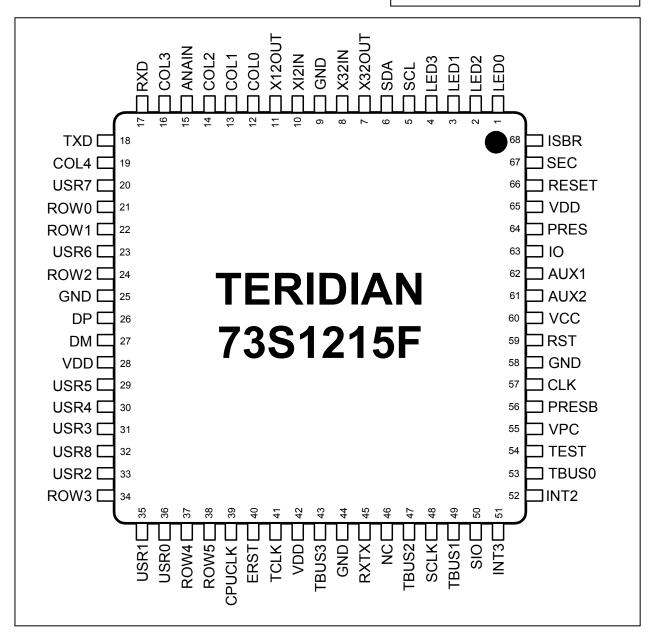

| 5 Package Pin Designation                                                                                                                                                                                                                                    |                          |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li></ul>                                                                                                                                                                                                                 |                          |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> </ul>                                                                                                                                                  |                          |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> </ul>                                                                                                                 |                          |  |  |  |  |  |  |  |

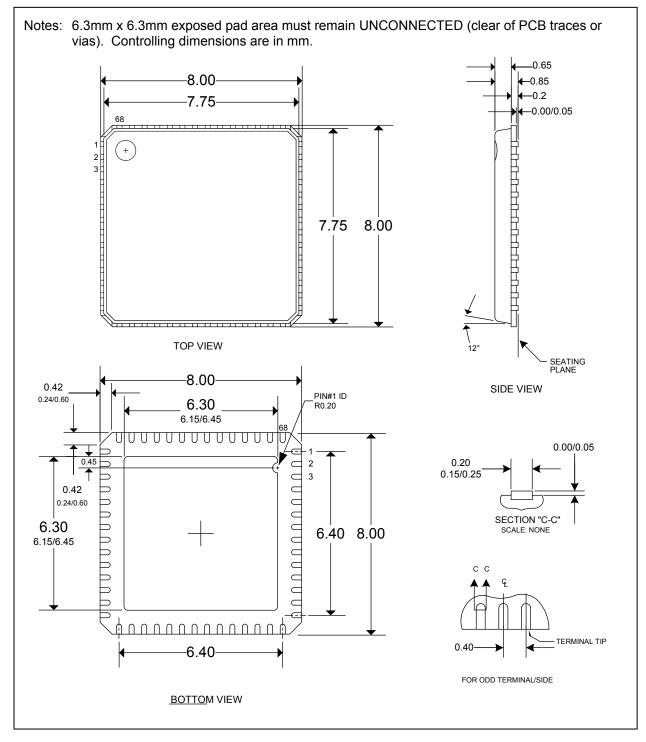

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> <li>6.1 68-Pin QFN Package Outline</li> </ul>                                                                         |                          |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> </ul>                                                                                                                 |                          |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> <li>6.1 68-Pin QFN Package Outline</li> </ul>                                                                         | 131<br>132               |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> <li>6.1 68-Pin QFN Package Outline</li> <li>6.2 44-Pin QFN Package Outline</li> </ul>                                 | 131<br>132<br><b>133</b> |  |  |  |  |  |  |  |

| <ul> <li>5 Package Pin Designation</li> <li>5.1 68-pin QFN Pinout</li> <li>5.2 44-pin QFN Pinout</li> <li>6 Packaging Information</li> <li>6.1 68-Pin QFN Package Outline</li> <li>6.2 44-Pin QFN Package Outline</li> <li>7 Ordering Information</li> </ul> |                          |  |  |  |  |  |  |  |

**Internal Data Memory:** The Internal data memory provides 256 bytes (0x00 to 0xFF) of data memory. The internal data memory address is always one byte wide and can be accessed by either direct or indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is available only by direct addressing. Indirect addressing accesses the upper 128 bytes of Internal RAM.

The lower 128 bytes contain working registers and bit-addressable memory. The lower 32 bytes form four banks of eight registers (R0-R7). Two bits on the program memory status word (PSW) select which bank is in use. The next 16 bytes form a block of bit-addressable memory space at bit addresses 0x00-0x7F. All of the bytes in the lower 128 bytes are accessible through direct or indirect addressing. Table 4 shows the internal data memory map.

| Address | Direct Addressing            | Indirect Addressing |  |  |  |

|---------|------------------------------|---------------------|--|--|--|

| 0xFF    | Special Function             | DAM                 |  |  |  |

| 0x80    | Registers (SFRs)             | RAM                 |  |  |  |

| 0x7F    | Dute ed                      |                     |  |  |  |

| 0x30    | Byle-au                      | dressable area      |  |  |  |

| 0x2F    | Dute er hit addresseble eres |                     |  |  |  |

| 0x20    | Byte or bit-addressable area |                     |  |  |  |

| 0x1F    | Register banks R0…R7 (x4)    |                     |  |  |  |

| 0x00    | Register ba                  | 11K5 KUKI (X4)      |  |  |  |

**External Data Memory:** While the 80515 can address up to 64KB of external data memory in the space from 0x0000 to 0xFFFF, only the memory ranges shown in Figure 2 contain physical memory. The 80515 writes into external data memory when the MPU executes a MOVX @Ri,A or MOVX @DPTR,A instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX A,@DPTR instruction.

There are two types of instructions, differing in whether they provide an eight-bit or sixteen-bit indirect address to the external data RAM.

In the first type (MOVX A,@Ri), the contents of R0 or R1, in the current register bank, provide the eight lower-ordered bits of address. This method allows the user access to the first 256 bytes of the 2KB of external data RAM. In the second type of MOVX instruction (MOVX A,@DPTR), the data pointer generates a sixteen-bit address.

| Address                             | Use                               | Address | Use                                                          |                    |                  |                                    |                   |              |  |

|-------------------------------------|-----------------------------------|---------|--------------------------------------------------------------|--------------------|------------------|------------------------------------|-------------------|--------------|--|

| 0xFFFF                              |                                   | 0xFFFF  | Peripheral Control<br>Registers (128b)<br>Smart Card Control |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0XFF80  |                                                              |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0xFF7F  |                                                              |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0XFE00  | (384b)                                                       |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0xFDFF  | LISP Degisters (512b)                                        |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0XFC00  | USB Registers (512b)                                         |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0xFBFF  |                                                              |                    |                  |                                    |                   |              |  |

|                                     |                                   | 0x0800  | -                                                            |                    |                  | U                                  | se                |              |  |

|                                     | Flash<br>Program<br>Memory<br>64K |         | Address                                                      | Indirect<br>Access | Direct<br>Access |                                    |                   |              |  |

|                                     |                                   |         | 0xFF                                                         |                    | SFRs             |                                    |                   |              |  |

|                                     |                                   |         |                                                              |                    | 0x80             | Byte RAM                           | SERS              |              |  |

|                                     |                                   |         |                                                              |                    | 0x7F             | - Byte RAM                         |                   |              |  |

|                                     | Bytes                             |         |                                                              |                    | 0x48             |                                    |                   |              |  |

|                                     |                                   |         |                                                              |                    |                  |                                    | 0x47              | Dit/Duto DAM |  |

|                                     |                                   |         |                                                              |                    | 0x20             | Bit/Byte RAM                       |                   |              |  |

|                                     |                                   | XRAM    |                                                              | 0x1F               | Desister bank 2  |                                    |                   |              |  |

|                                     |                                   |         |                                                              |                    | 0x18             | Register bank 3<br>Register bank 2 |                   |              |  |

|                                     |                                   |         |                                                              |                    | 0x17             |                                    |                   |              |  |

|                                     |                                   |         |                                                              |                    | 0x10             |                                    |                   |              |  |

|                                     |                                   |         |                                                              |                    |                  | 0x0F                               | - Register bank 1 |              |  |

|                                     |                                   | 0       |                                                              |                    | 0x08             |                                    |                   |              |  |

|                                     |                                   |         |                                                              | 0x07               | Denista          | r book 0                           |                   |              |  |

| 0x0000                              |                                   |         | 0x0000                                                       |                    | 0x00             | Registe                            | r bank 0          |              |  |

| Program Memory External Data Memory |                                   |         |                                                              |                    | Int              | ternal Data M                      | emory             |              |  |

### Figure 2: Memory Map

**Dual Data Pointer:** The Dual Data Pointer accelerates the block moves of data. The standard DPTR is a 16-bit register that is used to address external memory. In the 80515 core, the standard data pointer is called DPTR, the second data pointer is called DPTR1. The data pointer select bit chooses the active pointer. The data pointer select bit is located at the LSB of the DPS IRAM special function register (DPS.0). DPTR is selected when DPS.0 = 0 and DPTR1 is selected when DPS.0 = 1.

The user switches between pointers by toggling the LSB of the DPS register. All DPTR-related instructions use the currently selected DPTR for any activity.

### Note: The second data pointer may not be supported by certain compilers.

The master clock control register enables different sections of the clock circuitry and specifies the value of the VCO Mcount divider. The MCLK must be configured to operate at 96MHz to ensure proper operation of some of the peripheral blocks according to the following formula:

MCLK = (Mcount \* 2 + 4) \*  $F_{XTAL}$  = 96MHz

Mcount is configured in the MCLKCtl register must be bound between a value of 1 to 7. The possible crystal or external clock frequencies for getting MCLK = 96MHz are shown in Table 12.

| F <sub>XTAL</sub> (MHz) | Mcount (N) |

|-------------------------|------------|

| 12.00                   | 2          |

| 9.60                    | 3          |

| 8.00                    | 4          |

| 6.86                    | 5          |

| 6.00                    | 6          |

Table 12: Frequencies and Mcount Values for MCLK = 96MHz

### Master Clock Control Register (MCLKCtl): 0x8F ← 0x0A

#### Table 13: The MCLKCtl Register

| MSB   |      |      |       |       |       |       | LSB   |  |

|-------|------|------|-------|-------|-------|-------|-------|--|

| HSOEN | KBEN | SCEN | USBEN | 32KEN | MCT.2 | MCT.1 | MCT.0 |  |

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKCtl.7 | HSOEN  | High-speed oscillator disable. When set = 1, disables the high-speed crystal oscillator and VCO/PLL system. Do not set this bit = 1.                                                                                                                                                                                                                                                                                                                                         |

| MCLKCtl.6 | KBEN   | 1 = Disable the keypad logic clock.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MCLKCtl.5 | SCEN   | 1 = Disable the smart card logic clock.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MCLKCtl.4 | USBEN  | 1 = Disable the USB logic clock.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MCLKCtl.3 | 32KEN  | 1 = Disable the 32Khz oscillator. When the 32kHz oscillator is enabled, the RTC and other circuits such as debounce clocks are clocked using the 32kHz oscillator output. When disabled, the main oscillator provides the 32kHz clock for the RTC and other circuits. <b>Note: This bit must be set if there is no 32KHz crystal or the 44 pin package is used. Some internal clocks and circuits will not run if the oscillator is enabled and no crystal is connected.</b> |

| MCLKCtl.2 | MCT.2  | This value determines the ratio of the VCO frequency (MCLK) to the high-                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCLKCtl.1 | MCT.1  | speed crystal oscillator frequency such that:                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MCLKCtl.0 | MCT.0  | MCLK = (MCount*2 + 4)* $F_{XTAL}$ . The default value is MCount = 2h such that MCLK = (2*2 + 4)*12.00MHz = 96MHz.                                                                                                                                                                                                                                                                                                                                                            |

The MPU clock that drives the CPU core defaults to 3.6923MHz after reset. The MPU clock is scalable by configuring the MPU Clock Control register (MPUCKCtl).

### Master Clock Control Register (MCLKCtl): 0x8F ← 0x0A

### Table 18: The MCLKCtl Register

| MSB   |      |      |       |       |       |       | LSB   |  |

|-------|------|------|-------|-------|-------|-------|-------|--|

| HSOEN | KBEN | SCEN | USBEN | 32KEN | MCT.2 | MCT.1 | MCT.0 |  |

| Bit       | Symbol | Function                                                                                                                                                                                                                                                                       |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKCtl.7 | HSOEN* | High-speed oscillator enable. When set = 1, disables the high-speed crystal oscillator and VCO/PLL system. This bit is not changed when the PWRDN bit is set but the oscillator/VCO/PLL is disabled.                                                                           |

| MCLKCtl.6 | KBEN   | 1 = Disable the keypad logic clock. This bit is not changed in PWRDN mode but the function is disabled.                                                                                                                                                                        |

| MCLKCtl.5 | SCEN   | 1 = Disable the smart card logic clock. This bit is not changed in PWRDN mode but the function is disabled. Interrupt logic for card insertion/removal remains operable even with smart card clock disabled.                                                                   |

| MCLKCtl.4 | USBEN  | 1 = Disable the USB logic clock. This bit is not changed in PWRDN mode but the function is disabled.                                                                                                                                                                           |

| MCLKCtl.3 | 32KEN  | 1 = Disable the 32Khz oscillator. This function is not affected by PWRDN mode. Note: This bit must be set if there is no 32KHz crystal or the 44 pin package is used. Some internal clocks and circuits will not run if the oscillator is enabled and no crystal is connected. |

| MCLKCtl.2 | MCT.2  | This value determines the ratio of the VCO frequency (MCLK) to the high-                                                                                                                                                                                                       |

| MCLKCtl.1 | MCT.1  | speed crystal oscillator frequency such that:                                                                                                                                                                                                                                  |

| MCLKCtl.0 | MCT.0  | MCLK = (MCount*2 + 4)*Fxtal. The default value is MCount = 2h such that<br>MCLK = (2*2 + 4)*12.00MHz = 96MHz.                                                                                                                                                                  |

\*Note: The HSOEN bit should never be set under normal circumstances. Power down control should only be initiated via use of the PWRDN bit in MISCtIO.

### Miscellaneous Control Register 0 (MISCtI0): 0xFFF1 ← 0x00

Transmit and receive (TX and RX) pin selection and loop back test configuration are set up via this register.

|           | Table 38: The MISCIU Register |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

|-----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------------|----------|----------|--|

| MSB       |                               |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          | LSB      |  |

| PWF       | PWRDN – – – – – SLPBK SSEL    |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          | SSEL     |  |

| Bit       | Symbol                        |                                                                                                                                                                                                                                                                                                                                                                          |        |         | Functio    | on       |          |  |

| MISCtI0.7 | PWRDN                         | This bit plac                                                                                                                                                                                                                                                                                                                                                            | es the | 73S1215 | F into a p | ower dow | n state. |  |

| MISCtI0.6 | _                             |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

| MISCtI0.5 | _                             |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

| MISCtI0.4 | -                             |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

| MISCtI0.3 | -                             |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

| MISCtI0.2 | -                             |                                                                                                                                                                                                                                                                                                                                                                          |        |         |            |          |          |  |

| MISCtI0.1 | SLPBK                         | 1 = UART loop back testing mode. The pins TXD and RXD are to be connected together externally (with SLPBK =1) and therefore:         SLPBK       SSEL       Mode         0       0       normal using Serial_0         0       1       normal using Serial_1         1       0       Serial_0 TX feeds Serial_1 RX         1       1       Serial_1 TX feeds Serial_0 RX |        |         |            |          |          |  |

| MISCtI0.0 | SSEL                          | Selects either Serial_1 if set =1 or Serial_0 if set = 0 to be connected to RXD and TXD pins.                                                                                                                                                                                                                                                                            |        |         |            |          |          |  |

#### Table 38: The MISCtI0 Register

### 1.7.4.1 Serial Interface 0

The Serial Interface 0 can operate in four modes:

### • Mode 0

Pin RX serves as input and output. TX outputs the shift clock. 8 bits are transmitted with LSB first. The baud rate is fixed at 1/12 of the crystal frequency. Reception is initialized in Mode 0 by setting the flags in SOCON as follows: RI0 = 0 and REN0 = 1. In other modes, a start bit when REN0 = 1 starts receiving serial data.

### • Mode 1

Pin RX serves as input, and TX serves as serial output. No external shift clock is used, 10 bits are transmitted: a start bit (always 0), 8 data bits (LSB first), and a stop bit (always 1). On receive, a start bit synchronizes the transmission, 8 data bits are available by reading SOBUF, and stop bit sets the flag RB80 in the Special Function Register SOCON. In mode 1 either internal baud rate generator or timer 1 can be use to specify baud rate.

Mode 2

This mode is similar to Mode 1, with two differences. The baud rate is fixed at 1/32 or 1/64 of oscillator frequency and 11 bits are transmitted or received: a start bit (0), 8 data bits (LSB first), a programmable 9th bit, and a stop bit (1). The 9th bit can be used to control the parity of the serial interface: at transmission, bit TB80 in SOCON is output as the 9th bit, and at receive, the 9th bit affects RB80 in Special Function Register SOCON.

#### • Mode 3

The only difference between Mode 2 and Mode 3 is that in Mode 3 either internal baud rate generator or timer 1 can be use to specify baud rate.

The SOBUF register is used to read/write data to/from the serial 0 interface.

| M1 | MO | Mode   | Function                                                                                                                                                 |  |  |  |  |

|----|----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0  | 0  | Mode 0 | Mode 0 13-bit Counter/Timer.                                                                                                                             |  |  |  |  |

| 0  | 1  | Mode 1 | Mode 1 16-bit Counter/Timer.                                                                                                                             |  |  |  |  |

| 1  | 0  | Mode 2 | Mode 2 8-bit auto-reload Counter/Timer.                                                                                                                  |  |  |  |  |

| 1  | 1  | Mode 3 | If Timer 1 M1 and M0 bits are set to '1', Timer 1 stops. If Timer 0 M1 and M0 bits are set to '1', Timer 0 acts as two independent 8-bit Timer/Counters. |  |  |  |  |

#### Table 42: Timers/Counters Mode Description

### Mode 0

Putting either timer/counter into mode 0 configures it as an 8-bit timer/counter with a divide-by-32 prescaler. In this mode, the timer register is configured as a 13-bit register. As the count rolls over from all 1's to all 0's, it sets the timer overflow flag TF0. The overflow flag TF0 then can be used to request an interrupt. The counted input is enabled to the timer when TRx = 1 and either GATE = 0 or TX = 1 (setting GATE = 1 allows the timer to be controlled by external input TX, to facilitate pulse width measurements). TRx are control bits in the special function register TCON; GATE is in TMOD. The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL0. The upper 3 bits of TL0 are indeterminate and should be ignored. Setting the run flag (TRx) does not clear the registers. Mode 0 operation is the same for timer 0 as for timer 1.

### Mode 1

Mode 1 is the same as mode 0, except that the timer register is run with all 16 bits.

### Mode 2

Mode 2 configures the timer register as an 8-bit counter (TLx) with automatic reload. The overflow from TLx not only sets TFx, but also reloads TLx with the contents of THx, which is preset by software. The reload leaves THx unchanged.

### Mode 3

Mode 3 has different effects on timer 0 and timer 1. Timer 1 in mode 3 simply holds its count. The effect is the same as setting TR1 = 0. Timer 0 in mode 3 establishes TL0 and TH0 as two separate counters. TL0 uses the timer 0 control bits: C/T, GATE, TR0, INT0, and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from timer 1. Thus, TH0 now controls the "timer 1" interrupt. Mode 3 is provided for applications requiring an extra 8-bit timer or counter. When timer 0 is in mode 3, timer 1 can be turned on and off by switching it out of and into its own mode 3, or can still be used by the serial channel as a baud rate generator, or in fact, in any application not requiring an interrupt from timer 1 itself.

### 1.7.9 Analog Voltage Comparator

The 73S1215F includes a programmable comparator that is connected to the ANA\_IN pin. The comparator can be configured to trigger an interrupt if the input voltage rises above or falls below a selectable threshold voltage. The comparator control register should not be modified when the analog interrupt (ANAIEN bit in the INT6Ctl register) is enabled to guard against any false interrupt that might be generated when modifying the threshold. The comparator has a built-in hysteresis to prevent the comparator from repeatedly responding to low-amplitude noise. This hysteresis is approximately 20mV. The maximum voltage on the ANA\_IN pad should be less than 3 volts. An external resistor divider is required for detecting voltages greater than 3.0 volts. Interrupt control is handled in the INT6Ctl register.

### Analog Compare Control Register (ACOMP): 0xFFD0 ← 0x00

| MSB    |   |       |      |       |   |        | LSB    |  |

|--------|---|-------|------|-------|---|--------|--------|--|

| ANALVL | _ | ONCHG | CPOL | CMPEN | 0 | TSEL.1 | TSEL.0 |  |

| Bit     | Symbol | Function                                                                                                                                                                                        |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACOMP.7 | ANALVL | When read, indicates whether the input level is above or below the threshold. This is a real time value and is not latched, so it may change from the time of the interrupt trigger until read. |

| ACOMP.6 | -      |                                                                                                                                                                                                 |

| ACOMP.5 | ONCHG  | If set, the Ana_interrupt is invoked on any change above or below the threshold, bit 4 is ignored.                                                                                              |

| ACOMP.4 | CPOL   | If set = 1, Ana_interrupt is invoked when signal rises above selected threshold. If set = 0, Ana_interrupt is invoked when signal goes below selected threshold (default).                      |

| ACOMP.3 | CMPEN  | Enables power to the analog comparator. 1= Enabled. 0 = Disabled (default).                                                                                                                     |

| ACOMP.2 | 0      | This value must be fixed at 0.                                                                                                                                                                  |

| ACOMP.1 | TSEL.1 | Sets the voltage threshold for comparison to the voltage on pin ANA_IN.<br>Thresholds are as follows:<br>00 = 1.00V                                                                             |

| ACOMP.0 | TSEL.0 | 01 = 1.24V<br>10 = 1.40V<br>11 = 1.50V                                                                                                                                                          |

#### Table 60: The ACOMP Register

### I2C Secondary Read Data Register (SRDR): 0XFF84 ← 0x00

### Table 67: The SRDR Register

| MSB    |        |        |        |        |        |        | LSB    |  |

|--------|--------|--------|--------|--------|--------|--------|--------|--|

| SRDR.7 | SRDR.6 | SRDR.5 | SRDR.4 | SRDR.3 | SRDR.2 | SRDR.1 | SRDR.0 |  |

| Bit    | Function                                                                                            |

|--------|-----------------------------------------------------------------------------------------------------|

| SRDR.7 |                                                                                                     |

| SRDR.6 |                                                                                                     |

| SRDR.5 |                                                                                                     |

| SRDR.4 | Second Data byte to be read from the I <sup>2</sup> C slave device if bit 0 (I2CLEN) of the Control |

| SRDR.3 | and Status register (CSR) is set = 1.                                                               |

| SRDR.2 |                                                                                                     |

| SRDR.1 |                                                                                                     |

| SRDR.0 |                                                                                                     |

### I2C Control and Status Register (CSR): 0xFF85 ← 0x00

### Table 68: The CSR Register

| MSB |   |   |   |   |       |       | LSB    |

|-----|---|---|---|---|-------|-------|--------|

| _   | _ | — | _ | - | AKERR | I2CST | I2CLEN |

| Bit   | Symbol | Function                                                                                                                                                                                                                                                                                 |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSR.7 | -      |                                                                                                                                                                                                                                                                                          |

| CSR.6 | -      |                                                                                                                                                                                                                                                                                          |

| CSR.5 | -      |                                                                                                                                                                                                                                                                                          |

| CSR.4 | -      |                                                                                                                                                                                                                                                                                          |

| CSR.3 | -      |                                                                                                                                                                                                                                                                                          |

| CSR.2 | AKERR  | Set to 1 if acknowledge bit from Slave Device is not 0. Automatically reset when the new bus transaction is started.                                                                                                                                                                     |

| CSR.1 | I2CST  | Write a 1 to start I <sup>2</sup> C transaction. Automatically reset to 0 when the bus transaction is done. This bit should be treated as a "busy" indicator on reading. If it is high, the serial read/write operations are not completed and no new address or data should be written. |

| CSR.0 | I2CLEN | Set to 1 for 2-byte read or write operations. Set to 0 for 1-byte operations.                                                                                                                                                                                                            |

LSB

### Keypad Scan Time Register (KSCAN): 0xD3 ← 0x00

This register contains the values of scanning time and debouncing time.

#### Table 72: The KSCAN Register

#### MSB

DBTIME.5 DBTIME.4 DBTIME.3 DBTIME.2 DBTIME.1 DBTIME.0 SCTIME.1 SCTIME.0

| Bit     | Symbol   | Function                                                                                                                                     |  |  |  |  |  |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| KSCAN.7 | DBTIME.5 |                                                                                                                                              |  |  |  |  |  |

| KSCAN.6 | DBTIME.4 | De-bounce time in 4ms increments. $1 = 4ms$ de-bounce time, $0x3F = 252ms$ , $0x00 = 256ms$ . Key process and key releases are de bounced by |  |  |  |  |  |

| KSCAN.5 | DBTIME.3 |                                                                                                                                              |  |  |  |  |  |

| KSCAN.4 | DBTIME.2 | 252ms, 0x00 = 256ms. Key presses and key releases are de-bounced this amount of time.                                                        |  |  |  |  |  |

| KSCAN.3 | DBTIME.1 |                                                                                                                                              |  |  |  |  |  |

| KSCAN.2 | DBTIME.0 |                                                                                                                                              |  |  |  |  |  |

| KSCAN.1 | SCTIME.1 | Scan time in ms. 01 = 1ms, 02 = 2ms, 00 = 3ms, 00 = 4ms. Time between                                                                        |  |  |  |  |  |

| KSCAN.0 | SCTIME.0 | checking each key during keypad scanning.                                                                                                    |  |  |  |  |  |

### Keypad Control/Status Register (KSTAT): 0xD4 ← 0x00

This register is used to control the hardware keypad scanning and detection capabilities, as well as the keypad interrupt control and status.

#### Table 73: The KSTAT Register

| MSB |   |   |   |        |        |        | LSB    |

|-----|---|---|---|--------|--------|--------|--------|

| -   | - | _ | _ | KEYCLK | HWSCEN | KEYDET | KYDTEN |

| Bit     | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KSTAT.7 | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| KSTAT.6 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| KSTAT.5 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| KSTAT.4 | -      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| KSTAT.3 | KEYCLK | The current state of the keyboard clock can be read from this bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| KSTAT.2 | HWSCEN | Hardware Scan Enable – When set, the hardware will perform automatic key scanning. When cleared, the firmware must perform the key scanning manually (bypass mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| KSTAT.1 | KEYDET | Key Detect – When HWSCEN = 1 this bit is set causing an interrupt that<br>indicates a valid key press was detected and the key location can be read<br>from the Keypad Column and Row registers. When HWSCEN = 0, this bit<br>is an interrupt which indicates a falling edge on any Row input if all Row<br>inputs had been high previously (note: multiple Key Detect interrupts may<br>occur in this case due to the keypad switch bouncing). In all cases, this bit<br>is cleared when read. When HWSCEN = 0 and the keypad interface 1kHz<br>clock is disabled, a key press will still set this bit and cause an interrupt. |

| KSTAT.0 | KYDTEN | Key Detect Enable – When set, the KEYDET bit can cause an interrupt and when cleared the KEYDET cannot cause an interrupt. KEYDET can still get set even if the interrupt is not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

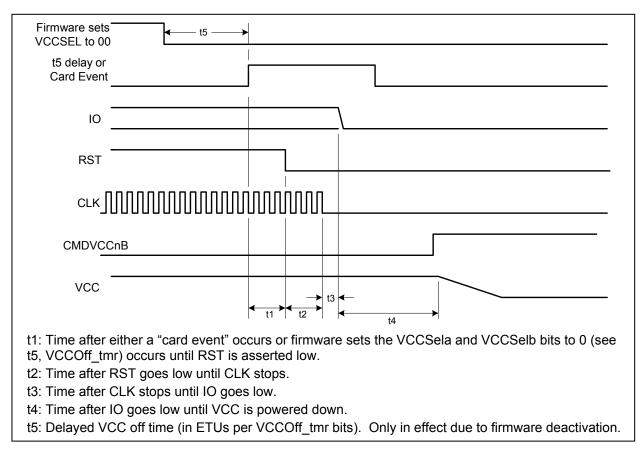

Smart card RST, I/O and CLK, C4, C8 shall be low before the end of the deactivation sequence. Figure 18 shows the timing for a deactivation sequence.

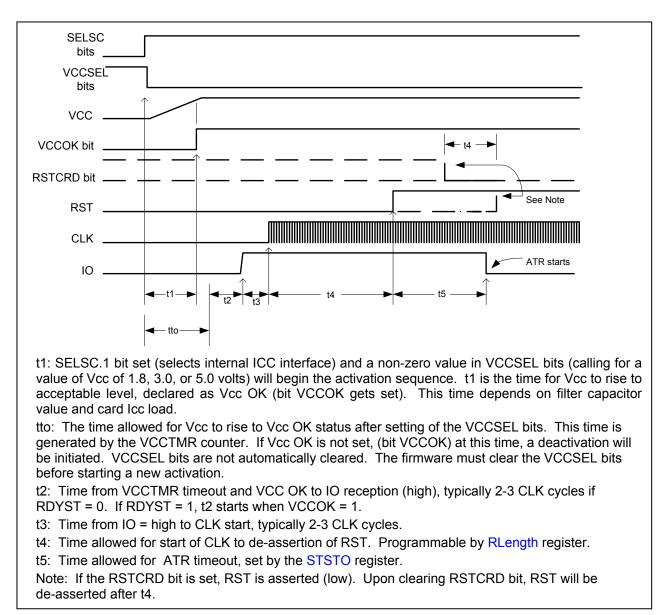

Figure 17: Asynchronous Activation Sequence Timing

### Figure 18: Deactivation Sequence

### 1.7.15.3 Data Reception/Transmission

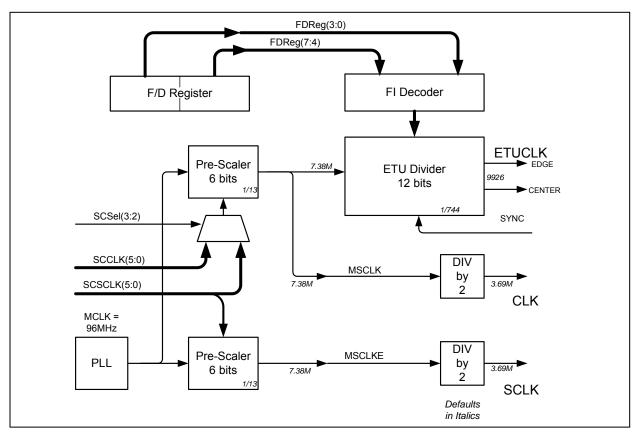

When a 12Mhz crystal is used, the smart card UART will generate a 3.69Mhz (default) clock to both smart card interfaces. This will allow approximately 9600bps (1/ETU) communication during ATR (ISO 7816 default). As part of the PPS negotiation between the smart card and the reader, the firmware may determine that the smart card parameters F & D may be changed. After this negotiation, the firmware may change the ETU by writing to the SFR FDReg to adjust the ETU and CLK. The firmware may also change the smart card clock frequency by writing to the SFR SCCLK (SCECLK for external interface). Independent clock frequency control is provided to each smart card interface. Clock stop high or Clock stop low is supported in asynchronous mode. Figure 19 shows the ETU and CLK control circuits. The firmware determines when clock stop is supported by the smart card and when it is appropriate to go into that mode (and when to come out of it). The smart card UART is clocked by the same clock that is provided to the selected smart card. The transition between smart card clocks is handled in hardware to eliminate any glitches for the UART during switchover. The external smart card clock is not affected when switching the UART to communicate with the internal smart card.

Figure 19: Smart Card CLK and ETU Generation

There are two, two-byte FIFOs that are used to buffer transmit and receive data. During a T=0 processing, if a parity error is detected by the 73S1215F during message reception, an error signal (BREAK) will be generated to the smart card. The byte received will be discarded and the firmware notified of the error. Break generation and receive byte dropping can be disabled under firmware control. During the transmission of a byte, if an error signal (BREAK) is detected, the last byte is retransmitted again and the firmware notified. Retransmission can be disabled by firmware. When a correct byte is received, an interrupt is generated to the firmware, which then reads the byte from the receive FIFO. Receive overruns are detected by the hardware and reported via an interrupt. During transmission of a message, the firmware will write bytes into the transmit FIFO. The hardware will send them to the smart card. When the last byte of a message has been written, the firmware will need to set the LASTTX bit in the STXCtI SFR. This will cause the hardware to insert the CRC/LRC if in a T=1 protocol mode. CRC/LRC generation/checking is only provided during T=1 processing. Firmware will need to instruct the smart function to go into receive mode after this last transmit data byte if it expects a response from the smart card. At the end of the smart card response, the firmware will put the interface back into transmit mode if appropriate.

The hardware can check for the following card-related timeouts:

- Character Waiting Time (CWT)

- Block Waiting Time (BWT)

- Initial Waiting Time (IWT)

The firmware will load the Wait Time registers with the appropriate value for the operating mode at the appropriate time. Figure 20 shows the guard, block, wait and ATR time definitions. If a timeout occurs, an interrupt will be generated and the firmware can take appropriate recovery steps. Support is provided for adding additional guard times between characters (Extra Guard Time register) and between the last byte received by the 73S1215F and the first byte transmitted by the 73S1215F Block Guard Time register (BGT). Other than the protocol checks described above, the firmware is responsible for all protocol checking and error recovery.

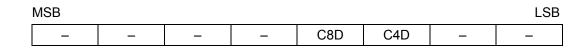

### C4/C8 Data Direction Register (SCDIR): 0xFE0C ← 0x00

This register determines the direction of the internal interface C4/C8 lines. After reset, all signals are tri-stated.

### Table 92: The SCDIR Register

| Bit     | Symbol | Function                                        |

|---------|--------|-------------------------------------------------|

| SCDIR.7 | _      |                                                 |

| SCDIR.6 | -      |                                                 |

| SCDIR.5 | -      |                                                 |

| SCDIR.4 | -      |                                                 |

| SCDIR.3 | C8D    | 1 = input, 0 = output. Smart Card C8 direction. |

| SCDIR.2 | C4D    | 1 = input, 0 = output. Smart Card C4 direction. |

| SCDIR.1 | -      |                                                 |

| SCDIR.0 | -      |                                                 |

ISB

### 1.7.16 VDD Fault Detect Function

The 73S1215F contains a circuit to detect a low-voltage condition on the supply voltage  $V_{DD}$ . If enabled, it will deactivate the active internal smart card interface when  $V_{DD}$  falls below the  $V_{DD}$  Fault threshold. The register configures the  $V_{DD}$  Fault threshold for the nominal default of 2.3V\* or a user selectable threshold. The user's code may load a different value using the FOVRVDDF bit =1 after the power-up cycle has completed

### VDDFault Control Register (VDDFCtl): 0xFFD4 ← 0x00

### Table 118: The VDDFCtl Register

MSB

| INISD |          |          |   |          |          |          | LOD      |

|-------|----------|----------|---|----------|----------|----------|----------|

| _     | FOVRVDDF | VDDFLTEN | _ | STXDAT.3 | VDDFTH.2 | VDDFTH.1 | VDDFTH.0 |

| Bit       | Symbol   | Function                                                                                                                                                                                                            |  |  |  |  |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| VDDFCtl.7 | -        |                                                                                                                                                                                                                     |  |  |  |  |

| VDDFCtl.6 | FOVRVDDF | Setting this bit high will allow the VDDFLT(2:0) bits set in this register to control the VDDFault threshold. When this bit is set low, the VDDFault threshold will be set to the factory default setting of 2.3V*. |  |  |  |  |

| VDDFCtl.5 | VDDFLTEN | Set = 1 will disable VDD Fault operation.                                                                                                                                                                           |  |  |  |  |

| VDDFCtl.4 | -        |                                                                                                                                                                                                                     |  |  |  |  |

| VDDFCtl.3 | _        |                                                                                                                                                                                                                     |  |  |  |  |

| VDDFCtl.2 | VDDFTH.2 | VDD Fault Threshold.<br>Bit value(2:0) VDDFault voltage                                                                                                                                                             |  |  |  |  |

| VDDFCtl.1 | VDDFTH.1 | 000         2.3 (nominal default)           001         2.4           010         2.5                                                                                                                               |  |  |  |  |

| VDDFCtl.0 | VDDFTH.0 | 011       2.6         100       2.7         101       2.8         110       2.9         111       3.0                                                                                                               |  |  |  |  |

\* Note: The  $V_{DD}$  Fault factory default can be set to any threshold as defined by bits VDDFTH(2:0). The 73S1215F has the capability to burn fuses at the factory to set the factory default to any of these voltages. Contact Teridian for further details.

## 3.7.1 DC Characteristics

| Symbol             | Parameter                                 | Condition                                                              | Min | Тур. | Max  | Unit |

|--------------------|-------------------------------------------|------------------------------------------------------------------------|-----|------|------|------|

| I <sub>DD</sub>    | Supply Current                            | CPU clock @ 24MHz                                                      |     | 30   | 35   | mA   |

|                    |                                           | CPU clock @ 12MHz                                                      |     | 22   | 25.5 | mA   |

|                    |                                           | CPU clock @ 6MHz                                                       |     | 16   | 19.5 | mA   |

|                    |                                           | CPU clock @ 3.69MHz                                                    |     | 14   | 17   | mA   |

|                    |                                           | Power down<br>(-40 to 85 C)                                            |     | 8    | 50   | μA   |

|                    |                                           | Power down (25 C)                                                      |     | 6    | 13   | μA   |

| I <sub>PC</sub>    | Supply Current                            | V <sub>cc</sub> on, ICC=0<br>I/O, AUX1, AUX2=high,<br>CLK not toggling |     | 450  | 650  | μΑ   |

|                    |                                           | Power down                                                             |     | 1    | 10   |      |

| I <sub>PCOFF</sub> | $V_{PC}$ supply current when $V_{CC}$ = 0 | Smart card deactivated                                                 |     | 345  |      | μA   |

# 3.8 Voltage / Temperature Fault Detection Circuits

| Symbol           | Parameter                                                      | Condition                                                | Min | Тур.                                          | Max  | Unit |

|------------------|----------------------------------------------------------------|----------------------------------------------------------|-----|-----------------------------------------------|------|------|

| $V_{PCF}$        | $V_{PC}$ fault ( $V_{PC}$ Voltage supervisor threshold)        | V <sub>PC</sub> <v<sub>CC, a transient<br/>event</v<sub> |     | V <sub>CC</sub> ><br>V <sub>PC</sub> +<br>0.3 |      | v    |