# E. Analog Devices Inc./Maxim Integrated - 7351215F-68IMR/F Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | 80515                                                                |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 24MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SmartCard, UART/USART, USB                         |

| Peripherals                | LED, POR, WDT                                                        |

| Number of I/O              | 9                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 68-VFQFN Exposed Pad                                                 |

| Supplier Device Package    | 68-QFN (8x8)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/73s1215f-68imr-f |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FEATURES

#### 80515 Core:

- 1 clock cycle per instruction (most instructions)

- CPU clocked up to 24MHz

- 64kB Flash memory with security

- 2kB XRAM (User Data Memory)

- 256 byte IRAM

- Hardware watchdog timer

#### **Oscillators:**

- Single low-cost 6MHz to 12MHz crystal

- Optional 32768 Hz crystal (with internal RTC)

- An Internal PLL provides all the necessary clocks to each block of the system

#### Interrupts:

- Standard 80C515 4-priority level structure

- Nine different sources of interrupt to the core

#### **Power Down Modes:**

- 2 standard 80C515 Power Down and IDLE modes

- Extensive device power down mode

#### Timers:

- Two standard 80C52 timers T0 and T1

- One 16-bit timer that can generate RTC interrupts from the 32kHz clock

#### Built-in ISO-7816 Card Interface:

- LDO regulator produces VCC for the card (1.8V, 3V or 5V)

- Full compliance with EMV 4.1

- Activation/Deactivation sequencers

- Auxiliary I/O lines (C4-C8 signals)

- 6kV ESD protection on all interface pins

#### **Communication with Smart Cards:**

- ISO 7816 UART for protocols T=0, T=1

- (2) 2-Byte FIFOs for transmit and receive

- Configured to drive multiple external Teridian 73S8010x interfaces (for multi-SAM architectures)

#### **Communication Interfaces:**

- Full-duplex serial interface (1200 to 115kbps UART)

- USB 2.0 Full Speed 12Mbps Interface, PC/SC compliant with 4 Endpoints:

- Control (16B FIFO)

- Interrupt IN (32B FIFO)

- Bulk IN (128B FIFO)

- Bulk OUT (128B FIFO)

- I<sup>2</sup>C Master Interface (400kbps)

#### Man-Machine Interface and I/Os:

- 5x6 Keyboard (hardware scanning, debouncing and scrambling)

- Nine User I/Os

- Up to 4 programmable current outputs (LED)

#### Voltage Detection:

• Analog Input (detection range: 1.0V to 1.5V)

#### **Operating Voltage:**

- 2.7V to 3.6V (3V to 3.6V when USB is in use)

- 4.75 to 5.5V for smart card supply

#### **Operating Temperature:**

-40°C to 85°C

#### Packages:

- 68-pin QFN

- 44-pin QFN

#### Software:

- Two-level Application Programming Interface (ANSI C-language libraries)

- USB, T=0/T=1 and EMV-compliant smart card protocol layers

- CCID reference design and Windows® driver

## 1.2 Hardware Overview

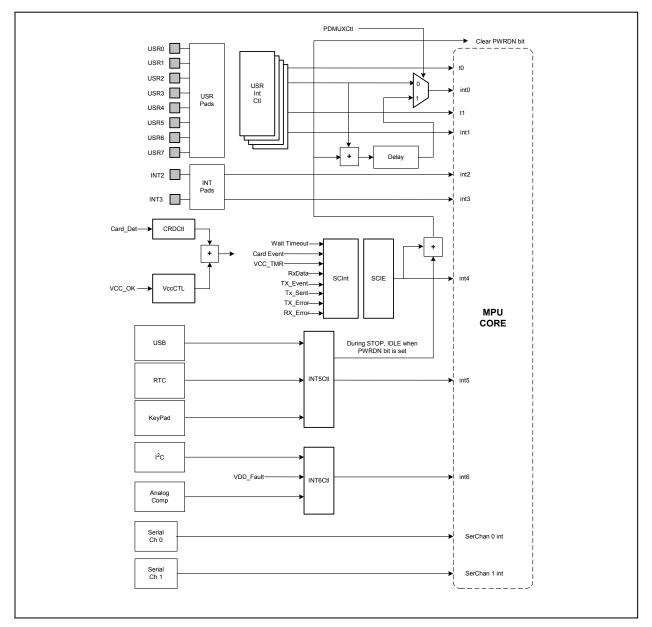

The Teridian 73S1215F single smart card controller integrates all primary functional blocks required to implement a smart card reader. Included on chip are an 8051-compatible microprocessor (MPU) which executes up to one instruction per clock cycle (80515), a fully integrated IS0-7816 compliant smart card interface, expansion smart card interface, full speed USB 2.0 compatible interface, serial interface, I2C interface, 6 x 5 keypad interface, 4 LED drivers, RAM, FLASH memory, a real time clock (RTC), and a variety of I/O pins. Figure 1 shows a functional block diagram of the 73S1215F.

## 1.3 80515 MPU Core

## 1.3.1 80515 Overview

The 73S1215F includes an 80515 MPU (8-bit, 8051-compatible) that performs most instructions in one clock cycle. The 80515 architecture eliminates redundant bus states and implements parallel execution of fetch and execution phases. Normally a machine cycle is aligned with a memory fetch, therefore, most of the 1-byte instructions are performed in a single cycle. This leads to an 8x performance (average) improvement (in terms of MIPS) over the Intel 8051 device running at the same clock frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application (cryptographic calculations, key management, memory management, and I/O management) using the XRAM special function register MPUCKCtl.

Typical smart card, USB, serial, keyboard, I2C, and RTC management functions are available for the MPU as part of the Teridian standard library. A standard ANSI "C" 80515-application programming interface library is available to help reduce design cycle. Refer to the *73S12xxF Software User's Guide*.

#### 1.3.2 Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces. Memory organization in the 80515 is similar to that of the industry standard 8051. There are three memory areas: Program memory (Flash), external data memory (XRAM), and internal data memory (IRAM). Data bus address space is allocated to on-chip memory as shown Table 2.

| Address<br>(hex) | Memory<br>Technology | Memory Type  | Typical Usage                 | Memory Size<br>(bytes) |

|------------------|----------------------|--------------|-------------------------------|------------------------|

| 0000-FFFF        | Flash Memory         | Non-volatile | Program and non-volatile data | 64KB                   |

| 0000-07FF        | Static RAM           | Volatile     | MPU data XRAM                 | 2KB                    |

| FC00-FFFF        | External SFR         | Volatile     | Peripheral control            | 1KB                    |

Table 2: MPU Data Memory Map

Note: The IRAM is part of the core and is addressed differently.

**Program Memory:** The 80515 can address up to 64KB of program memory space from 0x0000 to 0xFFFF. Program memory is read when the MPU fetches instructions or performs a MOVC operation. After reset, the MPU starts program execution from location 0x0000. The lower part of the program memory includes reset and interrupt vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0x0003 (Reset is located at 0x0000).

**Flash Memory:** The program memory consists of flash memory. The flash memory is intended to primarily contain MPU program code. Flash erasure is initiated by writing a specific data pattern to specific SFR registers in the proper sequence. These special pattern/sequence requirements prevent inadvertent erasure of the flash memory.

## 1.5 Special Function Registers (SFRs)

The 73S1215F utilizes numerous SFRs to communicate with the 73S1215F s many peripherals. This results in the need for more SFR locations outside the direct address IRAM space (0x80 to 0xFF). While some peripherals are mapped to unused IRAM SFR locations, additional SFRs for the USB, smart card and other peripheral functions are mapped to the top of the XRAM data space (0xFC00 to 0xFFF).

## 1.5.1 Internal Data Special Function Registers (SFRs)

A map of the Special Function Registers is shown in Table 6.

| Hex\<br>Bin | X000  | X001   | X010    | X011   | X100  | X101   | X110    | X111    | Bin/<br>Hex |

|-------------|-------|--------|---------|--------|-------|--------|---------|---------|-------------|

| F8          |       |        |         |        |       |        |         |         | FF          |

| F0          | В     |        |         |        |       |        |         |         | F7          |

| E8          |       |        |         |        |       |        |         |         | EF          |

| E0          | Α     |        |         |        |       |        |         |         | E7          |

| D8          | BRCON |        |         |        |       |        |         |         | DF          |

| D0          | PSW   | KCOL   | KROW    | KSCAN  | KSTAT | KSIZE  | KORDERL | KORDERH | D7          |

| C8          | T2CON |        |         |        |       |        |         |         | CF          |

| C0          | IRCON |        |         |        |       |        |         |         | C7          |

| B8          | IEN1  | IP1    | SORELH  | S1RELH |       |        |         |         | BF          |

| B0          |       |        | FLSHCTL |        |       |        |         | PGADDR  | B7          |

| A8          | IEN0  | IP0    | SORELL  |        |       |        |         |         | AF          |

| A0          | USR8  | UDIR8  |         |        |       |        |         |         | A7          |

| 98          | S0CON | SOBUF  | IEN2    | S1CON  | S1BUF | S1RELL |         |         | 9F          |

| 90          | USR70 | UDIR70 | DPS     |        | ERASE |        |         |         | 97          |

| 88          | TCON  | TMOD   | TL0     | TL1    | TH0   | TH1    | CKCON   | MCLKCTL | 8F          |

| 80          |       | SP     | DPL     | DPH    | DPL1  | DPH1   | WDTREL  | PCON    | 87          |

#### Table 6: IRAM Special Function Registers Locations

Only a few addresses are used, the others are not implemented. SFRs specific to the 73S1215F are shown in **bold** print (gray background). Any read access to unimplemented addresses will return undefined data, while most write access will have no effect. However, a few locations are reserved and not user configurable in the 73S1215F. Writes to the unused SFR locations can affect the operation of the core and therefore must not be written to. This applies to all the SFR areas in both the IRAM and XRAM spaces. In addition, all unused bit locations within valid SFR registers must be left in their default (power on default) states.

## 1.7.3 Interrupts

The 80515 core provides 10 interrupt sources with four priority levels. Each source has its own request flag(s) located in a special function register (TCON, IRCON, and SCON). Each interrupt requested by the corresponding flag can be individually enabled or disabled by the enable bits in SFRs IEN0, IEN1 and IEN2. Some of the 10 sources are multiplexed in order to expand the number of interrupt sources. These will be described in more detail in the respective sections.

External interrupts are the interrupts external to the 80515 core, i.e. signals that originate in other parts of the 73S1215F, for example the USB interface, USR I/O, RTC, smart card interface, analog comparators, etc. The external interrupt configuration is shown in Figure **8**.

#### Timer/Counter Control Register (TCON): 0x88 ← 0x00

Table 43: The TCON Register

| MSB |     |     |     |     |     |     | LSB |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |  |

| Bit    | Symbol | Function                                                                                                                                                                     |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCON.7 | TF1    | The Timer 1 overflow flag is set by hardware when Timer 1 overflows.<br>This flag can be cleared by software and is automatically cleared when<br>an interrupt is processed. |

| TCON.6 | TR1    | Timer 1 Run control bit. If cleared, Timer 1 stops.                                                                                                                          |

| TCON.5 | TF0    | Timer 0 overflow flag set by hardware when Timer 0 overflows. This flag can be cleared by software and is automatically cleared when an interrupt is processed.              |

| TCON.4 | TR0    | Timer 0 Run control bit. If cleared, Timer 0 stops.                                                                                                                          |

| TCON.3 | IE1    | External Interrupt 1 edge flag.                                                                                                                                              |

| TCON.2 | IT1    | External interrupt 1 type control bit.                                                                                                                                       |

| TCON.1 | IE0    | External Interrupt 0 edge flag.                                                                                                                                              |

| TCON.0 | IT0    | External Interrupt 0 type control bit.                                                                                                                                       |

#### 1.7.6 WD Timer (Software Watchdog Timer)

The software watchdog timer is a 16-bit counter that is incremented once every 24 or 384 clock cycles. After a reset, the watchdog timer is disabled and all registers are set to zero. The watchdog consists of a 16-bit counter (WDT), a reload register (WDTREL), prescalers (by 2 and by 16), and control logic. Once the watchdog starts, it cannot be stopped unless the internal reset signal becomes active.

## Note: It is recommended to use the hardware watchdog timer instead of the software watchdog timer (refer to the RTC description).

**WD Timer Start Procedure:** The WDT is started by setting the SWDT flag. When the WDT register enters the state 0x7CFF, an asynchronous WDTS signal will become active. The signal WDTS sets bit 6 in the IP0 register and requests a reset state. WDTS is cleared either by the reset signal or by changing the state of the WDT timer.

**Refreshing the WD Timer:** The watchdog timer must be refreshed regularly to prevent the reset request signal from becoming active. This requirement imposes an obligation on the programmer to issue two instructions. The first instruction sets WDT and the second instruction sets SWDT. The maximum delay allowed between setting WDT and SWDT is 12 clock cycles. If this period has expired and SWDT has not been set, WDT is automatically reset, otherwise the watchdog timer is reloaded with the content of the WDTREL register and WDT is automatically reset.

## 1.7.7 User (USR) Ports

The 73S1215F includes 9 pins of general purpose digital I/O (GPIO). On reset or power-up, all USR pins are inputs until they are configured for the desired direction. The pins are configured and controlled by the USR and UDIR SFRs. Each pin declared as USR can be configured independently as an input or output with the bits of the UDIRn registers. Table 48 lists the direction registers and configurability associated with each group of USR pins. USR pins 0 to 7 are multiple use pins that can be used for general purpose I/O, external interrupts and timer control.

Table 49 shows the configuration for a *USR* pin through its associated bit in its UDIR register. Values read from and written into the GPIO ports use the data registers USR70 and USR8. Note: After reset, all USR pins are defaulted as inputs and pulled up to VDD until any write to the corresponding UDIR register is performed. This insures all USR pins are set to a known value until set by the firmware. Unused USR pins can be set for output if unused and unconnected to prevent them from floating. Alternatively, unused USR pins can be set for input and tied to ground or  $V_{DD}$ .

Table 48: Direction Registers and Internal Resources for DIO Pin Groups

| USR Pin Group | Туре      | Direction<br>Register<br>Name | Direction<br>Register<br>(SFR)<br>Location | Data<br>Register<br>Name | Data<br>Register<br>(SFR)<br>Location |

|---------------|-----------|-------------------------------|--------------------------------------------|--------------------------|---------------------------------------|

| USR_0USR_7    | Multi-use | UDIR70                        | 0x91 [7:0]                                 | USR70                    | 0x90 [7:0]                            |

| USR_8         | GPIO only | UDIR8                         | 0xA1 [0]                                   | USR8                     | 0xA0 [0]                              |

#### Table 49: UDIR Control Bit

|                     | UDIR   | Bit   |  |  |

|---------------------|--------|-------|--|--|

|                     | 0 1    |       |  |  |

| USR Pin<br>Function | output | input |  |  |

Four XRAM SFR registers (USRIntCtl1, USRIntCtl2, USRIntCtl3, and USRIntCtl4) control the use of the USR [7:0] pins. Each of the USR [7:0] pins can be configured as GPIO or individually be assigned an internal resource such as an interrupt or a timer/counter control. Each of the four registers contains two 3-bit configuration words named UxIS (where x corresponds to the USR pin). The control resources selectable for the USR pins are listed in Table 50through Table 54. If more than one input is connected to the same resource, the resources are combined using a logical OR.

#### Table 50: Selectable Controls Using the UxIS Bits

| UxIS Value | Resource Selected for USRx Pin             |  |  |  |  |

|------------|--------------------------------------------|--|--|--|--|

| 0          | None                                       |  |  |  |  |

| 1          | None                                       |  |  |  |  |

| 2          | T0 (counter0 gate/clock)                   |  |  |  |  |

| 3          | T1 (counter1 gate/clock)                   |  |  |  |  |

| 4          | Interrupt 0 rising edge/high level on USRx |  |  |  |  |

| 5          | Interrupt 1 rising edge/high level on USRx |  |  |  |  |

| 6          | Interrupt 0 falling edge/low level on USRx |  |  |  |  |

| 7          | Interrupt 1 falling edge/low level on USRx |  |  |  |  |

Note: x denotes the corresponding USR pin. Interrupt edge or level control is assigned in the IT0 and IT1 bits in the TCON register.

#### External Interrupt Control Register (USRIntCtI1) : 0xFF90 ← 0x00

#### Table 51: The USRIntCtl1 Register

| MSB |        |        |        |   |        |        | LSB    |  |

|-----|--------|--------|--------|---|--------|--------|--------|--|

| _   | U1IS.6 | U1IS.5 | U1IS.4 | - | U0IS.2 | U0IS.1 | U0IS.0 |  |

#### External Interrupt Control Register (USRIntCtl2) : 0xFF91 ← 0x00

#### Table 52: The USRIntCtl2 Register

| MSB |        |        |        |   |        |        | LSB    |  |

|-----|--------|--------|--------|---|--------|--------|--------|--|

| -   | U3IS.6 | U3IS.5 | U3IS.4 | - | U2IS.2 | U2IS.1 | U2IS.0 |  |

#### External Interrupt Control Register (USRIntCtI3) : 0xFF92 ← 0x00

#### Table 53: The USRIntCtl3 Register

| Ν | /ISB |        |        |        |  |        |        | LSB    |

|---|------|--------|--------|--------|--|--------|--------|--------|

|   | _    | U5IS.6 | U5IS.5 | U5IS.4 |  | U4IS.2 | U4IS.1 | U4IS.0 |

#### External Interrupt Control Register (USRIntCtl4) : 0xFF93 ← 0x00

#### Table 54: The USRIntCtl4 Register

| I | MSB |        |        |        |   |        |        | LSB    |

|---|-----|--------|--------|--------|---|--------|--------|--------|

|   | _   | U7IS.6 | U7IS.5 | U7IS.4 | _ | U6IS.2 | U6IS.1 | U6IS.0 |

## 1.7.8 Real-Time Clock with Hardware Watchdog (RTC)

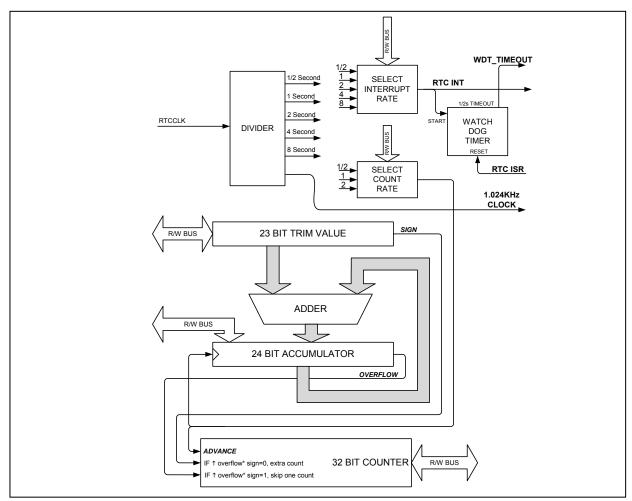

Figure 9 shows the block diagram of the Real Time Clock. The RTC block uses the 32768Hz oscillator signal and divider logic to produce 0.5-second time marks. The time marks are used to create interrupts at intervals from 0.5 seconds to 8 seconds as selected by RTC Interval (RTCINV(2:0)). The 32768Hz oscillator can be disabled but is intended to operate at all times and in all power consumption modes. If a 32kHz crystal is not provided, the 32kHz oscillator should be disabled and the RTC will operate from MCLK (96MHz) divided by 2930 (refer to the oscillator and clock generation section). The clock generated by the high speed oscillator will not yield exactly 32768 Hz, but a frequency of approximately 32764.505119 Hz. This yields a negative 106.6 PPM (1 / 9375) error with respect to 32768Hz. The RTC circuit provides hardware to compensate for this error by providing an offset circuit that will adjust the RTC counter.

Figure 9: Real Time Clock Block Diagram

## Device Address Register (DAR): 0xFF80 ← 0x00

## Table 63: The DAR Register

| MSB |         |         |         |         |         |         |         | LSB   |   |

|-----|---------|---------|---------|---------|---------|---------|---------|-------|---|

|     | DVADR.6 | DVADR.5 | DVADR.4 | DVADR.3 | DVADR.2 | DVADR.1 | DVADR.0 | I2CRW | 1 |

| Bit   | Symbol         | Function                                                            |  |  |  |  |  |

|-------|----------------|---------------------------------------------------------------------|--|--|--|--|--|

| DAR.7 |                |                                                                     |  |  |  |  |  |

| DAR.6 | DVADR<br>[0:6] |                                                                     |  |  |  |  |  |

| DAR.5 |                |                                                                     |  |  |  |  |  |

| DAR.4 |                | Slave device address.                                               |  |  |  |  |  |

| DAR.3 | [0.0]          |                                                                     |  |  |  |  |  |

| DAR.2 |                |                                                                     |  |  |  |  |  |

| DAR.1 |                |                                                                     |  |  |  |  |  |

| DAR.0 | I2CRW          | If set = 0, the transaction is a write operation. If set = 1, read. |  |  |  |  |  |

## I2C Write Data Register (WDR): 0XFF81 ← 0x00

#### Table 64: The WDR Register

| MSB         |                                                          |       |       |             |       |       | LSB   |   |  |  |  |

|-------------|----------------------------------------------------------|-------|-------|-------------|-------|-------|-------|---|--|--|--|

| WDR.7       | 7 WDR.6                                                  | WDR.5 | WDR.4 | WDR.3       | WDR.2 | WDR.1 | WDR.0 |   |  |  |  |

| <b>D</b> '' |                                                          |       |       | <b>F</b> () |       |       |       | ] |  |  |  |

| Bit         |                                                          |       |       | Functior    | 1     |       |       |   |  |  |  |

| WDR.7       |                                                          |       |       |             |       |       |       |   |  |  |  |

| WDR.6       |                                                          |       |       |             |       |       |       |   |  |  |  |

| WDR.5       | Data to be written to the I <sup>2</sup> C slave device. |       |       |             |       |       |       |   |  |  |  |

| WDR.4       |                                                          |       |       |             |       |       |       |   |  |  |  |

| WDR.3       |                                                          |       |       |             |       |       |       |   |  |  |  |

| WDR.2       |                                                          |       |       |             |       |       |       |   |  |  |  |

| WDR.1       |                                                          |       |       |             |       |       |       |   |  |  |  |

WDR.0

## External Interrupt Control Register (INT6CtI): 0xFF95 ← 0x00

## Table 69: The INT6Ctl Register

| MSB |   |        |        |        |        |       | LSB   |  |

|-----|---|--------|--------|--------|--------|-------|-------|--|

| _   | - | VFTIEN | VFTINT | I2CIEN | I2CINT | ANIEN | ANINT |  |

| Bit       | Symbol | Function                                                                                                      |

|-----------|--------|---------------------------------------------------------------------------------------------------------------|

| INT6Ctl.7 | _      |                                                                                                               |

| INT6Ctl.6 | _      |                                                                                                               |

| INT6Ctl.5 | VFTIEN | VDD fault interrupt enable.                                                                                   |

| INT6Ctl.4 | VFTINT | VDD fault interrupt flag.                                                                                     |

| INT6Ctl.3 | I2CIEN | When set = 1, the $I^2C$ interrupt is enabled.                                                                |

| INT6Ctl.2 | I2CINT | When set =1, the $I^2C$ transaction has completed. Cleared upon the start of a subsequent $I^2C$ transaction. |

| INT6Ctl.1 | ANIEN  | Analog compare interrupt enable.                                                                              |

| INT6Ctl.0 | ANINT  | Analog compare interrupt flag.                                                                                |

32768Hz crystal or the 12MHz crystal. The selection of the clock source is made external to this block, by setting bit 3 – 32KBEN – in the MCLKCtl register (see the oscillator and clock generation section). Disabling the 32kHz oscillator will source the 1kHz clock from the 12MHz main oscillator and divide it down. Setting bit 6 – KBEN – in the MCLKCtl register will enable keypad scanning and debouncing. The keypad size can be adjusted within the KSIZE register.

Normal scanning is performed by hardware when the bit SCNEN is set at 1 in the KSTAT register. Figure 13 shows the flowchart of how the hardware scanning operates. In order to minimize power, scanning does not occur until a key-press is detected. Once hardware key scanning is enabled, the hardware drives all column outputs low and waits for a low to be detected on one of the inputs. When a low is detected on any row, and before key scanning starts, the hardware checks that the low level is still detected after a debounce time. The debounce time is defined by firmware in the KSCAN register (bits 7:0, DBTIME). Debounce times from 4ms to 256ms in 4ms increments are supported. If a key is not pressed after the debounce time, the hardware will go back to looking for any input to be low. If a key is confirmed to be pressed, key scanning begins.

Key scanning asserts one of the 5 drive lines (COL 4:0) low and looks for a low on a sense line indicating that a key is pressed at the intersection of the drive/sense line in the keypad. After all sense lines have been checked without a key-press being detected, the next column line is asserted. The time between checking each sense line is the scan time and is defined by firmware in the KSCAN register (bits 0:1 – SCTIME). Scan times from 1ms to 4ms are supported. Scanning order does not affect the scan time. This scanning continues until the entire keypad is scanned. If only one key is pressed, a valid key is detected. Simultaneous key presses are not considered as valid (If two keys are pressed, no key is reported to firmware).

Possible scrambling of the column scan order is provided by means of KORDERL and KORDERH registers that define the order of column scanning. Values in these registers must be updated every time a new keyboard scan order is desired. It is not possible to change the order of scanning the sense lines. The column and row intersection for the detected valid key are stored in the KCOL and KROW registers. When a valid key is detected, an interrupt is generated. Firmware can then read those registers to determine which key had been pressed. After reading the KCOL and KROW registers, the firmware can update the KORDERL / KORDERH registers if a new scan order is needed.

When the SCNEN bit is enabled in the KSTAT register, the KCOL and KROW registers are only updated after a valid key has been identified. The hardware does not wait for the firmware to service the interrupt in order to proceed with the key scanning process. Once the valid key (or invalid key – e.g. two keys pressed) is detected, the hardware waits for the key to be released. Once the key is released, the debounce timer is started. If the key is not still released after the debounce time, the debounce counter starts again. After a key release, all columns will be driven low as before and the process will repeat waiting for any key to be pressed.

When the SCNEN bit is disabled, all drive outputs are set to the value in the KCOL register. If firmware clears the SCNEN bit in the middle of a key scan, the KCOL register contains the last value stored in there which will then be reflected on the output pins.

A bypass mode is provided so that the firmware can do the key scanning manually (SCNEN bit must be cleared). In bypass mode, the firmware writes/reads the Column and Row registers to perform the key scanning.

## Clock Control Register (CKCON): 0x8E ← 0x01

|         | Table 79: The CKCON Register |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

|---------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------|--|--|--|--|--|

| Ν       | ISB                          |                                                                                                                                                               |                                                                                                                                          |    | LSB                  |  |  |  |  |  |

|         | -                            |                                                                                                                                                               | —                                                                                                                                        | -  | CKWT.2 CKWT.1 CKWT.0 |  |  |  |  |  |

| Bit     | Symbol                       |                                                                                                                                                               |                                                                                                                                          | Fu | unction              |  |  |  |  |  |

| CKCON.7 | _                            |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.6 | _                            |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.5 | _                            |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.4 | _                            |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.3 | _                            |                                                                                                                                                               |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.2 | CKWT.2                       | insert when acc                                                                                                                                               | These three bits determine the number of wait states (machine cycles) to insert when accessing the USB SFRs: $000 = 0$ (not to be used). |    |                      |  |  |  |  |  |

| CKCON.1 | CKWT.1                       | 001 = 1 wait state.Use when MPU clock is <12MHz.010 = 2 wait states.Use when MPU clock is between 12 and 16MI011 = 3 wait states.Use when MPU clock is 24MHz. |                                                                                                                                          |    |                      |  |  |  |  |  |

| CKCON.0 | CKWT.0                       | 100 = 4 wait sta<br>101 = 5 wait sta<br>110 = 6 wait sta<br>111 = 7 wait sta                                                                                  | tes.<br>tes.                                                                                                                             |    |                      |  |  |  |  |  |

|                                                                                                                                          | START Bit                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                                                                                                                                      |                                                                                                                                                                                                                                   |

| IO                                                                                                                                       | Data from Card -end of ATR                                                                                                                                                                                                        |

| RLength Count - w                                                                                                                        | ras set for length of ATR RLength Count MAX 5 RLen=0 Rlen=1                                                                                                                                                                       |

| RLength Interrupt                                                                                                                        |                                                                                                                                                                                                                                   |

| CLK Stop                                                                                                                                 | ́,                                                                                                                                                                                                                                |

| CLK Stop Level                                                                                                                           | <sup>™</sup>                                                                                                                                                                                                                      |

| IO Bit                                                                                                                                   |                                                                                                                                                                                                                                   |

| IODir Bit                                                                                                                                |                                                                                                                                                                                                                                   |

| TX/RX Mode Bit<br>TX = '1'                                                                                                               | (4)                                                                                                                                                                                                                               |

| 2. Read and clea<br>3. Set CLK Stop<br>4. Set TX/RX Bit<br>5. Reload Rlengt<br>6. Set IO Bit Iow<br>7. Clear CLK Sto<br>Note: Data in TX | and CLK Stop level high in Interrupt routine.<br>to TX mode.<br>th Counter.<br>and IODir = Output. Since Rlen=(MAX or 0) and TX/RX =1, IO pin is controlled by IO bit.<br>p and CLK Stop level.<br>fifo should not be Empty here. |

|                                                                                                                                          | ous Clock Start/Stop Mode style Start bit procedure. This procedure should be used to<br>start bit insertion in Synchronous mode for Synchronous Clock Start/Stop Mode protocol.                                                  |

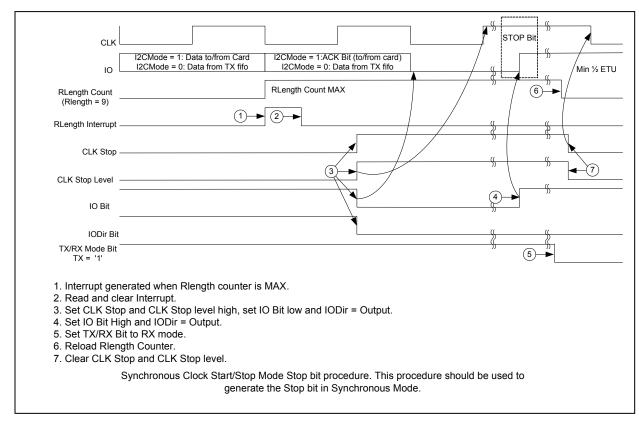

Figure 23: Creation of Synchronous Clock Start/Stop Mode Start Bit in Sync Mode

Figure 24: Creation of Synchronous Clock Start/Stop Mode Stop Bit in Sync Mode

#### Smart Card Interrupt Register (SCInt): 0xFE01 ← 0x00

When the smart card interrupt is asserted, the firmware can read this register to determine the actual cause of the interrupt. The bits are cleared when this register is read. Each interrupt can be disabled by the Smart Card Interrupt Enable register. Error processing must be handled by the firmware. This register relates to the interface that is active – see the SCSel register.

#### Table 82: The SCInt Register

| MSB    |        |         |       |       |        |       | LSB   |

|--------|--------|---------|-------|-------|--------|-------|-------|

| WAITTO | CRDEVT | VCCTMRI | RXDAV | TXEVT | TXSENT | TXERR | RXERR |

| Bit            | Symbol  | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCInt.7        | WAITTO  | Wait Timeout – An ATR or card wait timeout has occurred. In sync mode, this interrupt is asserted when the RLen counter (it advances on falling edges of CLK/ETU) reaches the loaded (max) value. This bit is cleared when the SCInt register is read. When running in Synchronous Clock Stop Mode, this bit becomes RLenINT interrupt (set when the Rlen counter reaches the terminal count).                                      |

| SCInt.6 CRDEVT |         | Card Event – A card event is signaled via pin DETCARD either when the Card was inserted or removed (read the CRDCtl register to determine card presence) or there was a fault condition in the interface circuitry. This bit is functional even if the smart card logic clock is disabled and when the PWRDN bit is set. This bit is cleared when the SCInt register is read.                                                       |

| SCInt.5        | VCCTMRI | VCC Timer – This bit is set when the VCCTMR times out. This bit is cleared when the SCInt register is read.                                                                                                                                                                                                                                                                                                                         |

| SCInt.4        | RXDAV   | Rx Data Available – Data was received from the smart card because the Rx FIFO is not empty. In bypass mode, this interrupt is generated on a falling edge of the smart card I/O line. After receiving this interrupt in bypass mode, firmware should disable it until the firmware has received the entire byte and is waiting for the next start delimiter. This bit is cleared when there is no RX data available in the RX FIFO. |

| SCInt.3        | TXEVNT  | TX Event – Set whenever the TXEMTY or TXFULL bits are set in the SRXCtl SFR. This bit is cleared when the STXCtl register is read.                                                                                                                                                                                                                                                                                                  |

| SCInt.2        | TXSENT  | TX Sent – Set whenever the ISO UART has successfully transmitted a byte to the smart card. Also set when a CRC/LRC byte is sent in T=1 mode. Will not be set in T=0 when a break is detected at the end of a byte (when break detection is enabled). This bit is cleared when the SCInt register is read.                                                                                                                           |

| SCInt.1        | TXERR   | TX Error – An error was detected during the transmission of data to the smart card as indicated by either BREAKD or TXUNDR bit being set in the STXCtl SFR. Additional information can be found in that register description. This bit is cleared when the STXCtl register is read.                                                                                                                                                 |

| SCInt.0        | RXERR   | RX Error – An error was detected during the reception of data from the smart card. Additional information can be found in the SRXCtl register. This interrupt will be asserted for RXOVRR, or RX Parity error events. This bit is cleared when the SRXCtl register is read.                                                                                                                                                         |

#### Smart Card V<sub>cc</sub> Control/Status Register (VccCtl): 0xFE03 ← 0x00

This register is used to control the power up and power down of the integrated smart card interface. It is used to determine whether to apply 5V, 3V, or 1.8V to the smart card. Perform the voltage selection with one write operation, setting both VCCSEL.1 and VCCSEL.0 bits simultaneously. The VDDFLT bit (if enabled) will provide an emergency deactivation of the internal smart card slot. See the VDD Fault Detect Function section for more detail.

#### Table 84: The VccCtl Register

| MSB      |          |        |       |       |   |   | LSB     |

|----------|----------|--------|-------|-------|---|---|---------|

| VCCSEL.1 | VCCSEL.0 | VDDFLT | RDYST | VCCOK | _ | - | SCPWRDN |

| Bit      | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          |          | Setting non-zero value for bits 7,6 will begin activation sequence with targe Vcc as given below:                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| VccCtl.7 | VCCSEL.1 | State VCCSEL.1 VCCSEL.0 VCC                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|          |          | 1 0 0 0V                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|          |          | 2 0 1 1.8V                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|          |          | 3 1 0 3.0V                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|          |          | 4 1 1 5V                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| VccCtl.6 | VCCSEL.0 | A card event or VCCOK going low will initiate a deactivation sequence.<br>When the deactivation sequence for RST, CLK and I/O is complete, $V_{CC}$ will<br>be turned off. When this type of deactivation occurs, the bits must be reset<br>before initiating another activation.                                                                                                     |  |  |  |  |  |  |

| VccCtl.5 | VDDFLT   | If this bit is set = 0, the CMDVCC3B and CMDVCC5B outputs are<br>immediately set = 1 to signal to the companion circuit to begin deactivation<br>when there is a VDD Fault event. If this bit is set = 1 and there is a VDD<br>Fault, the firmware should perform a deactivation sequence and then set<br>CMDVCC3B or CMDVCC5B = 1 to signal the companion circuit to set<br>VCC = 0. |  |  |  |  |  |  |

| VccCtl.4 | RDYST    | If this bit is set = 1, the activation sequence will start when bit VCCOK is set = 1. If not set, the deactivation sequence shall start when the VCCTMR times out.                                                                                                                                                                                                                    |  |  |  |  |  |  |

| VccCtl.3 | VCCOK    | (Read only). Indicates that $V_{CC}$ output voltage is stable.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| VccCtl.2 | _        |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| VccCtl.1 | _        |                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|          |          | This bit controls the power down mode of the 73S1215F circuit.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| VccCtl.0 | SCPWRDN  | 1 = power down, 0 = normal operation.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

#### ATR Timeout Registers (ATRLsB): 0xFE20 ← 0x00, (ATRMsB): 0xFE1F ← 0x00

| MSB     |         |         |         |         |         |         | LSB     |  |

|---------|---------|---------|---------|---------|---------|---------|---------|--|

| ATRTO.7 | ATRTO.6 | ATRTO.5 | ATRTO.4 | ATRTO.3 | ATRTO.1 | ATRTO.2 | ATRTO.0 |  |

#### Table 114: The ATRMsB Register

Table 113: The ATRLsB Register

| MSB |          |          |          |          |          |          |         |         |

|-----|----------|----------|----------|----------|----------|----------|---------|---------|

|     | ATRTO.15 | ATRTO.14 | ATRTO.13 | ATRTO.12 | ATRTO.11 | ATRTO.10 | ATRTO.9 | ATRTO.8 |

These registers (ATRLsB and ATRLsB) form the ATR timeout (ATRTO [15:0]) parameter. Time in ETU between the leading edge of the first character and leading edge of the last character of the ATR response. Timer is enabled when the RCVATR is set and starts when leading edge of the first start bit is received and disabled when the RCVATR is cleared. An ATR timeout is generated if this time is exceeded.

#### TS Timeout Register (STSTO): 0xFE21 ← 0x00

#### Table 115: The STSTO Register

| MSB |        |        |        |        |        |        |        |        |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

|     | TST0.7 | TST0.6 | TST0.5 | TST0.4 | TST0.3 | TST0.1 | TST0.2 | TST0.0 |

The TS timeout is the time in ETU between the de-assertion of smart card reset and the leading edge of the TS character in the ATR (when DETTS is set). The timer is started when smart card reset is de-asserted. An ATR timeout is generated if this time is exceeded (MUTE card).

#### Reset Time Register (RLength): 0xFE22 ← 0x70

#### Table 116: The RLength Register

| MSB    |        |        |        |        |        |        |        |  |  |

|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| RLen.7 | RLen.6 | RLen.5 | RLen.4 | RLen.3 | RLen.1 | RLen.2 | RLen.0 |  |  |

Time in ETUs that the hardware delays the de-assertion of RST. If set to zero and RSTCRD = 0, the hardware adds no extra delay and the hardware will release RST after VCCOK is asserted during power-up. If set to one, it will delay the release of RST by the time in this register. When the firmware sets the RSTCRD bit, the hardware will assert reset (RST = 0 on pin). When firmware clears the bit, the hardware will release RST after the delay specified in Rlen. If firmware sets the RSTCRD bit prior to instructing the power to be applied to the smart card, the hardware will not release RST after power-up until RLen after the firmware clears the RSTCRD bit. This provides a means to power up the smart card and hold it in reset until the firmware wants to release the RST to the selected smart card. Works with the selected smart card interface.

ISB

## 1.7.16 VDD Fault Detect Function

The 73S1215F contains a circuit to detect a low-voltage condition on the supply voltage  $V_{DD}$ . If enabled, it will deactivate the active internal smart card interface when  $V_{DD}$  falls below the  $V_{DD}$  Fault threshold. The register configures the  $V_{DD}$  Fault threshold for the nominal default of 2.3V\* or a user selectable threshold. The user's code may load a different value using the FOVRVDDF bit =1 after the power-up cycle has completed

#### VDDFault Control Register (VDDFCtl): 0xFFD4 ← 0x00

#### Table 118: The VDDFCtl Register

MSB

| _ | FOVRVDDF | VDDFLTEN | _ | STXDAT.3 | VDDFTH.2 | VDDFTH.1 | VDDFTH.0 |  |  |  |  |

|---|----------|----------|---|----------|----------|----------|----------|--|--|--|--|

| Bit       | Symbol   | Function                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VDDFCtl.7 | -        |                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| VDDFCtl.6 | FOVRVDDF | tting this bit high will allow the VDDFLT(2:0) bits set in this register to ntrol the VDDFault threshold. When this bit is set low, the VDDFault eshold will be set to the factory default setting of 2.3V*. |  |  |  |  |  |  |  |

| VDDFCtl.5 | VDDFLTEN | Set = 1 will disable VDD Fault operation.                                                                                                                                                                    |  |  |  |  |  |  |  |

| VDDFCtl.4 | -        |                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| VDDFCtl.3 | -        |                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| VDDFCtl.2 | VDDFTH.2 | VDD Fault Threshold.<br>Bit value(2:0) VDDFault voltage                                                                                                                                                      |  |  |  |  |  |  |  |

| VDDFCtl.1 | VDDFTH.1 | 000   2.3 (nominal default)     001   2.4     010   2.5                                                                                                                                                      |  |  |  |  |  |  |  |

| VDDFCtl.0 | VDDFTH.0 | 011 2.6   100 2.7   101 2.8   110 2.9   111 3.0                                                                                                                                                              |  |  |  |  |  |  |  |

\* Note: The  $V_{DD}$  Fault factory default can be set to any threshold as defined by bits VDDFTH(2:0). The 73S1215F has the capability to burn fuses at the factory to set the factory default to any of these voltages. Contact Teridian for further details.

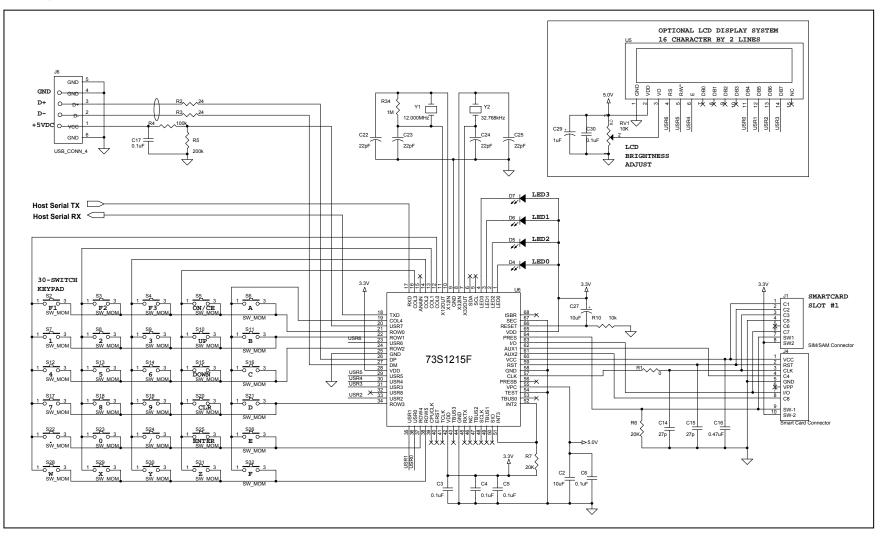

## 2 Typical Application Schematic

Figure 26: 73S1215F Typical Application Schematic

## 3.4 Oscillator Interface Requirements

| Symbol                                                                                                                                                                                 | Parameter                     | Condition           | Min     | Тур. | Max      | Unit |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|---------|------|----------|------|--|--|--|--|--|

| Low-Power Oscillator Requirements. No External Load Beside The Crystal And Capacitor Is Permitted On Xout32.                                                                           |                               |                     |         |      |          |      |  |  |  |  |  |

| Pxtal                                                                                                                                                                                  | Power In Crystal              |                     |         |      | 1        | Mw   |  |  |  |  |  |

| IIL                                                                                                                                                                                    | Input Leakage Current         | GND < Vin < VDD     | -5      |      | 5        | Ма   |  |  |  |  |  |

| High-Frequency Oscillator (Xin) Parameters. XIN Is Used As Input For External Clock For Test<br>Purposes Only. A Resistor Connecting X12in To X12out Is Required, Value = $1M\Omega$ . |                               |                     |         |      |          |      |  |  |  |  |  |

| VILX12IN                                                                                                                                                                               | Input Low Voltage –<br>X12IN  |                     | -0.3    |      | 0.3*VDD  | V    |  |  |  |  |  |

| VIHX12IN                                                                                                                                                                               | Input High Voltage – X12IN    |                     | 0.7*VDD |      | Vdd+.0.3 | V    |  |  |  |  |  |

| IILXTAL                                                                                                                                                                                | Input Current –<br>X12IN      | GND < Vin < Vdd     | -10     |      | 10       | Ма   |  |  |  |  |  |

| Fxtal                                                                                                                                                                                  | Crystal Resonant<br>Frequency | Fundamental<br>Mode | 6       |      | 12       | Mhz  |  |  |  |  |  |

## 3.5 DC Characteristics: Analog Input

| Symbol             | Parameter                      | Condition                   | Min | Тур. | Мах | Unit |

|--------------------|--------------------------------|-----------------------------|-----|------|-----|------|

| V <sub>THTOL</sub> | Voltage Threshold<br>Tolerance | Selected Threshold<br>Value | -3% |      | +3% | V    |

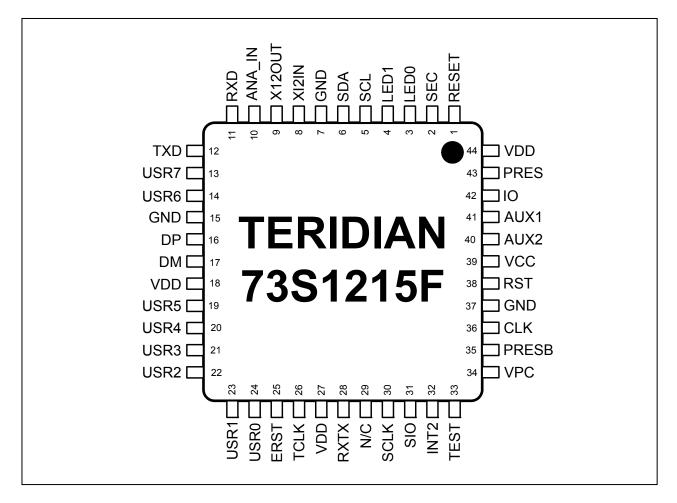

## 5.2 44-pin QFN Pinout

Figure 45: 73S1215F 44 QFN Pinout