Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

|                            |                                                                             |

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4221t-i-pt |

**Advance Information**

#### **REGISTER 4-1:** RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0 | R/W-1 | R-1 | R-1 | R/W-0 <sup>(2)</sup> | R/W-0 |

|-------|----------------------|-----|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | _   | RI    | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |     |       |     |     |                      | bit 0 |

bit 0

- bit 7 IPEN: Interrupt Priority Enable bit

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)

- **SBOREN:** BOR Software Enable bit<sup>(1)</sup> bit 6

If BOREN1:BOREN0 = 01:

- 1 = BOR is enabled

- 0 = BOR is disabled

If BOREN1:BOREN0 = 00, 10 or 11:

Bit is disabled and read as '0'.

- bit 5 Unimplemented: Read as '0'

- bit 4 RI: RESET Instruction Flag bit

- 1 = The RESET instruction was not executed (set by firmware only)

- 0 = The RESET instruction was executed causing a device Reset (must be set in software after a Brown-out Reset occurs)

- bit 3 TO: Watchdog Time-out Flag bit

- 1 = Set by power-up, CLRWDT instruction or SLEEP instruction

- 0 = A WDT time-out occurred

- PD: Power-Down Detection Flag bit bit 2

- 1 = Set by power-up or by the CLRWDT instruction

- 0 = Set by execution of the SLEEP instruction

- POR: Power-on Reset Status bit(2) bit 1

- 1 = A Power-on Reset has not occurred (set by firmware only)

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 **BOR:** Brown-out Reset Status bit

- 1 = A Brown-out Reset has not occurred (set by firmware only)

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'.

2: The actual Reset value of POR is determined by the type of device Reset. See the notes following this register and Section 4.6 "Reset State of Registers" for additional information.

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

- Note 1: It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

- 2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after POR).

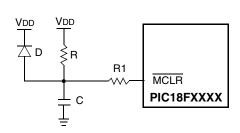

### 4.2 Master Clear (MCLR)

The MCLR pin provides a method for triggering an external Reset of the device. A Reset is generated by holding the pin low. These devices have a noise filter in the MCLR Reset path which detects and ignores small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

In PIC18F4321 family devices, the MCLR input can be disabled with the MCLRE configuration bit. When MCLR is disabled, the pin becomes a digital input. See Section 10.5 "PORTE, TRISE and LATE Registers" for more information.

#### 4.3 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip whenever VDD rises above a certain threshold. This allows the device to start in the initialized state when VDD is adequate for operation.

To take advantage of the POR circuitry, tie the  $\overline{MCLR}$  pin through a resistor (1 k $\Omega$  to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

POR events are captured by the POR bit (RCON<1>). The state of the bit is set to '0' whenever a POR occurs; it does not change for any other Reset event. POR is not reset to '1' by any hardware event. To capture multiple events, the user manually resets the bit to '1' in software following any POR.

# FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 \ge 1$  k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2221/2321/4221/4321) (CONTINUED)

|                      |                                                                                                    |                       |                | ,               |                    |                    | , ,                              |                    | Value on             | Deteile on       |

|----------------------|----------------------------------------------------------------------------------------------------|-----------------------|----------------|-----------------|--------------------|--------------------|----------------------------------|--------------------|----------------------|------------------|

| File Name            | Bit 7                                                                                              | Bit 6                 | Bit 5          | Bit 4           | Bit 3              | Bit 2              | Bit 1                            | Bit 0              | Value on<br>POR, BOR | Details on page: |

| SPBRGH               | EUSART Bau                                                                                         | ıd Rate Gener         | ator Register  | High Byte       |                    |                    |                                  |                    | 0000 0000            | 51, 210          |

| SPBRG                | EUSART Bau                                                                                         | ıd Rate Gener         | ator Register  | Low Byte        |                    |                    |                                  |                    | 0000 0000            | 51, 210          |

| RCREG                | EUSART Red                                                                                         | eive Register         |                |                 |                    |                    |                                  |                    | 0000 0000            | 51, 218          |

| TXREG                | EUSART Tra                                                                                         | nsmit Register        | •              |                 |                    |                    |                                  |                    | 0000 0000            | 51, 215          |

| TXSTA                | CSRC                                                                                               | TX9                   | TXEN           | SYNC            | SENDB              | BRGH               | TRMT                             | TX9D               | 0000 0010            | 51, 206          |

| RCSTA                | SPEN                                                                                               | RX9                   | SREN           | CREN            | ADDEN              | FERR               | OERR                             | RX9D               | 0000 000x            | 51, 207          |

| EEADR                | EEPROM Ad                                                                                          | dress Registe         | r              |                 |                    |                    |                                  |                    | 0000 0000            | 51, 74, 83       |

| EEDATA               | EEPROM Da                                                                                          | ta Register           |                |                 |                    |                    |                                  |                    | 0000 0000            | 51, 74, 83       |

| EECON2               | EEPROM Co                                                                                          | ntrol Register        | 2 (not a physi | cal register)   |                    |                    |                                  |                    | 0000 0000            | 51, 74, 83       |

| EECON1               | EEPGD                                                                                              | CFGS                  | _              | FREE            | WRERR              | WREN               | WR                               | RD                 | xx-0 x000            | 51, 75, 84       |

| IPR2                 | OSCFIP CMIP — EEIP BCLIP HLVDIP TMR3IP CCP2IP                                                      |                       |                |                 |                    |                    |                                  |                    | 11-1 1111            | 52, 101          |

| PIR2                 | OSCFIF CMIF — EEIF BCLIF HLVDIF TMR3IF CCP2IF                                                      |                       |                |                 |                    |                    |                                  |                    | 00-0 0000            | 52, 97           |

| PIE2                 | OSCFIE CMIE — EEIE BCLIE HLVDIE TMR3IE CCP2IE                                                      |                       |                |                 |                    |                    |                                  | 00-0 0000          | 52, 99               |                  |

| IPR1                 | PSPIP <sup>(2)</sup> ADIP RCIP TXIP SSPIP CCP1IP TMR2IP TMR1IP                                     |                       |                |                 |                    |                    |                                  | 1111 1111          | 52, 100              |                  |

| PIR1                 | PSPIF <sup>(2)</sup> ADIF RCIF TXIF SSPIF CCP1IF TMR2IF TMR1IF                                     |                       |                |                 |                    |                    | 0000 0000                        | 52, 96             |                      |                  |

| PIE1                 | PSPIE <sup>(2)</sup>                                                                               | ADIE                  | RCIE           | TXIE            | SSPIE              | CCP1IE             | TMR2IE                           | TMR1IE             | 0000 0000            | 52, 98           |

| OSCTUNE              | INTSRC                                                                                             | PLLEN <sup>(3)</sup>  | _              | TUN4            | TUN3               | TUN2               | TUN1                             | TUN0               | 00-0 0000            | 27, 52           |

| TRISE <sup>(2)</sup> | IBF                                                                                                | OBF                   | IBOV           | PSPMODE         | _                  | TRISE2             | TRISE1                           | TRISE0             | 0000 -111            | 52, 118          |

| TRISD <sup>(2)</sup> | PORTD Data                                                                                         | Direction Con         | trol Register  |                 |                    |                    |                                  |                    | 1111 1111            | 52, 114          |

| TRISC                | PORTC Data                                                                                         | Direction Con         | trol Register  |                 |                    |                    |                                  |                    | 1111 1111            | 52, 111          |

| TRISB                | PORTB Data                                                                                         | Direction Con         | trol Register  |                 |                    |                    |                                  |                    | 1111 1111            | 52, 108          |

| TRISA                | TRISA7 <sup>(5)</sup>                                                                              | TRISA6 <sup>(5)</sup> | PORTA Data     | Direction Con   | trol Register      |                    |                                  |                    | 1111 1111            | 52, 105          |

| LATE <sup>(2)</sup>  | _                                                                                                  | -                     | _              | -               | _                  |                    | Latch Register rite to Data Late | ch)                | xxx                  | 52, 117          |

| LATD <sup>(2)</sup>  | PORTD Data                                                                                         | Latch Registe         | er (Read and V | Vrite to Data L | atch)              |                    |                                  |                    | xxxx xxxx            | 52, 114          |

| LATC                 | PORTC Data                                                                                         | Latch Registe         | er (Read and V | Vrite to Data L | atch)              |                    |                                  |                    | xxxx xxxx            | 52, 111          |

| LATB                 | PORTB Data                                                                                         | Latch Registe         | r (Read and V  | Vrite to Data L | atch)              |                    |                                  |                    | xxxx xxxx            | 52, 108          |

| LATA                 | LATA7 <sup>(5)</sup> LATA6 <sup>(5)</sup> PORTA Data Latch Register (Read and Write to Data Latch) |                       |                |                 |                    |                    |                                  | xxxx xxxx          | 52, 105              |                  |

| PORTE                | _                                                                                                  | ı                     | _              | ı               | RE3 <sup>(4)</sup> | RE2 <sup>(2)</sup> | RE1 <sup>(2)</sup>               | RE0 <sup>(2)</sup> | xxxx                 | 52, 117          |

| PORTD <sup>(2)</sup> | RD7                                                                                                | RD6                   | RD5            | RD4             | RD3                | RD2                | RD1                              | RD0                | xxxx xxxx            | 52, 114          |

| PORTC                | RC7                                                                                                | RC6                   | RC5            | RC4             | RC3                | RC2                | RC1                              | RC0                | xxxx xxxx            | 52, 111          |

| PORTB                | RB7                                                                                                | RB6                   | RB5            | RB4             | RB3                | RB2                | RB1                              | RB0                | xxxx xxxx            | 52, 108          |

| PORTA                | RA7 <sup>(5)</sup>                                                                                 | RA6 <sup>(5)</sup>    | RA5            | RA4             | RA3                | RA2                | RA1                              | RA0                | xx0x 0000            | 52, 105          |

**Legend:** x = unknown, u = unchanged, -= unimplemented, q = value depends on condition

Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 configuration bits = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

- 2: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

- 3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

- 4: The RE3 bit is only available when Master Clear Reset is disabled (MCLRE configuration bit = 0); otherwise, RE3 reads as '0'. This bit is read-only.

- 5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

- **6:** Bit 7 and bit 6 are cleared by user software or by a POR.

#### **EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)**

| PROGRAM_MEMORY |        |              |   |                           |

|----------------|--------|--------------|---|---------------------------|

|                | BCF    | INTCON, GIE  | ; | disable interrupts        |

|                | MOVLW  | 55h          | ; | required sequence         |

|                | MOVWF  | EECON2       | ; | write 55H                 |

|                | MOVLW  | AAh          |   |                           |

|                | MOVWF  | EECON2       | ; | write AAH                 |

|                | BSF    | EECON1, WR   | ; | start program (CPU stall) |

|                | NOP    |              |   |                           |

|                | BSF    | INTCON, GIE  | ; | re-enable interrupts      |

|                | DECFSZ | COUNTER_HI   | ; | loop until done           |

|                | GOTO   | PROGRAM_LOOP |   |                           |

|                | BCF    | EECON1, WREN | ; | disable write to memory   |

|                |        |              |   |                           |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

# 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 23.0 "Special Features of the CPU" for more detail.

# 6.6 Flash Program Operation During Code Protection

See Section 23.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

TABLE 6-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Name    | Bit 7                                                 | Bit 6         | Bit 5                                                          | Bit 4          | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |  |

|---------|-------------------------------------------------------|---------------|----------------------------------------------------------------|----------------|----------|--------|--------|--------|----------------------------|--|

| TBLPTRU | _                                                     | _             | bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |                |          |        |        |        |                            |  |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |               |                                                                |                |          |        |        | 49     |                            |  |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)   |               |                                                                |                |          |        |        |        | 49                         |  |

| TABLAT  | Program M                                             | emory Table   | Latch                                                          |                |          |        |        |        | 49                         |  |

| INTCON  | GIE/GIEH                                              | PEIE/GIEL     | TMR0IE                                                         | INT0IE         | RBIE     | TMR0IF | INT0IF | RBIF   | 49                         |  |

| EECON2  | EEPROM C                                              | Control Regis | ster 2 (not                                                    | t a physical r | egister) |        |        |        | 51                         |  |

| EECON1  | EEPGD                                                 | CFGS          | _                                                              | FREE           | WRERR    | WREN   | WR     | RD     | 51                         |  |

| IPR2    | OSCFIP CMIP — EEIP BCLIP HLVDIP TMR3IP CCP2IP         |               |                                                                |                |          |        |        | 52     |                            |  |

| PIR2    | OSCFIF                                                | CMIF          | _                                                              | EEIF           | BCLIF    | HLVDIF | TMR3IF | CCP2IF | 52                         |  |

| PIE2    | OSCFIE                                                | CMIE          | _                                                              | EEIE           | BCLIE    | HLVDIE | TMR3IE | CCP2IE | 52                         |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

#### **REGISTER 7-1: EECON1: DATA EEPROM CONTROL REGISTER 1**

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|-------|-------|-------|-------|

| EEPGD | CFGS  | _   | FREE  | WRERR | WREN  | WR    | RD    |

| bit 7 |       |     |       |       |       |       | bit 0 |

bit 0

bit 7 **EEPGD:** Flash Program or Data EEPROM Memory Select bit

1 = Access Flash program memory

0 = Access data EEPROM memory

bit 6 CFGS: Flash Program/Data EEPROM or Configuration Select bit

1 = Access Configuration registers

0 = Access Flash program or data EEPROM memory

Unimplemented: Read as '0' bit 5

bit 4 FREE: Flash Row Erase Enable bit

> 1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by completion of erase operation)

0 = Perform write only

bit 3 WRERR: Flash Program/Data EEPROM Error Flag bit

> 1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation, or an improper write attempt)

0 = The write operation completed

Note: When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

WREN: Flash Program/Data EEPROM Write Enable bit bit 2

1 = Allows write cycles to Flash program/data EEPROM

0 = Inhibits write cycles to Flash program/data EEPROM

bit 1 WR: Write Control bit

> 1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

> 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)

0 = Does not initiate an EEPROM read

| Legend:           |                  |                                           |

|-------------------|------------------|-------------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared $x = Bit$ is unknown |

NOTES:

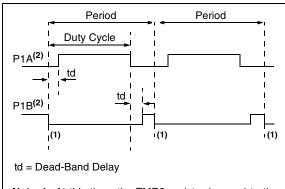

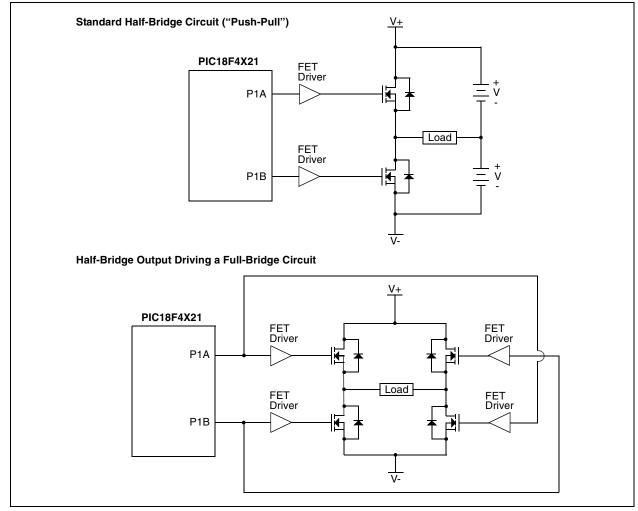

#### 16.4.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the P1A pin, while the complementary PWM output signal is output on the P1B pin (Figure 16-4). This mode can be used for half-bridge applications, as shown in Figure 16-5, or for full-bridge applications where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC6:PDC0, sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 16.4.6** "**Programmable Dead-Band Delay**" for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORTC<2> and PORTD<5> data latches, the TRISC<2> and TRISD<5> bits must be cleared to configure P1A and P1B as outputs.

## FIGURE 16-4: HALF-BRIDGE PWM OUTPUT

Note 1: At this time, the TMR2 register is equal to the PR2 register.

2: Output signals are shown as active-high.

FIGURE 16-5: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

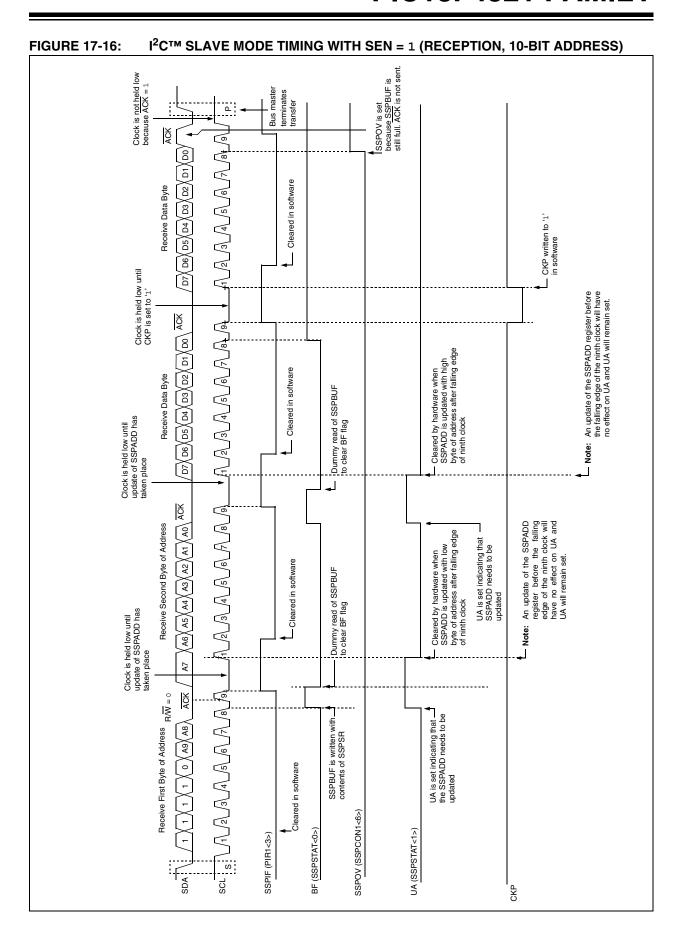

#### 17.4.3.3 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low  $(\overline{ACK})$ .

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPCON1<4>). See **Section 17.4.4** "Clock **Stretching**" for more detail.

#### 17.4.3.4 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 17.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit, CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-10).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

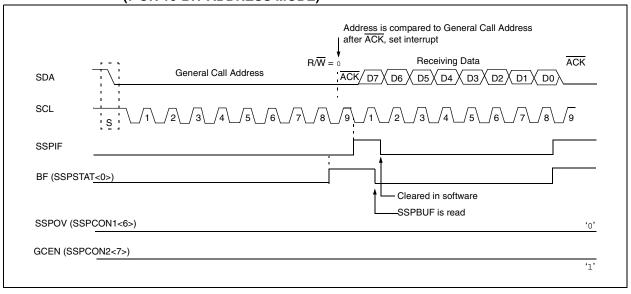

### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with  $R/\overline{W} = 0$ .

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPCON2<7> is set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit (SSPSTAT<1>) is set. If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-17).

FIGURE 17-17: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT ADDRESS MODE)

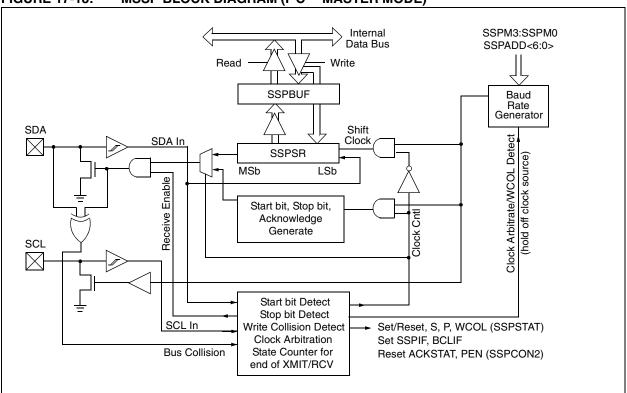

#### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- Assert a Start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

Start condition

Note:

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated Start

FIGURE 17-18: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MASTER MODE)

TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | l = 0, BRG            | <b>316</b> = 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000       | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     |            | _                           | _                     | _          | _                           | _                     | _              | _                           | _                     | _          | _                           |

| 1.2          | _                     | _          | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1201                  | -0.16      | 103                         |

| 2.4          | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2403                  | -0.16      | 51                          |

| 9.6          | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9615                  | -0.16      | 12                          |

| 19.2         | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6         | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | _                     | _          | _                           |

| 115.2        | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | -                     | _          | _                           |

|             |                       |            | s                           | YNC = 0, E            | BRGH = 0   | , BRG16 =                   | 0                     |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                 | 0.16       | 207                         | 300                   | -0.16      | 103                         | 300                   | -0.16      | 51                          |

| 1.2         | 1.202                 | 0.16       | 51                          | 1201                  | -0.16      | 25                          | 1201                  | -0.16      | 12                          |

| 2.4         | 2.404                 | 0.16       | 25                          | 2403                  | -0.16      | 12                          | _                     | _          | _                           |

| 9.6         | 8.929                 | -6.99      | 6                           | _                     | _          | _                           | _                     | _          | _                           |

| 19.2        | 20.833                | 8.51       | 2                           | _                     | _          | _                           | _                     | _          | _                           |

| 57.6        | 62.500 8.51 0         |            | _                           | _                     | _          | _                           | _                     | _          |                             |

| 115.2       | 62.500 -45.75 0       |            | _                           | _                     | _          | _                           | _                     | _          |                             |

|              |                       |            |                             |                       | SYNC       | = 0, BRGI                   | l = 1, BRG            | 1 <b>6 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     |            | _                           | _                     | _          | _                           | _                     | _              | _                           | _                     | _          | _                           |

| 1.2          | _                     |            | _                           | _                     | _          | _                           | _                     | _              | _                           | _                     | _          | _                           |

| 2.4          | _                     | _          | _                           | _                     | _          | _                           | 2.441                 | 1.73           | 255                         | 2403                  | -0.16      | 207                         |

| 9.6          | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16           | 64                          | 9615                  | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73           | 31                          | 19230                 | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36          | 10                          | 55555                 | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51           | 4                           |                       | _          | _                           |

|              |                       |            | s                           | YNC = 0, E            | BRGH = 1   | , BRG16 =                   | 0                     |            |                             |  |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc                  | = 4.000    | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | _                     | _          | _                           |                       | _          | _                           | 300                   | -0.16      | 207                         |  |

| 1.2          | 1.202                 | 0.16       | 207                         | 1201                  | -0.16      | 103                         | 1201                  | -0.16      | 51                          |  |

| 2.4          | 2.404                 | 0.16       | 103                         | 2403                  | -0.16      | 51                          | 2403                  | -0.16      | 25                          |  |

| 9.6          | 9.615                 | 0.16       | 25                          | 9615                  | -0.16      | 12                          | _                     | _          | _                           |  |

| 19.2         | 19.231                | 0.16       | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |

| 57.6         | 62.500 8.51 3         |            | _                           | _                     | _          | _                           | _                     | _          |                             |  |

| 115.2        | 125.000               | 8.51       | 1                           | _                     | _          | _                           | _                     | _          | _                           |  |

#### REGISTER 23-10: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | _   | _   | _   | EBTR1 | EBTR0 |

| hit 7 |     |     |     |     |     |       | hit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 EBTR1: Table Read Protection bit

1 = Block 1<sup>(1)</sup> not protected from table reads executed in other blocks  $0 = Block 1^{(1)}$  protected from table reads executed in other blocks

bit 0 EBTR0: Table Read Protection bit

1 = Block  $0^{(1)}$  not protected from table reads executed in other blocks 0 = Block  $0^{(1)}$  protected from table reads executed in other blocks

Note 1: See Figure 23-5 for variable block boundaries.

### Legend:

R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

#### REGISTER 23-11: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| _     | EBTRB | _   | _   | _   | _   |     | _     |

| bit 7 |       |     | •   | •   | •   | •   | bit 0 |

bit 7 Unimplemented: Read as '0'

bit 6 EBTRB: Boot Block Table Read Protection bit

1 = Boot block<sup>(1)</sup> not protected from table reads executed in other blocks  $0 = \text{Boot block}^{(1)}$  protected from table reads executed in other blocks

bit 5-0 **Unimplemented:** Read as '0'

Note 1: See Figure 23-5 for variable block boundaries.

#### Legend:

$R = Readable \ bit$   $C = Clearable \ bit$   $U = Unimplemented \ bit, read as '0'$  $-n = Value \ when \ device is \ unprogrammed$  $<math>u = Unchanged \ from \ programmed \ state$

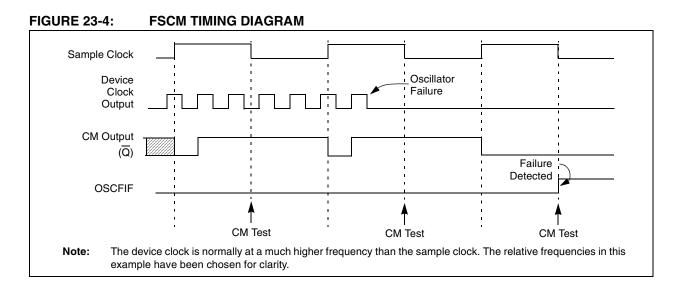

### 23.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTOSC source.

#### 23.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR, or wake from Sleep, will also prevent the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in Section 23.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

| IORLW             | Inclusive OR Literal with W                                                           |                   |      |      |  |  |

|-------------------|---------------------------------------------------------------------------------------|-------------------|------|------|--|--|

| Syntax:           | IORLW k                                                                               |                   |      |      |  |  |

| Operands:         | $0 \le k \le 25$                                                                      | $0 \le k \le 255$ |      |      |  |  |

| Operation:        | (W) .OR. $k \rightarrow W$                                                            |                   |      |      |  |  |

| Status Affected:  | N, Z                                                                                  |                   |      |      |  |  |

| Encoding:         | 0000                                                                                  | 1001              | kkkk | kkkk |  |  |

| Description:      | The contents of W are ORed with the eight-bit literal 'k'. The result is placed in W. |                   |      |      |  |  |

| Words:            | 1                                                                                     |                   |      |      |  |  |

| Cycles:           | 1                                                                                     |                   |      |      |  |  |

| Q Cycle Activity: |                                                                                       |                   |      |      |  |  |

| Q1                | Q2                                                                                    | Q3                | 3    | Q4   |  |  |

Example: IORLW 35h

Read

literal 'k'

Process

Data

Write to W

Before Instruction

Decode

W = 9Ah

After Instruction

W = BFh

| IORV    | VF            | Inclusive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OR W with          | f        |  |  |

|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--|--|

| Synta   | ix:           | IORWF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | {,d {,a}}          |          |  |  |

| Opera   | ands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |          |  |  |

| Opera   | ation:        | (W) .OR. (f)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\rightarrow$ dest |          |  |  |

| Statu   | s Affected:   | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    |          |  |  |

| Enco    | ding:         | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00da ff            | ff ffff  |  |  |

| Desc    | ription:      | Inclusive OR W with register 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default).  If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default).  If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See  Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                    |          |  |  |

| Word    | s:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |  |  |

| Cycles: |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |  |  |

| Q Cy    | cle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |  |  |

|         | Q1            | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Q3                 | Q4       |  |  |

|         | Decode        | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Process            | Write to |  |  |

register 'f' Data destination

IORWF RESULT, 0, 1

Before Instruction

Example:

RESULT = 13hW = 91h

After Instruction

$\begin{array}{ccc} \mathsf{RESULT} &=& 13\mathsf{h} \\ \mathsf{W} &=& 93\mathsf{h} \end{array}$

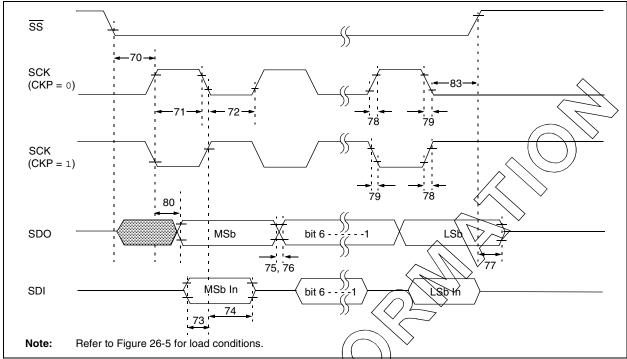

FIGURE 26-15: EXAMPLE SPI™ SLAVE MODE TIMING (CKE = 0)

TABLE 26-16: EXAMPLE SPI™ MODE REQUIREMENTS (SLAVE MODE TIMING, CKE = 0)

| Param<br>No. | Symbol                | Characteristic                              |                      | Min           | Max | Units | Conditions |

|--------------|-----------------------|---------------------------------------------|----------------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | SS ↓ to SCK ↓ or SCK ↑ Input                |                      | Tcy           | 1   | ns    |            |

| 71           | TscH                  | SCK Input High Time                         | Continuous           | 1.25 Tcy + 30 | 1   | ns    |            |

| 71A          |                       | (Slave mode)                                | Single Byte          | 40            | -   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                          | Continuous           | 1.25 Tcy + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                                | Single Byte          | 40            | _   | ns    | (Note 1)   |

| 73           | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SCK Edge    |                      | 100           |     | ns    |            |

| 73A          | Tb2b                  | Last Clock Edge of Byte 1 to the First Cloc | ck Edge of Byte 2    | 1.5 Tcy + 40  | _   | ns    | (Note 2)   |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge     |                      | 100           | _   | ns    |            |

| 75           | TdoP <sub></sub>      | SDQ Data Output Rise Time                   | PIC18FXXXX           | _             | 25  | ns    |            |

|              |                       |                                             | PIC18 <b>LF</b> XXXX |               | 45  | ns    | VDD = 2.0V |

| 76 <         | TdoF                  | SDO Data Output Fall Time                   |                      |               | 25  | ns    |            |

| 77           | TssH2doZ              | SS ↑ to SDO Output High-Impedance           |                      | 10            | 50  | ns    |            |

| 78           | TseR                  | SCK Output Rise Time (Master mode)          | PIC18FXXXX           | _             | 25  | ns    |            |

|              | <b>/</b>              |                                             | PIC18 <b>LF</b> XXXX |               | 45  | ns    | VDD = 2.0V |

| 79           | TscF                  | SCK Output Fall Time (Master mode)          |                      |               | 25  | ns    |            |

| 80           | TscH2doV,             | SDO Data Output Valid after SCK Edge        | PIC18FXXXX           | _             | 50  | ns    |            |

|              | TscL2doV              |                                             | PIC18 <b>LF</b> XXXX |               | 100 | ns    | VDD = 2.0V |

| 83           | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                         |                      | 1.5 Tcy + 40  | _   | ns    |            |

Note 1: Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

| PUSH302                                         |

|-------------------------------------------------|

| RCALL                                           |

| RESET                                           |

| RETFIE                                          |

| RETLW                                           |

| RETURN                                          |

| RLCF 305                                        |

| RLNCF                                           |

| RRCF                                            |

| RRNCF                                           |

| SETF                                            |

| SETF (Indexed Literal Offset Mode)321           |

| SLEEP                                           |

| Standard Instructions                           |

| SUBFWB                                          |

| SUBLW                                           |

|                                                 |

| SUBWF                                           |

| SWAPF                                           |

|                                                 |

| TBLRD                                           |

| TBLWT                                           |

| TSTFSZ                                          |

| XORLW                                           |

| XORWF                                           |

| INTCON Registers                                |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |

| Internal Oscillator Block                       |

| Adjustment26                                    |

| INTIO Modes26                                   |

| INTOSC Frequency Drift27                        |

| INTOSC Output Frequency26                       |

| OSCTUNE Register26                              |

| PLL in INTOSC Modes27                           |

| Internal RC Oscillator                          |

| Use with WDT263                                 |

| Internet Address389                             |

| Interrupt Sources253                            |

| A/D Conversion Complete231                      |

| Capture Complete (CCP)141                       |

| Compare Complete (CCP)142                       |

| Interrupt-on-Change (RB7:RB4)108                |

| INTn Pin103                                     |

| PORTB, Interrupt-on-Change103                   |

| TMR0103                                         |

| TMR0 Overflow125                                |

| TMR1 Overflow127                                |

| TMR2-to-PR2 Match (PWM)144, 149                 |

| TMR3 Overflow135, 137                           |

| Interrupts91                                    |

| Interrupts, Flag Bits                           |

| Interrupt-on-Change (RB7:RB4) Flag              |

| (RBIF Bit)108                                   |

| INTOSC, INTRC. See Internal Oscillator Block.   |

| IORLW296                                        |

| IORWF296                                        |

| IPR Registers100                                |

| L<br>L                                          |

| _                                               |

| LFSR                                            |

| Low-Voltage ICSP Programming. See Single-Supply |

| ICSP Programming.                               |

| M                                                        |        |

|----------------------------------------------------------|--------|

| Master Clear (MCLR)                                      | 43     |

| Master Synchronous Serial Port (MSSP). See MSSP.         |        |

| Memory Organization                                      |        |

| Data Memory                                              |        |

| Program Memory                                           |        |

| Memory Programming Requirements                          |        |

| Microchip Internet Web Site                              |        |

| Migration from Baseline to Enhanced Devices              |        |

| Migration from High-End to Enhanced Devices              |        |

| Migration from Mid-Range to Enhanced Devices MOVF        |        |

| MOVF                                                     |        |

| MOVLB                                                    |        |

| MOVLW                                                    |        |

| MOVSF                                                    |        |

| MOVSS                                                    |        |

| MOVWF                                                    |        |

| MPLAB ASM30 Assembler, Linker, Librarian                 | 324    |

| MPLAB ICD 2 In-Circuit Debugger                          | 325    |

| MPLAB ICE 2000 High-Performance Universal                |        |

| In-Circuit Emulator                                      | 325    |

| MPLAB ICE 4000 High-Performance Universal                |        |

| In-Circuit Emulator                                      | 325    |

| MPLAB Integrated Development                             |        |

| Environment Software                                     |        |

| MPLAB PM3 Device Programmer                              |        |

| MPLINK Object Linker/MPLIB Object Librarian              | 324    |

| MSSP ACK Pulse 17                                        | '5 177 |

| Control Registers (general)                              |        |

| I <sup>2</sup> C Mode. <i>See</i> I <sup>2</sup> C Mode. | 101    |

| Module Overview                                          | 161    |

| SPI Master/Slave Connection                              |        |

| SPI Mode. See SPI Mode.                                  |        |

| SSPBUF Register                                          | 166    |

| SSPSR Register                                           | 166    |

| MULLW                                                    | 300    |

| MULWF                                                    | 300    |

| N                                                        |        |

| NEGF                                                     | 001    |

|                                                          |        |

| NOP                                                      | 301    |

| 0                                                        |        |

| Oscillator Configuration                                 | 23     |

| EC                                                       |        |

| ECIO                                                     |        |

| HS                                                       | 23     |

| HSPLL                                                    | 23     |

| Internal Oscillator Block                                | 26     |

| INTIO1                                                   | 23     |

| INTIO2                                                   | 23     |

| LP                                                       |        |

| RC                                                       |        |

| RCIO                                                     |        |

| XT                                                       |        |

| Oscillator Selection                                     |        |

| Oscillator Start-up Timer (OST)                          |        |

| Oscillator Switching                                     |        |

| Oscillator Transitions                                   |        |

| Oscillator, Timer3                                       |        |

| Ooomatol, 1111010                                        | 100    |

| P                                    |        | POR. See Power-on Reset.                |     |

|--------------------------------------|--------|-----------------------------------------|-----|

| Packaging Information                | 367    | PORTA                                   |     |

| Details                              |        | Associated Registers                    |     |

| Marking                              |        | LATA Register                           |     |

| Parallel Slave Port (PSP)            |        | PORTA Register                          |     |

| Associated Registers                 |        | TRISA Register                          | 105 |

| CS (Chip Select)                     |        | PORTB                                   |     |

| PORTD                                |        | Associated Registers                    |     |

| RD (Read Input)                      |        | LATB Register                           |     |

| Select (PSPMODE Bit)                 |        | PORTB Register                          | 108 |

| WR (Write Input)                     |        | RB7:RB4 Interrupt-on-Change Flag        |     |

| PICSTART Plus Development Programmer |        | (RBIF Bit)                              |     |

| PIE Registers                        |        | TRISB Register                          | 108 |

| Pin Functions                        |        | PORTC                                   |     |

| MCLR/VPP/RE3                         | 12. 16 | Associated Registers                    |     |

| NC/ICCK/ICPGC                        | ,      | LATC Register                           |     |

| NC/ICDT/ICPGD                        |        | PORTC Register                          |     |

| NC/ICPORTS                           |        | RC3/SCK/SCL Pin                         |     |

| NC/ICRST/ICVPP                       |        | TRISC Register                          | 111 |

| OSC1/CLKI/RA7                        |        | PORTD                                   |     |

| OSC2/CLKO/RA6                        |        | Associated Registers                    |     |

| RA0/AN0                              |        | LATD Register                           |     |

| RA1/AN1                              | •      | Parallel Slave Port (PSP) Function      |     |

| RA2/AN2/VREF-/CVREF                  |        | PORTD Register                          |     |

| RA3/AN3/VREF+                        |        | TRISD Register                          | 114 |

| RA4/T0CKI/C1OUT                      | ,      | PORTE                                   |     |

| RA5/AN4/SS/HLVDIN/C2OUT              | ·      | Associated Registers                    |     |

| RB0/INT0/FLT0/AN12                   |        | LATE Register                           |     |

| RB1/INT1/AN10                        |        | PORTE Register                          |     |

| RB2/INT2/AN8                         | 14, 18 | PSP Mode Select (PSPMODE Bit)           |     |

| RB3/AN9/CCP2                         | 14, 18 | TRISE Register                          |     |

| RB4/KBI0/AN11                        | ·      | Power-Managed Modes                     |     |

| RB5/KBI1/PGM                         | 14, 18 | and A/D Operation                       |     |

| RB6/KBI2/PGC                         |        | and EUSART Operation                    |     |

| RB7/KBI3/PGD                         | ·      | and PWM Operation                       |     |

| RC0/T10S0/T13CKI                     | 15, 19 | and SPI Operation                       |     |

| RC1/T1OSI/CCP2                       |        | Clock Sources                           |     |

| RC2/CCP1                             |        | Clock Transitions and Status Indicators |     |

| RC2/CCP1/P1A                         | 19     | Effects on Clock Sources                |     |

| RC3/SCK/SCL                          | 15, 19 | Entering                                |     |

| RC4/SDI/SDA                          | 15, 19 | Exiting Idle and Sleep Modes            |     |

| RC5/SDO                              | 15, 19 | By Interrupt                            |     |

| RC6/TX/CK                            | 15, 19 | By Reset                                |     |

| RC7/RX/DT                            | 15, 19 | By WDT Time-out                         |     |

| RD0/PSP0                             | 20     | Without an Oscillator Start-up Delay    |     |

| RD1/PSP1                             | 20     | Idle Modes                              |     |

| RD2/PSP2                             | 20     | PRI_IDLE                                |     |

| RD3/PSP3                             | 20     | RC_IDLE                                 |     |

| RD4/PSP4                             | 20     | SEC_IDLE                                |     |

| RD5/PSP5/P1B                         | 20     | Multiple Sleep Commands                 |     |

| RD6/PSP6/P1C                         | 20     | Run Modes                               |     |

| RD7/ <u>PS</u> P7/P1D                | 20     | PRI_RUN                                 |     |

| RE0/RD/AN5                           | 21     | RC_RUN                                  |     |

| RE1/WR/AN6                           |        | SEC_RUN                                 |     |

| RE2/CS/AN7                           | 21     | Sleep Mode                              |     |

| VDD                                  | 15, 21 | Summary (table)                         |     |

| Vss                                  | 15, 21 | Power-on Reset (POR)                    |     |

| Pinout I/O Descriptions              |        | Power-up Timer (PWRT)                   |     |