Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | 1377                                                           |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 228                                                            |

| Number of Gates                | 10000                                                          |

| Voltage - Supply               | 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 313-BBGA                                                       |

| Supplier Device Package        | 313-PBGA (35x35)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a14100a-1bg313c |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ACT 3 Family Overview

| Device and Speed<br>Grade | t <sub>CKHS</sub> (ns) | t <sub>TRACE</sub> (ns) | t <sub>INSU</sub> (ns) | Total (ns) | MHz |

|---------------------------|------------------------|-------------------------|------------------------|------------|-----|

| A1425A -3                 | 7.5                    | 1.0                     | 1.8                    | 10.3       | 97  |

| A1460A -3                 | 9.0                    | 1.0                     | 1.3                    | 11.3       | 88  |

| A1425A -2                 | 7.5                    | 1.0                     | 2.0                    | 10.5       | 95  |

| A1460A -2                 | 9.0                    | 1.0                     | 1.5                    | 11.5       | 87  |

| A1425A -1                 | 9.0                    | 1.0                     | 2.3                    | 12.3       | 81  |

| A1460A -1                 | 10.0                   | 1.0                     | 1.8                    | 12.8       | 78  |

| A1425A STD                | 10.0                   | 1.0                     | 2.7                    | 13.7       | 73  |

| A1460A STD                | 11.5                   | 1.0                     | 2.0                    | 14.5       | 69  |

#### Table 1-1 • Chip-to-Chip Performance (worst-case commercial)

Note: The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

**Detailed Specifications**

# **Logic Modules**

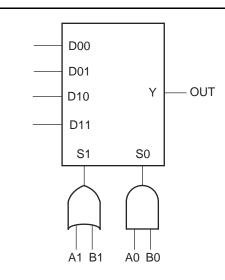

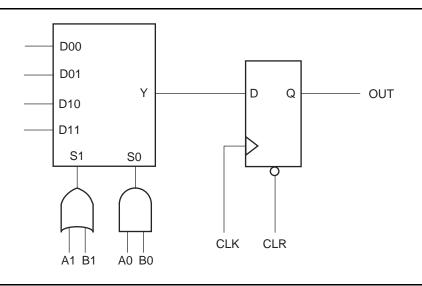

ACT 3 logic modules are enhanced versions of the 1200XL family logic modules. As in the 1200XL family, there are two types of modules: C-modules and S-modules (Figure 2-2 and Figure 2-3). The C-module is functionally equivalent to the 1200XL C-module and implements high fanin combinatorial macros, such as 5-input AND, 5-input OR, and so on. It is available for use as the CM8 hard macro. The S-module is designed to implement high-speed sequential functions within a single module.

*Figure 2-3* • S-Module Diagram

S-modules consist of a full C-module driving a flip-flop, which allows an additional level of logic to be implemented without additional propagation delay. It is available for use as the DFM8A/B and DLM8A/B hard macros. C-modules and S-modules are arranged in pairs called module-pairs. Module-pairs are arranged in alternating patterns and make up the bulk of the array. This arrangement allows the placement software to support two-module macros of four types (CC, CS, SC, and SS). The C-module implements the following function:

EQ 1

where: S0 = A0 \* B0 and S1 = A1 + B1

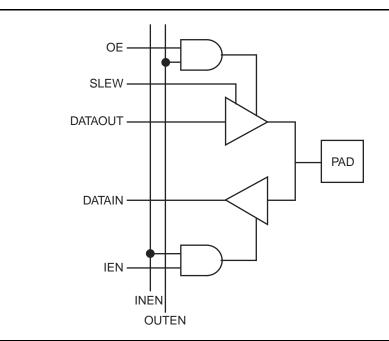

The I/O module output Y is used to bring Pad signals into the array or to feed the output register back into the array. This allows the output register to be used in high-speed state machine applications. Side I/O modules have a dedicated output segment for Y extending into the routing channels above and below (similar to logic modules). Top/Bottom I/O modules have no dedicated output segment. Signals coming into the chip from the top or bottom are routed using F-fuses and LVTs (F-fuses and LVTs are explained in detail in the routing section).

# I/O Pad Drivers

All pad drivers are capable of being tristate. Each buffer connects to an associated I/O module with four signals: OE (Output Enable), IE (Input Enable), DataOut, and DataIn. Certain special signals used only during programming and test also connect to the pad drivers: OUTEN (global output enable), INEN (global input enable), and SLEW (individual slew selection). See Figure 2-5.

*Figure 2-5* • Function Diagram for I/O Pad Driver

# Special I/Os

The special I/Os are of two types: temporary and permanent. Temporary special I/Os are used during programming and testing. They function as normal I/Os when the MODE pin is inactive. Permanent special I/Os are user programmed as either normal I/Os or special I/Os. Their function does not change once the device has been programmed. The permanent special I/Os consist of the array clock input buffers (CLKA and CLKB), the hard-wired array clock input buffer (HCLK), the hard-wired I/O clock input buffer (IOCLK), and the hard-wired I/O register preset/clear input buffer (IOPCL). Their function is determined by the I/O macros selected.

# **Clock Networks**

The ACT 3 architecture contains four clock networks: two high-performance dedicated clock networks and two general purpose routed networks. The high-performance networks function up to 200 MHz, while the general purpose routed networks function up to 150 MHz.

# **5 V Operating Conditions**

| Symbol           | Parameter                            | Limits            | Units |

|------------------|--------------------------------------|-------------------|-------|

| VCC              | DC supply voltage                    | -0.5 to +7.0      | V     |

| VI               | Input voltage                        | -0.5 to VCC + 0.5 | V     |

| VO               | Output voltage                       | -0.5 to VCC + 0.5 | V     |

| IIO              | I/O source sink current <sup>2</sup> | ±20               | mA    |

| T <sub>STG</sub> | Storage temperature                  | -65 to +150       | °C    |

Table 2-2 • Absolute Maximum Ratings<sup>1</sup>, Free Air Temperature Range

Notes:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the recommended operating conditions.

2. Device inputs are normally high impedance and draw extremely low current. However, when input voltage is greater than VCC + 0.5 V for less than GND –0.5 V, the internal protection diodes will forward bias and can draw excessive current.

Table 2-3 • Recommended Operating Conditions

| Parameter                  | Commercial | Industrial | Military    | Units |

|----------------------------|------------|------------|-------------|-------|

| Temperature range*         | 0 to +70   | -40 to +85 | -55 to +125 | °C    |

| 5 V power supply tolerance | ±5         | ±10        | ±10         | %VCC  |

Note: \*Ambient temperature  $(T_A)$  is used for commercial and industrial; case temperature  $(T_C)$  is used for military.

|                    |                                |                                 | Со       | nmercial    | In   | dustrial  | Ν    | Ailitary  |          |

|--------------------|--------------------------------|---------------------------------|----------|-------------|------|-----------|------|-----------|----------|

| Symbol             | Parameter                      | Test Condition                  | Min.     | Max.        | Min. | Max.      | Min. | Max.      | Units    |

| VOH <sup>1,2</sup> | High level output              | IOH = -4 mA (CMOS)              | -        | -           | 3.7  | -         | 3.7  | -         | V        |

|                    |                                | IOH = –6 mA (CMOS)              | 3.84     |             |      |           |      |           | V        |

|                    |                                | IOH = –10 mA (TTL) <sup>3</sup> | 2.40     |             |      |           |      |           | V        |

| VOL <sup>1,2</sup> | Low level output               | IOL = +6 mA (CMOS)              |          | 0.33        |      | 0.4       |      | 0.4       | V        |

|                    |                                | IOL = +12 mA (TTL) <sup>3</sup> |          | 0.50        |      |           |      |           |          |

| VIH                | High level input               | TTL inputs                      | 2.0      | VCC + 0.3   | 2.0  | VCC + 0.3 | 2.0  | VCC + 0.3 | V        |

| VIL                | Low level input                | TTL inputs                      | -0.3     | 0.8         | -0.3 | 0.8       | -0.3 | 0.8       | V        |

| IIN                | Input leakage                  | VI = VCC or GND                 | -10      | +10         | -10  | +10       | -10  | +10       | μA       |

| IOZ                | 3-state output leakage         | VO = VCC or GND                 | -10      | +10         | -10  | +10       | -10  | +10       | μA       |

| C <sub>IO</sub>    | I/O capacitance <sup>3,4</sup> |                                 |          | 10          |      | 10        |      | 10        | pF       |

| ICC(S)             | Standby VCC supply cu          | rrent (typical = 0.7 mA)        |          | 2           |      | 10        |      | 20        | mA       |

| ICC(D)             | Dynamic VCC supply c           | urrent. See the Power Dis       | ssipatio | on section. | •    |           |      | •         | <b>.</b> |

#### Table 2-4 • Electrical Specifications

Notes:

1. Microsemi devices can drive and receive either CMOS or TTL signal levels. No assignment of I/Os as TTL or CMOS is required.

2. Tested one output at a time, VCC = minimum.

3. Not tested; for information only.

4. VOUT = 0 V, f = 1 MHz

5. Typical standby current = 0.7 mA. All outputs unloaded. All inputs = VCC or GND.

Accelerator Series FPGAs – ACT 3 Family

Equivalent capacitance is calculated by measuring ICC active at a specified frequency and voltage for each circuit component of interest. Measurements have been made over a range of frequencies at a fixed value of VCC. Equivalent capacitance is frequency independent so that the results may be used over a wide range of operating conditions. Equivalent capacitance values are shown in Figure 2-10.

| Item                                                 | CEQ Value |

|------------------------------------------------------|-----------|

| Modules (C <sub>EQM</sub> )                          | 6.7       |

| Input Buffers (C <sub>EQI</sub> )                    | 7.2       |

| Output Buffers (C <sub>EQO</sub> )                   | 10.4      |

| Routed Array Clock Buffer Loads (C <sub>EQCR</sub> ) | 1.6       |

| Dedicated Clock Buffer Loads (C <sub>EQCD</sub> )    | 0.7       |

| I/O Clock Buffer Loads (C <sub>EQCI)</sub>           | 0.9       |

To calculate the active power dissipated from the complete design, the switching frequency of each part of the logic must be known. EQ 5 shows a piece-wise linear summation over all components.

Power =VCC<sup>2</sup> \* [(m \* C<sub>EQM</sub> \* f<sub>m</sub>)<sub>modules</sub> + (n \* C<sub>EQI</sub> \* f<sub>n</sub>) inputs

+ ( $p * (C_{EQO} + C_L) * f_p$ )outputs

+ 0.5 \* (q1 \* C<sub>EQCR</sub> \* f<sub>q1</sub>)<sub>routed\_Clk1</sub> + (r1 \* fq1)<sub>routed\_Clk1</sub>

+ 0.5 \* (q2 \* C<sub>EQCR</sub> \* fq2)<sub>routed\_Clk2</sub>

+  $(r_2 * f_{q2})_{routed\_Clk2}$  + 0.5 \*  $(s_1 * C_{EQCD} * f_{s1})_{dedicated\_Clk}$

+ (s<sub>2</sub> \* C<sub>EQCI</sub> \* f<sub>s2</sub>)<sub>IO\_CIk</sub>]

Where: m = Number of logic modules switching at fm n = Number of input buffers switching at fn p = Number of output buffers switching at  $f_p$ q1 = Number of clock loads on the first routed array clock q2 = Number of clock loads on the second routed array clock  $r_1$  = Fixed capacitance due to first routed array clock r<sub>2</sub> = Fixed capacitance due to second routed array clock s<sub>1</sub> = Fixed number of clock loads on the dedicated array clock s2 = Fixed number of clock loads on the dedicated I/O clock C<sub>FOM</sub> = Equivalent capacitance of logic modules in pF C<sub>EQI</sub> = Equivalent capacitance of input buffers in pF C<sub>EOO</sub> = Equivalent capacitance of output buffers in pF C<sub>EOCR</sub> = Equivalent capacitance of routed array clock in pF C<sub>EQCD</sub> = Equivalent capacitance of dedicated array clock in pF C<sub>EOCI</sub> = Equivalent capacitance of dedicated I/O clock in pF C<sub>1</sub> = Output lead capacitance in pF f<sub>m</sub> = Average logic module switching rate in MHz fn = Average input buffer switching rate in MHz f<sub>p</sub> = Average output buffer switching rate in MHz  $f_{q1}$  = Average first routed array clock rate in MHz  $f_{\alpha 2}$  = Average second routed array clock rate in MHz f<sub>s1</sub> = Average dedicated array clock rate in MHz f<sub>s2</sub> = Average dedicated I/O clock rate in MHz

EQ 5

# A1425A, A14V25A Timing Characteristics (continued)

| Table 2-25 • A1425A. | A14V25A Worst-Case Comme | ercial Conditions, VCC | = 4.75 V. T <sub>1</sub> = 70°C |

|----------------------|--------------------------|------------------------|---------------------------------|

| TUDIO E EO TATEON,   |                          |                        | - + v, v                        |

| Dedicate             | d (hardwired) I/O Clock Network                  | -3 Sp      | beed <sup>1</sup> | -2 Sp      | beed <sup>1</sup> | -1 Speed   |            | Std. Speed |            | 3.3 V Speed <sup>1</sup> |            | Units |

|----------------------|--------------------------------------------------|------------|-------------------|------------|-------------------|------------|------------|------------|------------|--------------------------|------------|-------|

| Paramete             | er/Description                                   | Min.       | Max.              | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.                     | Max.       |       |

| t <sub>IOCKH</sub>   | Input Low to High (pad to I/O module input)      |            | 2.0               |            | 2.3               |            | 2.6        |            | 3.0        |                          | 3.5        | ns    |

| t <sub>IOPWH</sub>   | Minimum Pulse Width High                         | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IPOWL</sub>   | Minimum Pulse Width Low                          | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IOSAPW</sub>  | Minimum Asynchronous Pulse Width                 | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IOCKSW</sub>  | Maximum Skew                                     |            | 0.4               |            | 0.4               |            | 0.4        |            | 0.4        |                          | 0.4        | ns    |

| t <sub>IOP</sub>     | Minimum Period                                   | 4.0        |                   | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0                     |            | ns    |

| f <sub>IOMAX</sub>   | Maximum Frequency                                |            | 250               |            | 200               |            | 150        |            | 125        |                          | 100        | MHz   |

| Dedicated            | d (hardwired) Array Clock                        |            |                   | •          |                   |            |            | •          | -          |                          |            |       |

| tнскн                | Input Low to High (pad to S-module input)        |            | 3.0               |            | 3.4               |            | 3.9        |            | 4.5        |                          | 5.5        | ns    |

| t <sub>HCKL</sub>    | Input High to Low (pad to S-module input)        |            | 3.0               |            | 3.4               |            | 3.9        |            | 4.5        |                          | 5.5        | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width High                         | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width Low                          | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>HCKSW</sub>   | Delta High to Low, Low Slew                      |            | 0.3               |            | 0.3               |            | 0.3        |            | 0.3        |                          | 0.3        | ns    |

| t <sub>HP</sub>      | Minimum Period                                   | 4.0        |                   | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0                     |            | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                |            | 250               |            | 200               |            | 150        |            | 125        |                          | 100        | MHz   |

| Routed A             | rray Clock Networks                              |            |                   | •          |                   |            |            | •          |            |                          |            |       |

| t <sub>RCKH</sub>    | Input Low to High (FO = 64)                      |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                          | 9.0        | ns    |

| t <sub>RCKL</sub>    | Input High to Low (FO = 64)                      |            | 4.0               |            | 4.5               |            | 5.1        |            | 6.0        |                          | 9.0        | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width High (FO = 64)                  | 3.3        |                   | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5                      |            | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width Low (FO = 64)                   | 3.3        |                   | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5                      |            | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew (FO = 128)                          |            | 0.7               |            | 0.8               |            | 0.9        |            | 1.0        |                          | 1.0        | ns    |

| t <sub>RP</sub>      | Minimum Period (FO = 64)                         | 6.8        |                   | 8.0        |                   | 8.7        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>RMAX</sub>    | Maximum Frequency (FO = 64)                      |            | 150               |            | 125               |            | 115        |            | 100        |                          | 75         | MHz   |

| Clock-to-            | Clock Skews                                      |            |                   |            |                   |            |            |            |            |                          |            |       |

| t <sub>IOHCKSW</sub> | I/O Clock to H-Clock Skew                        | 0.0        | 1.7               | 0.0        | 1.8               | 0.0        | 2.0        | 0.0        | 2.2        | 0.0                      | 3.0        | ns    |

| t <sub>IORCKSW</sub> | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 80) | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 3.0<br>3.0 | ns    |

| t <sub>HRCKSW</sub>  | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 80)   | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 1.0<br>3.0 | ns    |

Notes:

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

**Detailed Specifications**

# A1440A, A14V40A Timing Characteristics (continued)

Table 2-28 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Moo            | dule – TTL Output Timing <sup>1</sup>  | -3 S | beed <sup>2</sup> | -2 Sp | beed <sup>2</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min. | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               | 1     |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 5.0               |       | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 8.0               |       | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 4.0               |       | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 8.5               |       | 8.5               |      | 9.5  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 11.3              |       | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.02              |       | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Moo            | dule – CMOS Output Timing <sup>1</sup> |      |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 6.2               |       | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 11.7              |       | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 5.2               |       | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 8.9               |       | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 9.0               |       | 9.0               |      | 10.1 |      | 11.8  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 13.0              |       | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.04              |       | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.07              |       | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.03              |       | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

# A1440A, A14V40A Timing Characteristics (continued)

| Table 2-29 • A1440A. | A14V40A Worst-Case                     | Commercial Conditions.                  | VCC = 4.75 V, T <sub>J</sub> = 70°C |

|----------------------|----------------------------------------|-----------------------------------------|-------------------------------------|

|                      | ////////////////////////////////////// | ••••••••••••••••••••••••••••••••••••••• |                                     |

| Dedicate             | d (hardwired) I/O Clock Network                   | -3 Sp      | beed <sup>1</sup> | -2 Sp      | beed <sup>1</sup> | -1 Speed   |            | Std. Speed |            | I 3.3 V Speed <sup>1</sup> |            | Units |

|----------------------|---------------------------------------------------|------------|-------------------|------------|-------------------|------------|------------|------------|------------|----------------------------|------------|-------|

| Paramete             | er/Description                                    | Min.       | Max.              | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.                       | Max.       |       |

| t <sub>IOCKH</sub>   | Input Low to High (pad to I/O module input)       |            | 2.0               |            | 2.3               |            | 2.6        |            | 3.0        |                            | 3.5        | ns    |

| t <sub>IOPWH</sub>   | Minimum Pulse Width High                          | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                        |            | ns    |

| t <sub>IPOWL</sub>   | Minimum Pulse Width Low                           | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                        |            | ns    |

| t <sub>IOSAPW</sub>  | Minimum Asynchronous Pulse Width                  | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                        |            | ns    |

| t <sub>IOCKSW</sub>  | Maximum Skew                                      |            | 0.4               |            | 0.4               |            | 0.4        |            | 0.4        |                            | 0.4        | ns    |

| t <sub>IOP</sub>     | Minimum Period                                    | 4.0        |                   | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0                       |            | ns    |

| f <sub>IOMAX</sub>   | Maximum Frequency                                 |            | 250               |            | 200               |            | 150        |            | 125        |                            | 100        | MHz   |

| Dedicate             | d (hardwired) Array Clock                         | •          |                   |            |                   |            |            | •          | -          |                            |            |       |

| <sup>t</sup> нскн    | Input Low to High (pad to S-module input)         |            | 3.0               |            | 3.4               |            | 3.9        |            | 4.5        |                            | 5.5        | ns    |

| t <sub>HCKL</sub>    | Input High to Low (pad to S-module input)         |            | 3.0               |            | 3.4               |            | 3.9        |            | 4.5        |                            | 5.5        | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width High                          | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                        |            | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width Low                           | 1.9        |                   | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8                        |            | ns    |

| t <sub>HCKSW</sub>   | Delta High to Low, Low Slew                       |            | 0.3               |            | 0.3               |            | 0.3        |            | 0.3        |                            | 0.3        | ns    |

| t <sub>HP</sub>      | Minimum Period                                    | 4.0        |                   | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0                       |            | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                 |            | 250               |            | 200               |            | 150        |            | 125        |                            | 100        | MHz   |

| Routed A             | rray Clock Networks                               | •          |                   |            | •                 |            |            | •          | -          |                            |            |       |

| t <sub>RCKH</sub>    | Input Low to High (FO = 64)                       |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                            | 9.0        | ns    |

| t <sub>RCKL</sub>    | Input High to Low (FO = 64)                       |            | 4.0               |            | 4.5               |            | 5.1        |            | 6.0        |                            | 9.0        | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width High (FO = 64)                   | 3.3        |                   | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5                        |            | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width Low (FO = 64)                    | 3.3        |                   | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5                        |            | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew (FO = 128)                           |            | 0.7               |            | 0.8               |            | 0.9        |            | 1.0        |                            | 1.0        | ns    |

| t <sub>RP</sub>      | Minimum Period (FO = 64)                          | 6.8        |                   | 8.0        |                   | 8.7        |            | 10.0       |            | 13.4                       |            | ns    |

| f <sub>RMAX</sub>    | Maximum Frequency (FO = 64)                       |            | 150               |            | 125               |            | 115        |            | 100        |                            | 75         | MHz   |

| Clock-to-            | Clock Skews                                       | •          |                   |            |                   |            |            | •          | -          |                            |            |       |

| t <sub>IOHCKSW</sub> | I/O Clock to H-Clock Skew                         | 0.0        | 1.7               | 0.0        | 1.8               | 0.0        | 2.0        | 0.0        | 2.2        | 0.0                        | 3.0        | ns    |

| t <sub>IORCKSW</sub> | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 144) | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0                 | 3.0<br>3.0 | ns    |

| t <sub>HRCKSW</sub>  | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 144)   | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0                 | 1.0<br>3.0 | ns    |

Notes:

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

# A1460A, A14V60A Timing Characteristics (continued)

| Dedicated (hardwired) I/O Clock Network |                                                   | —3 Sp      | beed <sup>1</sup> | -2 Sp      | beed <sup>1</sup> | -1 Speed   |            | Std. Speed |            | 3.3 V Speed <sup>1</sup> |            | Units |

|-----------------------------------------|---------------------------------------------------|------------|-------------------|------------|-------------------|------------|------------|------------|------------|--------------------------|------------|-------|

| Parameter/Description                   |                                                   | Min.       | Max.              | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.                     | Max.       |       |

| t <sub>IOCKH</sub>                      | Input Low to High (pad to I/O module input)       |            | 2.3               |            | 2.6               |            | 3.0        |            | 3.5        |                          | 4.5        | ns    |

| t <sub>IOPWH</sub>                      | Minimum Pulse Width High                          | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IPOWL</sub>                      | Minimum Pulse Width Low                           | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IOSAPW</sub>                     | Minimum Asynchronous Pulse Width                  | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IOCKSW</sub>                     | Maximum Skew                                      |            | 0.6               |            | 0.6               |            | 0.6        |            | 0.6        |                          | 0.6        | ns    |

| t <sub>IOP</sub>                        | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>IOMAX</sub>                      | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |                          | 75         | MHz   |

| Dedicate                                | d (hardwired) Array Clock                         |            |                   |            |                   | -          |            |            |            |                          |            |       |

| t <sub>HCKH</sub>                       | Input Low to High (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                          | 7.0        | ns    |

| t <sub>HCKL</sub>                       | Input High to Low (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                          | 7.0        | ns    |

| t <sub>HPWH</sub>                       | Minimum Pulse Width High                          | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>HPWL</sub>                       | Minimum Pulse Width Low                           | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>HCKSW</sub>                      | Delta High to Low, Low Slew                       |            | 0.6               |            | 0.6               |            | 0.6        |            | 0.6        |                          | 0.6        | ns    |

| t <sub>HP</sub>                         | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>HMAX</sub>                       | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |                          | 75         | MHz   |

| Routed A                                | rray Clock Networks                               |            |                   |            |                   |            |            |            |            |                          |            |       |

| t <sub>RCKH</sub>                       | Input Low to High (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |                          | 11.8       | ns    |

| t <sub>RCKL</sub>                       | Input High to Low (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |                          | 11.8       | ns    |

| t <sub>RPWH</sub>                       | Min. Pulse Width High (FO = 64)                   | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2                      |            | ns    |

| t <sub>RPWL</sub>                       | Min. Pulse Width Low (FO = 64)                    | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2                      |            | ns    |

| t <sub>RCKSW</sub>                      | Maximum Skew (FO = 128)                           |            | 1.2               |            | 1.4               |            | 1.6        |            | 1.8        |                          | 1.8        | ns    |

| t <sub>RP</sub>                         | Minimum Period (FO = 64)                          | 8.3        |                   | 9.3        |                   | 11.1       |            | 12.5       |            | 16.7                     |            | ns    |

| f <sub>RMAX</sub>                       | Maximum Frequency (FO = 64)                       |            | 120               |            | 105               |            | 90         |            | 80         |                          | 60         | MHz   |

| Clock-to-                               | Clock Skews                                       |            |                   |            |                   |            |            |            |            |                          |            |       |

| t <sub>IOHCKSW</sub>                    | I/O Clock to H-Clock Skew                         | 0.0        | 2.6               | 0.0        | 2.7               | 0.0        | 2.9        | 0.0        | 3.0        | 0.0                      | 3.0        | ns    |

| t <sub>IORCKSW</sub>                    | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 216) | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0               | 5.0<br>5.0 | ns    |

| t <sub>HRCKSW</sub>                     | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 216)   | 0.0<br>0.0 | 1.3<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 1.0<br>3.0 | ns    |

Notes:

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

**Detailed Specifications**

## A14100A, A14V100A Timing Characteristics

| Logic Module Propagation Delays <sup>2</sup> |                                       | -3 S | peed <sup>3</sup> | -2 Speed <sup>3</sup> |      | -1 Speed |      | Std. Speed |      | 3.3 V Speed <sup>1</sup> |      | Units |

|----------------------------------------------|---------------------------------------|------|-------------------|-----------------------|------|----------|------|------------|------|--------------------------|------|-------|

| Parameter/Description                        |                                       | Min. | Max.              | Min.                  | Max. | Min.     | Max. | Min.       | Max. | Min.                     | Max. |       |

| t <sub>PD</sub>                              | Internal Array Module                 |      | 2.0               |                       | 2.3  |          | 2.6  |            | 3.0  |                          | 3.9  | ns    |

| t <sub>CO</sub>                              | Sequential Clock to Q                 |      | 2.0               |                       | 2.3  |          | 2.6  |            | 3.0  |                          | 3.9  | ns    |

| t <sub>CLR</sub>                             | Asynchronous Clear to Q               |      | 2.0               |                       | 2.3  |          | 2.6  |            | 3.0  |                          | 3.9  | ns    |

| Predict                                      | Predicted Routing Delays <sup>4</sup> |      |                   |                       |      |          |      |            |      |                          |      |       |

| t <sub>RD1</sub>                             | FO = 1 Routing Delay                  |      | 0.9               |                       | 1.0  |          | 1.1  |            | 1.3  |                          | 1.7  | ns    |

| t <sub>RD2</sub>                             | FO = 2 Routing Delay                  |      | 1.2               |                       | 1.4  |          | 1.6  |            | 1.8  |                          | 2.4  | ns    |

| t <sub>RD3</sub>                             | FO = 3 Routing Delay                  |      | 1.4               |                       | 1.6  |          | 1.8  |            | 2.1  |                          | 2.8  | ns    |

| t <sub>RD4</sub>                             | FO = 4 Routing Delay                  |      | 1.7               |                       | 1.9  |          | 2.2  |            | 2.5  |                          | 3.3  | ns    |

| t <sub>RD8</sub>                             | FO = 8 Routing Delay                  |      | 2.8               |                       | 3.2  |          | 3.6  |            | 4.2  |                          | 5.5  | ns    |

| Logic N                                      | Nodule Sequential Timing              |      |                   |                       |      |          |      |            |      |                          |      |       |

| t <sub>SUD</sub>                             | Flip-Flop Data Input Setup            | 0.5  |                   | 0.6                   |      | 0.8      |      | 0.8        |      | 0.8                      |      | ns    |

| t <sub>HD</sub>                              | Flip-Flop Data Input Hold             | 0.0  |                   | 0.0                   |      | 0.5      |      | 0.5        |      | 0.5                      |      | ns    |

| t <sub>SUD</sub>                             | Latch Data Input Setup                | 0.5  |                   | 0.6                   |      | 0.8      |      | 0.8        |      | 0.8                      |      | ns    |

| t <sub>HD</sub>                              | Latch Data Input Hold                 | 0.0  |                   | 0.0                   |      | 0.5      |      | 0.5        |      | 0.5                      |      | ns    |

| t <sub>WASYN</sub>                           | Asynchronous Pulse Width              | 2.4  |                   | 3.2                   |      | 3.8      |      | 4.8        |      | 6.5                      |      | ns    |

| t <sub>WCLKA</sub>                           | Flip-Flop Clock Pulse Width           | 2.4  |                   | 3.2                   |      | 3.8      |      | 4.8        |      | 6.5                      |      | ns    |

| t <sub>A</sub>                               | Flip-Flop Clock Input Period          | 5.0  |                   | 6.8                   |      | 8.0      |      | 10.0       |      | 13.4                     |      | ns    |

| f <sub>MAX</sub>                             | Flip-Flop Clock Frequency             |      | 200               |                       | 150  |          | 125  |            | 100  |                          | 75   | MHz   |

Notes:

1. VCC = 3.0 V for 3.3 V specifications.

2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn} + t_{CO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

3. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

4. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

# A14100A, A14V100A Timing Characteristics (continued)

| Dedicated (hardwired) I/O Clock Network |                                                   | -3 Sp      | beed <sup>1</sup> | -2 Sp      | beed <sup>1</sup> | -1 Speed   |            | Std. Speed |            | 3.3 V Speed <sup>1</sup> |            | Units |

|-----------------------------------------|---------------------------------------------------|------------|-------------------|------------|-------------------|------------|------------|------------|------------|--------------------------|------------|-------|

| Parameter/Description                   |                                                   | Min.       | Max.              | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.                     | Max.       |       |

| t <sub>IOCKH</sub>                      | Input Low to High (pad to I/O module input)       |            | 2.3               |            | 2.6               |            | 3.0        |            | 3.5        |                          | 4.5        | ns    |

| t <sub>IOPWH</sub>                      | Minimum Pulse Width High                          | 2.4        |                   | 3.3        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IPOWL</sub>                      | Minimum Pulse Width Low                           | 2.4        |                   | 3.3        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IOSAPW</sub>                     | Minimum Asynchronous Pulse Width                  | 2.4        |                   | 3.3        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>IOCKSW</sub>                     | Maximum Skew                                      |            | 0.6               |            | 0.6               |            | 0.7        |            | 0.8        |                          | 0.6        | ns    |

| t <sub>IOP</sub>                        | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>IOMAX</sub>                      | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |                          | 75         | MHz   |

| Dedicated                               | d (hardwired) Array Clock                         |            |                   |            |                   |            |            |            |            | -                        | -          |       |

| t <sub>HCKH</sub>                       | Input Low to High (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                          | 7.0        | ns    |

| t <sub>HCKL</sub>                       | Input High to Low (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |                          | 7.0        | ns    |

| t <sub>HPWH</sub>                       | Minimum Pulse Width High                          | 2.4        |                   | 3.3        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>HPWL</sub>                       | Minimum Pulse Width Low                           | 2.4        |                   | 3.3        |                   | 3.8        |            | 4.8        |            | 6.5                      |            | ns    |

| t <sub>HCKSW</sub>                      | Delta High to Low, Low Slew                       |            | 0.6               |            | 0.6               |            | 0.7        |            | 0.8        |                          | 0.6        | ns    |

| t <sub>HP</sub>                         | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>HMAX</sub>                       | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |                          | 75         | MHz   |

| Routed A                                | rray Clock Networks                               |            |                   |            |                   |            |            |            |            | -                        | -          |       |

| t <sub>RCKH</sub>                       | Input Low to High (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |                          | 11.8       | ns    |

| t <sub>RCKL</sub>                       | Input High to Low (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |                          | 11.8       | ns    |

| t <sub>RPWH</sub>                       | Min. Pulse Width High (FO = 64)                   | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2                      |            | ns    |

| t <sub>RPWL</sub>                       | Min. Pulse Width Low (FO = 64)                    | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2                      |            | ns    |

| t <sub>RCKSW</sub>                      | Maximum Skew (FO = 128)                           |            | 1.2               |            | 1.4               |            | 1.6        |            | 1.8        |                          | 1.8        | ns    |

| t <sub>RP</sub>                         | Minimum Period (FO = 64)                          | 8.3        |                   | 9.3        |                   | 11.1       |            | 12.5       |            | 16.7                     |            | ns    |

| f <sub>RMAX</sub>                       | Maximum Frequency (FO = 64)                       |            | 120               |            | 105               |            | 90         |            | 80         |                          | 60         | MHz   |

| Clock-to-                               | Clock Skews                                       |            |                   |            |                   |            |            |            |            |                          |            |       |

| t <sub>IOHCKSW</sub>                    | I/O Clock to H-Clock Skew                         | 0.0        | 2.6               | 0.0        | 2.7               | 0.0        | 2.9        | 0.0        | 3.0        | 0.0                      | 3.0        | ns    |

| t <sub>IORCKSW</sub>                    | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 350) | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0               | 5.0<br>5.0 | ns    |

| t <sub>HRCKSW</sub>                     | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 350)   | 0.0<br>0.0 | 1.3<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 1.0<br>3.0 | ns    |

Notes: \*

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

Package Pin Assignments

|            | PQ100          |                |  |  |  |  |  |  |

|------------|----------------|----------------|--|--|--|--|--|--|

| Pin Number | A1415 Function | A1425 Function |  |  |  |  |  |  |

| 2          | IOCLK, I/O     | IOCLK, I/O     |  |  |  |  |  |  |

| 14         | CLKA, I/O      | CLKA, I/O      |  |  |  |  |  |  |

| 15         | CLKB, I/O      | CLKB, I/O      |  |  |  |  |  |  |

| 16         | VCC            | VCC            |  |  |  |  |  |  |

| 17         | GND            | GND            |  |  |  |  |  |  |

| 18         | VCC            | VCC            |  |  |  |  |  |  |

| 19         | GND            | GND            |  |  |  |  |  |  |

| 20         | PRA, I/O       | PRA, I/O       |  |  |  |  |  |  |

| 27         | DCLK, I/O      | DCLK, I/O      |  |  |  |  |  |  |

| 28         | GND            | GND            |  |  |  |  |  |  |

| 29         | SDI, I/O       | SDI, I/O       |  |  |  |  |  |  |

| 34         | MODE           | MODE           |  |  |  |  |  |  |

| 35         | VCC            | VCC            |  |  |  |  |  |  |

| 36         | GND            | GND            |  |  |  |  |  |  |

| 47         | GND            | GND            |  |  |  |  |  |  |

| 48         | VCC            | VCC            |  |  |  |  |  |  |

| 61         | PRB, I/O       | PRB, I/O       |  |  |  |  |  |  |

| 62         | GND            | GND            |  |  |  |  |  |  |

| 63         | VCC            | VCC            |  |  |  |  |  |  |

| 64         | GND            | GND            |  |  |  |  |  |  |

| 65         | VCC            | VCC            |  |  |  |  |  |  |

| 67         | HCLK, I/O      | HCLK, I/O      |  |  |  |  |  |  |

| 77         | SDO            | SDO            |  |  |  |  |  |  |

| 78         | IOPCL, I/O     | IOPCL, I/O     |  |  |  |  |  |  |

| 79         | GND            | GND            |  |  |  |  |  |  |

| 85         | VCC            | VCC            |  |  |  |  |  |  |

| 86         | VCC            | VCC            |  |  |  |  |  |  |

| 87         | GND            | GND            |  |  |  |  |  |  |

| 96         | VCC            | VCC            |  |  |  |  |  |  |

| 97         | GND            | GND            |  |  |  |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Package Pin Assignments

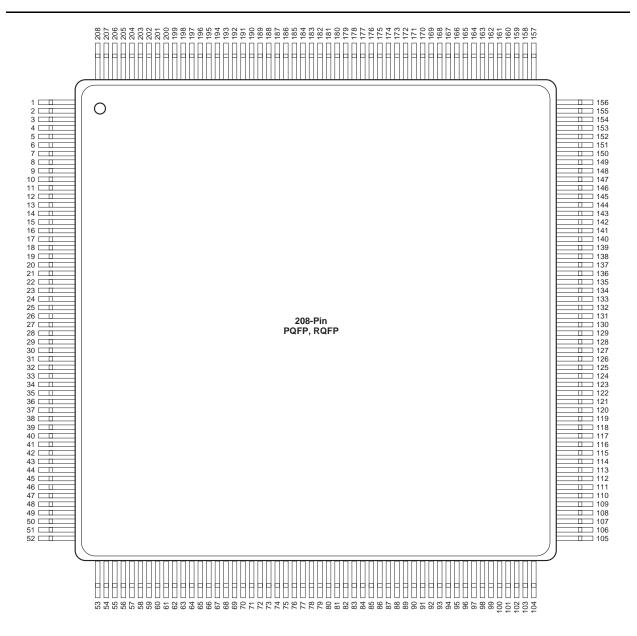

# PQ208, RQ208

Note: This is the top view of the package

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs – ACT 3 Family

| VQ100      |                        |                        |                        |  |  |  |

|------------|------------------------|------------------------|------------------------|--|--|--|

| Pin Number | A1415, A14V15 Function | A1425, A14V25 Function | A1440, A14V40 Function |  |  |  |

| 1          | GND                    | GND                    | GND                    |  |  |  |

| 2          | SDI, I/O               | SDI, I/O               | SDI, I/O               |  |  |  |

| 7          | MODE                   | MODE                   | MODE                   |  |  |  |

| 8          | VCC                    | VCC                    | VCC                    |  |  |  |

| 9          | GND                    | GND                    | GND                    |  |  |  |

| 20         | VCC                    | VCC                    | VCC                    |  |  |  |

| 21         | NC                     | I/O                    | I/O                    |  |  |  |

| 34         | PRB, I/O               | PRB, I/O               | PRB, I/O               |  |  |  |

| 35         | VCC                    | VCC                    | VCC                    |  |  |  |

| 36         | GND                    | GND                    | GND                    |  |  |  |

| 37         | VCC                    | VCC                    | VCC                    |  |  |  |

| 39         | HCLK, I/O              | HCLK, I/O              | HCLK, I/O              |  |  |  |

| 49         | SDO                    | SDO                    | SDO                    |  |  |  |

| 50         | IOPCL, I/O             | IOPCL, I/O             | IOPCL, I/O             |  |  |  |

| 51         | GND                    | GND                    | GND                    |  |  |  |

| 57         | VCC                    | VCC                    | VCC                    |  |  |  |

| 58         | VCC                    | VCC                    | VCC                    |  |  |  |

| 67         | VCC                    | VCC                    | VCC                    |  |  |  |

| 68         | GND                    | GND                    | GND                    |  |  |  |

| 69         | GND                    | GND                    | GND                    |  |  |  |

| 74         | NC                     | I/O                    | I/O                    |  |  |  |

| 75         | IOCLK, I/O             | IOCLK, I/O             | IOCLK, I/O             |  |  |  |

| 87         | CLKA, I/O              | CLKA, I/O              | CLKA, I/O              |  |  |  |

| 88         | CLKB, I/O              | CLKB, I/O              | CLKB, I/O              |  |  |  |

| 89         | VCC                    | VCC                    | VCC                    |  |  |  |

| 90         | VCC                    | VCC                    | VCC                    |  |  |  |

| 91         | GND                    | GND                    | GND                    |  |  |  |

| 92         | PRA, I/O               | PRA, I/O               | PRA, I/O               |  |  |  |

| 93         | NC                     | I/O                    | I/O                    |  |  |  |

| 100        | DCLK, I/O              | DCLK, I/O              | DCLK, I/O              |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Microsemi

Accelerator Series FPGAs - ACT 3 Family

|            | CQ132          | CQ132      |                |  |  |  |

|------------|----------------|------------|----------------|--|--|--|

| Pin Number | A1425 Function | Pin Number | A1425 Function |  |  |  |

| 1          | NC             | 67         | NC             |  |  |  |

| 2          | GND            | 74         | GND            |  |  |  |

| 3          | SDI, I/O       | 75         | VCC            |  |  |  |

| 9          | MODE           | 78         | VCC            |  |  |  |

| 10         | GND            | 89         | VCC            |  |  |  |

| 11         | VCC            | 90         | GND            |  |  |  |

| 22         | VCC            | 91         | VCC            |  |  |  |

| 26         | GND            | 92         | GND            |  |  |  |

| 27         | VCC            | 98         | IOCLK, I/O     |  |  |  |

| 34         | NC             | 99         | NC             |  |  |  |

| 36         | GND            | 100        | NC             |  |  |  |

| 42         | GND            | 101        | GND            |  |  |  |

| 43         | VCC            | 106        | GND            |  |  |  |

| 48         | PRB, I/O       | 107        | VCC            |  |  |  |

| 50         | HCLK, I/O      | 116        | CLKA, I/O      |  |  |  |

| 58         | GND            | 117        | CLKB, I/O      |  |  |  |

| 59         | VCC            | 118        | PRA, I/O       |  |  |  |

| 63         | SDO            | 122        | GND            |  |  |  |

| 64         | IOPCL, I/O     | 123        | VCC            |  |  |  |

| 65         | GND            | 131        | DCLK, I/O      |  |  |  |

| 66         | NC             | 132        | NC             |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Package Pin Assignments

Microsemi

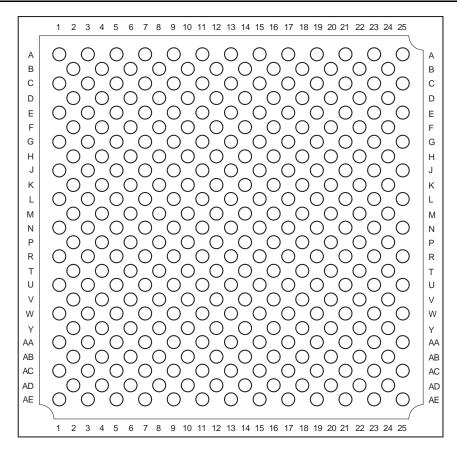

# BG313

#### Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs – ACT 3 Family

|                | PG133                                                    |  |  |  |  |  |  |

|----------------|----------------------------------------------------------|--|--|--|--|--|--|

| A1425 Function | Location                                                 |  |  |  |  |  |  |

| CLKA or I/O    | D7                                                       |  |  |  |  |  |  |

| CLKB or I/O    | B6                                                       |  |  |  |  |  |  |

| DCLK or I/O    | D4                                                       |  |  |  |  |  |  |

| GND            | A2, C3, C7, C11, C12, F10, G3, G11, L3, L7, L11, M3, N12 |  |  |  |  |  |  |

| HCLK or I/O    | К7                                                       |  |  |  |  |  |  |

| IOCLK or I/O   | C10                                                      |  |  |  |  |  |  |

| IOPCL or I/O   | L10                                                      |  |  |  |  |  |  |

| MODE           | E3                                                       |  |  |  |  |  |  |

| NC             | A1, A7, A13, G1, G13, N1, N7, N13                        |  |  |  |  |  |  |

| PRA or I/O     | A6                                                       |  |  |  |  |  |  |

| PRB or I/O     | L6                                                       |  |  |  |  |  |  |

| SDI or I/O     | C2                                                       |  |  |  |  |  |  |

| SDO            | M11                                                      |  |  |  |  |  |  |

| VCC            | B2, B7, B12, E11, G2, G12, J2, J12, M2, M7, M12          |  |  |  |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

- 4. The PG133 package has been discontinued.

Package Pin Assignments

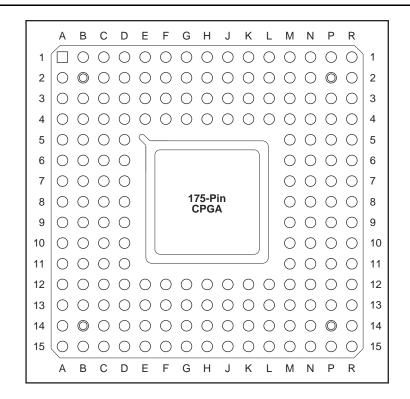

# PG175

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

# **Datasheet Categories**

### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

## **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

#### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Production

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.