Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 310                                                           |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 70                                                            |

| Number of Gates                | 2500                                                          |

| Voltage - Supply               | 4.5V ~ 5.5V                                                   |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 85°C (TA)                                             |

| Package / Case                 | 84-LCC (J-Lead)                                               |

| Supplier Device Package        | 84-PLCC (29.31x29.31)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1425a-1plg84i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The I/O module output Y is used to bring Pad signals into the array or to feed the output register back into the array. This allows the output register to be used in high-speed state machine applications. Side I/O modules have a dedicated output segment for Y extending into the routing channels above and below (similar to logic modules). Top/Bottom I/O modules have no dedicated output segment. Signals coming into the chip from the top or bottom are routed using F-fuses and LVTs (F-fuses and LVTs are explained in detail in the routing section).

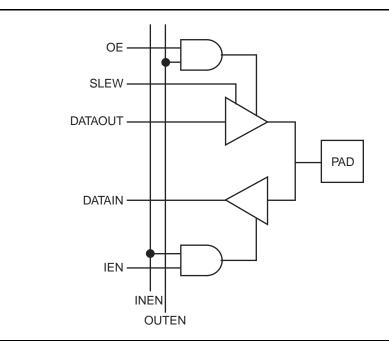

# I/O Pad Drivers

All pad drivers are capable of being tristate. Each buffer connects to an associated I/O module with four signals: OE (Output Enable), IE (Input Enable), DataOut, and DataIn. Certain special signals used only during programming and test also connect to the pad drivers: OUTEN (global output enable), INEN (global input enable), and SLEW (individual slew selection). See Figure 2-5.

*Figure 2-5* • Function Diagram for I/O Pad Driver

# **Special I/Os**

The special I/Os are of two types: temporary and permanent. Temporary special I/Os are used during programming and testing. They function as normal I/Os when the MODE pin is inactive. Permanent special I/Os are user programmed as either normal I/Os or special I/Os. Their function does not change once the device has been programmed. The permanent special I/Os consist of the array clock input buffers (CLKA and CLKB), the hard-wired array clock input buffer (HCLK), the hard-wired I/O clock input buffer (IOCLK), and the hard-wired I/O register preset/clear input buffer (IOPCL). Their function is determined by the I/O macros selected.

# **Clock Networks**

The ACT 3 architecture contains four clock networks: two high-performance dedicated clock networks and two general purpose routed networks. The high-performance networks function up to 200 MHz, while the general purpose routed networks function up to 150 MHz.

# **Package Thermal Characteristics**

The device junction to case thermal characteristic is  $\theta$ jc, and the junction to ambient air characteristic is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

Maximum junction temperature is 150°C.

A sample calculation of the absolute maximum power dissipation allowed for a CPGA 175-pin package at commercial temperature and still air is as follows:

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{ja} °C/W} = \frac{150°C - 70°C}{25°C/W} = 3.2 \text{ W}$$

EQ 2

| Package Type∗               | Pin Count | θ <sub>jc</sub> | θ <sub>ja</sub><br>Still Air | θ <sub>ja</sub><br>300 ft./min. | Units |

|-----------------------------|-----------|-----------------|------------------------------|---------------------------------|-------|

| Ceramic Pin Grid Array      | 100       | 20              | 35                           | 17                              | °C/W  |

|                             | 133       | 20              | 30                           | 15                              | °C/W  |

|                             | 175       | 20              | 25                           | 14                              | °C/W  |

|                             | 207       | 20              | 22                           | 13                              | °C/W  |

|                             | 257       | 20              | 15                           | 8                               | °C/W  |

| Ceramic Quad Flatpack       | 132       | 13              | 55                           | 30                              | °C/W  |

|                             | 196       | 13              | 36                           | 24                              | °C/W  |

|                             | 256       | 13              | 30                           | 18                              | °C/W  |

| Plastic Quad Flatpack       | 100       | 13              | 51                           | 40                              | °C/W  |

|                             | 160       | 10              | 33                           | 26                              | °C/W  |

|                             | 208       | 10              | 33                           | 26                              | °C/W  |

| Very Thin Quad Flatpack     | 100       | 12              | 43                           | 35                              | °C/W  |

| Thin Quad Flatpack          | 176       | 11              | 32                           | 25                              | °C/W  |

| Power Quad Flatpack         | 208       | 0.4             | 17                           | 13                              | °C/W  |

| Plastic Leaded Chip Carrier | 84        | 12              | 37                           | 28                              | °C/W  |

| Plastic Ball Grid Array     | 225       | 10              | 25                           | 19                              | °C/W  |

|                             | 313       | 10              | 23                           | 17                              | °C/W  |

#### Table 2-8 • Package Thermal Characteristics

Note: Maximum power dissipation in still air:

PQ160 = 2.4 W PQ208 = 2.4 W PQ100 = 1.6 W VQ100 = 1.9 W TQ176 = 2.5 W PL84 = 2.2 W RQ208 = 4.7 W BG225 = 3.2 W BG313 = 3.5 W

# **Tightest Delay Distributions**

Propagation delay between logic modules depends on the resistive and capacitive loading of the routing tracks, the interconnect elements, and the module inputs being driven. Propagation delay increases as the length of routing tracks, the number of interconnect elements, or the number of inputs increases.

From a design perspective, the propagation delay can be statistically correlated or modeled by the fanout (number of loads) driven by a module. Higher fanout usually requires some paths to have longer lengths of routing track. The ACT 3 family delivers the tightest fanout delay distribution of any FPGA. This tight distribution is achieved in two ways: by decreasing the delay of the interconnect elements and by decreasing the number of interconnect elements per path.

Microsemi's patented PLICE antifuse offers a very low resistive/capacitive interconnect. The ACT 3 family's antifuses, fabricated in 0.8 micron m lithography, offer nominal levels of  $200\Omega$  resistance and 6 femtofarad (fF) capacitance per antifuse. The ACT 3 fanout distribution is also tighter than alternative devices due to the low number of antifuses required per interconnect path. The ACT 3 family's proprietary architecture limits the number of antifuses per path to only four, with 90% of interconnects using only two antifuses.

The ACT 3 family's tight fanout delay distribution offers an FPGA design environment in which fanout can be traded for the increased performance of reduced logic level designs. This also simplifies performance estimates when designing with ACT 3 devices.

| Speed Grade | FO = 1 | FO = 2 | FO = 3 | FO = 4 | FO = 8 |

|-------------|--------|--------|--------|--------|--------|

| ACT 3 –3    | 2.9    | 3.2    | 3.4    | 3.7    | 4.8    |

| ACT 3 –2    | 3.3    | 3.7    | 3.9    | 4.2    | 5.5    |

| ACT 3 –1    | 3.7    | 4.2    | 4.4    | 4.8    | 6.2    |

| ACT 3 STD   | 4.3    | 4.8    | 5.1    | 5.5    | 7.2    |

Table 2-14 • Logic Module and Routing Delay by Fanout (ns); Worst-Case Commercial Conditions

Notes:

- Obtained by added t<sub>RD(x=FO)</sub> to t<sub>PD</sub> from the Logic Module Timing Characteristics Tables found in this datasheet.

- 2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

# **Timing Characteristics**

Timing characteristics for ACT 3 devices fall into three categories: family dependent, device dependent, and design dependent. The input and output buffer characteristics are common to all ACT 3 family members. Internal routing delays are device dependent. Design dependency means actual delays are not determined until after placement and routing of the user's design is complete. Delay values may then be determined by using the ALS Timer utility or performing simulation with post-layout delays.

## Critical Nets and Typical Nets

Propagation delays are expressed only for typical nets, which are used for initial design performance evaluation. Critical net delays can then be applied to the most time-critical paths. Critical nets are determined by net property assignment prior to placement and routing. Up to 6% of the nets in a design may be designated as critical, while 90% of the nets in a design are typical.

## Long Tracks

Some nets in the design use long tracks. Long tracks are special routing resources that span multiple rows, columns, or modules. Long tracks employ three and sometimes four antifuse connections. This increases capacitance and resistance, result ng in longer net delays for macros connected to long tracks. Typically up to 6% of nets in a fully utilized device require long tracks. Long tracks contribute approximately 4 ns to 14 ns delay. This additional delay is represented statistically in higher fanout (FO = 8) routing delays in the datasheet specifications section.

**Detailed Specifications**

## A1415A, A14V15A Timing Characteristics (continued)

Table 2-20 • A1415A, A14V15A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Moc            | dule – TTL Output Timing <sup>1</sup> | -3 Sp | beed <sup>2</sup> | –2 S | peed <sup>2</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|---------------------------------------|-------|-------------------|------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                      | Min.  | Max.              | Min. | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                |       | 5.0               |      | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                 |       | 8.0               |      | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew    |       | 4.0               |      | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew     |       | 7.4               |      | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew    |       | 6.5               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew     |       | 6.5               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew       |       | 7.5               |      | 7.5               |      | 9.0  |      | 10.0  |       | 13.0               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew        |       | 11.3              |      | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew          |       | 0.02              |      | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew           |       | 0.05              |      | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew          |       | 0.04              |      | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew           |       | 0.05              |      | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Moc            | ule – CMOS Output Timing <sup>1</sup> |       |                   |      |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                |       | 6.2               |      | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                 |       | 11.7              |      | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew    |       | 5.2               |      | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew     |       | 8.9               |      | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew    |       | 6.7               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew     |       | 6.7               |      | 7.5               |      | 9.0  |      | 10.0  |       | 13.0               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew       |       | 8.9               |      | 8.9               |      | 10.7 |      | 11.8  |       | 15.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew        |       | 13.0              |      | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew          |       | 0.04              |      | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew           |       | 0.07              |      | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew          |       | 0.03              |      | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew           |       | 0.04              |      | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Please refer to the Product Discontinuation Notices (PDNs) listed below:

PDN March 2001 PDN 0104 PDN 0203 PDN 0604 PDN 1004

## A1415A, A14V15A Timing Characteristics (continued)

#### *Table 2-21* • A1415A, A14V15A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| Dedicate             | d (hardwired) I/O Clock Network                         | -3 S | peed | –2 S | peed | –1 S | peed | Std. | Speed | 3.3 V      | Speed <sup>1</sup> | Units |

|----------------------|---------------------------------------------------------|------|------|------|------|------|------|------|-------|------------|--------------------|-------|

| Paramete             | er/Description                                          | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max.  | Min.       | Max.               |       |

| t <sub>IOCKH</sub>   | Input Low to High (pad to I/O module input)             |      | 2.0  |      | 2.3  |      | 2.6  |      | 3.0   |            | 3.5                | ns    |

| t <sub>IOPWH</sub>   | Minimum Pulse Width High                                | 1.9  |      | 2.4  |      | 3.3  |      | 3.8  |       | 4.8        |                    | ns    |

| t <sub>IPOWL</sub>   | Minimum Pulse Width Low                                 | 1.9  |      | 2.4  |      | 3.3  |      | 3.8  |       | 4.8        |                    | ns    |

| t <sub>IOSAPW</sub>  | Minimum Asynchronous Pulse Width                        | 1.9  |      | 2.4  |      | 3.3  |      | 3.8  |       | 4.8        |                    | ns    |

| t <sub>IOCKSW</sub>  | Maximum Skew                                            |      | 0.4  |      | 0.4  |      | 0.4  |      | 0.4   |            | 0.4                | ns    |

| t <sub>IOP</sub>     | Minimum Period                                          | 4.0  |      | 5.0  |      | 6.8  |      | 8.0  |       | 10.0       |                    | ns    |

| f <sub>IOMAX</sub>   | Maximum Frequency                                       |      | 250  |      | 200  |      | 150  |      | 125   |            | 100                | MHz   |

| Dedicate             | d (hardwired) Array Clock                               |      |      |      |      |      |      |      |       |            |                    |       |

| <sup>t</sup> нскн    | Input Low to High (pad to S-module input)               |      | 3.0  |      | 3.4  |      | 3.9  |      | 4.5   |            | 5.5                | ns    |

| t <sub>HCKL</sub>    | Input High to Low (pad to S-module input)               |      | 3.0  |      | 3.4  |      | 3.9  |      | 4.5   |            | 5.5                | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width High                                | 1.9  |      | 2.4  |      | 3.3  |      | 3.8  |       | 4.8        |                    | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width Low                                 | 1.9  |      | 2.4  |      | 3.3  |      | 3.8  |       | 4.8        |                    | ns    |

| t <sub>HCKSW</sub>   | Delta High to Low, Low Slew                             |      | 0.3  |      | 0.3  |      | 0.3  |      | 0.3   |            | 0.3                | ns    |

| t <sub>HP</sub>      | Minimum Period                                          | 4.0  |      | 5.0  |      | 6.8  |      | 8.0  |       | 10.0       |                    | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                       |      | 250  |      | 200  |      | 150  |      | 125   |            | 100                | MHz   |

| Routed A             | rray Clock Networks                                     | •    |      |      | •    |      |      | •    | -     |            |                    |       |

| t <sub>RCKH</sub>    | Input Low to High (FO = 64)                             |      | 3.7  |      | 4.1  |      | 4.7  |      | 5.5   |            | 9.0                | ns    |

| t <sub>RCKL</sub>    | Input High to Low (FO = 64)                             |      | 4.0  |      | 4.5  |      | 5.1  |      | 6.0   |            | 9.0                | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width High (FO = 64)                         | 3.3  |      | 3.8  |      | 4.2  |      | 4.9  |       | 6.5        |                    | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width Low (FO = 64)                          | 3.3  |      | 3.8  |      | 4.2  |      | 4.9  |       | 6.5        |                    | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew (FO = 128)                                 |      | 0.7  |      | 0.8  |      | 0.9  |      | 1.0   |            | 1.0                | ns    |

| t <sub>RP</sub>      | Minimum Period (FO = 64)                                | 6.8  |      | 8.0  |      | 8.7  |      | 10.0 |       | 13.4       |                    | ns    |

| f <sub>RMAX</sub>    | Maximum Frequency (FO = 64)                             |      | 150  |      | 125  |      | 115  |      | 100   |            | 75                 | MHz   |

| Clock-to-            | Clock Skews                                             | •    |      |      | •    |      |      | •    | -     |            |                    |       |

| t <sub>IOHCKSW</sub> | I/O Clock to H-Clock Skew                               | 0.0  | 1.7  | 0.0  | 1.8  | 0.0  | 2.0  | 0.0  | 2.2   | 0.0        | 3.0                | ns    |

| t <sub>IORCKSW</sub> | I/O Clock to R-Clock Skew (FO = 64)                     | 0.0  | 1.0  | 0.0  | 1.0  | 0.0  | 1.0  | 0.0  | 1.0   | 0.0        | 3.0                | ns    |

| t <sub>HRCKSW</sub>  | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 50% maximum) | 0.0  | 1.0  | 0.0  | 1.0  | 0.0  | 1.0  | 0.0  | 1.0   | 0.0<br>0.0 | 3.0<br>3.0         | ns    |

Notes:

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

**Detailed Specifications**

## A1425A, A14V25A Timing Characteristics

Table 2-22 • A1425A, A14V25A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C<sup>1</sup>

| Logic N            | Iodule Propagation Delays <sup>2</sup> | -3 S | peed <sup>3</sup> | –2 S | peed <sup>3</sup> | -1 S | peed | Std. S | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|------|-------------------|------|-------------------|------|------|--------|-------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min. | Max.              | Min. | Max.              | Min. | Max. | Min.   | Max.  | Min.  | Max.               | 1     |

| t <sub>PD</sub>    | Internal Array Module                  |      | 2.0               |      | 2.3               |      | 2.6  |        | 3.0   |       | 3.9                | ns    |

| t <sub>CO</sub>    | Sequential Clock to Q                  |      | 2.0               |      | 2.3               |      | 2.6  |        | 3.0   |       | 3.9                | ns    |

| t <sub>CLR</sub>   | Asynchronous Clear to Q                |      | 2.0               |      | 2.3               |      | 2.6  |        | 3.0   |       | 3.9                | ns    |

| Predict            | ed Routing Delays <sup>4</sup>         |      |                   |      |                   |      |      |        |       |       |                    |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                   |      | 0.9               |      | 1.0               |      | 1.1  |        | 1.3   |       | 1.7                | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                   |      | 1.2               |      | 1.4               |      | 1.6  |        | 1.8   |       | 2.4                | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                   |      | 1.4               |      | 1.6               |      | 1.8  |        | 2.1   |       | 2.8                | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                   |      | 1.7               |      | 1.9               |      | 2.2  |        | 2.5   |       | 3.3                | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                   |      | 2.8               |      | 3.2               |      | 3.6  |        | 4.2   |       | 5.5                | ns    |

| Logic N            | Nodule Sequential Timing               |      |                   |      |                   |      |      |        |       |       | 1                  |       |

| t <sub>SUD</sub>   | Flip-Flop Data Input Setup             | 0.5  |                   | 0.6  |                   | 0.7  |      | 0.8    |       | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Flip-Flop Data Input Hold              | 0.0  |                   | 0.0  |                   | 0.0  |      | 0.0    |       | 0.0   |                    | ns    |

| t <sub>SUD</sub>   | Latch Data Input Setup                 | 0.5  |                   | 0.6  |                   | 0.7  |      | 0.8    |       | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Latch Data Input Hold                  | 0.0  |                   | 0.0  |                   | 0.0  |      | 0.0    |       | 0.0   |                    | ns    |

| t <sub>WASYN</sub> | Asynchronous Pulse Width               | 1.9  |                   | 2.4  |                   | 3.2  |      | 3.8    |       | 4.8   |                    | ns    |

| t <sub>WCLKA</sub> | Flip-Flop Clock Pulse Width            | 1.9  |                   | 2.4  |                   | 3.2  |      | 3.8    |       | 4.8   |                    | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period           | 4.0  |                   | 5.0  |                   | 6.8  |      | 8.0    |       | 10.0  |                    | ns    |

| f <sub>MAX</sub>   | Flip-Flop Clock Frequency              |      | 250               |      | 200               |      | 150  |        | 125   |       | 100                | MHz   |

Notes:

1. VCC = 3.0 V for 3.3 V specifications.

2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn} + t_{CO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

3. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

4. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

## A1440A, A14V40A Timing Characteristics (continued)

| Table 2-27 $\bullet$ $\Lambda 1/10\Lambda$ | A14V40A Worst-Case  | Commercial Conditions | , VCC = 4.75 V, T <sub>J</sub> = 70°C |

|--------------------------------------------|---------------------|-----------------------|---------------------------------------|

| <i>Table 2-27</i> • A 1440A,               | A 14V4UA WUISI-Case | Commercial Conditions | , v = 4.75 v, 1 = 70 c                |

| I/O Moc            | lule Input Propagation Delays        | -3 Sp | beed <sup>1</sup> | -2 Sp | beed <sup>1</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|--------------------------------------|-------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                     | Min.  | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               |       |

| t <sub>INY</sub>   | Input Data Pad to Y                  |       | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |       | 5.5                | ns    |

| t <sub>ICKY</sub>  | Input Reg IOCLK Pad to Y             |       | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>OCKY</sub>  | Output Reg IOCLK Pad to Y            |       | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>ICLRY</sub> | Input Asynchronous Clear to Y        |       | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>OCLRY</sub> | Output Asynchronous Clear to Y       |       | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| Predict            | ed Input Routing Delays <sup>2</sup> |       |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                 |       | 0.9               |       | 1.0               |      | 1.1  |      | 1.3   |       | 1.7                | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                 |       | 1.2               |       | 1.4               |      | 1.6  |      | 1.8   |       | 2.4                | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                 |       | 1.4               |       | 1.6               |      | 1.8  |      | 2.1   |       | 2.8                | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                 |       | 1.7               |       | 1.9               |      | 2.2  |      | 2.5   |       | 3.3                | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                 |       | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |       | 5.5                | ns    |

| I/O Mod            | lule Sequential Timing (wrt IOCLK    | pad)  |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>INH</sub>   | Input F-F Data Hold                  | 0.0   |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0   |                    | ns    |

| t <sub>INSU</sub>  | Input F-F Data Setup                 | 1.8   |                   | 1.7   |                   | 2.0  |      | 2.3  |       | 2.3   |                    | ns    |

| t <sub>IDEH</sub>  | Input Data Enable Hold               | 0.0   |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0   |                    | ns    |

| t <sub>IDESU</sub> | Input Data Enable Setup              | 5.8   |                   | 6.5   |                   | 7.5  |      | 8.6  |       | 8.6   |                    | ns    |

| t <sub>OUTH</sub>  | Output F-F Data hold                 | 0.7   |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0   |                    | ns    |

| t <sub>OUTSU</sub> | Output F-F Data Setup                | 0.7   |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0   |                    | ns    |

| t <sub>ODEH</sub>  | Output Data Enable Hold              | 0.3   |                   | 0.4   |                   | 0.4  |      | 0.5  |       | 0.5   |                    | ns    |

| f <sub>ODESU</sub> | Output Data Enable Setup             | 1.3   |                   | 1.5   |                   | 1.7  |      | 2.0  |       | 2.0   |                    | ns    |

Notes:

1. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

## A1440A, A14V40A Timing Characteristics (continued)

Table 2-28 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Moo            | dule – TTL Output Timing <sup>1</sup>  | -3 S | beed <sup>2</sup> | -2 Sp | beed <sup>2</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min. | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               | 1     |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 5.0               |       | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 8.0               |       | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 4.0               |       | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 8.5               |       | 8.5               |      | 9.5  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 11.3              |       | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.02              |       | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Moo            | dule – CMOS Output Timing <sup>1</sup> |      |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 6.2               |       | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 11.7              |       | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 5.2               |       | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 8.9               |       | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 9.0               |       | 9.0               |      | 10.1 |      | 11.8  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 13.0              |       | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.04              |       | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.07              |       | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.03              |       | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

**Detailed Specifications**

## A14100A, A14V100A Timing Characteristics

| Logic N            | Iodule Propagation Delays <sup>2</sup> | -3 S | peed <sup>3</sup> | -2 Sp | beed <sup>3</sup> | –1 S      | peed | Std. S    | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|------|-------------------|-------|-------------------|-----------|------|-----------|-------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min. | Max.              | Min.  | Max.              | Min. Max. |      | Min. Max. |       | Min.  | Max.               |       |

| t <sub>PD</sub>    | Internal Array Module                  |      | 2.0               |       | 2.3               |           | 2.6  |           | 3.0   |       | 3.9                | ns    |

| t <sub>CO</sub>    | Sequential Clock to Q                  |      | 2.0               |       | 2.3               |           | 2.6  |           | 3.0   |       | 3.9                | ns    |

| t <sub>CLR</sub>   | Asynchronous Clear to Q                |      | 2.0               |       | 2.3               |           | 2.6  |           | 3.0   |       | 3.9                | ns    |

| Predict            | ed Routing Delays <sup>4</sup>         |      |                   |       |                   |           |      |           |       |       |                    |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                   |      | 0.9               |       | 1.0               |           | 1.1  |           | 1.3   |       | 1.7                | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                   |      | 1.2               |       | 1.4               |           | 1.6  |           | 1.8   |       | 2.4                | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                   |      | 1.4               |       | 1.6               |           | 1.8  |           | 2.1   |       | 2.8                | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                   |      | 1.7               |       | 1.9               |           | 2.2  |           | 2.5   |       | 3.3                | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                   |      | 2.8               |       | 3.2               |           | 3.6  |           | 4.2   |       | 5.5                | ns    |

| Logic N            | Nodule Sequential Timing               |      |                   |       |                   |           |      |           |       |       |                    |       |

| t <sub>SUD</sub>   | Flip-Flop Data Input Setup             | 0.5  |                   | 0.6   |                   | 0.8       |      | 0.8       |       | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Flip-Flop Data Input Hold              | 0.0  |                   | 0.0   |                   | 0.5       |      | 0.5       |       | 0.5   |                    | ns    |

| t <sub>SUD</sub>   | Latch Data Input Setup                 | 0.5  |                   | 0.6   |                   | 0.8       |      | 0.8       |       | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Latch Data Input Hold                  | 0.0  |                   | 0.0   |                   | 0.5       |      | 0.5       |       | 0.5   |                    | ns    |

| t <sub>WASYN</sub> | Asynchronous Pulse Width               | 2.4  |                   | 3.2   |                   | 3.8       |      | 4.8       |       | 6.5   |                    | ns    |

| t <sub>WCLKA</sub> | Flip-Flop Clock Pulse Width            | 2.4  |                   | 3.2   |                   | 3.8       |      | 4.8       |       | 6.5   |                    | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period           | 5.0  |                   | 6.8   |                   | 8.0       |      | 10.0      |       | 13.4  |                    | ns    |

| f <sub>MAX</sub>   | Flip-Flop Clock Frequency              |      | 200               |       | 150               |           | 125  |           | 100   |       | 75                 | MHz   |

Notes:

1. VCC = 3.0 V for 3.3 V specifications.

2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn} + t_{CO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

3. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

4. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

Accelerator Series FPGAs – ACT 3 Family

#### SDO Serial Data Output (Output)

Serial data output for diagnostic probe. SDO is active when the MODE pin is High. This pin functions as an I/O when the MODE pin is Low.

#### DCLK Diagnostic Clock (Input)

Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### VCC 5 V Supply Voltage

HIGH supply voltage.

Microsemi

Accelerator Series FPGAs – ACT 3 Family

| PQ160 Pin Number 01425 014V25 Eulection 01400 014V40 Eulection 01460 014V60 Eulection |                        |                        |                        |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|--|--|--|--|--|--|--|--|

| Pin Number                                                                            | A1425, A14V25 Function | A1440, A14V40 Function | A1460, A14V60 Function |  |  |  |  |  |  |  |  |

| 92                                                                                    | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 93                                                                                    | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 98                                                                                    | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 99                                                                                    | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 100                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 103                                                                                   | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 107                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 109                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 110                                                                                   | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 111                                                                                   | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 112                                                                                   | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 113                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 119                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 120                                                                                   | IOCLK, I/O             | IOCLK, I/O             | IOCLK, I/O             |  |  |  |  |  |  |  |  |

| 121                                                                                   | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 124                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 127                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 136                                                                                   | CLKA, I/O              | CLKA, I/O              | CLKA, I/O              |  |  |  |  |  |  |  |  |

| 137                                                                                   | CLKB, I/O              | CLKB, I/O              | CLKB, I/O              |  |  |  |  |  |  |  |  |

| 138                                                                                   | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 139                                                                                   | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 140                                                                                   | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 141                                                                                   | GND                    | GND                    | GND                    |  |  |  |  |  |  |  |  |

| 142                                                                                   | PRA, I/O               | PRA, I/O               | PRA, I/O               |  |  |  |  |  |  |  |  |

| 143                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 145                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 147                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 149                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 151                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 153                                                                                   | NC                     | I/O                    | I/O                    |  |  |  |  |  |  |  |  |

| 154                                                                                   | VCC                    | VCC                    | VCC                    |  |  |  |  |  |  |  |  |

| 160                                                                                   | DCLK, I/O              | DCLK, I/O              | DCLK, I/O              |  |  |  |  |  |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Microsemi

Accelerator Series FPGAs – ACT 3 Family

| BG225          |                                                                                     |  |  |

|----------------|-------------------------------------------------------------------------------------|--|--|

| A1460 Function | Location                                                                            |  |  |

| CLKA or I/O    | C8                                                                                  |  |  |

| CLKB or I/O    | B8                                                                                  |  |  |

| DCLK or I/O    | B2                                                                                  |  |  |

| GND            | A1, A15, D15, F8, G7, G8, G9, H6, H7, H8, H9, H10, J7, J8, J9, K8, P2, R15          |  |  |

| HCLK or I/O    | P9                                                                                  |  |  |

| IOCLK or I/O   | B14                                                                                 |  |  |

| IOPCL or I/O   | P14                                                                                 |  |  |

| MODE           | D1                                                                                  |  |  |

| NC             | A11, B5, B7, D8, D12, F6, F11, H1, H12, H14, K11, L1, L13, N8, P5, R1, R8, R11, R14 |  |  |

| PRA or I/O     | A7                                                                                  |  |  |

| PRB or I/O     | L7                                                                                  |  |  |

| SDI or I/O     | D4                                                                                  |  |  |

| SDO            | N13                                                                                 |  |  |

| VCC            | A8, B12, D5, D14, E3, E8, E13, H2, H3, H11, H15, K4, L2, L12, M8, M15, P4, P8, R13  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

- 4. The BG225 package has been discontinued.

Package Pin Assignments

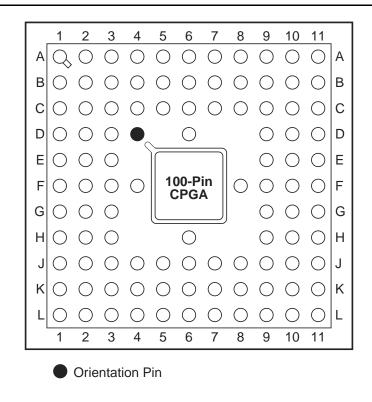

# PG100

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Package Pin Assignments

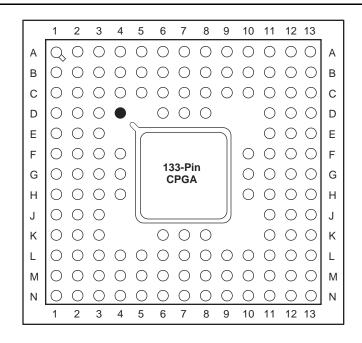

# PG133

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs – ACT 3 Family

|                | PG133                                                    |  |  |  |  |

|----------------|----------------------------------------------------------|--|--|--|--|

| A1425 Function | Location                                                 |  |  |  |  |

| CLKA or I/O    | D7                                                       |  |  |  |  |

| CLKB or I/O    | B6                                                       |  |  |  |  |

| DCLK or I/O    | D4                                                       |  |  |  |  |

| GND            | A2, C3, C7, C11, C12, F10, G3, G11, L3, L7, L11, M3, N12 |  |  |  |  |

| HCLK or I/O    | К7                                                       |  |  |  |  |

| IOCLK or I/O   | C10                                                      |  |  |  |  |

| IOPCL or I/O   | L10                                                      |  |  |  |  |

| MODE           | E3                                                       |  |  |  |  |

| NC             | A1, A7, A13, G1, G13, N1, N7, N13                        |  |  |  |  |

| PRA or I/O     | A6                                                       |  |  |  |  |

| PRB or I/O     | L6                                                       |  |  |  |  |

| SDI or I/O     | C2                                                       |  |  |  |  |

| SDO            | M11                                                      |  |  |  |  |

| VCC            | B2, B7, B12, E11, G2, G12, J2, J12, M2, M7, M12          |  |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

- 4. The PG133 package has been discontinued.

Package Pin Assignments

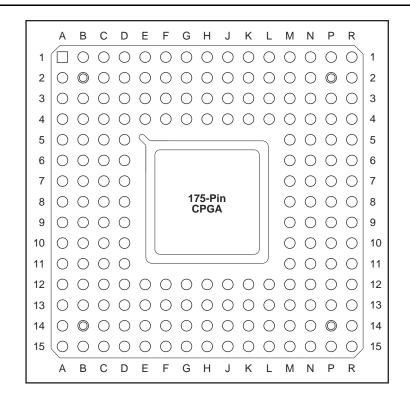

# PG175

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Package Pin Assignments

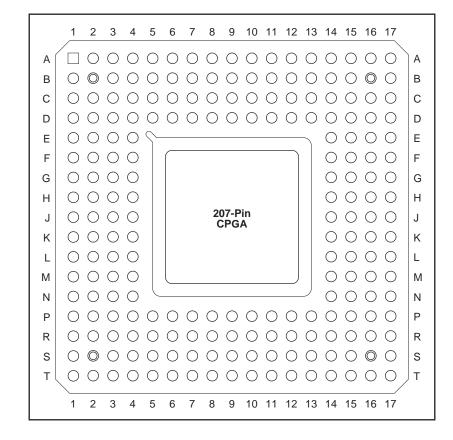

# PG207

#### Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs – ACT 3 Family

|                | PG207                                                            |  |  |  |

|----------------|------------------------------------------------------------------|--|--|--|

| A1460 Function | Location                                                         |  |  |  |

| CLKA or I/O    | К1                                                               |  |  |  |

| CLKB or I/O    | J3                                                               |  |  |  |

| DCLK or I/O    | E4                                                               |  |  |  |

| GND            | C14, D4, D5, D9, D14, J4, J14, P3, P4, P7, P9, P14, R15          |  |  |  |

| HCLK or I/O    | J15                                                              |  |  |  |

| IOCLK or I/O   | P5                                                               |  |  |  |

| IOPCL or I/O   | N14                                                              |  |  |  |

| MODE           | D7                                                               |  |  |  |

| NC             | A1, A2, A16, A17, B1, B17, C1, C2, S1, S3, S17, T1, T2, T16, T17 |  |  |  |

| PRA or I/O     | H1                                                               |  |  |  |

| PRB or I/O     | К16                                                              |  |  |  |

| SDI or I/O     | C3                                                               |  |  |  |

| SDO            | P15                                                              |  |  |  |

| VCC            | B2, B9, B16, D11, J2, J16, P12, S2, S9, S16, T5                  |  |  |  |

Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

# 4 – Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each version of the datasheet.

| Revision                       | Changes                                                                                                                                                                                                                                                                                                                                          | Page            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 3<br>(January 2012)   | The description for SDO pins had earlier been removed from the datasheet and has now been included again, in the "Pin Descriptions" section (SAR 35820).                                                                                                                                                                                         | 2-21            |

|                                | SDO pin numbers had earlier been removed from package pin assignment tables in the datasheet, and have now been restored to the pin tables (SAR 35820).                                                                                                                                                                                          | 3-1             |

| Revision 2<br>(September 2011) | The ACT 3 datasheet was formatted newly in the style used for current datasheets. The same information is present (other than noted in the list of changes for this revision) but divided into chapters.                                                                                                                                         | N/A             |

|                                | The datasheet was revised to note in multiple places that speed grades -2 and -3 have been discontinued. The following device/package combinations have been discontinued for all speed grades and temperatures (SAR 33872):<br>A1415 PG100<br>A1425 PG133<br>A1440 PG175<br>A1460 BG225<br>Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004. | I and<br>others |

|                                | The "Features" section was revised to state the clock-to-ouput time and on-chip performance for –1 speed grade as 9.0 ns and 186 MHz. The "General Description" section was revised in accordance (SAR 33872).                                                                                                                                   | I               |

|                                | The maximum performance values were updated in Table 1 • ACT 3 Family Product Information, and now reflect worst-case commercial for the -1 speed grade (SAR 33872).                                                                                                                                                                             | Ι               |

|                                | The "Product Plan" table was updated as follows to conform to current offerings (SAR 33872):<br>The A1415A device is offered in PL84, PG100, and VQ100 packages for Military application.<br>The A1440A device is offered in TQ176 and VQ100 packages for Industrial application.                                                                | 111             |

|                                | Table 1-1 • Chip-to-Chip Performance (worst-case commercial) was updated to include data for all speed grades instead of only –3 (SAR 33872).                                                                                                                                                                                                    | 1-2             |

|                                | Figure 1-1 • Predictable Performance (worst-case commercial, –1 speed grade) was revised to reflect values for the –1 speed grade (SAR 33872).                                                                                                                                                                                                   | 1-1             |

|                                | Figure 2-10 • Timing Model was updated to show data for the –1 speed grade instead of –3 (SAR 33872).                                                                                                                                                                                                                                            | 2-16            |

|                                | Table 2-14 • Logic Module and Routing Delay by Fanout (ns); Worst-Case Commercial Conditions was updated to include data for all speed grades instead of only –3 (SAR 33872).                                                                                                                                                                    | 2-20            |

|                                | Package names used in the "Package Pin Assignments" section and throughout the document were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                                                                 | 3-1             |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.