Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | 564                                                            |

| Number of Logic Elements/Cells | •                                                              |

| Total RAM Bits                 | •                                                              |

| Number of I/O                  | 100                                                            |

| Number of Gates                | 4000                                                           |

| Voltage - Supply               | 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 85°C (TA)                                              |

| Package / Case                 | 160-BQFP                                                       |

| Supplier Device Package        | 160-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1440a-1pqg160i |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Microsemi

Accelerator Series FPGAs - ACT 3 Family

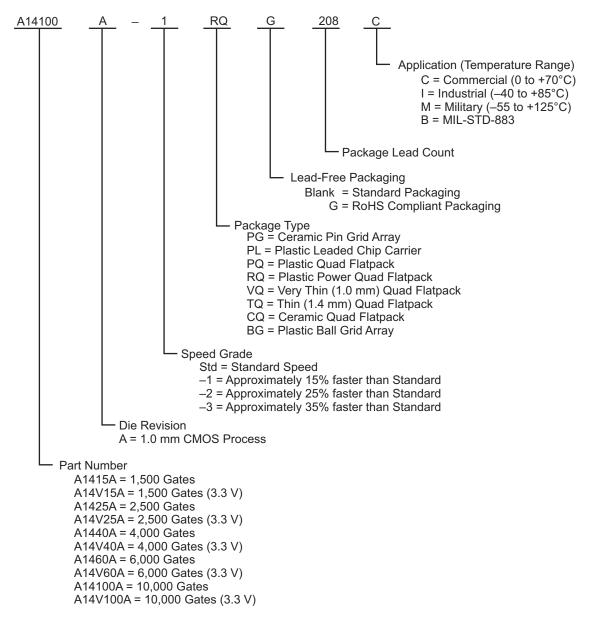

# **Ordering Information**

Notes:

- 1. The -2 and -3 speed grades have been discontinued.

- The Ceramic Pin Grid Array packages PG100, PG133, and PG175 have been discontinued in all device densities, speed grades, and temperature grades.

The Plastic Ball Grid Array package BG225 has been discontinued in all device densities (specifically for A1460A), all speed

- 3. The Plastic Ball Grid Array package BG225 has been discontinued in all device densities (specifically for A1460A), all speed grades, and all temperature grades.

- 4. Military Grade devices are no longer available for the A1440A device.

- For more information about discontinued devices, refer to the Product Discontinuation Notices (PDNs) listed below, available on the Microsemi SoC Products Group website: PDN March 2001

PDN March 20 PDN 0104 PDN 0203 PDN 0604 PDN 1004

ACT 3 Family Overview

| Device and Speed<br>Grade | t <sub>CKHS</sub> (ns) | t <sub>TRACE</sub> (ns) | t <sub>INSU</sub> (ns) | Total (ns) | MHz |

|---------------------------|------------------------|-------------------------|------------------------|------------|-----|

| A1425A -3                 | 7.5                    | 1.0                     | 1.8                    | 10.3       | 97  |

| A1460A -3                 | 9.0                    | 1.0                     | 1.3                    | 11.3       | 88  |

| A1425A -2                 | 7.5                    | 1.0                     | 2.0                    | 10.5       | 95  |

| A1460A -2                 | 9.0                    | 1.0                     | 1.5                    | 11.5       | 87  |

| A1425A -1                 | 9.0                    | 1.0                     | 2.3                    | 12.3       | 81  |

| A1460A -1                 | 10.0                   | 1.0                     | 1.8                    | 12.8       | 78  |

| A1425A STD                | 10.0                   | 1.0                     | 2.7                    | 13.7       | 73  |

| A1460A STD                | 11.5                   | 1.0                     | 2.0                    | 14.5       | 69  |

#### Table 1-1 • Chip-to-Chip Performance (worst-case commercial)

Note: The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

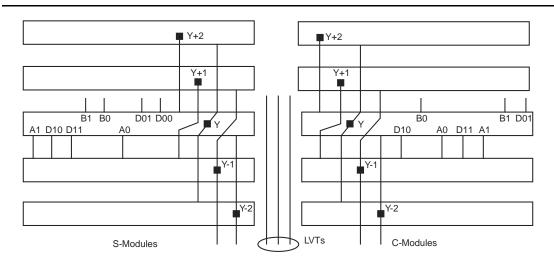

The I/O module output Y is used to bring Pad signals into the array or to feed the output register back into the array. This allows the output register to be used in high-speed state machine applications. Side I/O modules have a dedicated output segment for Y extending into the routing channels above and below (similar to logic modules). Top/Bottom I/O modules have no dedicated output segment. Signals coming into the chip from the top or bottom are routed using F-fuses and LVTs (F-fuses and LVTs are explained in detail in the routing section).

## I/O Pad Drivers

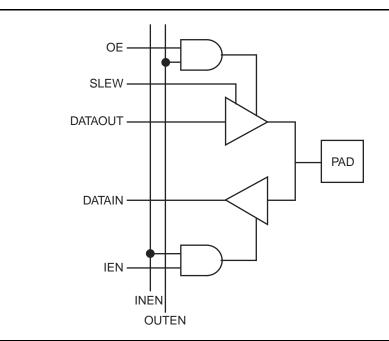

All pad drivers are capable of being tristate. Each buffer connects to an associated I/O module with four signals: OE (Output Enable), IE (Input Enable), DataOut, and DataIn. Certain special signals used only during programming and test also connect to the pad drivers: OUTEN (global output enable), INEN (global input enable), and SLEW (individual slew selection). See Figure 2-5.

*Figure 2-5* • Function Diagram for I/O Pad Driver

## **Special I/Os**

The special I/Os are of two types: temporary and permanent. Temporary special I/Os are used during programming and testing. They function as normal I/Os when the MODE pin is inactive. Permanent special I/Os are user programmed as either normal I/Os or special I/Os. Their function does not change once the device has been programmed. The permanent special I/Os consist of the array clock input buffers (CLKA and CLKB), the hard-wired array clock input buffer (HCLK), the hard-wired I/O clock input buffer (IOCLK), and the hard-wired I/O register preset/clear input buffer (IOPCL). Their function is determined by the I/O macros selected.

# **Clock Networks**

The ACT 3 architecture contains four clock networks: two high-performance dedicated clock networks and two general purpose routed networks. The high-performance networks function up to 200 MHz, while the general purpose routed networks function up to 150 MHz.

## **Antifuse Connections**

An antifuse is a "normally open" structure as opposed to the normally closed fuse structure used in PROMs or PALs. The use of antifuses to implement a programmable logic device results in highly testable structures as well as an efficient programming architecture. The structure is highly testable because there are no preexisting connections; temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed as well as isolate individual circuit structures to be tested. This can be done both before and after programming. For example, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

Four types of antifuse connections are used in the routing structure of the ACT 3 array. (The physical structure of the antifuse is identical in each case; only the usage differs.)

Table 2-1 shows four types of antifuses.

| Туре | Description                         |

|------|-------------------------------------|

| XF   | Horizontal-to-vertical connection   |

| HF   | Horizontal-to-horizontal connection |

| VF   | Vertical-to-vertical connection     |

| FF   | "Fast" vertical connection          |

Examples of all four types of connections are shown in Figure 2-7 on page 2-6 and Figure 2-8 on page 2-6.

## Module Interface

Connections to Logic and I/O modules are made through vertical segments that connect to the module inputs and outputs. These vertical segments lie on vertical tracks that span the entire height of the array.

#### Module Input Connections

The tracks dedicated to module inputs are segmented by pass transistors in each module row. During normal user operation, the pass transistors are inactive, which isolates the inputs of a module from the inputs of the module directly above or below it. During certain test modes, the pass transistors are active to verify the continuity of the metal tracks. Vertical input segments span only the channel above or the channel below. The logic modules are arranged such that half of the inputs are connected to the channel above and half of the inputs to segments in the channel below, as shown in Figure 2-9.

Figure 2-9 • Logic Module Routing Interface

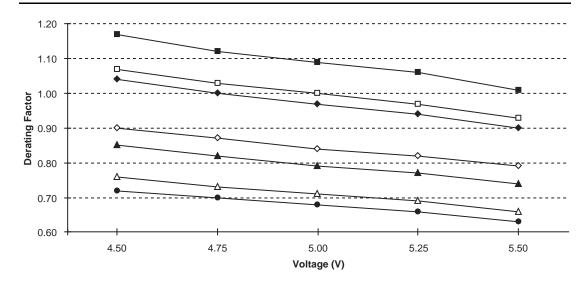

## **Timing Derating**

ACT 3 devices are manufactured in a CMOS process. Therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing.

#### Table 2-15 • Timing Derating Factor (Temperature and Voltage)

| (Commercial Minimum/Maximum Specification) x | Indus | strial | Military |      |  |

|----------------------------------------------|-------|--------|----------|------|--|

|                                              | Min.  | Max.   | Min.     | Max. |  |

|                                              | 0.66  | 1.07   | 0.63     | 1.17 |  |

#### Table 2-16 • Timing Derating Factor for Designs at Typical Temperature ( $T_J = 25^{\circ}C$ ) and Voltage (5.0 V)

| (Commercial Maximum Specification) x 0.85 |

|-------------------------------------------|

|-------------------------------------------|

#### Table 2-17 • Temperature and Voltage Derating Factors

(normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

|      | -55  | -40  | 0    | 25   | 70   | 85   | 125   |

|------|------|------|------|------|------|------|-------|

| 4.50 | 0.72 | 0.76 | 0.85 | 0.90 | 1.04 | 1.07 | 1.117 |

| 4.75 | 0.70 | 0.73 | 0.82 | 0.87 | 1.00 | 1.03 | 1.12  |

| 5.00 | 0.68 | 0.71 | 0.79 | 0.84 | 0.97 | 1.00 | 1.09  |

| 5.25 | 0.66 | 0.69 | 0.77 | 0.82 | 0.94 | 0.97 | 1.06  |

| 5.50 | 0.63 | 0.66 | 0.74 | 0.79 | 0.90 | 0.93 | 1.01  |

Note: This derating factor applies to all routing and propagation delays.

## A1425A, A14V25A Timing Characteristics (continued)

|                    |                                      | -3 S | beed <sup>1</sup> | –2 Speed <sup>1</sup> |      | -1 Speed |      | Std. Speed |      | 3.3 V Speed <sup>1</sup> |      | Units |

|--------------------|--------------------------------------|------|-------------------|-----------------------|------|----------|------|------------|------|--------------------------|------|-------|

|                    |                                      | Min. | Max.              | Min.                  | Max. | Min.     | Max. | Min.       | Max. | Min.                     | Max. |       |

| t <sub>INY</sub>   | Input Data Pad to Y                  |      | 2.8               |                       | 3.2  |          | 3.6  |            | 4.2  |                          | 5.5  | ns    |

| t <sub>ICKY</sub>  | Input Reg IOCLK Pad to Y             |      | 4.7               |                       | 5.3  |          | 6.0  |            | 7.0  |                          | 9.2  | ns    |

| t <sub>OCKY</sub>  | Output Reg IOCLK Pad to Y            |      | 4.7               |                       | 5.3  |          | 6.0  |            | 7.0  |                          | 9.2  | ns    |

| t <sub>ICLRY</sub> | Input Asynchronous Clear to Y        |      | 4.7               |                       | 5.3  |          | 6.0  |            | 7.0  |                          | 9.2  | ns    |

| t <sub>OCLRY</sub> | Output Asynchronous Clear to Y       |      | 4.7               |                       | 5.3  |          | 6.0  |            | 7.0  |                          | 9.2  | ns    |

| Predict            | ed Input Routing Delays <sup>2</sup> |      |                   |                       |      |          |      |            |      |                          |      |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                 |      | 0.9               |                       | 1.0  |          | 1.1  |            | 1.3  |                          | 1.7  | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                 |      | 1.2               |                       | 1.4  |          | 1.6  |            | 1.8  |                          | 2.4  | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                 |      | 1.4               |                       | 1.6  |          | 1.8  |            | 2.1  |                          | 2.8  | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                 |      | 1.7               |                       | 1.9  |          | 2.2  |            | 2.5  |                          | 3.3  | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                 |      | 2.8               |                       | 3.2  |          | 3.6  |            | 4.2  |                          | 5.5  | ns    |

| I/O Mod            | ule Sequential Timing (wrt IOCLK     | pad) |                   |                       |      |          |      |            |      |                          |      |       |

| t <sub>INH</sub>   | Input F-F Data Hold                  | 0.0  |                   | 0.0                   |      | 0.0      |      | 0.0        |      | 0.0                      |      | ns    |

| t <sub>INSU</sub>  | Input F-F Data Setup                 | 1.8  |                   | 2.0                   |      | 2.3      |      | 2.7        |      | 3.0                      |      | ns    |

| t <sub>IDEH</sub>  | Input Data Enable Hold               | 0.0  |                   | 0.0                   |      | 0.0      |      | 0.0        |      | 0.0                      |      | ns    |

| t <sub>IDESU</sub> | Input Data Enable Setup              | 5.8  |                   | 6.5                   |      | 7.5      |      | 8.6        |      | 8.6                      |      | ns    |

| t <sub>OUTH</sub>  | Output F-F Data hold                 | 0.7  |                   | 0.8                   |      | 0.9      |      | 1.0        |      | 1.0                      |      | ns    |

| t <sub>OUTSU</sub> | Output F-F Data Setup                | 0.7  |                   | 0.8                   |      | 0.9      |      | 1.0        |      | 1.0                      |      | ns    |

| t <sub>ODEH</sub>  | Output Data Enable Hold              | 0.3  |                   | 0.4                   |      | 0.4      |      | 0.5        |      | 0.5                      |      | ns    |

| f <sub>ODESU</sub> | Output Data Enable Setup             | 1.3  |                   | 1.5                   |      | 1.7      |      | 2.0        |      | 2.0                      |      | ns    |

Notes: \*

1. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

## A1440A, A14V40A Timing Characteristics (continued)

Table 2-28 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

|                    |                                        | -3 S | beed <sup>2</sup> | -2 Sp | beed <sup>2</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

|                    |                                        | Min. | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               | 1     |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 5.0               |       | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 8.0               |       | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 4.0               |       | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 8.5               |       | 8.5               |      | 9.5  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 11.3              |       | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.02              |       | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Moo            | dule – CMOS Output Timing <sup>1</sup> |      |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |      | 6.2               |       | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |      | 11.7              |       | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |      | 5.2               |       | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |      | 8.9               |       | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |      | 9.0               |       | 9.0               |      | 10.1 |      | 11.8  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |      | 13.0              |       | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |      | 0.04              |       | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |      | 0.07              |       | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |      | 0.03              |       | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

Notes:

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

## A1440A, A14V40A Timing Characteristics (continued)

| Table 2-29 • A1440A. | A14V40A Worst-Case                     | Commercial Conditions.                  | VCC = 4.75 V, T <sub>J</sub> = 70°C |

|----------------------|----------------------------------------|-----------------------------------------|-------------------------------------|

|                      | ////////////////////////////////////// | ••••••••••••••••••••••••••••••••••••••• |                                     |

|                      |                                                   | -3 Sp      | beed <sup>1</sup> | –2 Speed <sup>1</sup> |            | -1 Speed   |            | Std. Speed |            | 3.3 V Speed <sup>1</sup> |            | Units |

|----------------------|---------------------------------------------------|------------|-------------------|-----------------------|------------|------------|------------|------------|------------|--------------------------|------------|-------|

|                      |                                                   | Min.       | Max.              | Min.                  | Max.       | Min.       | Max.       | Min.       | Max.       | Min.                     | Max.       |       |

| t <sub>IOCKH</sub>   | Input Low to High (pad to I/O module input)       |            | 2.0               |                       | 2.3        |            | 2.6        |            | 3.0        |                          | 3.5        | ns    |

| t <sub>IOPWH</sub>   | Minimum Pulse Width High                          | 1.9        |                   | 2.4                   |            | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IPOWL</sub>   | Minimum Pulse Width Low                           | 1.9        |                   | 2.4                   |            | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IOSAPW</sub>  | Minimum Asynchronous Pulse Width                  | 1.9        |                   | 2.4                   |            | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>IOCKSW</sub>  | Maximum Skew                                      |            | 0.4               |                       | 0.4        |            | 0.4        |            | 0.4        |                          | 0.4        | ns    |

| t <sub>IOP</sub>     | Minimum Period                                    | 4.0        |                   | 5.0                   |            | 6.8        |            | 8.0        |            | 10.0                     |            | ns    |

| f <sub>IOMAX</sub>   | Maximum Frequency                                 |            | 250               |                       | 200        |            | 150        |            | 125        |                          | 100        | MHz   |

| Dedicate             | d (hardwired) Array Clock                         | •          |                   |                       | •          |            |            | •          | -          |                          |            |       |

| <sup>t</sup> нскн    | Input Low to High (pad to S-module input)         |            | 3.0               |                       | 3.4        |            | 3.9        |            | 4.5        |                          | 5.5        | ns    |

| t <sub>HCKL</sub>    | Input High to Low (pad to S-module input)         |            | 3.0               |                       | 3.4        |            | 3.9        |            | 4.5        |                          | 5.5        | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width High                          | 1.9        |                   | 2.4                   |            | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width Low                           | 1.9        |                   | 2.4                   |            | 3.3        |            | 3.8        |            | 4.8                      |            | ns    |

| t <sub>HCKSW</sub>   | Delta High to Low, Low Slew                       |            | 0.3               |                       | 0.3        |            | 0.3        |            | 0.3        |                          | 0.3        | ns    |

| t <sub>HP</sub>      | Minimum Period                                    | 4.0        |                   | 5.0                   |            | 6.8        |            | 8.0        |            | 10.0                     |            | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                 |            | 250               |                       | 200        |            | 150        |            | 125        |                          | 100        | MHz   |

| Routed A             | rray Clock Networks                               | •          |                   |                       |            |            |            | •          | -          |                          |            |       |

| t <sub>RCKH</sub>    | Input Low to High (FO = 64)                       |            | 3.7               |                       | 4.1        |            | 4.7        |            | 5.5        |                          | 9.0        | ns    |

| t <sub>RCKL</sub>    | Input High to Low (FO = 64)                       |            | 4.0               |                       | 4.5        |            | 5.1        |            | 6.0        |                          | 9.0        | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width High (FO = 64)                   | 3.3        |                   | 3.8                   |            | 4.2        |            | 4.9        |            | 6.5                      |            | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width Low (FO = 64)                    | 3.3        |                   | 3.8                   |            | 4.2        |            | 4.9        |            | 6.5                      |            | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew (FO = 128)                           |            | 0.7               |                       | 0.8        |            | 0.9        |            | 1.0        |                          | 1.0        | ns    |

| t <sub>RP</sub>      | Minimum Period (FO = 64)                          | 6.8        |                   | 8.0                   |            | 8.7        |            | 10.0       |            | 13.4                     |            | ns    |

| f <sub>RMAX</sub>    | Maximum Frequency (FO = 64)                       |            | 150               |                       | 125        |            | 115        |            | 100        |                          | 75         | MHz   |

| Clock-to-            | Clock Skews                                       | •          |                   |                       |            |            |            | •          | -          |                          |            |       |

| t <sub>IOHCKSW</sub> | I/O Clock to H-Clock Skew                         | 0.0        | 1.7               | 0.0                   | 1.8        | 0.0        | 2.0        | 0.0        | 2.2        | 0.0                      | 3.0        | ns    |

| t <sub>IORCKSW</sub> | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 144) | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0            | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 3.0<br>3.0 | ns    |

| t <sub>HRCKSW</sub>  | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 144)   | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0            | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0               | 1.0<br>3.0 | ns    |

Notes:

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

**Detailed Specifications**

## A1460A, A14V60A Timing Characteristics

Table 2-30 • A1460A, A14V60A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C<sup>1</sup>

| Logic Module Propagation Delays <sup>2</sup> |                                | -3 S | peed <sup>3</sup> | -2 Speed <sup>3</sup> -1 Speed St |      | Std. S | Std. Speed |      | 3.3 V Speed <sup>1</sup> |      |      |     |

|----------------------------------------------|--------------------------------|------|-------------------|-----------------------------------|------|--------|------------|------|--------------------------|------|------|-----|

| Parameter/Description                        |                                | Min. | Max.              | Min.                              | Max. | Min.   | Max.       | Min. | Max.                     | Min. | Max. |     |

| t <sub>PD</sub>                              | Internal Array Module          |      | 2.0               |                                   | 2.3  |        | 2.6        |      | 3.0                      |      | 3.9  | ns  |

| t <sub>CO</sub>                              | Sequential Clock to Q          |      | 2.0               |                                   | 2.3  |        | 2.6        |      | 3.0                      |      | 3.9  | ns  |

| t <sub>CLR</sub>                             | Asynchronous Clear to Q        |      | 2.0               |                                   | 2.3  |        | 2.6        |      | 3.0                      |      | 3.9  | ns  |

| Predict                                      | ed Routing Delays <sup>4</sup> |      |                   |                                   |      |        |            |      |                          |      |      |     |

| t <sub>RD1</sub>                             | FO = 1 Routing Delay           |      | 0.9               |                                   | 1.0  |        | 1.1        |      | 1.3                      |      | 1.7  | ns  |

| t <sub>RD2</sub>                             | FO = 2 Routing Delay           |      | 1.2               |                                   | 1.4  |        | 1.6        |      | 1.8                      |      | 2.4  | ns  |

| t <sub>RD3</sub>                             | FO = 3 Routing Delay           |      | 1.4               |                                   | 1.6  |        | 1.8        |      | 2.1                      |      | 2.8  | ns  |

| t <sub>RD4</sub>                             | FO = 4 Routing Delay           |      | 1.7               |                                   | 1.9  |        | 2.2        |      | 2.5                      |      | 3.3  | ns  |

| t <sub>RD8</sub>                             | FO = 8 Routing Delay           |      | 2.8               |                                   | 3.2  |        | 3.6        |      | 4.2                      |      | 5.5  | ns  |

| Logic N                                      | Iodule Sequential Timing       |      |                   |                                   |      |        |            |      |                          |      |      |     |

| t <sub>SUD</sub>                             | Flip-Flop Data Input Setup     | 0.5  |                   | 0.6                               |      | 0.7    |            | 0.8  |                          | 0.8  |      | ns  |

| t <sub>HD</sub>                              | Flip-Flop Data Input Hold      | 0.0  |                   | 0.0                               |      | 0.0    |            | 0.0  |                          | 0.0  |      | ns  |

| t <sub>SUD</sub>                             | Latch Data Input Setup         | 0.5  |                   | 0.6                               |      | 0.7    |            | 0.8  |                          | 0.8  |      | ns  |

| t <sub>HD</sub>                              | Latch Data Input Hold          | 0.0  |                   | 0.0                               |      | 0.0    |            | 0.0  |                          | 0.0  |      | ns  |

| t <sub>WASYN</sub>                           | Asynchronous Pulse Width       | 2.4  |                   | 3.2                               |      | 3.8    |            | 4.8  |                          | 6.5  |      | ns  |

| t <sub>WCLKA</sub>                           | Flip-Flop Clock Pulse Width    | 2.4  |                   | 3.2                               |      | 3.8    |            | 4.8  |                          | 6.5  |      | ns  |

| t <sub>A</sub>                               | Flip-Flop Clock Input Period   | 5.0  |                   | 6.8                               |      | 8.0    |            | 10.0 |                          | 13.4 |      | ns  |

| f <sub>MAX</sub>                             | Flip-Flop Clock Frequency      |      | 200               |                                   | 150  |        | 125        |      | 100                      |      | 75   | MHz |

Notes:

1. VCC = 3.0 V for 3.3 V specifications.

2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn} + t_{CO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

3. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

4. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

## **Pin Descriptions**

#### CLKA Clock A (Input)

Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### CLKB Clock B (Input)

Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### GND Ground

LOW supply voltage.

#### HCLK Dedicated (Hard-wired) Array Clock (Input)

Clock input for sequential modules. This input is directly wired to each S-Module and offers clock speeds independent of the number of S-Modules being driven. This pin can also be used as an I/O.

#### I/O Input/Output (Input, Output)

The I/O pin functions as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are tristated by the Designer Series software.

#### IOCLK Dedicated (Hard-wired) I/O Clock (Input)

Clock input for I/O modules. This input is directly wired to each I/O module and offers clock speeds independent of the number of I/O modules being driven. This pin can also be used as an I/O.

#### IOPCL Dedicated (Hard-wired) I/O Preset/Clear (Input)

Input for I/O preset or clear. This global input is directly wired to the preset and clear inputs of all I/O registers. This pin functions as an I/O when no I/O preset or clear macros are used.

#### MODE Mode (Input)

The MODE pin controls the use of diagnostic pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os. To provide Actionprobe capability, the MODE pin should be terminated to GND through a 10K resistor so that the MODE pin can be pulled high when required.

#### NC No Connection

This pin is not connected to circuitry within the device.

#### PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### PRB Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

| PL84       |                        |                        |                        |  |  |

|------------|------------------------|------------------------|------------------------|--|--|

| Pin Number | A1415, A14V15 Function | A1425, A14V25 Function | A1440, A14V40 Function |  |  |

| 1          | VCC                    | VCC                    | VCC                    |  |  |

| 2          | GND                    | GND                    | GND                    |  |  |

| 3          | VCC                    | VCC                    | VCC                    |  |  |

| 4          | PRA, I/O               | PRA, I/O               | PRA, I/O               |  |  |

| 11         | DCLK, I/O              | DCLK, I/O              | DCLK, I/O              |  |  |

| 12         | SDI, I/O               | SDI, I/O               | SDI, I/O               |  |  |

| 16         | MODE                   | MODE                   | MODE                   |  |  |

| 27         | GND                    | GND                    | GND                    |  |  |

| 28         | VCC                    | VCC                    | VCC                    |  |  |

| 40         | PRB, I/O               | PRB, I/O               | PRB, I/O               |  |  |

| 41         | VCC                    | VCC                    | VCC                    |  |  |

| 42         | GND                    | GND                    | GND                    |  |  |

| 43         | VCC                    | VCC                    | VCC                    |  |  |

| 45         | HCLK, I/O              | HCLK, I/O              | HCLK, I/O              |  |  |

| 52         | SDO                    | SDO                    | SDO                    |  |  |

| 53         | IOPCL, I/O             | IOPCL, I/O             | IOPCL, I/O             |  |  |

| 59         | VCC                    | VCC                    | VCC                    |  |  |

| 60         | VCC                    | VCC                    | VCC                    |  |  |

| 61         | GND                    | GND                    | GND                    |  |  |

| 68         | VCC                    | VCC                    | VCC                    |  |  |

| 69         | GND                    | GND                    | GND                    |  |  |

| 74         | IOCLK, I/O             | IOCLK, I/O             | IOCLK, I/O             |  |  |

| 83         | CLKA, I/O              | CLKA, I/O              | CLKA, I/O              |  |  |

| 84         | CLKB, I/O              | CLKB, I/O              | CLKB, I/O              |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

|            | PQ100          |                |  |  |  |  |  |

|------------|----------------|----------------|--|--|--|--|--|

| Pin Number | A1415 Function | A1425 Function |  |  |  |  |  |

| 2          | IOCLK, I/O     | IOCLK, I/O     |  |  |  |  |  |

| 14         | CLKA, I/O      | CLKA, I/O      |  |  |  |  |  |

| 15         | CLKB, I/O      | CLKB, I/O      |  |  |  |  |  |

| 16         | VCC            | VCC            |  |  |  |  |  |

| 17         | GND            | GND            |  |  |  |  |  |

| 18         | VCC            | VCC            |  |  |  |  |  |

| 19         | GND            | GND            |  |  |  |  |  |

| 20         | PRA, I/O       | PRA, I/O       |  |  |  |  |  |

| 27         | DCLK, I/O      | DCLK, I/O      |  |  |  |  |  |

| 28         | GND            | GND            |  |  |  |  |  |

| 29         | SDI, I/O       | SDI, I/O       |  |  |  |  |  |

| 34         | MODE           | MODE           |  |  |  |  |  |

| 35         | VCC            | VCC            |  |  |  |  |  |

| 36         | GND            | GND            |  |  |  |  |  |

| 47         | GND            | GND            |  |  |  |  |  |

| 48         | VCC            | VCC            |  |  |  |  |  |

| 61         | PRB, I/O       | PRB, I/O       |  |  |  |  |  |

| 62         | GND            | GND            |  |  |  |  |  |

| 63         | VCC            | VCC            |  |  |  |  |  |

| 64         | GND            | GND            |  |  |  |  |  |

| 65         | VCC            | VCC            |  |  |  |  |  |

| 67         | HCLK, I/O      | HCLK, I/O      |  |  |  |  |  |

| 77         | SDO            | SDO            |  |  |  |  |  |

| 78         | IOPCL, I/O     | IOPCL, I/O     |  |  |  |  |  |

| 79         | GND            | GND            |  |  |  |  |  |

| 85         | VCC            | VCC            |  |  |  |  |  |

| 86         | VCC            | VCC            |  |  |  |  |  |

| 87         | GND            | GND            |  |  |  |  |  |

| 96         | VCC            | VCC            |  |  |  |  |  |

| 97         | GND            | GND            |  |  |  |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

| PQ160      |                        |                        |                        |  |  |  |

|------------|------------------------|------------------------|------------------------|--|--|--|

| Pin Number | A1425, A14V25 Function | A1440, A14V40 Function | A1460, A14V60 Function |  |  |  |

| 1          | GND                    | GND                    | GND                    |  |  |  |

| 2          | SDI, I/O               | SDI, I/O               | SDI, I/O               |  |  |  |

| 5          | NC                     | I/O                    | I/O                    |  |  |  |

| 9          | MODE                   | MODE                   | MODE                   |  |  |  |

| 10         | VCC                    | VCC                    | VCC                    |  |  |  |

| 14         | NC                     | I/O                    | I/O                    |  |  |  |

| 15         | GND                    | GND                    | GND                    |  |  |  |

| 18         | VCC                    | VCC                    | VCC                    |  |  |  |

| 19         | GND                    | GND                    | GND                    |  |  |  |

| 20         | NC                     | I/O                    | I/O                    |  |  |  |

| 24         | NC                     | I/O                    | I/O                    |  |  |  |

| 27         | NC                     | I/O                    | I/O                    |  |  |  |

| 28         | VCC                    | VCC                    | VCC                    |  |  |  |

| 29         | VCC                    | VCC                    | VCC                    |  |  |  |

| 40         | GND                    | GND                    | GND                    |  |  |  |

| 41         | NC                     | I/O                    | I/O                    |  |  |  |

| 43         | NC                     | I/O                    | I/O                    |  |  |  |

| 45         | NC                     | I/O                    | I/O                    |  |  |  |

| 46         | VCC                    | VCC                    | VCC                    |  |  |  |

| 47         | NC                     | I/O                    | I/O                    |  |  |  |

| 49         | NC                     | I/O                    | I/O                    |  |  |  |

| 51         | NC                     | I/O                    | I/O                    |  |  |  |

| 53         | NC                     | I/O                    | I/O                    |  |  |  |

| 58         | PRB, I/O               | PRB, I/O               | PRB, I/O               |  |  |  |

| 59         | GND                    | GND                    | GND                    |  |  |  |

| 60         | VCC                    | VCC                    | VCC                    |  |  |  |

| 62         | HCLK, I/O              | HCLK, I/O              | HCLK, I/O              |  |  |  |

| 63         | GND                    | GND                    | GND                    |  |  |  |

| 74         | NC                     | I/O                    | I/O                    |  |  |  |

| 75         | VCC                    | VCC                    | VCC                    |  |  |  |

| 76         | NC                     | I/O                    | I/O                    |  |  |  |

| 77         | NC                     | I/O                    | I/O                    |  |  |  |

| 78         | NC                     | I/O                    | I/O                    |  |  |  |

| 79         | SDO                    | SDO                    | SDO                    |  |  |  |

| 80         | IOPCL, I/O             | IOPCL, I/O             | IOPCL, I/O             |  |  |  |

| 81         | GND                    | GND                    | GND                    |  |  |  |

| 90         | VCC                    | VCC                    | VCC                    |  |  |  |

| 91         | VCC                    | VCC                    | VCC                    |  |  |  |

Microsemi

Accelerator Series FPGAs - ACT 3 Family

|            | CQ196          |            | CQ196          |

|------------|----------------|------------|----------------|

| Pin Number | A1460 Function | Pin Number | A1460 Function |

| 1          | GND            | 101        | GND            |

| 2          | SDI, I/O       | 110        | VCC            |

| 11         | MODE           | 111        | VCC            |

| 12         | VCC            | 112        | GND            |

| 13         | GND            | 137        | VCC            |

| 37         | GND            | 138        | GND            |

| 38         | VCC            | 139        | GND            |

| 39         | VCC            | 140        | VCC            |

| 51         | GND            | 148        | IOCLK, I/O     |

| 52         | GND            | 149        | GND            |

| 59         | VCC            | 155        | VCC            |

| 64         | GND            | 162        | GND            |

| 77         | HCLK, I/O      | 172        | CLKA, I/O      |

| 79         | PRB, I/O       | 173        | CLKB, I/O      |

| 86         | GND            | 174        | PRA, I/O       |

| 94         | VCC            | 183        | GND            |

| 98         | GND            | 189        | VCC            |

| 99         | SDO            | 193        | GND            |

| 100        | IOPCL, I/O     | 196        | DCLK, I/O      |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

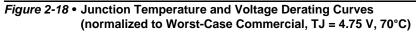

# CQ256

Note: This is the top view.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs - ACT 3 Family

|            | CQ256           |            | CQ256           |

|------------|-----------------|------------|-----------------|

| Pin Number | A14100 Function | Pin Number | A14100 Function |

| 1          | GND             | 141        | VCC             |

| 2          | SDI, I/O        | 158        | GND             |

| 11         | MODE            | 159        | VCC             |

| 28         | VCC             | 160        | GND             |

| 29         | GND             | 161        | VCC             |

| 30         | VCC             | 174        | VCC             |

| 31         | GND             | 175        | GND             |

| 46         | VCC             | 176        | GND             |

| 59         | GND             | 188        | IOCLK, I/O      |

| 90         | PRB, I/O        | 189        | GND             |

| 91         | GND             | 219        | CLKA, I/O       |

| 92         | VCC             | 220        | CLKB, I/O       |

| 93         | GND             | 221        | VCC             |

| 94         | VCC             | 222        | GND             |

| 96         | HCLK, I/O       | 223        | VCC             |

| 110        | GND             | 224        | GND             |

| 126        | SDO             | 225        | PRA, I/O        |

| 127        | IOPCL, I/O      | 240        | GND             |

| 128        | GND             | 256        | DCLK, I/O       |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Microsemi

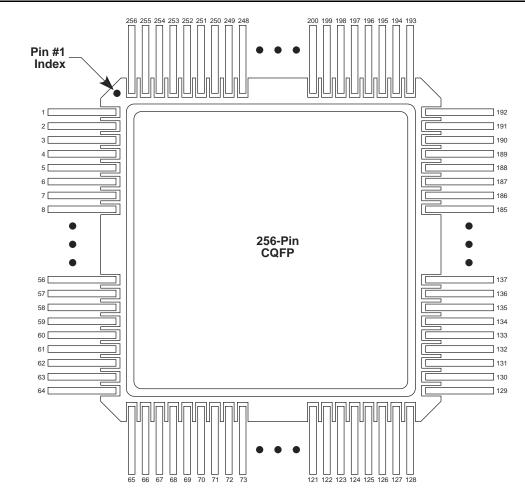

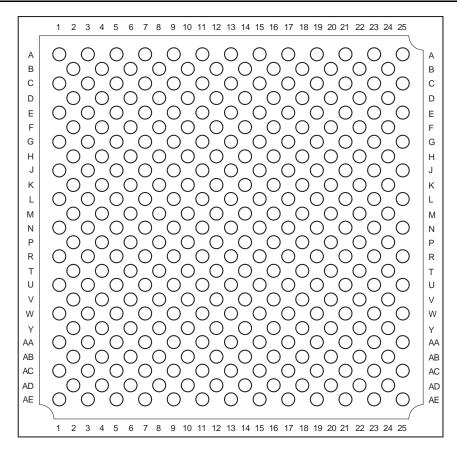

# BG313

#### Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Microsemi

Accelerator Series FPGAs – ACT 3 Family

|                             | BG313                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A14100, A14V100<br>Function | Location                                                                                                                                                                                                                                            |  |  |  |  |

| CLKA or I/O                 | J13                                                                                                                                                                                                                                                 |  |  |  |  |

| CLKB or I/O                 | G13                                                                                                                                                                                                                                                 |  |  |  |  |

| DCLK or I/O                 | B2                                                                                                                                                                                                                                                  |  |  |  |  |

| GND                         | A1, A25, AD2, AE25, J21, L13, M12, M14, N11, N13, N15, P12, P14, R13                                                                                                                                                                                |  |  |  |  |

| HCLK or I/O                 | T14                                                                                                                                                                                                                                                 |  |  |  |  |

| IOCLK or I/O                | B24                                                                                                                                                                                                                                                 |  |  |  |  |

| IOPCL or I/O                | AD24                                                                                                                                                                                                                                                |  |  |  |  |

| MODE                        | G3                                                                                                                                                                                                                                                  |  |  |  |  |

| NC                          | A3, A13, A23, AA5, AA9, AA23, AB2, AB4, AB20, AC13, AC25, AD22, AE1, AE21, B14, C5, C25, D4, D24, E3, E21, F6, F10, F16, G1, G25, H18, H24, J1, J7, J25, K12, L15, L17, M6, N1, N5, N7, N21, N23, P20, R11, T6, T8, U9, U13, U21, V16, W7, Y20, Y24 |  |  |  |  |

| PRA or I/O                  | H12                                                                                                                                                                                                                                                 |  |  |  |  |

| PRB or I/O                  | AD12                                                                                                                                                                                                                                                |  |  |  |  |

| SDI or I/O                  | C1                                                                                                                                                                                                                                                  |  |  |  |  |

| SDO                         | AE23                                                                                                                                                                                                                                                |  |  |  |  |

| VCC                         | AB18, AD6, AE13, C13, C19, E13, G9, H22, K8, K20, M16, N3, N9, N25, U5, W13, V2, V22, V24                                                                                                                                                           |  |  |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Datasheet Information

| Revision                  | Changes                                                                                                                                      | Page |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 2<br>(continued) | In the "Package Pin Assignments" section, notes were added to the pin tables for the following packages, stating that they are discontinued: |      |

|                           | "BG225"                                                                                                                                      | 3-20 |

|                           | "PG100"                                                                                                                                      | 3-24 |

|                           | "PG133"                                                                                                                                      | 3-26 |

|                           | "PG175"                                                                                                                                      | 3-28 |

| Revision 1<br>(June 2006) | RoHS compliant information was added to the "Ordering Information" section.                                                                  | II   |

# **Datasheet Categories**

## Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

## **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Production

This version contains information that is considered to be final.

## **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.