Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 564                                                          |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | -                                                            |

| Number of I/O                  | 83                                                           |

| Number of Gates                | 4000                                                         |

| Voltage - Supply               | 4.5V ~ 5.5V                                                  |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 100-TQFP                                                     |

| Supplier Device Package        | 100-VQFP (14x14)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1440a-vq100c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

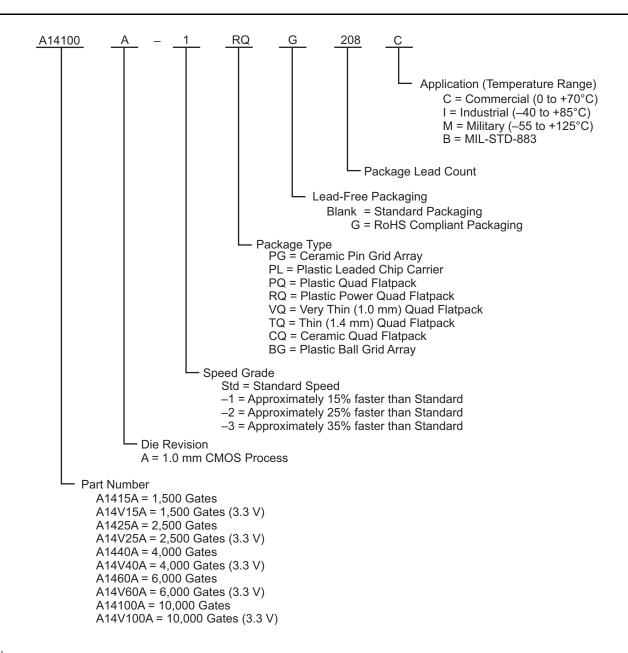

# **Ordering Information**

#### Notes:

- 1. The –2 and –3 speed grades have been discontinued.

- The Ceramic Pin Grid Array packages PG100, PG133, and PG175 have been discontinued in all device densities, speed grades, and temperature grades.

3. The Plastic Ball Grid Array package BG225 has been discontinued in all device densities (specifically for A1460A), all speed

- grades, and all temperature grades.

- 4. Military Grade devices are no longer available for the A1440A device.

- 5. For more information about discontinued devices, refer to the Product Discontinuation Notices (PDNs) listed below, available on the Microsemi SoC Products Group website:

PDN March 2001 PDN 0104 PDN 0203

PDN 0604 PDN 1004

**Revision 3**

### **Product Plan**

|                                           |      | Speed | Grade <sup>1</sup> |    |          | Applic | ation <sup>1</sup> |   |

|-------------------------------------------|------|-------|--------------------|----|----------|--------|--------------------|---|

| Device/Package                            | Std. | -1    | -2                 | -3 | С        | I      | М                  | В |

| A1415A Device                             | •    | •     |                    | •  | •        | •      | •                  | • |

| 84-Pin Plastic Leaded Chip Carrier (PLCC) | ✓    | ✓     | D                  | D  | ✓        | 1      | 1                  | _ |

| 100-Pin Plastic Quad Flatpack (PQFP)      | 1    | ✓     | D                  | D  | ✓        | ✓      | ✓                  | - |

| 100-Pin Very Thin Quad Flatpack (VQFP)    | 1    | ✓     | D                  | D  | ✓        | 1      | ✓                  | - |

| 100-Pin Ceramic Pin Grid Array (CPGA)     | D    | D     | D                  | D  | D        | _      | _                  | - |

| A14V15A Device                            |      |       |                    |    |          |        |                    |   |

| 84-Pin Plastic Leaded Chip Carrier (PLCC) | ✓    | -     | _                  | _  | ✓        | _      | -                  | _ |

| 100-Pin Very Thin Quad Flatpack (VQFP)    | ✓    | -     | -                  | _  | ✓        | -      | -                  | _ |

| A1425A Device                             |      |       |                    |    |          |        | •                  | • |

| 84-Pin Plastic Leaded Chip Carrier (PLCC) | ✓    | ✓     | D                  | D  | ✓        | 1      |                    |   |

| 100-Pin Plastic Quad Flatpack (PQFP)      | 1    | ✓     | D                  | D  | ✓        | 1      | -                  | - |

| 100-Pin Very Thin Quad Flatpack (VQFP)    | 1    | 1     | D                  | D  | ✓        | ✓      | -                  | _ |

| 132-Pin Ceramic Quad Flatpack (CQFP)      | ✓    | ✓     | -                  | _  | ✓        | -      | ✓                  | 1 |

| 133-Pin Ceramic Pin Grid Array (CPGA)     | D    | D     | D                  | D  | D        | _      | D                  | D |

| 160-Pin Plastic Quad Flatpack (PQFP)      | ✓    | ✓     | D                  | D  | ✓        | 1      | -                  | _ |

| A14V25A Device                            |      |       |                    |    |          |        |                    |   |

| 84-Pin Plastic Leaded Chip Carrier (PLCC) | ✓    | -     | _                  | _  | ✓        | _      | _                  | - |

| 100-Pin Very Thin Quad Flatpack (VQFP)    | 1    | -     | -                  | _  | ✓        | -      | -                  | - |

| 160-Pin Plastic Quad Flatpack (PQFP)      | 1    | -     | _                  | _  | ✓        | -      | -                  | - |

| A1440A Device                             |      | .•    |                    |    |          |        |                    |   |

| 84-Pin Plastic Leaded Chip Carrier (PLCC) | ✓    | ✓     | D                  | D  | ✓        | 1      | _                  | _ |

| 100-Pin Very Thin Quad Flatpack (VQFP)    | ✓    | 1     | D                  | D  | ✓        | ✓      | -                  | - |

| 160-Pin Plastic Quad Flatpack (PQFP)      | 1    | 1     | D                  | D  | <b>✓</b> | ✓      | -                  | - |

| 175-Pin Ceramic Pin Grid Array (CPGA)     | D    | D     | D                  | D  | D        | -      | -                  | - |

| 176-Pin Thin Quad Flatpack (TQFP)         | ✓    | ✓     | D                  | D  | ✓        | 1      | -                  | - |

#### Notes:

1. Applications: C = Commercial I = Industrial M = Military

2. Commercial only

Availability: **√** = Available P = Planned-= Not planned D = Discontinued

Speed Grade:

-1 = Approx. 15% faster than Std.

-2 = Approx. 25% faster than Std.

-3 = Approx. 35% faster than Std.

(-2 and -3 speed grades have been discontinued.)

Revision 3 Ш

ACT 3 Family Overview

Table 1-1 • Chip-to-Chip Performance (worst-case commercial)

| Device and Speed Grade | t <sub>CKHS</sub> (ns) | t <sub>TRACE</sub> (ns) | t <sub>INSU</sub> (ns) | Total (ns) | MHz |

|------------------------|------------------------|-------------------------|------------------------|------------|-----|

| A1425A -3              | 7.5                    | 1.0                     | 1.8                    | 10.3       | 97  |

| A1460A -3              | 9.0                    | 1.0                     | 1.3                    | 11.3       | 88  |

| A1425A -2              | 7.5                    | 1.0                     | 2.0                    | 10.5       | 95  |

| A1460A -2              | 9.0                    | 1.0                     | 1.5                    | 11.5       | 87  |

| A1425A -1              | 9.0                    | 1.0                     | 2.3                    | 12.3       | 81  |

| A1460A -1              | 10.0                   | 1.0                     | 1.8                    | 12.8       | 78  |

| A1425A STD             | 10.0                   | 1.0                     | 2.7                    | 13.7       | 73  |

| A1460A STD             | 11.5                   | 1.0                     | 2.0                    | 14.5       | 69  |

Note: The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

1-2 Revision 3

### **Determining Average Switching Frequency**

To determine the switching frequency for a design, you must have a detailed understanding of the data input values to the circuit. The following guidelines are meant to represent worst-case scenarios so that they can be generally used to predict the upper limits of power dissipation. These guidelines are as follows:

Table 2-13 • Guidelines for Predicting Power Dissipation

| Data                                         | Value                     |

|----------------------------------------------|---------------------------|

| Logic Modules (m)                            | 80% of modules            |

| Inputs switching (n)                         | # inputs/4                |

| Outputs switching (p)                        | # output/4                |

| First routed array clock loads (q1)          | 40% of sequential modules |

| Second routed array clock loads (q2)         | 40% of sequential modules |

| Load capacitance (CL)                        | 35 pF                     |

| Average logic module switching rate (fm)     | F/10                      |

| Average input switching rate (fn)            | F/5                       |

| Average output switching rate (fp)           | F/10                      |

| Average first routed array clock rate (fq1)  | F/2                       |

| Average second routed array clock rate (fq2) | F/2                       |

| Average dedicated array clock rate (fs1)     | F                         |

| Average dedicated I/O clock rate (fs2)       | F                         |

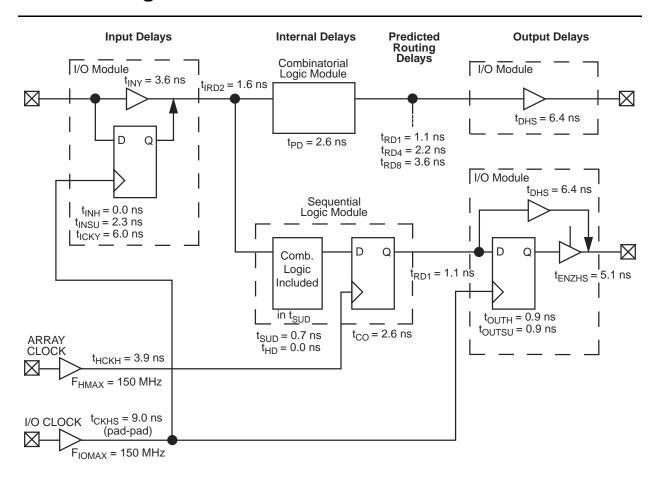

# **ACT 3 Timing Model**

Note: Values shown for A1425A -1 speed grade device.

Figure 2-10 • Timing Model

2-16 Revision 3

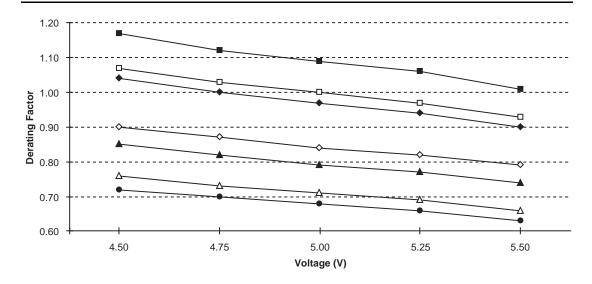

### **Timing Derating**

ACT 3 devices are manufactured in a CMOS process. Therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing.

Table 2-15 • Timing Derating Factor (Temperature and Voltage)

| (Commercial Minimum/Maximum Specification) x | Indus | strial | Mili | tary |

|----------------------------------------------|-------|--------|------|------|

|                                              | Min.  | Max.   | Min. | Max. |

|                                              | 0.66  | 1.07   | 0.63 | 1.17 |

Table 2-16 • Timing Derating Factor for Designs at Typical Temperature ( $T_J = 25$ °C) and Voltage (5.0 V)

| (Commercial Maximum Specification) x | 0.85 |

|--------------------------------------|------|

|--------------------------------------|------|

Table 2-17 • Temperature and Voltage Derating Factors (normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

|      | -55  | -40  | 0    | 25   | 70   | 85   | 125   |

|------|------|------|------|------|------|------|-------|

| 4.50 | 0.72 | 0.76 | 0.85 | 0.90 | 1.04 | 1.07 | 1.117 |

| 4.75 | 0.70 | 0.73 | 0.82 | 0.87 | 1.00 | 1.03 | 1.12  |

| 5.00 | 0.68 | 0.71 | 0.79 | 0.84 | 0.97 | 1.00 | 1.09  |

| 5.25 | 0.66 | 0.69 | 0.77 | 0.82 | 0.94 | 0.97 | 1.06  |

| 5.50 | 0.63 | 0.66 | 0.74 | 0.79 | 0.90 | 0.93 | 1.01  |

Note: This derating factor applies to all routing and propagation delays.

Figure 2-18 • Junction Temperature and Voltage Derating Curves (normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

### A1415A, A14V15A Timing Characteristics (continued)

Table 2-19 • A1415A, A14V15A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Mod            | dule Input Propagation Delays        | -3 S <sub>I</sub> | peed <sup>1</sup> | -2 Sp | peed <sup>1</sup> | -1 S | peed | Std. | Speed | 3.3 V | Speed <sup>2</sup> | Units |

|--------------------|--------------------------------------|-------------------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                     | Min.              | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               |       |

| t <sub>INY</sub>   | Input Data Pad to Y                  |                   | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |       | 5.5                | ns    |

| t <sub>ICKY</sub>  | Input Reg IOCLK Pad to Y             |                   | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>OCKY</sub>  | Output Reg IOCLK Pad to Y            |                   | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>ICLRY</sub> | Input Asynchronous Clear to Y        |                   | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| t <sub>OCLRY</sub> | Output Asynchronous Clear to Y       |                   | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |       | 9.2                | ns    |

| Predict            | ed Input Routing Delays <sup>2</sup> |                   |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                 |                   | 0.9               |       | 1.0               |      | 1.1  |      | 1.3   |       | 1.7                | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                 |                   | 1.2               |       | 1.4               |      | 1.6  |      | 1.8   |       | 2.4                | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                 |                   | 1.4               |       | 1.6               |      | 1.8  |      | 2.1   |       | 2.8                | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                 |                   | 1.7               |       | 1.9               |      | 2.2  |      | 2.5   |       | 3.3                | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                 |                   | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |       | 5.5                | ns    |

| I/O Mod            | dule Sequential Timing (wrt IOCLK    | pad)              | •                 |       |                   | •    |      |      |       |       |                    |       |

| t <sub>INH</sub>   | Input F-F Data Hold                  | 0.0               |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0   |                    | ns    |

| t <sub>INSU</sub>  | Input F-F Data Setup                 | 2.0               |                   | 2.3   |                   | 2.5  |      | 3.0  |       | 3.0   |                    | ns    |

| t <sub>IDEH</sub>  | Input Data Enable Hold               | 0.0               |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0   |                    | ns    |

| t <sub>IDESU</sub> | Input Data Enable Setup              | 5.8               |                   | 6.5   |                   | 7.5  |      | 8.6  |       | 8.6   |                    | ns    |

| t <sub>OUTH</sub>  | Output F-F Data hold                 | 0.7               |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0   |                    | ns    |

| t <sub>OUTSU</sub> | Output F-F Data Setup                | 0.7               |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0   |                    | ns    |

| t <sub>ODEH</sub>  | Output Data Enable Hold              | 0.3               |                   | 0.4   |                   | 0.4  |      | 0.5  |       | 0.5   |                    | ns    |

| f <sub>ODESU</sub> | Output Data Enable Setup             | 1.3               |                   | 1.5   |                   | 1.7  |      | 2.0  |       | 2.0   |                    | ns    |

| Notos:             | 1                                    |                   |                   |       |                   |      |      |      |       |       |                    |       |

#### Notes:

1. The -2 and -3 speed grades have been discontinued. Please refer to the Product Discontinuation Notices (PDNs) listed below:

PDN March 2001

PDN 0104

PDN 0203

PDN 0604

PDN 1004

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

### A1415A, A14V15A Timing Characteristics (continued)

Table 2-20 • A1415A, A14V15A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J = 70^{\circ}$ C

| I/O Mod            | lule – TTL Output Timing <sup>1</sup>  | -3 Sp | peed <sup>2</sup> | -2 S | peed <sup>2</sup> | -1 S | peed | Std. | Speed | 3.3 V | Units |       |

|--------------------|----------------------------------------|-------|-------------------|------|-------------------|------|------|------|-------|-------|-------|-------|

| Parame             | eter/Description                       | Min.  | Max.              | Min. | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.  |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |       | 5.0               |      | 5.6               |      | 6.4  |      | 7.5   |       | 9.8   | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |       | 8.0               |      | 9.0               |      | 10.2 |      | 12.0  |       | 15.6  | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |       | 4.0               |      | 4.5               |      | 5.1  |      | 6.0   |       | 7.8   | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |       | 7.4               |      | 8.3               |      | 9.4  |      | 11.0  |       | 14.3  | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |       | 6.5               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0  | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |       | 6.5               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0  | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |       | 7.5               |      | 7.5               |      | 9.0  |      | 10.0  |       | 13.0  | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |       | 11.3              |      | 11.3              |      | 13.5 |      | 15.0  |       | 19.5  | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |       | 0.02              |      | 0.02              |      | 0.03 |      | 0.03  |       | 0.04  | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |       | 0.05              |      | 0.05              |      | 0.06 |      | 0.07  |       | 0.09  | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |       | 0.04              |      | 0.04              |      | 0.04 |      | 0.05  |       | 0.07  | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |       | 0.05              |      | 0.05              |      | 0.06 |      | 0.07  |       | 0.09  | ns/pF |

| I/O Mod            | lule – CMOS Output Timing <sup>1</sup> |       |                   |      |                   |      |      |      |       |       |       |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |       | 6.2               |      | 7.0               |      | 7.9  |      | 9.3   |       | 12.1  | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |       | 11.7              |      | 13.1              |      | 14.9 |      | 17.5  |       | 22.8  | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |       | 5.2               |      | 5.9               |      | 6.6  |      | 7.8   |       | 10.1  | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |       | 8.9               |      | 10.0              |      | 11.3 |      | 13.3  |       | 17.3  | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |       | 6.7               |      | 7.5               |      | 8.5  |      | 10.0  |       | 13.0  | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |       | 6.7               |      | 7.5               |      | 9.0  |      | 10.0  |       | 13.0  | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |       | 8.9               |      | 8.9               |      | 10.7 |      | 11.8  |       | 15.3  | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |       | 13.0              |      | 13.0              |      | 15.6 |      | 17.3  |       | 22.5  | ns    |

| $d_TLHHS$          | Delta Low to High, High Slew           |       | 0.04              |      | 0.04              |      | 0.05 |      | 0.06  |       | 0.08  | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |       | 0.07              |      | 0.08              |      | 0.09 |      | 0.11  |       | 0.14  | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |       | 0.03              |      | 0.03              |      | 0.03 |      | 0.04  |       | 0.05  | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |       | 0.04              |      | 0.04              |      | 0.04 |      | 0.05  |       | 0.07  | ns/pF |

#### Notes:

1. Delays based on 35 pF loading.

2. The -2 and -3 speed grades have been discontinued. Please refer to the Product Discontinuation Notices (PDNs) listed below:

PDN March 2001

PDN 0104

PDN 0203

PDN 0604

PDN 1004

2-24 Revision 3

**Detailed Specifications**

### A1440A, A14V40A Timing Characteristics

Table 2-26 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C<sup>1</sup>

| Logic N            | Module Propagation Delays <sup>2</sup> | -3 Sp | peed 3 | -2 S <sub>l</sub> | peed <sup>3</sup> | -1 S | peed | Std. S | peed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|-------|--------|-------------------|-------------------|------|------|--------|------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min.  | Max.   | Min.              | Max.              | Min. | Max. | Min.   | Max. | Min.  | Max.               |       |

| t <sub>PD</sub>    | Internal Array Module                  |       | 2.0    |                   | 2.3               |      | 2.6  |        | 3.0  |       | 3.9                | ns    |

| t <sub>CO</sub>    | Sequential Clock to Q                  |       | 2.0    |                   | 2.3               |      | 2.6  |        | 3.0  |       | 3.9                | ns    |

| t <sub>CLR</sub>   | Asynchronous Clear to Q                |       | 2.0    |                   | 2.3               |      | 2.6  |        | 3.0  |       | 3.9                | ns    |

| Predict            | ed Routing Delays <sup>4</sup>         |       |        |                   |                   |      | •    |        |      |       |                    |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                   |       | 0.9    |                   | 1.0               |      | 1.1  |        | 1.3  |       | 1.7                | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                   |       | 1.2    |                   | 1.4               |      | 1.6  |        | 1.8  |       | 2.4                | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                   |       | 1.4    |                   | 1.6               |      | 1.8  |        | 2.1  |       | 2.8                | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                   |       | 1.7    |                   | 1.9               |      | 2.2  |        | 2.5  |       | 3.3                | ns    |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                   |       | 2.8    |                   | 3.2               |      | 3.6  |        | 4.2  |       | 5.5                | ns    |

| Logic N            | Module Sequential Timing               |       |        |                   |                   |      | •    |        |      |       |                    |       |

| t <sub>SUD</sub>   | Flip-Flop Data Input Setup             | 0.5   |        | 0.6               |                   | 0.7  |      | 0.8    |      | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Flip-Flop Data Input Hold              | 0.0   |        | 0.0               |                   | 0.0  |      | 0.0    |      | 0.0   |                    | ns    |

| t <sub>SUD</sub>   | Latch Data Input Setup                 | 0.5   |        | 0.6               |                   | 0.7  |      | 0.8    |      | 0.8   |                    | ns    |

| t <sub>HD</sub>    | Latch Data Input Hold                  | 0.0   |        | 0.0               |                   | 0.0  |      | 0.0    |      | 0.0   |                    | ns    |

| t <sub>WASYN</sub> | Asynchronous Pulse Width               | 1.9   |        | 2.4               |                   | 3.2  |      | 3.8    |      | 4.8   |                    | ns    |

| t <sub>WCLKA</sub> | Flip-Flop Clock Pulse Width            | 1.9   |        | 2.4               |                   | 3.2  |      | 3.8    |      | 4.8   |                    | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period           | 4.0   |        | 5.0               |                   | 6.8  |      | 8.0    |      | 10.0  |                    | ns    |

| f <sub>MAX</sub>   | Flip-Flop Clock Frequency              |       | 250    |                   | 200               |      | 150  |        | 125  |       | 100                | MHz   |

#### Notes:

- 1. VCC = 3.0 V for 3.3 V specifications.

- 2. For dual-module macros, use  $t_{PD} + t_{RD1} + t_{PDn} + t_{CO} + t_{RD1} + t_{PDn}$  or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

- 3. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

- 4. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

2-30 Revision 3

**Detailed Specifications**

### A1440A, A14V40A Timing Characteristics (continued)

Table 2-28 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Mod            | dule – TTL Output Timing <sup>1</sup>  | -3 Sp | oeed <sup>2</sup> | -2 Sp | peed <sup>2</sup> | -1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|--------------------|----------------------------------------|-------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parame             | eter/Description                       | Min.  | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |       | 5.0               |       | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |       | 8.0               |       | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |       | 4.0               |       | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |       | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |       | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |       | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |       | 8.5               |       | 8.5               |      | 9.5  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |       | 11.3              |       | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub> | Delta Low to High, High Slew           |       | 0.02              |       | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |       | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |       | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub> | Delta High to Low, Low Slew            |       | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Mod            | dule – CMOS Output Timing <sup>1</sup> |       |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>   | Data to Pad, High Slew                 |       | 6.2               |       | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>   | Data to Pad, Low Slew                  |       | 11.7              |       | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub> | Enable to Pad, Z to H/L, High Slew     |       | 5.2               |       | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub> | Enable to Pad, Z to H/L, Low Slew      |       | 8.9               |       | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub> | Enable to Pad, H/L to Z, High Slew     |       | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENLSZ</sub> | Enable to Pad, H/L to Z, Low Slew      |       | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>CKHS</sub>  | IOCLK Pad to Pad H/L, High Slew        |       | 9.0               |       | 9.0               |      | 10.1 |      | 11.8  |       | 14.3               | ns    |

| t <sub>CKLS</sub>  | IOCLK Pad to Pad H/L, Low Slew         |       | 13.0              |       | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| $d_{TLHHS}$        | Delta Low to High, High Slew           |       | 0.04              |       | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub> | Delta Low to High, Low Slew            |       | 0.07              |       | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub> | Delta High to Low, High Slew           |       | 0.03              |       | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| $d_{THLLS}$        | Delta High to Low, Low Slew            |       | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

#### Notes:

2-32 Revision 3

<sup>1.</sup> Delays based on 35 pF loading.

<sup>2.</sup> The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

### A1440A, A14V40A Timing Characteristics (continued)

Table 2-29 • A1440A, A14V40A Worst-Case Commercial Conditions, VCC = 4.75 V,  $T_J = 70^{\circ}$ C

| Dedicate             | d (hardwired) I/O Clock Network                   | –3 Sp      | eed <sup>1</sup> | –2 Sp      | oeed <sup>1</sup> | –1 S       | peed       | Std.       | Speed      | 3.3 V      | Speed <sup>1</sup> | Units |

|----------------------|---------------------------------------------------|------------|------------------|------------|-------------------|------------|------------|------------|------------|------------|--------------------|-------|

| Paramete             | er/Description                                    | Min.       | Max.             | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.       | Max.               |       |

| t <sub>IOCKH</sub>   | Input Low to High (pad to I/O module input)       |            | 2.0              |            | 2.3               |            | 2.6        |            | 3.0        |            | 3.5                | ns    |

| t <sub>IOPWH</sub>   | Minimum Pulse Width High                          | 1.9        |                  | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8        |                    | ns    |

| t <sub>IPOWL</sub>   | Minimum Pulse Width Low                           | 1.9        |                  | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8        |                    | ns    |

| t <sub>IOSAPW</sub>  | Minimum Asynchronous Pulse Width                  | 1.9        |                  | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8        |                    | ns    |

| t <sub>iocksw</sub>  | Maximum Skew                                      |            | 0.4              |            | 0.4               |            | 0.4        |            | 0.4        |            | 0.4                | ns    |

| t <sub>IOP</sub>     | Minimum Period                                    | 4.0        |                  | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0       |                    | ns    |

| f <sub>IOMAX</sub>   | Maximum Frequency                                 |            | 250              |            | 200               |            | 150        |            | 125        |            | 100                | MHz   |

| Dedicate             | d (hardwired) Array Clock                         |            |                  |            |                   |            |            |            |            |            |                    |       |

| t <sub>HCKH</sub>    | Input Low to High (pad to S-module input)         |            | 3.0              |            | 3.4               |            | 3.9        |            | 4.5        |            | 5.5                | ns    |

| t <sub>HCKL</sub>    | Input High to Low (pad to S-module input)         |            | 3.0              |            | 3.4               |            | 3.9        |            | 4.5        |            | 5.5                | ns    |

| t <sub>HPWH</sub>    | Minimum Pulse Width High                          | 1.9        |                  | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8        |                    | ns    |

| t <sub>HPWL</sub>    | Minimum Pulse Width Low                           | 1.9        |                  | 2.4        |                   | 3.3        |            | 3.8        |            | 4.8        |                    | ns    |

| t <sub>HCKSW</sub>   | Delta High to Low, Low Slew                       |            | 0.3              |            | 0.3               |            | 0.3        |            | 0.3        |            | 0.3                | ns    |

| t <sub>HP</sub>      | Minimum Period                                    | 4.0        |                  | 5.0        |                   | 6.8        |            | 8.0        |            | 10.0       |                    | ns    |

| f <sub>HMAX</sub>    | Maximum Frequency                                 |            | 250              |            | 200               |            | 150        |            | 125        |            | 100                | MHz   |

| Routed A             | rray Clock Networks                               |            |                  |            |                   |            |            |            |            |            |                    |       |

| t <sub>RCKH</sub>    | Input Low to High (FO = 64)                       |            | 3.7              |            | 4.1               |            | 4.7        |            | 5.5        |            | 9.0                | ns    |

| t <sub>RCKL</sub>    | Input High to Low (FO = 64)                       |            | 4.0              |            | 4.5               |            | 5.1        |            | 6.0        |            | 9.0                | ns    |

| t <sub>RPWH</sub>    | Min. Pulse Width High (FO = 64)                   | 3.3        |                  | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5        |                    | ns    |

| t <sub>RPWL</sub>    | Min. Pulse Width Low (FO = 64)                    | 3.3        |                  | 3.8        |                   | 4.2        |            | 4.9        |            | 6.5        |                    | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew (FO = 128)                           |            | 0.7              |            | 0.8               |            | 0.9        |            | 1.0        |            | 1.0                | ns    |

| t <sub>RP</sub>      | Minimum Period (FO = 64)                          | 6.8        |                  | 8.0        |                   | 8.7        |            | 10.0       |            | 13.4       |                    | ns    |

| f <sub>RMAX</sub>    | Maximum Frequency (FO = 64)                       |            | 150              |            | 125               |            | 115        |            | 100        |            | 75                 | MHz   |

| Clock-to-            | Clock Skews                                       |            |                  |            |                   |            |            |            |            |            |                    |       |

| t <sub>IOHCKSW</sub> | I/O Clock to H-Clock Skew                         | 0.0        | 1.7              | 0.0        | 1.8               | 0.0        | 2.0        | 0.0        | 2.2        | 0.0        | 3.0                | ns    |

| t <sub>IORCKSW</sub> | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 144) | 0.0<br>0.0 | 1.0<br>3.0       | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 3.0<br>3.0         | ns    |

| t <sub>HRCKSW</sub>  | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 144)   | 0.0<br>0.0 | 1.0<br>3.0       | 0.0<br>0.0 | 1.0<br>3.0        | 0.0        | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0         | ns    |

#### Notes:

<sup>1.</sup> The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

<sup>2.</sup> Delays based on 35 pF loading.

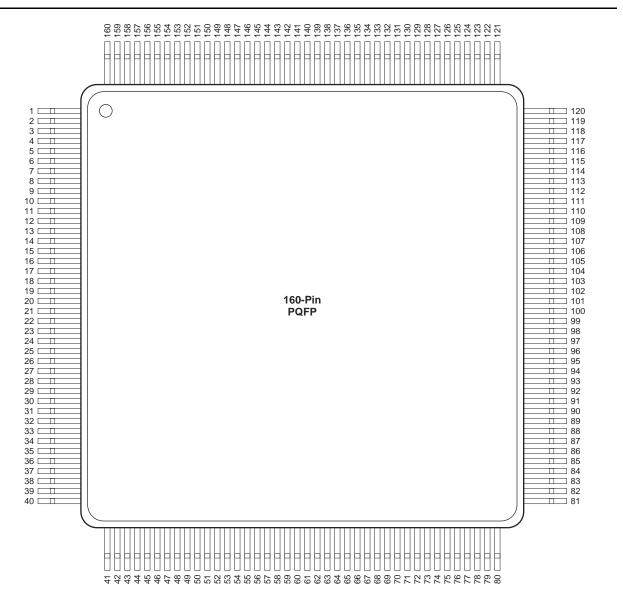

### **PQ160**

Note: This is the top view of the package

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Package Pin Assignments

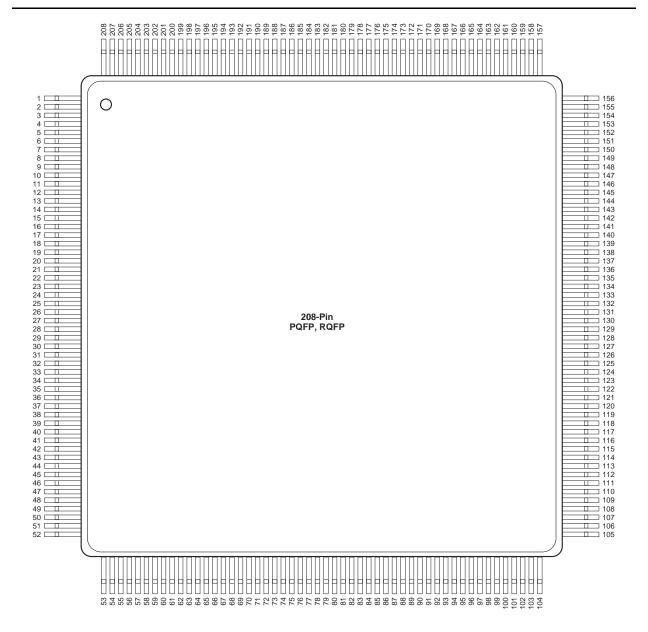

# PQ208, RQ208

Note: This is the top view of the package

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-8 Revision 3

|            | PQ208, RQ20               | 8                           |

|------------|---------------------------|-----------------------------|

| Pin Number | A1460, A14V60<br>Function | A14100, A14V100<br>Function |

| 1          | GND                       | GND                         |

| 2          | SDI, I/O                  | SDI, I/O                    |

| 11         | MODE                      | MODE                        |

| 12         | VCC                       | VCC                         |

| 25         | VCC                       | VCC                         |

| 26         | GND                       | GND                         |

| 27         | VCC                       | VCC                         |

| 28         | GND                       | GND                         |

| 40         | VCC                       | VCC                         |

| 41         | VCC                       | VCC                         |

| 52         | GND                       | GND                         |

| 53         | NC                        | I/O                         |

| 60         | VCC                       | VCC                         |

| 65         | NC                        | I/O                         |

| 76         | PRB, I/O                  | PRB, I/O                    |

| 77         | GND                       | GND                         |

| 78         | VCC                       | VCC                         |

| 79         | GND                       | GND                         |

| 80         | VCC                       | VCC                         |

| 82         | HCLK, I/O                 | HCLK, I/O                   |

| 98         | VCC                       | VCC                         |

| 102        | NC                        | I/O                         |

| 103        | SDO                       | SDO                         |

| 104        | IOPCL, I/O                | IOPCL, I/O                  |

| 105        | GND                       | GND                         |

| 114        | VCC                       | VCC                         |

| PQ208, RQ208 |                           |                             |  |  |

|--------------|---------------------------|-----------------------------|--|--|

| Pin Number   | A1460, A14V60<br>Function | A14100, A14V100<br>Function |  |  |

| 115          | VCC                       | VCC                         |  |  |

| 116          | NC                        | I/O                         |  |  |

| 129          | GND                       | GND                         |  |  |

| 130          | VCC                       | VCC                         |  |  |

| 131          | GND                       | GND                         |  |  |

| 132          | VCC                       | VCC                         |  |  |

| 145          | VCC                       | VCC                         |  |  |

| 146          | GND                       | GND                         |  |  |

| 147          | NC                        | I/O                         |  |  |

| 148          | VCC                       | VCC                         |  |  |

| 156          | IOCLK, I/O                | IOCLK, I/O                  |  |  |

| 157          | GND                       | GND                         |  |  |

| 158          | NC                        | I/O                         |  |  |

| 164          | VCC                       | VCC                         |  |  |

| 180          | CLKA, I/O                 | CLKA, I/O                   |  |  |

| 181          | CLKB, I/O                 | CLKB, I/O                   |  |  |

| 182          | VCC                       | VCC                         |  |  |

| 183          | GND                       | GND                         |  |  |

| 184          | VCC                       | VCC                         |  |  |

| 185          | GND                       | GND                         |  |  |

| 186          | PRA, I/O                  | PRA, I/O                    |  |  |

| 195          | NC                        | I/O                         |  |  |

| 201          | VCC                       | VCC                         |  |  |

| 205          | NC                        | I/O                         |  |  |

| 208          | DCLK, I/O                 | DCLK, I/O                   |  |  |

### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

| VQ100      |                        |                        |                        |  |

|------------|------------------------|------------------------|------------------------|--|

| Pin Number | A1415, A14V15 Function | A1425, A14V25 Function | A1440, A14V40 Function |  |

| 1          | GND                    | GND                    | GND                    |  |

| 2          | SDI, I/O               | SDI, I/O               | SDI, I/O               |  |

| 7          | MODE                   | MODE                   | MODE                   |  |

| 8          | VCC                    | VCC                    | VCC                    |  |

| 9          | GND                    | GND                    | GND                    |  |

| 20         | VCC                    | VCC                    | VCC                    |  |

| 21         | NC                     | I/O                    | I/O                    |  |

| 34         | PRB, I/O               | PRB, I/O               | PRB, I/O               |  |

| 35         | VCC                    | VCC                    | VCC                    |  |

| 36         | GND                    | GND                    | GND                    |  |

| 37         | VCC                    | VCC                    | VCC                    |  |

| 39         | HCLK, I/O              | HCLK, I/O              | HCLK, I/O              |  |

| 49         | SDO                    | SDO                    | SDO                    |  |

| 50         | IOPCL, I/O             | IOPCL, I/O             | IOPCL, I/O             |  |

| 51         | GND                    | GND                    | GND                    |  |

| 57         | VCC                    | VCC                    | VCC                    |  |

| 58         | VCC                    | VCC                    | VCC                    |  |

| 67         | VCC                    | VCC                    | VCC                    |  |

| 68         | GND                    | GND                    | GND                    |  |

| 69         | GND                    | GND                    | GND                    |  |

| 74         | NC                     | I/O                    | I/O                    |  |

| 75         | IOCLK, I/O             | IOCLK, I/O             | IOCLK, I/O             |  |

| 87         | CLKA, I/O              | CLKA, I/O              | CLKA, I/O              |  |

| 88         | CLKB, I/O              | CLKB, I/O              | CLKB, I/O              |  |

| 89         | VCC                    | VCC                    | VCC                    |  |

| 90         | VCC                    | VCC                    | VCC                    |  |

| 91         | GND                    | GND                    | GND                    |  |

| 92         | PRA, I/O               | PRA, I/O               | PRA, I/O               |  |

| 93         | NC                     | I/O                    | I/O                    |  |

| 100        | DCLK, I/O              | DCLK, I/O              | DCLK, I/O              |  |

### Notes:

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Package Pin Assignments

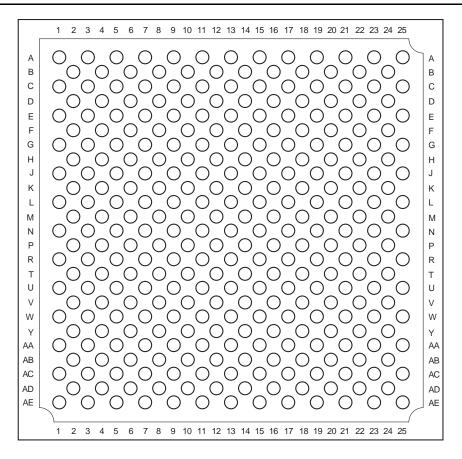

### **BG313**

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-22 Revision 3

Package Pin Assignments

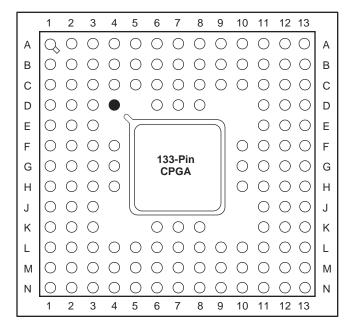

### **PG133**

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

3-26 Revision 3

# 4 - Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each version of the datasheet.

| Revision                       | Changes                                                                                                                                                                                                                                                                                                                            | Page            |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 3<br>(January 2012)   | The description for SDO pins had earlier been removed from the datasheet and has now been included again, in the "Pin Descriptions" section (SAR 35820).                                                                                                                                                                           | 2-21            |

|                                | SDO pin numbers had earlier been removed from package pin assignment tables in the datasheet, and have now been restored to the pin tables (SAR 35820).                                                                                                                                                                            | 3-1             |

| Revision 2<br>(September 2011) | The ACT 3 datasheet was formatted newly in the style used for current datasheets. The same information is present (other than noted in the list of changes for this revision) but divided into chapters.                                                                                                                           | N/A             |

|                                | The datasheet was revised to note in multiple places that speed grades –2 and –3 have been discontinued. The following device/package combinations have been discontinued for all speed grades and temperatures (SAR 33872):  A1415 PG100 A1425 PG133 A1440 PG175 A1460 BG225 Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004. | I and<br>others |

|                                | The "Features" section was revised to state the clock-to-ouput time and on-chip performance for -1 speed grade as 9.0 ns and 186 MHz. The "General Description" section was revised in accordance (SAR 33872).                                                                                                                     | I               |

|                                | The maximum performance values were updated in Table 1 • ACT 3 Family Product Information, and now reflect worst-case commercial for the -1 speed grade (SAR 33872).                                                                                                                                                               | I               |

|                                | The "Product Plan" table was updated as follows to conform to current offerings (SAR 33872):  The A1415A device is offered in PL84, PG100, and VQ100 packages for Military application.  The A1440A device is offered in TQ176 and VQ100 packages for Industrial application.                                                      | III             |

|                                | Table 1-1 • Chip-to-Chip Performance (worst-case commercial) was updated to include data for all speed grades instead of only –3 (SAR 33872).                                                                                                                                                                                      | 1-2             |

|                                | Figure 1-1 • Predictable Performance (worst-case commercial, -1 speed grade) was revised to reflect values for the -1 speed grade (SAR 33872).                                                                                                                                                                                     | 1-1             |

|                                | Figure 2-10 • Timing Model was updated to show data for the -1 speed grade instead of -3 (SAR 33872).                                                                                                                                                                                                                              | 2-16            |

|                                | Table 2-14 • Logic Module and Routing Delay by Fanout (ns); Worst-Case Commercial Conditions was updated to include data for all speed grades instead of only –3 (SAR 33872).                                                                                                                                                      | 2-20            |

|                                | Package names used in the "Package Pin Assignments" section and throughout the document were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                                                   | 3-1             |