Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | 848                                                            |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 131                                                            |

| Number of Gates                | 6000                                                           |

| Voltage - Supply               | 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 160-BQFP                                                       |

| Supplier Device Package        | 160-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a1460a-1pqg160c |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – ACT 3 Family Overview

# **General Description**

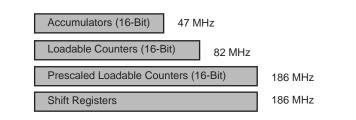

Microsemi's ACT 3 Accelerator Series of FPGAs offers the industry's fastest high-capacity programmable logic device. ACT 3 FPGAs offer a high performance, PCI compliant programmable solution capable of 186 MHz on-chip performance and 9.0 nanosecond clock-to-output (-1 speed grade), with capacities spanning from 1,500 to 10,000 gate array equivalent gates.

The ACT 3 family builds on the proven two-module architecture consisting of combinatorial and sequential logic modules used in Microsemi's 3200DX and 1200XL families. In addition, the ACT 3 I/O modules contain registers which deliver 9.0 nanosecond clock-to-out times (-1 speed grade). The devices contain four clock distribution networks, including dedicated array and I/O clocks, supporting very fast synchronous and asynchronous designs. In addition, routed clocks can be used to drive high fanout signals such as flip-flop resets and output.

The ACT 3 family is supported by Microsemi's Designer Series Development System which offers automatic placement and routing (with automatic or fixed pin assignments), static timing analysis, user programming, and debug and diagnostic probe capabilities.

*Figure 1-1* • Predictable Performance (worst-case commercial, –1 speed grade)

# System Performance Model

**Detailed Specifications**

# **Power Dissipation**

P = [ICC standby + lactive] \* VCC \* IOL \* VOL \* N + IOH\* (VCC - VOH) \* M

where:

EQ 3

ICC standby is the current flowing when no inputs or outputs are changing

lactive is the current flowing due to CMOS switching.

IOL and IOH are TTL sink/source current.

VOL and VOH are TTL level output voltages.

N is the number of outputs driving TTL loads to VOL.

M equals the number of outputs driving TTL loads to VOH.

An accurate determination of N and M is problematical because their values depend on the design and on the system I/O. The power can be divided into two components: static and active.

## **Static Power Component**

Microsemi FPGAs have small static power components that result in lower power dissipation than PALs or PLDs. By integrating multiple PALs/PLDs into one FPGA, an even greater reduction in board-level power dissipation can be achieved.

The power due to standby current is typically a small component of the overall power. Standby power is calculated in Table 2-9 for commercial, worst case conditions.

#### Table 2-9 • Standby Power Calculation

| ICC  | VCC    | Power   |

|------|--------|---------|

| 2 mA | 5.25 V | 10.5 mW |

The static power dissipated by TTL loads depends on the number of outputs driving high or low and the DC load current. Again, this value is typically small. For instance, a 32-bit bus sinking 4 mA at 0.33 V will generate 42 mW with all outputs driving low, and 140 mW with all outputs driving high. The actual dissipation will average somewhere between as I/Os switch states with time.

# **Active Power Component**

Power dissipation in CMOS devices is usually dominated by the active (dynamic) power dissipation. This component is frequency dependent, a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitance due to PC board traces and load device inputs.

An additional component of the active power dissipation is the totem-pole current in CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

# **Equivalent Capacitance**

The power dissipated by a CMOS circuit can be expressed by EQ 4.

Power ( $\mu$ W) = C<sub>EQ</sub> \* VCC<sup>2</sup> \* F

EQ 4

Where:

$C_{EQ}$  is the equivalent capacitance expressed in pF.

VCC is the power supply in volts.

F is the switching frequency in MHz.

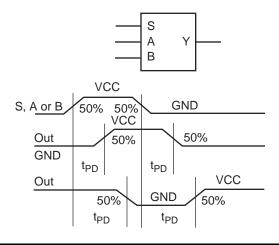

## Figure 2-14 • Module Delays

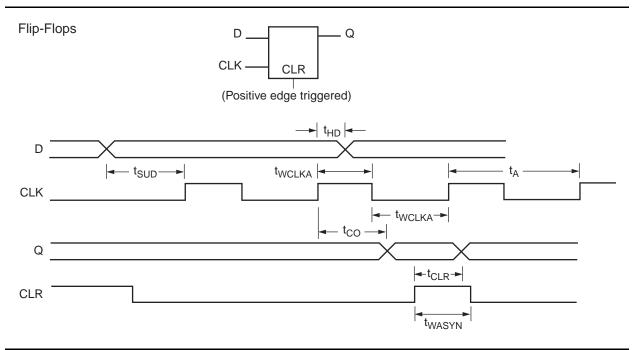

#### Figure 2-15 • Sequential Module Timing Characteristics

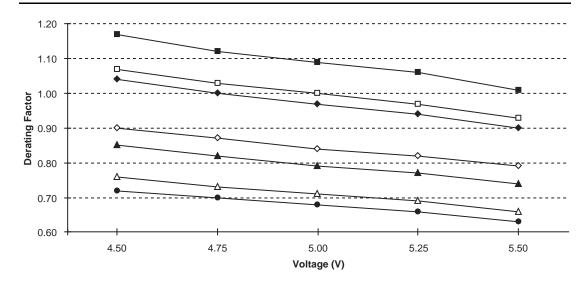

# **Timing Derating**

ACT 3 devices are manufactured in a CMOS process. Therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing.

#### Table 2-15 • Timing Derating Factor (Temperature and Voltage)

| (Commercial Minimum/Maximum Specification) x | Indus     | strial | Mili | tary |

|----------------------------------------------|-----------|--------|------|------|

|                                              | Min. Max. |        | Min. | Max. |

|                                              | 0.66      | 1.07   | 0.63 | 1.17 |

#### Table 2-16 • Timing Derating Factor for Designs at Typical Temperature ( $T_J = 25^{\circ}C$ ) and Voltage (5.0 V)

| (Commercial Maximum Specification) x 0.85 |

|-------------------------------------------|

|-------------------------------------------|

#### Table 2-17 • Temperature and Voltage Derating Factors

(normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

|      | -55  | -40  | 0    | 25   | 70   | 85   | 125   |

|------|------|------|------|------|------|------|-------|

| 4.50 | 0.72 | 0.76 | 0.85 | 0.90 | 1.04 | 1.07 | 1.117 |

| 4.75 | 0.70 | 0.73 | 0.82 | 0.87 | 1.00 | 1.03 | 1.12  |

| 5.00 | 0.68 | 0.71 | 0.79 | 0.84 | 0.97 | 1.00 | 1.09  |

| 5.25 | 0.66 | 0.69 | 0.77 | 0.82 | 0.94 | 0.97 | 1.06  |

| 5.50 | 0.63 | 0.66 | 0.74 | 0.79 | 0.90 | 0.93 | 1.01  |

Note: This derating factor applies to all routing and propagation delays.

## A1425A, A14V25A Timing Characteristics (continued)

| I/O Module Input Propagation Delays |                                      |      | beed <sup>1</sup> | -2 Sp | beed <sup>1</sup> | –1 S | peed | Std. | Speed | d 3.3 V Speed <sup>1</sup> |      | Units |

|-------------------------------------|--------------------------------------|------|-------------------|-------|-------------------|------|------|------|-------|----------------------------|------|-------|

| Parameter/Description               |                                      | Min. | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.                       | Max. |       |

| t <sub>INY</sub>                    | Input Data Pad to Y                  |      | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |                            | 5.5  | ns    |

| t <sub>ICKY</sub>                   | Input Reg IOCLK Pad to Y             |      | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |                            | 9.2  | ns    |

| t <sub>OCKY</sub>                   | Output Reg IOCLK Pad to Y            |      | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |                            | 9.2  | ns    |

| t <sub>ICLRY</sub>                  | Input Asynchronous Clear to Y        |      | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |                            | 9.2  | ns    |

| t <sub>OCLRY</sub>                  | Output Asynchronous Clear to Y       |      | 4.7               |       | 5.3               |      | 6.0  |      | 7.0   |                            | 9.2  | ns    |

| Predict                             | ed Input Routing Delays <sup>2</sup> |      |                   |       |                   |      |      |      |       |                            |      |       |

| t <sub>RD1</sub>                    | FO = 1 Routing Delay                 |      | 0.9               |       | 1.0               |      | 1.1  |      | 1.3   |                            | 1.7  | ns    |

| t <sub>RD2</sub>                    | FO = 2 Routing Delay                 |      | 1.2               |       | 1.4               |      | 1.6  |      | 1.8   |                            | 2.4  | ns    |

| t <sub>RD3</sub>                    | FO = 3 Routing Delay                 |      | 1.4               |       | 1.6               |      | 1.8  |      | 2.1   |                            | 2.8  | ns    |

| t <sub>RD4</sub>                    | FO = 4 Routing Delay                 |      | 1.7               |       | 1.9               |      | 2.2  |      | 2.5   |                            | 3.3  | ns    |

| t <sub>RD8</sub>                    | FO = 8 Routing Delay                 |      | 2.8               |       | 3.2               |      | 3.6  |      | 4.2   |                            | 5.5  | ns    |

| I/O Mod                             | ule Sequential Timing (wrt IOCLK     | pad) |                   |       |                   |      |      |      |       |                            |      |       |

| t <sub>INH</sub>                    | Input F-F Data Hold                  | 0.0  |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0                        |      | ns    |

| t <sub>INSU</sub>                   | Input F-F Data Setup                 | 1.8  |                   | 2.0   |                   | 2.3  |      | 2.7  |       | 3.0                        |      | ns    |

| t <sub>IDEH</sub>                   | Input Data Enable Hold               | 0.0  |                   | 0.0   |                   | 0.0  |      | 0.0  |       | 0.0                        |      | ns    |

| t <sub>IDESU</sub>                  | Input Data Enable Setup              | 5.8  |                   | 6.5   |                   | 7.5  |      | 8.6  |       | 8.6                        |      | ns    |

| t <sub>OUTH</sub>                   | Output F-F Data hold                 | 0.7  |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0                        |      | ns    |

| t <sub>OUTSU</sub>                  | Output F-F Data Setup                | 0.7  |                   | 0.8   |                   | 0.9  |      | 1.0  |       | 1.0                        |      | ns    |

| t <sub>ODEH</sub>                   | Output Data Enable Hold              | 0.3  |                   | 0.4   |                   | 0.4  |      | 0.5  |       | 0.5                        |      | ns    |

| f <sub>ODESU</sub>                  | Output Data Enable Setup             | 1.3  |                   | 1.5   |                   | 1.7  |      | 2.0  |       | 2.0                        |      | ns    |

Notes: \*

1. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual worst-case performance. Post-route timing is based on actual routing delay measurements performed on the device prior to shipment.

**Detailed Specifications**

## A1425A, A14V25A Timing Characteristics (continued)

Table 2-24 • A1425A, A14V25A Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C

| I/O Module – TTL Output Timing <sup>1</sup> |                                        |      | beed <sup>2</sup> | -2 Sp | beed <sup>2</sup> | –1 S | peed | Std. | Speed | 3.3 V | Speed <sup>1</sup> | Units |

|---------------------------------------------|----------------------------------------|------|-------------------|-------|-------------------|------|------|------|-------|-------|--------------------|-------|

| Parameter/Description                       |                                        | Min. | Max.              | Min.  | Max.              | Min. | Max. | Min. | Max.  | Min.  | Max.               | 1     |

| t <sub>DHS</sub>                            | Data to Pad, High Slew                 |      | 5.0               |       | 5.6               |      | 6.4  |      | 7.5   |       | 9.8                | ns    |

| t <sub>DLS</sub>                            | Data to Pad, Low Slew                  |      | 8.0               |       | 9.0               |      | 10.2 |      | 12.0  |       | 15.6               | ns    |

| t <sub>ENZHS</sub>                          | Enable to Pad, Z to H/L, High Slew     |      | 4.0               |       | 4.5               |      | 5.1  |      | 6.0   |       | 7.8                | ns    |

| t <sub>ENZLS</sub>                          | Enable to Pad, Z to H/L, Low Slew      |      | 7.4               |       | 8.3               |      | 9.4  |      | 11.0  |       | 14.3               | ns    |

| t <sub>ENHSZ</sub>                          | Enable to Pad, H/L to Z, High Slew     |      | 6.5               |       | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

| t <sub>ENLSZ</sub>                          | Enable to Pad, H/L to Z, Low Slew      |      | 6.5               |       | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

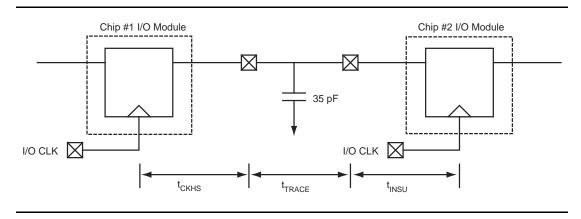

| t <sub>CKHS</sub>                           | IOCLK Pad to Pad H/L, High Slew        |      | 7.5               |       | 7.5               |      | 9.0  |      | 10.0  |       | 13.0               | ns    |

| t <sub>CKLS</sub>                           | IOCLK Pad to Pad H/L, Low Slew         |      | 11.3              |       | 11.3              |      | 13.5 |      | 15.0  |       | 19.5               | ns    |

| d <sub>TLHHS</sub>                          | Delta Low to High, High Slew           |      | 0.02              |       | 0.02              |      | 0.03 |      | 0.03  |       | 0.04               | ns/pF |

| d <sub>TLHLS</sub>                          | Delta Low to High, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| d <sub>THLHS</sub>                          | Delta High to Low, High Slew           |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

| d <sub>THLLS</sub>                          | Delta High to Low, Low Slew            |      | 0.05              |       | 0.05              |      | 0.06 |      | 0.07  |       | 0.09               | ns/pF |

| I/O Moo                                     | dule – CMOS Output Timing <sup>1</sup> |      |                   |       |                   |      |      |      |       |       |                    |       |

| t <sub>DHS</sub>                            | Data to Pad, High Slew                 |      | 6.2               |       | 7.0               |      | 7.9  |      | 9.3   |       | 12.1               | ns    |

| t <sub>DLS</sub>                            | Data to Pad, Low Slew                  |      | 11.7              |       | 13.1              |      | 14.9 |      | 17.5  |       | 22.8               | ns    |

| t <sub>ENZHS</sub>                          | Enable to Pad, Z to H/L, High Slew     |      | 5.2               |       | 5.9               |      | 6.6  |      | 7.8   |       | 10.1               | ns    |

| t <sub>ENZLS</sub>                          | Enable to Pad, Z to H/L, Low Slew      |      | 8.9               |       | 10.0              |      | 11.3 |      | 13.3  |       | 17.3               | ns    |

| t <sub>ENHSZ</sub>                          | Enable to Pad, H/L to Z, High Slew     |      | 6.7               |       | 7.5               |      | 8.5  |      | 10.0  |       | 13.0               | ns    |

| t <sub>ENLSZ</sub>                          | Enable to Pad, H/L to Z, Low Slew      |      | 6.7               |       | 7.5               |      | 9.0  |      | 10.0  |       | 13.0               | ns    |

| t <sub>CKHS</sub>                           | IOCLK Pad to Pad H/L, High Slew        |      | 8.9               |       | 8.9               |      | 10.7 |      | 11.8  |       | 15.3               | ns    |

| t <sub>CKLS</sub>                           | IOCLK Pad to Pad H/L, Low Slew         |      | 13.0              |       | 13.0              |      | 15.6 |      | 17.3  |       | 22.5               | ns    |

| d <sub>TLHHS</sub>                          | Delta Low to High, High Slew           |      | 0.04              |       | 0.04              |      | 0.05 |      | 0.06  |       | 0.08               | ns/pF |

| d <sub>TLHLS</sub>                          | Delta Low to High, Low Slew            |      | 0.07              |       | 0.08              |      | 0.09 |      | 0.11  |       | 0.14               | ns/pF |

| d <sub>THLHS</sub>                          | Delta High to Low, High Slew           |      | 0.03              |       | 0.03              |      | 0.03 |      | 0.04  |       | 0.05               | ns/pF |

| d <sub>THLLS</sub>                          | Delta High to Low, Low Slew            |      | 0.04              |       | 0.04              |      | 0.04 |      | 0.05  |       | 0.07               | ns/pF |

Notes: \*

1. Delays based on 35 pF loading.

2. The –2 and –3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

## A1460A, A14V60A Timing Characteristics (continued)

| Table 2-33 • A1460A. | A14V60A Worst-Case Con | nmercial Conditions. V | CC = 4.75 V. T <sub>1</sub> = 70°C |

|----------------------|------------------------|------------------------|------------------------------------|

| 10010 E 00 1114001   |                        |                        | 00 = 4000, $1 = 100$               |

| Dedicate              | d (hardwired) I/O Clock Network                   | —3 Sp      | beed <sup>1</sup> | -2 Sp      | beed <sup>1</sup> | –1 S       | peed       | Std. Speed |            | 3.3 V      | Speed <sup>1</sup> | Units |

|-----------------------|---------------------------------------------------|------------|-------------------|------------|-------------------|------------|------------|------------|------------|------------|--------------------|-------|

| Parameter/Description |                                                   | Min.       | Max.              | Min.       | Max.              | Min.       | Max.       | Min.       | Max.       | Min.       | Max.               |       |

| t <sub>IOCKH</sub>    | Input Low to High (pad to I/O module input)       |            | 2.3               |            | 2.6               |            | 3.0        |            | 3.5        |            | 4.5                | ns    |

| t <sub>IOPWH</sub>    | Minimum Pulse Width High                          | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5        |                    | ns    |

| t <sub>IPOWL</sub>    | Minimum Pulse Width Low                           | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5        |                    | ns    |

| t <sub>IOSAPW</sub>   | Minimum Asynchronous Pulse Width                  | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5        |                    | ns    |

| t <sub>IOCKSW</sub>   | Maximum Skew                                      |            | 0.6               |            | 0.6               |            | 0.6        |            | 0.6        |            | 0.6                | ns    |

| t <sub>IOP</sub>      | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4       |                    | ns    |

| f <sub>IOMAX</sub>    | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |            | 75                 | MHz   |

| Dedicate              | d (hardwired) Array Clock                         |            |                   |            | •                 |            |            | •          | -          |            |                    |       |

| t <sub>HCKH</sub>     | Input Low to High (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |            | 7.0                | ns    |

| t <sub>HCKL</sub>     | Input High to Low (pad to S-module input)         |            | 3.7               |            | 4.1               |            | 4.7        |            | 5.5        |            | 7.0                | ns    |

| t <sub>HPWH</sub>     | Minimum Pulse Width High                          | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5        |                    | ns    |

| t <sub>HPWL</sub>     | Minimum Pulse Width Low                           | 2.4        |                   | 3.2        |                   | 3.8        |            | 4.8        |            | 6.5        |                    | ns    |

| t <sub>HCKSW</sub>    | Delta High to Low, Low Slew                       |            | 0.6               |            | 0.6               |            | 0.6        |            | 0.6        |            | 0.6                | ns    |

| t <sub>HP</sub>       | Minimum Period                                    | 5.0        |                   | 6.8        |                   | 8.0        |            | 10.0       |            | 13.4       |                    | ns    |

| f <sub>HMAX</sub>     | Maximum Frequency                                 |            | 200               |            | 150               |            | 125        |            | 100        |            | 75                 | MHz   |

| Routed A              | rray Clock Networks                               |            |                   |            |                   |            |            | •          | -          |            |                    |       |

| t <sub>RCKH</sub>     | Input Low to High (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |            | 11.8               | ns    |

| t <sub>RCKL</sub>     | Input High to Low (FO = 64)                       |            | 6.0               |            | 6.8               |            | 7.7        |            | 9.0        |            | 11.8               | ns    |

| t <sub>RPWH</sub>     | Min. Pulse Width High (FO = 64)                   | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2        |                    | ns    |

| t <sub>RPWL</sub>     | Min. Pulse Width Low (FO = 64)                    | 4.1        |                   | 4.5        |                   | 5.4        |            | 6.1        |            | 8.2        |                    | ns    |

| t <sub>RCKSW</sub>    | Maximum Skew (FO = 128)                           |            | 1.2               |            | 1.4               |            | 1.6        |            | 1.8        |            | 1.8                | ns    |

| t <sub>RP</sub>       | Minimum Period (FO = 64)                          | 8.3        |                   | 9.3        |                   | 11.1       |            | 12.5       |            | 16.7       |                    | ns    |

| f <sub>RMAX</sub>     | Maximum Frequency (FO = 64)                       |            | 120               |            | 105               |            | 90         |            | 80         |            | 60                 | MHz   |

| Clock-to-             | Clock Skews                                       |            |                   |            |                   | -          |            |            | -          |            |                    |       |

| t <sub>IOHCKSW</sub>  | I/O Clock to H-Clock Skew                         | 0.0        | 2.6               | 0.0        | 2.7               | 0.0        | 2.9        | 0.0        | 3.0        | 0.0        | 3.0                | ns    |

| t <sub>IORCKSW</sub>  | I/O Clock to R-Clock Skew (FO = 64)<br>(FO = 216) | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0        | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0 | 1.7<br>5.0 | 0.0<br>0.0 | 5.0<br>5.0         | ns    |

| t <sub>HRCKSW</sub>   | H-Clock to R-Clock Skew (FO = 64)<br>(FO = 216)   | 0.0<br>0.0 | 1.3<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0        | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0 | 0.0<br>0.0 | 1.0<br>3.0         | ns    |

Notes:

1. The -2 and -3 speed grades have been discontinued. Refer to PDN 0104, PDN 0203, PDN 0604, and PDN 1004 at http://www.microsemi.com/soc/support/notifications/default.aspx#pdn.

2. Delays based on 35 pF loading.

**Detailed Specifications**

# **Pin Descriptions**

#### CLKA Clock A (Input)

Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### CLKB Clock B (Input)

Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### GND Ground

LOW supply voltage.

#### HCLK Dedicated (Hard-wired) Array Clock (Input)

Clock input for sequential modules. This input is directly wired to each S-Module and offers clock speeds independent of the number of S-Modules being driven. This pin can also be used as an I/O.

#### I/O Input/Output (Input, Output)

The I/O pin functions as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are tristated by the Designer Series software.

#### IOCLK Dedicated (Hard-wired) I/O Clock (Input)

Clock input for I/O modules. This input is directly wired to each I/O module and offers clock speeds independent of the number of I/O modules being driven. This pin can also be used as an I/O.

#### IOPCL Dedicated (Hard-wired) I/O Preset/Clear (Input)

Input for I/O preset or clear. This global input is directly wired to the preset and clear inputs of all I/O registers. This pin functions as an I/O when no I/O preset or clear macros are used.

#### MODE Mode (Input)

The MODE pin controls the use of diagnostic pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os. To provide Actionprobe capability, the MODE pin should be terminated to GND through a 10K resistor so that the MODE pin can be pulled high when required.

#### NC No Connection

This pin is not connected to circuitry within the device.

#### PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### PRB Probe B (Output)

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin can be used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDI Serial Data Input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

# 3 – Package Pin Assignments

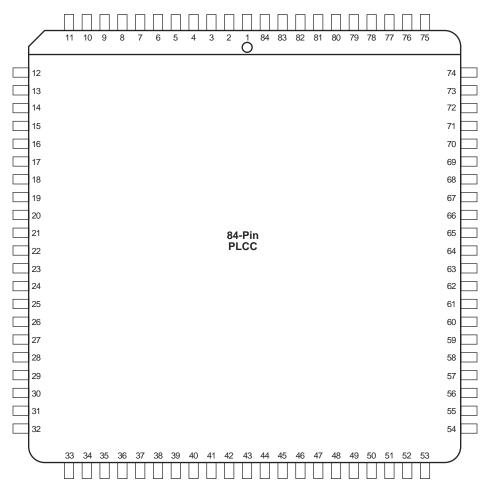

# **PL84**

Note: This is the top view of the package.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

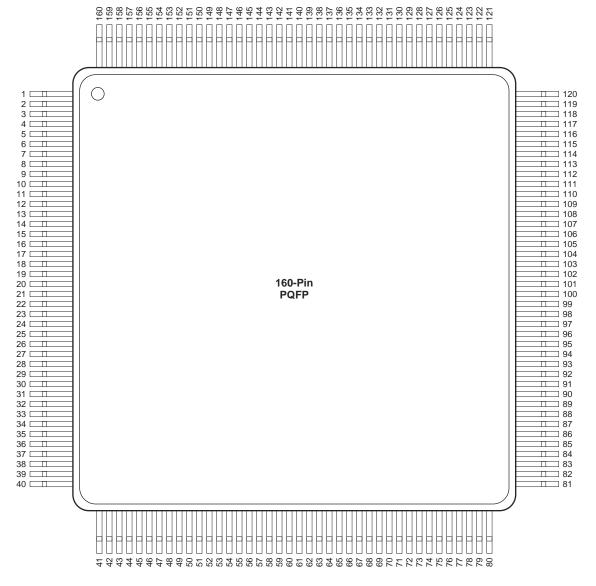

# PQ160

Note: This is the top view of the package

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Package Pin Assignments

| PQ160      |                        |                        |                        |  |  |  |  |  |

|------------|------------------------|------------------------|------------------------|--|--|--|--|--|

| Pin Number | A1425, A14V25 Function | A1440, A14V40 Function | A1460, A14V60 Function |  |  |  |  |  |

| 1          | GND                    | GND                    | GND                    |  |  |  |  |  |

| 2          | SDI, I/O               | SDI, I/O               | SDI, I/O               |  |  |  |  |  |

| 5          | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 9          | MODE                   | MODE                   | MODE                   |  |  |  |  |  |

| 10         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 14         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 15         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 18         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 19         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 20         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 24         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 27         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 28         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 29         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 40         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 41         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 43         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 45         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 46         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 47         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 49         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 51         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 53         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 58         | PRB, I/O               | PRB, I/O               | PRB, I/O               |  |  |  |  |  |

| 59         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 60         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 62         | HCLK, I/O              | HCLK, I/O              | HCLK, I/O              |  |  |  |  |  |

| 63         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 74         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 75         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 76         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 77         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 78         | NC                     | I/O                    | I/O                    |  |  |  |  |  |

| 79         | SDO                    | SDO                    | SDO                    |  |  |  |  |  |

| 80         | IOPCL, I/O             | IOPCL, I/O             | IOPCL, I/O             |  |  |  |  |  |

| 81         | GND                    | GND                    | GND                    |  |  |  |  |  |

| 90         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

| 91         | VCC                    | VCC                    | VCC                    |  |  |  |  |  |

Package Pin Assignments

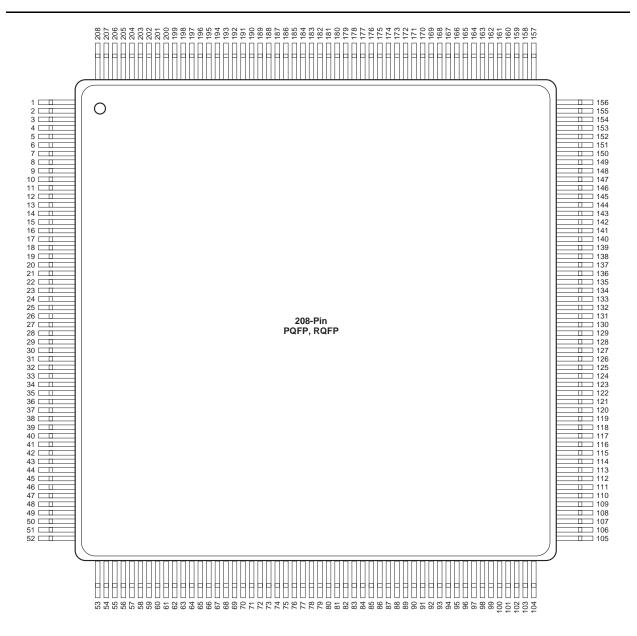

# PQ208, RQ208

Note: This is the top view of the package

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Accelerator Series FPGAs – ACT 3 Family

|            | TQ176                     |                           | TQ176      |                           |                           |  |  |  |

|------------|---------------------------|---------------------------|------------|---------------------------|---------------------------|--|--|--|

| Pin Number | A1440, A14V40<br>Function | A1460, A14V60<br>Function | Pin Number | A1440, A14V40<br>Function | A1460, A14V60<br>Function |  |  |  |

| 1          | GND                       | GND                       | 89         | GND                       | GND                       |  |  |  |

| 2          | SDI, I/O                  | SDI, I/O                  | 98         | VCC                       | VCC                       |  |  |  |

| 10         | MODE                      | MODE                      | 99         | VCC                       | VCC                       |  |  |  |

| 11         | VCC                       | VCC                       | 108        | GND                       | GND                       |  |  |  |

| 20         | NC                        | I/O                       | 109        | VCC                       | VCC                       |  |  |  |

| 21         | GND                       | GND                       | 110        | GND                       | GND                       |  |  |  |

| 22         | VCC                       | VCC                       | 119        | NC                        | I/O                       |  |  |  |

| 23         | GND                       | GND                       | 121        | NC                        | I/O                       |  |  |  |

| 32         | VCC                       | VCC                       | 122        | VCC                       | VCC                       |  |  |  |

| 33         | VCC                       | VCC                       | 123        | GND                       | GND                       |  |  |  |

| 44         | GND                       | GND                       | 124        | VCC                       | VCC                       |  |  |  |

| 49         | NC                        | I/O                       | 132        | IOCLK, I/O                | IOCLK, I/O                |  |  |  |

| 51         | NC                        | I/O                       | 133        | GND                       | GND                       |  |  |  |

| 63         | NC                        | I/O                       | 138        | NC                        | I/O                       |  |  |  |

| 64         | PRB, I/O                  | PRB, I/O                  | 152        | CLKA, I/O                 | CLKA, I/O                 |  |  |  |

| 65         | GND                       | GND                       | 153        | CLKB, I/O                 | CLKB, I/O                 |  |  |  |

| 66         | VCC                       | VCC                       | 154        | VCC                       | VCC                       |  |  |  |

| 67         | VCC                       | VCC                       | 155        | GND                       | GND                       |  |  |  |

| 69         | HCLK, I/O                 | HCLK, I/O                 | 156        | VCC                       | VCC                       |  |  |  |

| 82         | NC                        | I/O                       | 157        | PRA, I/O                  | PRA, I/O                  |  |  |  |

| 83         | NC                        | I/O                       | 158        | NC                        | I/O                       |  |  |  |

| 87         | SDO                       | SDO                       | 170        | NC                        | I/O                       |  |  |  |

| 88         | IOPCL, I/O                | IOPCL, I/O                | 176        | DCLK, I/O                 | DCLK, I/O                 |  |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Accelerator Series FPGAs - ACT 3 Family

| CQ256      |                 | CQ256      |                 |

|------------|-----------------|------------|-----------------|

| Pin Number | A14100 Function | Pin Number | A14100 Function |

| 1          | GND             | 141        | VCC             |

| 2          | SDI, I/O        | 158        | GND             |

| 11         | MODE            | 159        | VCC             |

| 28         | VCC             | 160        | GND             |

| 29         | GND             | 161        | VCC             |

| 30         | VCC             | 174        | VCC             |

| 31         | GND             | 175        | GND             |

| 46         | VCC             | 176        | GND             |

| 59         | GND             | 188        | IOCLK, I/O      |

| 90         | PRB, I/O        | 189        | GND             |

| 91         | GND             | 219        | CLKA, I/O       |

| 92         | VCC             | 220        | CLKB, I/O       |

| 93         | GND             | 221        | VCC             |

| 94         | VCC             | 222        | GND             |

| 96         | HCLK, I/O       | 223        | VCC             |

| 110        | GND             | 224        | GND             |

| 126        | SDO             | 225        | PRA, I/O        |

| 127        | IOPCL, I/O      | 240        | GND             |

| 128        | GND             | 256        | DCLK, I/O       |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Package Pin Assignments

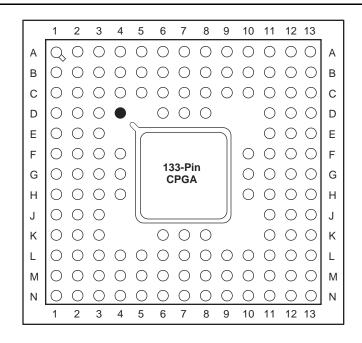

# PG133

Note: This is the top view.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx

Accelerator Series FPGAs – ACT 3 Family

| PG133          |                                                          |  |  |

|----------------|----------------------------------------------------------|--|--|

| A1425 Function | Location                                                 |  |  |

| CLKA or I/O    | D7                                                       |  |  |

| CLKB or I/O    | B6                                                       |  |  |

| DCLK or I/O    | D4                                                       |  |  |

| GND            | A2, C3, C7, C11, C12, F10, G3, G11, L3, L7, L11, M3, N12 |  |  |

| HCLK or I/O    | К7                                                       |  |  |

| IOCLK or I/O   | C10                                                      |  |  |

| IOPCL or I/O   | L10                                                      |  |  |

| MODE           | E3                                                       |  |  |

| NC             | A1, A7, A13, G1, G13, N1, N7, N13                        |  |  |

| PRA or I/O     | A6                                                       |  |  |

| PRB or I/O     | L6                                                       |  |  |

| SDI or I/O     | C2                                                       |  |  |

| SDO            | M11                                                      |  |  |

| VCC            | B2, B7, B12, E11, G2, G12, J2, J12, M2, M7, M12          |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

- 4. The PG133 package has been discontinued.

Accelerator Series FPGAs – ACT 3 Family

|                | PG207                                                            |  |  |  |

|----------------|------------------------------------------------------------------|--|--|--|

| A1460 Function | Location                                                         |  |  |  |

| CLKA or I/O    | К1                                                               |  |  |  |

| CLKB or I/O    | J3                                                               |  |  |  |

| DCLK or I/O    | E4                                                               |  |  |  |

| GND            | C14, D4, D5, D9, D14, J4, J14, P3, P4, P7, P9, P14, R15          |  |  |  |

| HCLK or I/O    | J15                                                              |  |  |  |

| IOCLK or I/O   | P5                                                               |  |  |  |

| IOPCL or I/O   | N14                                                              |  |  |  |

| MODE           | D7                                                               |  |  |  |

| NC             | A1, A2, A16, A17, B1, B17, C1, C2, S1, S3, S17, T1, T2, T16, T17 |  |  |  |

| PRA or I/O     | H1                                                               |  |  |  |

| PRB or I/O     | К16                                                              |  |  |  |

| SDI or I/O     | C3                                                               |  |  |  |

| SDO            | P15                                                              |  |  |  |

| VCC            | B2, B9, B16, D11, J2, J16, P12, S2, S9, S16, T5                  |  |  |  |

- 1. All unlisted pin numbers are user I/Os.

- 2. NC denotes no connection.

- 3. MODE should be terminated to GND through a 10K resistor to enable Actionprobe usage; otherwise it can be terminated directly to GND.

Datasheet Information

| Revision                  | Changes                                                                     |      |

|---------------------------|-----------------------------------------------------------------------------|------|

| Revision 2<br>(continued) |                                                                             |      |

|                           | "BG225"                                                                     | 3-20 |

|                           | "PG100"                                                                     | 3-24 |

|                           | "PG133"                                                                     | 3-26 |

|                           | "PG175"                                                                     | 3-28 |

| Revision 1<br>(June 2006) | RoHS compliant information was added to the "Ordering Information" section. | II   |