Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | Ethernet, Host Interface, FIFO, SCI                                             |

| Peripherals                | DMA, POR, WDT                                                                   |

| Number of I/O              | 71                                                                              |

| Program Memory Size        | •                                                                               |

| Program Memory Type        | ROMIess                                                                         |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.4V ~ 1.6V                                                                     |

| Data Converters            | -                                                                               |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 176-LFBGA                                                                       |

| Supplier Device Package    | 176-LFBGA (13x13)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d17618abgw100v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# 32

## SH7618 Group

### Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperHTM RISC engine Family / SH7618 Series

> SH7618 HD6417618 SH7618A HD6417618A

Renesas Electronics

Rev.6.00 2007.06

| Туре                      | Kinds of<br>Instruction | Op Code | Function                          | Number of<br>Instructions |

|---------------------------|-------------------------|---------|-----------------------------------|---------------------------|

| Arithmetic                | 21                      | MULS    | Signed multiplication             | 33                        |

| operation<br>instructions |                         | MULU    | Unsigned multiplication           |                           |

|                           |                         | NEG     | Sign inversion                    |                           |

|                           |                         | NEGC    | Sign inversion with borrow        |                           |

|                           |                         | SUB     | Binary subtraction                |                           |

|                           |                         | SUBC    | Binary subtraction with carry     |                           |

|                           |                         | SUBV    | Binary subtraction with underflow |                           |

| Logic                     | 6                       | AND     | Logical AND                       | 14                        |

| operation<br>instructions |                         | NOT     | Bit inversion                     |                           |

|                           |                         | OR      | Logical OR                        |                           |

|                           |                         | TAS     | Memory test and bit setting       |                           |

|                           |                         | TST     | T bit setting for logical AND     |                           |

|                           |                         | XOR     | Exclusive logical OR              |                           |

| Shift                     | 10                      | ROTL    | 1-bit left shift                  | 14                        |

| instructions              |                         | ROTR    | 1-bit right shift                 |                           |

|                           |                         | ROTCL   | 1-bit left shift with T bit       |                           |

|                           |                         | ROTCR   | 1-bit right shift with T bit      |                           |

|                           |                         | SHAL    | Arithmetic 1-bit left shift       |                           |

|                           |                         | SHAR    | Arithmetic 1-bit right shift      |                           |

|                           |                         | SHLL    | Logical 1-bit left shift          |                           |

|                           |                         | SHLLn   | Logical n-bit left shift          |                           |

|                           |                         | SHLR    | Logical 1-bit right shift         |                           |

|                           |                         | SHLRn   | Logical n-bit right shift         |                           |

| Instruc | tion           | Operation                                                                                                                     | Code             | Execution<br>Cycles | T Bit |  |

|---------|----------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|-------|--|

| MOV.L   | Rm,@(R0,Rn)    | $\text{Rm} \rightarrow (\text{R0} + \text{Rn})$                                                                               | 0000nnnnmmm0110  | 1                   | —     |  |

| MOV.B   | @(R0,Rm),Rn    | $(R0 + Rm) \rightarrow Sign$<br>extension $\rightarrow Rn$                                                                    | 0000nnnnmmm1100  | 1                   |       |  |

| MOV.W   | @(R0,Rm),Rn    | $(R0 + Rm) \rightarrow Sign$<br>extension $\rightarrow Rn$                                                                    | 0000nnnnmmm1101  | 1                   |       |  |

| MOV.L   | @(R0,Rm),Rn    | $(R0 + Rm) \rightarrow Rn$                                                                                                    | 0000nnnnmmm1110  | 1                   | _     |  |

| MOV.B   | R0,@(disp,GBR) | $\text{R0} \rightarrow (\text{disp} + \text{GBR})$                                                                            | 11000000ddddddd  | 1                   | _     |  |

| MOV.W   | R0,@(disp,GBR) | $\text{R0} \rightarrow (\text{disp} \times \text{2 + GBR})$                                                                   | 11000001ddddddd  | 1                   | _     |  |

| MOV.L   | R0,@(disp,GBR) | $\text{R0} \rightarrow (\text{disp} \times \text{4} + \text{GBR})$                                                            | 11000010ddddddd  | 1                   | _     |  |

| MOV.B   | @(disp,GBR),R0 | $\begin{array}{l} (\text{disp} + \text{GBR}) \rightarrow \text{Sign} \\ \text{extension} \rightarrow \text{R0} \end{array}$   | 11000100ddddddd  | 1                   |       |  |

| MOV.W   | @(disp,GBR),R0 | $\begin{array}{l} (\text{disp} \times 2 + \text{GBR}) \rightarrow \\ \text{Sign extension} \rightarrow \text{R0} \end{array}$ | 11000101ddddddd  | 1                   |       |  |

| MOV.L   | @(disp,GBR),R0 | $(\text{disp}\times 4+\text{GBR})\rightarrow\text{R0}$                                                                        | 11000110ddddddd  | 1                   | _     |  |

| MOVA    | @(disp,PC),R0  | $\text{disp} \times \text{4} + \text{PC} \rightarrow \text{R0}$                                                               | 11000111ddddddd  | 1                   |       |  |

| MOVT    | Rn             | $T \to Rn$                                                                                                                    | 0000nnnn00101001 | 1                   |       |  |

| SWAP.E  | 3 Rm,Rn        | $\label{eq:Rm} \begin{array}{l} Rm \to Swap \text{ lowest two} \\ bytes \to Rn \end{array}$                                   | 0110nnnnmmm1000  | 1                   |       |  |

| SWAP.W  | /Rm,Rn         | $Rm \rightarrow Swap two$ consecutive words $\rightarrow Rn$                                                                  | 0110nnnnmmm1001  | 1                   |       |  |

| XTRCT   | Rm,Rn          | Rm: Middle 32 bits of $Rn \rightarrow Rn$                                                                                     | 0010nnnnmmm1101  | 1                   |       |  |

| 31                                       | access                                                             | 24 23 | J                      | (14*)(1<br>12 | 3*)(12<br>11 10      |                   | 3           | 2 1 | 0    |

|------------------------------------------|--------------------------------------------------------------------|-------|------------------------|---------------|----------------------|-------------------|-------------|-----|------|

|                                          | 1111 0000                                                          |       | **                     |               | W                    | Entry address     | 0           | * C | 0    |

| Write<br>31                              | access                                                             | 24 23 | 1                      | (14*)(1<br>12 | 3*)(12<br>11 10      |                   | 3           | 2 1 | 0    |

|                                          | 1111 0000                                                          |       | **                     |               | W                    | Entry address     | А           | * ( | ) () |

| 0                                        | 1 - 1 - 1                                                          |       | Tag address (28 to 10) |               |                      | LRU               | Х           | хU  | V    |

| Data arra<br>(a) Addre                   | ay access (both                                                    | ı     | vrite accesses)        | (14*)(1       |                      | !*)(11*)          |             |     |      |

| Data arra                                | ay access (both                                                    |       | vrite accesses)        | . , .         | 3*)(12<br>11 10<br>W | !*)(11*)          | X<br>3<br>L | 2 1 |      |

| Data arra<br>(a) Addra<br>31             | ay access (both<br>ess specification<br>1111 0001                  | ı     | vrite accesses)        | . , .         | 11 10                | !*)(11*)<br>) 9 4 | 3           | 2 1 | 0    |

| Data arra<br>(a) Addro<br>31<br>(b) Data | ay access (both<br>ess specification<br>1111 0001<br>specification | ı     | vrite accesses)        | . , .         | 11 10                | !*)(11*)<br>) 9 4 | 3           | 2 1 | 0    |

| Data arra<br>(a) Addra<br>31             | ay access (both<br>ess specification<br>1111 0001<br>specification | ı     | vrite accesses)        | 12            | 11 10                | !*)(11*)<br>) 9 4 | 3           | 2 1 | 0    |

Figure 3.4 Specifying Address and Data for Memory-Mapped Cache Access

#### 7.4.1 Common Control Register (CMNCR)

CMNCR is a 32-bit register that controls the common items for each area. Do not access external memory other than area 0 until setting CMNCR is complete.

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                       |

|----------|----------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 13 | _        | All 0            | R   | Reserved                                                                                                                                                                          |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                              |

| 12       | MAP      | 0                | R/W | Space Specification                                                                                                                                                               |

|          |          |                  |     | Selects the address map for the external address space.<br>The address maps to be selected are shown in tables 7.2<br>and 7.3.                                                    |

|          |          |                  |     | 0: Selects address map 1                                                                                                                                                          |

|          |          |                  |     | 1: Selects address map 2                                                                                                                                                          |

| 11 to 5  | _        | All 0            | R   | Reserved                                                                                                                                                                          |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                              |

| 4        | —        | 1                | R   | Reserved                                                                                                                                                                          |

|          |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                 |

| 3        | ENDIAN   | 0/1*             | R   | Endian Flag                                                                                                                                                                       |

|          |          |                  |     | Fetches the external pin (MD5) state for specifying<br>endian at a power-on reset. The endian setting for all the<br>address spaces are set by this bit. This is a read-only bit. |

|          |          |                  |     | <ol> <li>External pin (MD5) for specifying endian was driven<br/>low at a power-on reset. This LSI is operated as big<br/>endian.</li> </ol>                                      |

|          |          |                  |     | <ol> <li>External pin (MD5) for specifying endian was driven<br/>high at a power-on reset. This LSI is being operated as<br/>little endian.</li> </ol>                            |

| 2        | _        | 1                | R   | Reserved                                                                                                                                                                          |

|          |          |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                 |

#### 7.5.2 Normal Space Interface

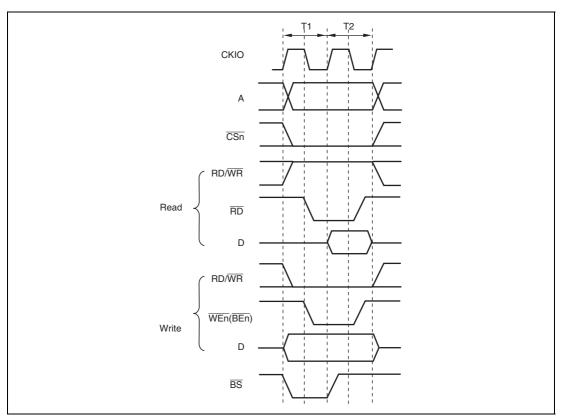

**Basic Timing:** For access to a normal space, this LSI uses strobe signal output in consideration of the fact that mainly static RAM will be directly connected. When using SRAM with a byte-selection pin, see section 7.5.6, Byte-Selection SRAM Interface. Figure 7.3 shows the basic timings of normal space access. A no-wait normal access is completed in two cycles. The  $\overline{BS}$  signal is asserted for one cycle to indicate the start of a bus cycle.

Figure 7.3 Normal Space Basic Access Timing (No-Wait Access)

There is no output signal which informs external devices of the access size when reading. Although the least significant bit of the address indicates the correct address when the access starts, 16-bit data is always read from a 16-bit device. When writing, only the  $\overline{\text{WEn}}$  ( $\overline{\text{BEn}}$ ) signal for the byte to be written to is asserted.

|     |          | Initial |     |                                                                                                                                                                                                                               |

|-----|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                   |

| 2   | CKS2     | 0       | R/W | Clock Select 2 to 0                                                                                                                                                                                                           |

| 1   | CKS1     | 0       | R/W | These bits select the clock to be used for the                                                                                                                                                                                |

| 0   | CKS0     | 0       | R/W | WTCNT count from the eight types obtainable by dividing the peripheral clock ( $P\phi$ ). The overflow period that is shown inside the parenthesis in the table is the value when the peripheral clock ( $P\phi$ ) is 25 MHz. |

|     |          |         |     | 000: Ρφ (10 μs)                                                                                                                                                                                                               |

|     |          |         |     | 001: Ρφ/4 (41 μs)                                                                                                                                                                                                             |

|     |          |         |     | 010: Ρφ/16 (164 μs)                                                                                                                                                                                                           |

|     |          |         |     | 011: Ρφ/32 (328 μs)                                                                                                                                                                                                           |

|     |          |         |     | 100: Ρφ/64 (655 μs)                                                                                                                                                                                                           |

|     |          |         |     | 101: Ρφ/256 (2.62 ms)                                                                                                                                                                                                         |

|     |          |         |     | 110: Pø/1024 (10.49 ms)                                                                                                                                                                                                       |

|     |          |         |     | 111: Ρφ/4096 (41.94 ms)                                                                                                                                                                                                       |

|     |          |         |     | Note: If bits CKS2 to CKS0 are modified when the WDT is operating, the up-count may not be performed correctly. Ensure that these bits are modified only when the WDT is not operating.                                       |

#### 9.2.3 Notes on Register Access

The watchdog timer counter (WTCNT) and watchdog timer control/status register (WTCSR) are more difficult to write to than other registers. The procedure for writing to these registers is given below.

**Writing to WTCNT and WTCSR:** These registers must be written by a word transfer instruction. They cannot be written by a byte or longword transfer instruction. When writing to WTCNT, set the upper byte to H'5A and transfer the lower byte as the write data, as shown in figure 9.2. When writing to WTCSR, set the upper byte to H'A5 and transfer the lower byte as the write data. This transfer procedure writes the lower byte data to WTCNT or WTCSR.

#### 10.3.1 Standby Control Register (STBCR)

STBCR is an 8-bit readable/writable register that specifies the state of the power-down mode.

|        |          | Initial |     |                                                                                                                                                                                                                                                      |

|--------|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                          |

| 7      | STBY     | 0       | R/W | Standby                                                                                                                                                                                                                                              |

|        |          |         |     | Specifies transition to software standby mode.                                                                                                                                                                                                       |

|        |          |         |     | 0: Executing SLEEP instruction makes this LSI<br>sleep mode                                                                                                                                                                                          |

|        |          |         |     | <ol> <li>Executing SLEEP instruction makes this LSI<br/>software standby mode</li> </ol>                                                                                                                                                             |

| 6 to 4 | _        | All 0   | R   | Reserved                                                                                                                                                                                                                                             |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                 |

| 3      | MDCHG    | 0       | R/W | MD2 to MD0 Pin Control                                                                                                                                                                                                                               |

|        |          |         |     | Specifies whether or not the values of pins MD2 to<br>MD0 are reflected in software standby mode. The<br>values of pins MD2 to MD0 are reflected at<br>returning from software standby mode by an<br>interrupt when the MDCHG bit has been set to 1. |

|        |          |         |     | 0: The values of pins MD2 to MO0 are not reflected<br>in software standby mode.                                                                                                                                                                      |

|        |          |         |     | 1: The values of pins MD2 to MD0 are reflected in<br>software standby mode.                                                                                                                                                                          |

| 2 to 0 | _        | All 0   | R   | Reserved                                                                                                                                                                                                                                             |

|        |          |         |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                 |

|         |          | Initial |     |                                                                                                                                                                                                                                                           |

|---------|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit Name | value   | R/W | Description                                                                                                                                                                                                                                               |

| 29      | TFP1     | 0       | R/W | Transmit Frame Position 1, 0                                                                                                                                                                                                                              |

| 28      | TFP0     | 0       | R/W | These two bits specify the relationship between the transmit buffer and transmit frame. In the preceding and following descriptors, a logically positive relationship must be maintained between the settings of this bit and the TDLE bit.               |

|         |          |         |     | 00: Frame transmission for transmit buffer indicated<br>by this descriptor continues (frame is not<br>concluded)                                                                                                                                          |

|         |          |         |     | 01: Transmit buffer indicated by this descriptor<br>contains end of frame (frame is concluded)                                                                                                                                                            |

|         |          |         |     | 10: Transmit buffer indicated by this descriptor is start<br>of frame (frame is not concluded)                                                                                                                                                            |

|         |          |         |     | <ol> <li>Contents of transmit buffer indicated by this<br/>descriptor are equivalent to one frame (one<br/>frame/one buffer)</li> </ol>                                                                                                                   |

| 27      | TFE      | 0       | R/W | Transmit Frame Error                                                                                                                                                                                                                                      |

|         |          |         |     | Indicates that one or other bit of the transmit frame<br>status indicated by bits 26 to 0 is set. Whether or not<br>the transmit frame status information is copied into<br>this bit is specified by the transmit/receive status copy<br>enable register. |

|         |          |         |     | 0: No error during transmission                                                                                                                                                                                                                           |

|         |          |         |     | 1: An error occurred during transmission                                                                                                                                                                                                                  |

| 26 to 0 | TFS26 to | All 0   | R/W | Transmit Frame Status                                                                                                                                                                                                                                     |

|         | TFS0     |         |     | TFS26 to TFS4: Reserved (The write value should always be 0.)                                                                                                                                                                                             |

|         |          |         |     | TFS3: Carrier Not Detect (corresponds to CND bit in<br>EESR)                                                                                                                                                                                              |

|         |          |         |     | TFS2: Detect Loss of Carrier (corresponds to DLC bit in EESR)                                                                                                                                                                                             |

|         |          |         |     | TFS1: Delayed collision Detect (corresponds to CD<br>bit in EESR)                                                                                                                                                                                         |

|         |          |         |     | TFS0: Transmit Retry Over (corresponds to TRO bit in EESR)                                                                                                                                                                                                |

#### 14.3 Register Description

The SCIF has the following registers. These registers specify the data format and bit rate, and control the transmitter and receiver sections.

- Receive FIFO data register\_0 (SCFRDR\_0)

- Transmit FIFO data register\_0 (SCFTDR\_0)

- Serial mode register\_0 (SCSMR\_0)

- Serial control register\_0 (SCSCR\_0)

- Serial status register\_0 (SCFSR\_0)

- Bit rate register\_0 (SCBRR\_0)

- FIFO control register\_0 (SCFCR\_0)

- FIFO data count register\_0 (SCFDR\_0)

- Serial port register\_0 (SCSPTR\_0)

- Line status register\_0 (SCLSR\_0)

- Receive FIFO data register\_1 (SCFRDR\_1)

- Transmit FIFO data register\_1 (SCFTDR\_1)

- Serial mode register\_1 (SCSMR\_1)

- Serial control register\_1 (SCSCR\_1)

- Serial status register\_1 (SCFSR\_1)

- Bit rate register\_1 (SCBRR\_1)

- FIFO control register\_1 (SCFCR\_1)

- FIFO data count register\_1 (SCFDR\_1)

- Serial port register\_1 (SCSPTR\_1)

- Line status register\_1 (SCLSR\_1)

- Receive FIFO data register\_2 (SCFRDR\_2)

- Transmit FIFO data register\_2 (SCFTDR\_2)

- Serial mode register\_2 (SCSMR\_2)

- Serial control register\_2 (SCSCR\_2)

- Serial status register\_2 (SCFSR\_2)

- Bit rate register\_2 (SCBRR\_2)

- FIFO control register\_2 (SCFCR\_2)

- FIFO data count register\_2 (SCFDR\_2)

- Serial port register\_2 (SCSPTR\_2)

- Line status register\_2 (SCLSR\_2)

4. Sending a Break Signal

The I/O condition and level of the TxD pin are determined by the SPBIO and SPBDT bits in the serial port register (SCSPTR). This feature can be used to send a break signal.

Until TE bit is set to 1 (enabling transmission) after initializing, TxD pin does not work. During the period, mark status is performed by SPBDT bit. Therefore, the SPBIO and SPBDT bits should be set to 1 (high level output).

To send a break signal during serial transmission, clear the SPBDT bit to 0 (designating low level), then clear the TE bit to 0 (halting transmission). When the TE bit is cleared to 0, the transmitter is initialized regardless of the current transmission state, and 0 is output from the TxD pin.

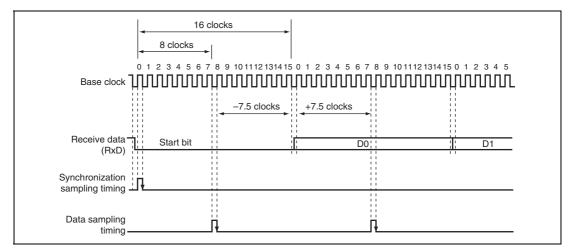

5. Receive Data Sampling Timing and Receive Margin (Asynchronous Mode)

The SCIF operates on a base clock with a frequency of 16 times the transfer rate. In reception, the SCIF synchronizes internally with the fall of the start bit, which it samples on the base clock. Receive data is latched at the rising edge of the eighth base clock pulse. The timing is shown in figure 14.24.

The receive margin in asynchronous mode can therefore be expressed as shown in equation 1.

#### 15.3 Parallel Access

#### 15.3.1 Operation

The HIF can be accessed by combining the  $\overline{\text{HIFCS}}$ ,  $\overline{\text{HIFRR}}$ ,  $\overline{\text{HIFWR}}$ , and  $\overline{\text{HIFRD}}$  pins. Table 15.2 shows the correspondence between combinations of these signals and HIF operations.

| HIFCS | HIFRS | HIFWR | HIFRD | Operation                                   |

|-------|-------|-------|-------|---------------------------------------------|

| 1     | ×     | ×     | ×     | No operation (NOP)                          |

| 0     | 0     | 1     | 0     | Read from register specified by HIFIDX[7:0] |

| 0     | 0     | 0     | 1     | Write to register specified by HIFIDX[7:0]  |

| 0     | 1     | 1     | 0     | Read from status register (HIFGSR[7:0])     |

| 0     | 1     | 0     | 1     | Write to index register (HIFIDX[7:0])       |

| 0     | ×     | 1     | 1     | No operation (NOP)                          |

| 0     | ×     | 0     | 0     | Setting prohibited                          |

Table 15.2HIF Operations

[Legend]

$\times$ : Don't care

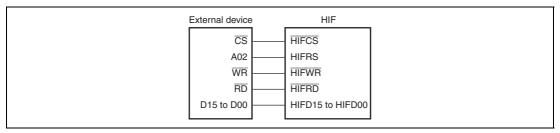

#### 15.3.2 Connection Method

When connecting the HIF to an external device, a method like that shown in figure 15.2 should be used.

Figure 15.2 HIF Connection Example

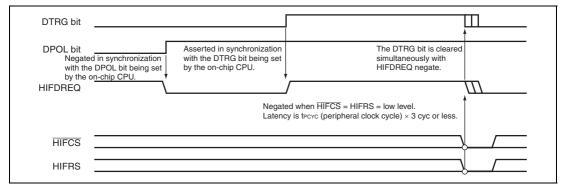

When the external DMAC is specified to detect high level of the HIFDREQ signal, set DMD = 0 and DPOL = 1. At the time the DPOL bit is set to 1, HIFDREQ becomes low. Then after writing 1 to the DTRG bit, HIFDREQ remains high until low level is detected for both the  $\overline{\text{HIFCS}}$  and HIFRS signals.

In this case, when the HIFDREQ signal is used, make sure that the setup time (HIFCS assertion to HIFRS settling) and the hold time (HIFRS hold to HIFCS negate) are satisfied. If  $t_{HIFAS}$  and  $t_{HIFAH}$  stipulated in section 21.4.9, HIF Timing, are not satisfied, the HIFDREQ signal may be negated unintentionally.

Figure 15.9 HIFDREQ Timing (When DMD = 0 and DPOL = 1)

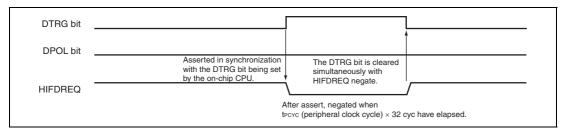

When the external DMAC is specified to detect the falling edge of the HIFDREQ signal, set DMD = 1 and DPOL = 0. After writing 1 to the DTRG bit, a low pulse of 32 peripheral clock cycles is generated at the HIFDREQ pin.

Figure 15.10 HIFDREQ Timing (When DMD = 1 and DPOL = 0)

RENESAS

• PBCRL2

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 15  | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 14  | PB7MD0   | 0                | R/W | PB7 Mode                                                          |

|     |          |                  |     | Selects the function of pin PB07/CE2B.                            |

|     |          |                  |     | 0: PB07 input/output (port)                                       |

|     |          |                  |     | 1: CE2B output (BSC)                                              |

| 13  | _        | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 12  | PB6MD0   | 0                | R/W | PB6 Mode                                                          |

|     |          |                  |     | Selects the function of pin PB06/ICIOWR.                          |

|     |          |                  |     | 0: PB06 input/output (port)                                       |

|     |          |                  |     | 1: ICIOWR output (BSC)                                            |

| 11  |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 10  | PB5MD0   | 0                | R/W | PB5 Mode                                                          |

|     |          |                  |     | Selects the function of pin PB05/ICIORD.                          |

|     |          |                  |     | 0: PB05 input/output (port)                                       |

|     |          |                  |     | 1: ICIORD output (BSC)                                            |

| 9   |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 8   | PB4MD0   | 0                | R/W | PB4 Mode                                                          |

|     |          |                  |     | Selects the function of pin PB04/RAS.                             |

|     |          |                  |     | 0: PB04 input/output (port)                                       |

|     |          |                  |     | 1: RAS output (BSC)                                               |

| 7   |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                       |

|-----|----------|------------------|-----|-------------------------------------------------------------------|

| 9   | PD4MD1   | 0                | R/W | PD4 Mode                                                          |

| 8   | PD4MD0   | 0                | R/W | Selects the function of pin PD4/IRQ4/SCK1.                        |

|     |          |                  |     | 00: PD4 input/output (port)                                       |

|     |          |                  |     | 01: IRQ4 input (INTC)                                             |

|     |          |                  |     | 10: SCK1 input/output (SCIF)                                      |

|     |          |                  |     | 11: Setting prohibited                                            |

| 7   | PD3MD1   | 0                | R/W | PD3 Mode                                                          |

| 6   | PD3MD0   | 0                | R/W | Selects the function of pin PD3/IRQ3/RxD1.                        |

|     |          |                  |     | 00: PD3 input/output (port)                                       |

|     |          |                  |     | 01: IRQ3 input (INTC)                                             |

|     |          |                  |     | 10: RxD1 input (SCIF)                                             |

|     |          |                  |     | 11: Setting prohibited                                            |

| 5   | PD2MD1   | 0                | R/W | PD2 Mode                                                          |

| 4   | PD2MD0   | 0                | R/W | Selects the function of pin PD2/IRQ2/TxD1.                        |

|     |          |                  |     | 00: PD2 input/output (port)                                       |

|     |          |                  |     | 01: IRQ2 input (INTC)                                             |

|     |          |                  |     | 10: TxD1 output (SCIF)                                            |

|     |          |                  |     | 11: Setting prohibited                                            |

| 3   |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 2   | PD1MD0   | 0                | R/W | PD1 Mode                                                          |

|     |          |                  |     | Selects the function of pin PD1/IRQ1.                             |

|     |          |                  |     | 0: PD1 input/output (port)                                        |

|     |          |                  |     | 1: IRQ1 input (INTC)                                              |

| 1   |          | 0                | R   | Reserved                                                          |

|     |          |                  |     | This bit is always read as 0. The write value should always be 0. |

| 0   | PD0MD0   | 0                | R/W | PD0 Mode                                                          |

|     |          |                  |     | Selects the function of pin PD0/IRQ0.                             |

|     |          |                  |     | 0: PD0 input/output (port)                                        |

|     |          |                  |     | 1: IRQ0 input (INTC)                                              |

|     |          |                  |     |                                                                   |

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Modul |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|-------|

| PCIORL                   | PC15IOR           | PC14IOR           | PC13IOR           | PC12IOR           | PC11IOR           | PC10IOR           | PC9IOR           | PC8IOR           | I/O   |

|                          | PC7IOR            | PC6IOR            | PC5IOR            | PC4IOR            | PC3IOR            | PC2IOR            | PC1IOR           | PC0IOR           | -     |

| PCCRH2                   | _                 | _                 | _                 | _                 | _                 | _                 | _                | PC20MD0          | -     |

|                          | _                 | PC19MD0           | _                 | PC18MD0           | _                 | PC17MD0           | _                | PC16MD0          | -     |

| PCCRL1                   | _                 | PC15MD0           | _                 | PC14MD0           | _                 | PC13MD0           | _                | PC12MD0          | -     |

|                          | _                 | PC11MD0           |                   | PC10MD0           |                   | PC9MD0            | _                | PC8MD0           | -     |

| PCCRL2                   | _                 | PC7MD0            | _                 | PC6MD0            | _                 | PC5MD0            | _                | PC4MD0           | -     |

|                          | _                 | PC3MD0            | _                 | PC2MD0            | _                 | PC1MD0            | _                | PC0MD0           | -     |

| PDDRL                    | _                 | _                 | _                 |                   | _                 | _                 | _                | _                | -     |

|                          | PD7DR             | PD6DR             | PD5DR             | PD4DR             | PD3DR             | PD2DR             | PD1DR            | PD0DR            | -     |

| PDIORL                   | _                 | _                 | _                 |                   | _                 | _                 | _                | _                | -     |

|                          | PD7IOR            | PD6IOR            | PD5IOR            | PD4IOR            | PD3IOR            | PD2IOR            | PD1IOR           | PD0IOR           | -     |

| PDCRL2                   | PD7MD1            | PD7MD0            | PD6MD1            | PD6MD0            | PD5MD1            | PD5MD0            | PD4MD1           | PD4MD0           | -     |

|                          | PD3MD1            | PD3MD0            | PD2MD1            | PD2MD0            | _                 | PD1MD0            | _                | PD0MD0           | -     |

| PEDRH                    | _                 | _                 | _                 | _                 | _                 | _                 | _                | PE24DR           | -     |

|                          | PE23DR            | PE22DR            | PE21DR            | PE20DR            | PE19DR            | PE18DR            | PE17DR           | PE16DR           | -     |

| PEDRL                    | PE15DR            | PE14DR            | PE13DR            | PE12DR            | PE11DR            | PE10DR            | PE9DR            | PE8DR            | -     |

|                          | PE7DR             | PE6DR             | PE5DR             | PE4DR             | PE3DR             | PE2DR             | PE1DR            | PE0DR            | -     |

| PEIORH                   | _                 | _                 | _                 | _                 | _                 | _                 | _                | PE24IOR          | -     |

|                          | PE23IOR           | PE22IOR           | PE21IOR           | PE20IOR           | PE19IOR           | PE18IOR           | PE17IOR          | PE16IOR          | -     |

| PEIORL                   | PE15IOR           | PE14IOR           | PE13IOR           | PE12IOR           | PE11IOR           | PE10IOR           | PE9IOR           | PE8IOR           | -     |

|                          | PE7IOR            | PE6IOR            | PE5IOR            | PE4IOR            | PE3IOR            | PE2IOR            | PE1IOR           | PE0IOR           | -     |

| PECRH1                   | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                | -     |

|                          | _                 |                   |                   |                   |                   | _                 | PE24MD1          | PE24MD0          | -     |

| PECRH2                   | PE23MD1           | PE23MD0           | PE22MD1           | PE22MD0           | PE21MD1           | PE21MD0           | PE20MD1          | PE20MD0          | -     |

|                          | PE19MD1           | PE19MD0           | PE18MD1           | PE18MD0           | PE17MD1           | PE17MD0           | PE16MD1          | PE16MD0          | -     |

| PECRL1                   | PE15MD1           | PE15MD0           |                   | PE14MD0           |                   | PE13MD0           | _                | PE12MD0          | -     |

|                          | _                 | PE11MD0           |                   | PE10MD0           |                   | PE9MD0            |                  | PE8MD0           | -     |

| PECRL2                   | _                 | PE7MD0            | _                 | PE6MD0            | _                 | PE5MD0            | _                | PE4MD0           | -     |

|                          |                   | PE3MD0            | _                 | PE2MD0            | _                 | PE1MD0            | _                | PE0MD0           | -     |

| Register<br>Abbreviation | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 | Module |

|--------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--------|

| CS0BCR                   | _                 | _                 | IWW1              | IWW0              | _                 | IWRWD1            | IWRWD0           | _                | BSC    |

|                          | IWRWS1            | IWRWS0            | _                 | IWRRD1            | IWRRD0            | _                 | IWRRS1           | IWRRS0           | _      |

|                          | TYPE3             | TYPE2             | TYPE1             | TYPE0             | _                 | BSZ1              | BSZ0             | _                | _      |

|                          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                | _      |

| CS3BCR                   | _                 | _                 | IWW1              | IWW0              | _                 | IWRWD1            | IWRWD0           | _                | -      |

|                          | IWRWS1            | IWRWS0            | _                 | IWRRD1            | IWRRD0            | _                 | IWRRS1           | IWRRS0           | _      |

|                          | TYPE3             | TYPE2             | TYPE1             | TYPE0             | _                 | BSZ1              | BSZ0             | _                | -      |

|                          | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                | -      |

| CS4BCR                   | _                 |                   | IWW1              | IWW0              | _                 | IWRWD1            | IWRWD0           | _                | -      |

|                          | IWRWS1            | IWRWS0            |                   | IWRRD1            | IWRRD0            | _                 | IWRRS1           | IWRRS0           | -      |

|                          | TYPE3             | TYPE2             | TYPE1             | TYPE0             | _                 | BSZ1              | BSZ0             | _                | -      |

|                          | _                 |                   |                   |                   |                   |                   |                  |                  | -      |

| CS5BBCR                  | _                 |                   | IWW1              | IWW0              |                   | IWRWD1            | IWRWD0           |                  | -      |

|                          | IWRWS1            | IWRWS0            | _                 | IWRRD1            | IWRRD0            | _                 | IWRRS1           | IWRRS0           | -      |

|                          | TYPE3             | TYPE2             | TYPE1             | TYPE0             | _                 | BSZ1              | BSZ0             | _                | -      |

|                          | _                 |                   |                   |                   | _                 | _                 |                  | _                | -      |

| CS6BBCR                  | _                 |                   | IWW1              | IWW0              | _                 | IWRWD1            | IWRWD0           | _                | -      |

|                          | IWRWS1            | IWRWS0            |                   | IWRRD1            | IWRRD0            | _                 | IWRRS1           | IWRRS0           | -      |

|                          | TYPE3             | TYPE2             | TYPE1             | TYPE0             | _                 | BSZ1              | BSZ0             | _                | -      |

|                          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                | -      |

| CS0WCR                   | _                 |                   |                   |                   |                   |                   |                  |                  | -      |

|                          | _                 |                   |                   |                   |                   |                   |                  |                  | -      |

|                          | _                 | _                 | _                 | SW1               | SW0               | WR3               | WR2              | WR1              | -      |

|                          | WR0               | WM                |                   |                   |                   |                   | HW1              | HW0              | -      |

| CS3WCR                   | _                 | _                 | _                 | _                 | _                 | _                 |                  | _                | _      |

|                          | _                 |                   |                   | BAS               |                   |                   |                  | _                | _      |

|                          | _                 |                   |                   |                   |                   | WR3               | WR2              | WR1              | _      |

|                          | WR0               | WM                |                   |                   |                   |                   |                  | _                | _      |

#### 21.4.10 EtherC Timing

#### Table 21.13 EtherC Timing

Conditions:  $V_{cc}Q = 3.0 \text{ V}$  to 3.6 V,  $V_{cc} = 1.4 \text{ V}$  to 1.6 V,  $T_a = -20^{\circ}\text{C}$  to +75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to +85°C (wide-range specifications)

| Item                           | Symbol               | Min. | Max. | Unit | Reference Figures |

|--------------------------------|----------------------|------|------|------|-------------------|

| TX-CLK cycle time              | t <sub>Tcyc</sub>    | 40   |      | ns   | _                 |

| TX-EN output delay time        | $t_{_{\text{TENd}}}$ | 1    | 20   | ns   | Figure 21.43      |

| MII_TXD[3:0] output delay time | t <sub>MTDd</sub>    | 1    | 20   | ns   | _                 |

| CRS setup time                 | t <sub>CRSs</sub>    | 10   |      | ns   | _                 |

| CRS hold time                  | t <sub>CRSh</sub>    | 10   |      | ns   | —                 |

| COL setup time                 | t <sub>COLs</sub>    | 10   | _    | ns   | Figure 21.44      |

| COL hold time                  | t <sub>colh</sub>    | 10   |      | ns   | _                 |

| RX-CLK cycle time              | t <sub>Rcyc</sub>    | 40   |      | ns   | —                 |

| RX-DV setup time               | t <sub>RDVs</sub>    | 10   |      | ns   | Figure 21.45      |

| RX-DV hold time                | t <sub>RDVh</sub>    | 10   | _    | ns   | _                 |

| MII_RXD[3:0] setup time        | t <sub>MRDs</sub>    | 10   | _    | ns   | _                 |

| MII_RXD[3:0] hold time         | t <sub>MRDh</sub>    | 10   | _    | ns   | _                 |

| RX-ER setup time               | t <sub>rens</sub>    | 10   | _    | ns   | Figure 21.46      |

| RX-ER hold time                | t <sub>RERh</sub>    | 10   | _    | ns   | _                 |

| MDIO setup time                | t <sub>MDIOs</sub>   | 10   | _    | ns   | Figure 21.47      |

| MDIO hold time                 | t <sub>MDIOh</sub>   | 10   | _    | ns   | _                 |

| MDIO output data hold time     | t <sub>MDIOdh</sub>  | 5    | 18   | ns   | Figure 21.48      |

| WOL output delay time          | t <sub>woLd</sub>    | 1    | 20   | ns   | Figure 21.49      |

| EXOUT output delay time        | $t_{_{\rm EXOUTd}}$  | 1    | 20   | ns   | Figure 21.50      |

| Item                                      | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14.4.3 Synchronous Operation              | 376  | Amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Clock                                     |      | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                           |      | When only receiving, the clock signal outputs while the RE bit of SCSCR is 1 and the number of data in receive FIFO is less than the receive FIFO data trigger number. In this case, $8 \times (16 + 1) = 136$ pulses of synchronous clock are output. To perform reception of n characters of data, select an external clock as the clock source. If an internal clock should be used, set RE = 1 and TE = 1 and receive n characters of data simultaneously with the transmission of n characters of dummy data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 14.13 Sample Flowchart             | 378  | Amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| for Transmitting Serial Data              |      | Start of transmission         Read TDFE flag in SCFSR         TDFE = 17         No         Whe transmit data to SCFDR Read the TDFE flag is set to 1, then write         Read TDFE and TEND flags         in SCFSR While they are 1, then clear them to 0         III         (2) Schild themeriseion confinuation procedure:         Toontinue serial transmission, read 1 from the TDFE flag is be on them that the the top carbon is the top of the |

| Figure 14.18 Sample Flowchart             | 382  | Amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| for Transmitting/Receiving Serial<br>Data |      | Initialization       [1] SCIF status check and transmit data         Start of transmission and reception       Read SCIFSR and check that the TDFE flag is set to 1, then write         Read TDFE flag in SCFSR       TDFE flag is set to 1, then write         No       TDFE at 100         TDFE flag is set to 100 minute       Read SCIFSR in the initial set to 100 minute         No       TDFE at 100         Veal       TDFE at 100 minute         Webs transmit data to SCFTDR in the initial minute       Read FDFER flag is 0.00 minute         No       TDFE at 100 minute         Veal       Read TDFE flag is 0.00 minute         No       TDFE at 100 minute         Veal       Read FDFER flag is 0.00 minute         No       TDFE flag is 0.00 minute         Veal       Read to ORER flag is 0.00 minute         Read to DFE at 100 minute       Diagon flag is 0.00 minute         No       TDFE at 100 minute         Veal       TDFE at 100 minute         No       TDFE at 100 minute         Veal       TDFE at 100 minute         No       TDFE at 100 minute         Veal       TDFE at 100 minute         No       TDFE at 100 minute         Veal       TDFE at 100 minute         Veal       TDFE flag 100 minute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 19.6 Usage Notes                          | 470  | Added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                           |      | <ol> <li>Since the HIFMD pin is not initially set to function as a general port pin, it must be pulled up or down externally to fix its state.</li> <li>When using a multiplexed pin with a function not selected with its initial value (for example, using the PB12/CS3 pin, the initial function of which is PB12, as the CS3 pin), the pin must be pulled up or down externally at least after a reset until its pin function is selected by software to fix its state.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |