Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

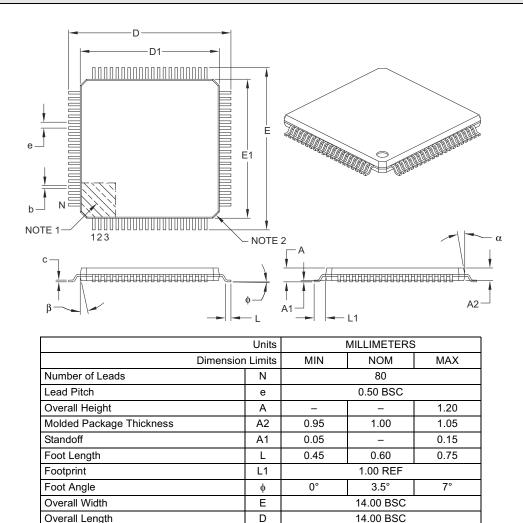

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6520-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome              | Pin Nu         | umber           | Pin   | Buffer   | Description                                                                          |  |  |

|-----------------------|----------------|-----------------|-------|----------|--------------------------------------------------------------------------------------|--|--|

| Pin Name              | PIC18F6X20     | PIC18F8X20      | Туре  | Туре     | Description                                                                          |  |  |

|                       |                |                 |       |          | PORTE is a bidirectional I/O port.                                                   |  |  |

| RE0/RD/AD8            | 2              | 4               |       |          |                                                                                      |  |  |

| RE0                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| RD                    |                |                 | I     | TTL      | Read control for Parallel Slave Port (see $\overline{WR}$ and $\overline{CS}$ pins). |  |  |

| AD8 <sup>(3)</sup>    |                |                 | I/O   | TTL      | External memory address/data 8.                                                      |  |  |

| RE1/WR/AD9            | 1              | 3               |       |          |                                                                                      |  |  |

| RE1                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| WR                    |                |                 | I     | TTL      | Write control for Parallel Slave Port                                                |  |  |

| (2)                   |                |                 |       |          | (see $\overline{CS}$ and $\overline{RD}$ pins).                                      |  |  |

| AD9 <sup>(3)</sup>    |                |                 | I/O   | TTL      | External memory address/data 9.                                                      |  |  |

| RE2/CS/AD10           | 64             | 78              |       |          |                                                                                      |  |  |

| RE2                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| CS                    |                |                 | I     | TTL      | Chip select control for Parallel Slave                                               |  |  |

| (2)                   |                |                 |       |          | Port (see $\overline{RD}$ and $\overline{WR}$ ).                                     |  |  |

| AD10 <sup>(3)</sup>   |                |                 | I/O   | TTL      | External memory address/data 10.                                                     |  |  |

| RE3/AD11              | 63             | 77              |       |          |                                                                                      |  |  |

| RE3                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| AD11 <sup>(3)</sup>   |                |                 | I/O   | TTL      | External memory address/data 11.                                                     |  |  |

| RE4/AD12              | 62             | 76              |       |          |                                                                                      |  |  |

| RE4                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| AD12                  |                |                 | I/O   | TTL      | External memory address/data 12.                                                     |  |  |

| RE5/AD13              | 61             | 75              |       |          |                                                                                      |  |  |

| RE5                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| AD13 <sup>(3)</sup>   |                |                 | I/O   | TTL      | External memory address/data 13.                                                     |  |  |

| RE6/AD14              | 60             | 74              |       |          |                                                                                      |  |  |

| RE6                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| AD14 <sup>(3)</sup>   |                |                 | I/O   | TTL      | External memory address/data 14.                                                     |  |  |

| RE7/CCP2/AD15         | 59             | 73              |       |          |                                                                                      |  |  |

| RE7                   |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |

| CCP2 <sup>(1,4)</sup> |                |                 | I/O   | ST       | Capture2 input/Compare2 output/                                                      |  |  |

|                       |                |                 |       |          | PWM2 output.                                                                         |  |  |

| AD15 <sup>(3)</sup>   |                |                 | I/O   | TTL      | External memory address/data 15.                                                     |  |  |

| _egend: TTL = TTL o   | compatible inp | ut              |       | CMOS =   | CMOS compatible input or output                                                      |  |  |

|                       |                | ut with CMOS le | evels | Analog = | Analog input                                                                         |  |  |

| I = Input             |                |                 |       |          | Output                                                                               |  |  |

| P = Powe              | er             |                 |       | OD =     | <ul> <li>Open-Drain (no P diode to VDD)</li> </ul>                                   |  |  |

#### PIC18EXX20 PINOLIT I/O DESCRIPTIONS (CONTINUED) TARI E 1-2.

Microcontroller).

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

6: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

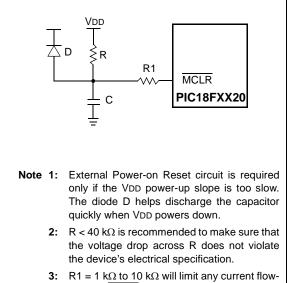

#### 3.1 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a 1 k $\Omega$  to 10 k $\Omega$  resistor to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

ing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

## 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter #33 for details.

## 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from Sleep.

### 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter #35, the brown-out situation will reset the chip. A Reset may not occur if VDD falls below parameter D005 for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. If the Power-up Timer is enabled, it will be invoked after VDD rises above BVDD; it then will keep the chip in Reset for an additional time delay (parameter #33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

#### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figures 3-3 through 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, the time-outs will expire if MCLR is kept low long enough. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes, or to synchronize more than one PIC18FXX20 device operating in parallel.

Table 3-2 shows the Reset conditions for some Special Function Registers, while Table 3-3 shows the Reset conditions for all of the registers.

| REGISTER 5-1: | EECON1 F               | REGISTER                                                                                                                                                                                                                                                                   | (ADDRE                     | SS FA6h)                     |                                                        |              |               |            |  |  |  |

|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|--------------------------------------------------------|--------------|---------------|------------|--|--|--|

|               | R/W-x                  | R/W-x                                                                                                                                                                                                                                                                      | U-0                        | R/W-0                        | R/W-x                                                  | R/W-0        | R/S-0         | R/S-0      |  |  |  |

|               | EEPGD                  | CFGS                                                                                                                                                                                                                                                                       | _                          | FREE                         | WRERR                                                  | WREN         | WR            | RD         |  |  |  |

|               | bit 7                  |                                                                                                                                                                                                                                                                            |                            |                              |                                                        |              |               | bit 0      |  |  |  |

| bit 7         | EEPGD: F               | lash Prograr                                                                                                                                                                                                                                                               | n or Data E                |                              | mory Select b                                          | it           |               |            |  |  |  |

|               | 1 = Acces              | s Flash prog<br>s data EEPF                                                                                                                                                                                                                                                | ram memo                   | ry                           | ,                                                      |              |               |            |  |  |  |

| bit 6         |                        |                                                                                                                                                                                                                                                                            |                            | -                            | figuration Sele                                        | ct bit       |               |            |  |  |  |

|               |                        | <ul> <li>Access configuration registers</li> <li>Access Flash program or data EEPROM memory</li> </ul>                                                                                                                                                                     |                            |                              |                                                        |              |               |            |  |  |  |

| bit 5         | Unimplem               | ented: Read                                                                                                                                                                                                                                                                | <b>d as</b> '0'            |                              |                                                        |              |               |            |  |  |  |

| bit 4         | FREE: Flas             | EE: Flash Row Erase Enable bit                                                                                                                                                                                                                                             |                            |                              |                                                        |              |               |            |  |  |  |

|               | (cleare                | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul>                                                                                             |                            |                              |                                                        |              |               |            |  |  |  |

| bit 3         | WRERR: F               | WRERR: Flash Program/Data EEPROM Error Flag bit                                                                                                                                                                                                                            |                            |                              |                                                        |              |               |            |  |  |  |

|               | (any R<br>0 = The w    | leset during rite operatio                                                                                                                                                                                                                                                 | self-timed  <br>n complete | d                            | g in normal ope                                        | ,            |               |            |  |  |  |

|               | Note:                  | When a Wi<br>tracing of th                                                                                                                                                                                                                                                 |                            |                              | GD and CFGS                                            | bits are not | t cleared. T  | his allows |  |  |  |

| bit 2         | WREN: Fla              | ash Program                                                                                                                                                                                                                                                                | /Data EEP                  | ROM Write I                  | Enable bit                                             |              |               |            |  |  |  |

|               |                        | •                                                                                                                                                                                                                                                                          | •                          | rogram/data<br>program/data  |                                                        |              |               |            |  |  |  |

| bit 1         | WR: Write              | Control bit                                                                                                                                                                                                                                                                |                            |                              |                                                        |              |               |            |  |  |  |

|               | cycle.<br>comple       | (The opera                                                                                                                                                                                                                                                                 | tion is sel<br>bit can on  | f-timed and<br>ly be set (no | cle or a progra<br>the bit is clea<br>t cleared) in so | ared by ha   |               |            |  |  |  |

| bit 0         |                        | •                                                                                                                                                                                                                                                                          |                            | bompiete                     |                                                        |              |               |            |  |  |  |

| bit 0         | 1 = Initiate<br>can or | <ul> <li>RD: Read Control bit</li> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)</li> <li>0 = Does not initiate an EEPROM read</li> </ul> |                            |                              |                                                        |              |               |            |  |  |  |

|               | Legend:                |                                                                                                                                                                                                                                                                            |                            |                              |                                                        |              |               | ]          |  |  |  |

|               | R = Reada              | ble bit                                                                                                                                                                                                                                                                    | W = V                      | Vritable bit                 | U = Unimp                                              | lemented bi  | it. read as ' | 0'         |  |  |  |

|               |                        |                                                                                                                                                                                                                                                                            |                            |                              | -                                                      |              |               |            |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

NOTES:

| LIN 3-11. | IF NZ. FLN                                       | IFILINAL   |                 |                | I I KLOIS     |           |              |        |

|-----------|--------------------------------------------------|------------|-----------------|----------------|---------------|-----------|--------------|--------|

|           | U-0                                              | R/W-1      | U-0             | R/W-1          | R/W-1         | R/W-1     | R/W-1        | R/W-1  |

|           | —                                                | CMIP       | _               | EEIP           | BCLIP         | LVDIP     | TMR3IP       | CCP2IP |

|           | bit 7                                            |            |                 |                |               |           |              | bit 0  |

| bit 7     | Unimpleme                                        | ented: Rea | <b>d as</b> '0' |                |               |           |              |        |

| bit 6     | <b>CMIP:</b> Com<br>1 = High pri<br>0 = Low pri  | iority     | errupt Priorit  | y bit          |               |           |              |        |

| bit 5     | Unimpleme                                        | ented: Rea | <b>d as</b> '0' |                |               |           |              |        |

| bit 4     | <b>EEIP:</b> Data<br>1 = High pri<br>0 = Low pri | iority     | Flash Write     | Operation In   | terrupt Prior | ity bit   |              |        |

| bit 3     | <b>BCLIP:</b> Bus<br>1 = High pri<br>0 = Low pri | iority     | nterrupt Prio   | rity bit       |               |           |              |        |

| bit 2     | <b>LVDIP:</b> Low<br>1 = High pri<br>0 = Low pri | iority     | etect Interru   | pt Priority bi | t             |           |              |        |

| bit 1     | <b>TMR3IP:</b> T<br>1 = High pr<br>0 = Low pri   | iority     | ow Interrupt    | Priority bit   |               |           |              |        |

| bit 0     | <b>CCP2IP:</b> C<br>1 = High pr<br>0 = Low pri   | iority     | pt Priority bi  | t              |               |           |              |        |

|           | Legend:                                          |            |                 |                |               |           |              |        |

|           | R = Readal                                       | ole bit    | W = W           | ritable bit    | U = Unin      | plemented | bit, read as | '0'    |

|           | 1                                                |            |                 |                |               |           |              |        |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 9-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

- n = Value at POR

x = Bit is unknown

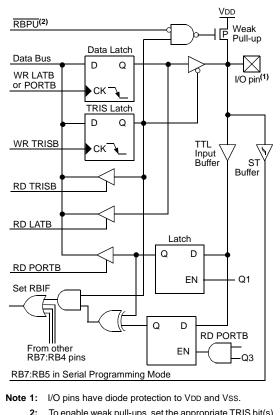

#### 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register, read and write the latched output value for PORTB.

#### **EXAMPLE 10-2:** INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATB  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISB | ; Set RB<3:0> as inputs |

|       |       | ; RB<5:4> as outputs    |

|       |       | ; RB<7:6> as inputs     |

|       |       | , 1                     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

On a Power-on Reset, these pins are Note: configured as digital inputs.

Four of the PORTB pins (RB3:RB0) are the external interrupt pins, INT3 through INT0. In order to use these pins as external interrupts, the corresponding TRISB bit must be set to '1'.

The other four PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- Clear flag bit RBIF. b)

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the configuration bit CCP2MX, as the alternate peripheral pin for the CCP2 module. This is only available when the device is configured in Microprocessor, Microprocessor with Boot Block, or Extended Microcontroller operating modes.

The RB5 pin is used as the LVP programming pin. When the LVP configuration bit is programmed, this pin loses the I/O function and become a programming test function.

Note: When LVP is enabled, the weak pull-up on RB5 is disabled.

#### **FIGURE 10-5: BLOCK DIAGRAM OF RB7:RB4 PINS**

<sup>2:</sup> To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (INTCON2<7>).

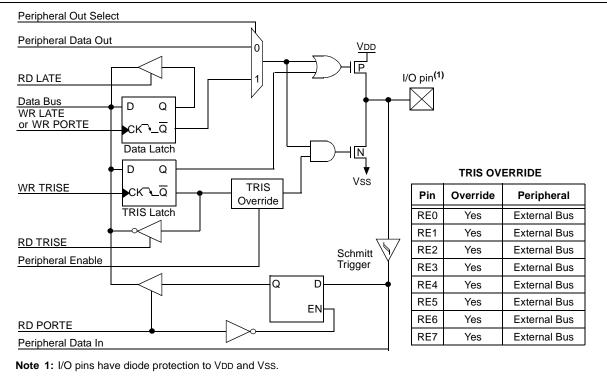

### FIGURE 10-11: PORTE BLOCK DIAGRAM IN I/O MODE

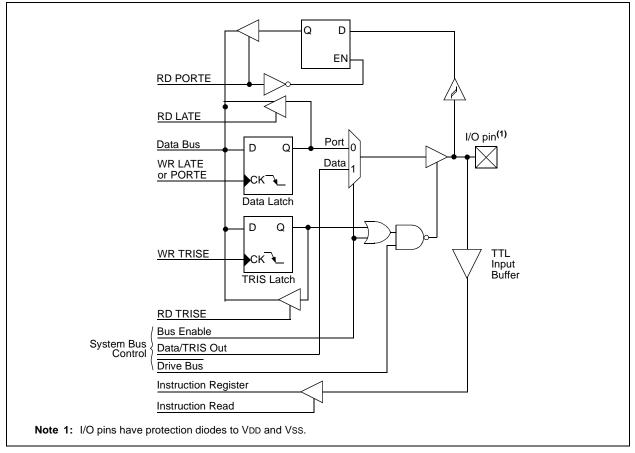

#### FIGURE 10-12: PORTE BLOCK DIAGRAM IN SYSTEM BUS MODE

© 2003-2013 Microchip Technology Inc.

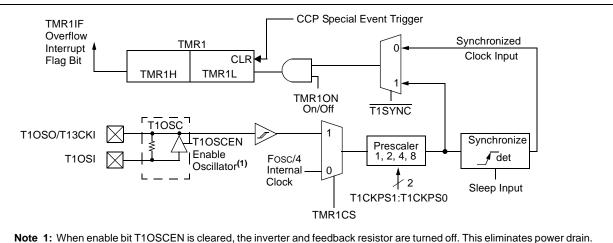

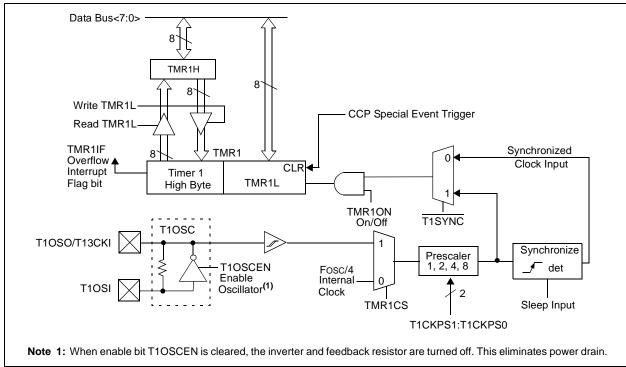

## 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs. That is, the TRISC<1:0> value is ignored and the pins are read as '0'.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see Section 16.0 "Capture/Compare/PWM (CCP) Modules").

## FIGURE 12-2: TIMER1 BLOCK DIAGRAM: 16-BIT READ/WRITE MODE

## FIGURE 12-1: TIMER1 BLOCK DIAGRAM

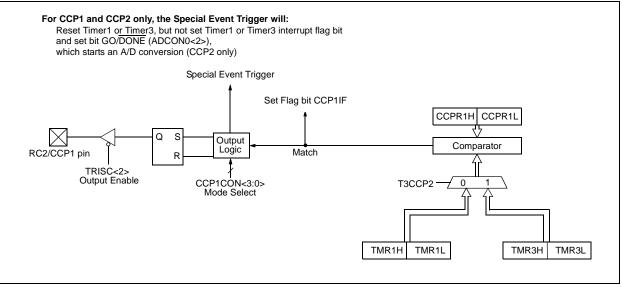

### 16.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against either the TMR1 register pair value or the TMR3 register pair value. When a match occurs, the CCP1 pin:

- is driven High

- is driven Low

- toggles output (high-to-low or low-to-high)

- · remains unchanged

The action on the pin is based on the value of control bits, CCP1M3:CCP1M0. At the same time, interrupt flag bit CCP1IF (CCP2IF) is set.

#### 16.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2/CCP1 compare output latch to     |

|       | the default low level. This is not the   |

|       | PORTC I/O data latch.                    |

#### 16.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 16.3.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 16.3.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of either CCP1 or CCP2, resets the TMR1 or TMR3 register pair, depending on which timer resource is currently selected. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1 or Timer3.

The CCP2 Special Event Trigger will also start an A/D conversion if the A/D module is enabled.

Note: The special event trigger from the CCP2 module will not set the Timer1 or Timer3 interrupt flag bits.

#### FIGURE 16-3: COMPARE MODE OPERATION BLOCK DIAGRAM

| IER 17-2: |                                                                                                                                                                                                                                                                                                                                                                                                 | . 11001 0                                    |                               | EGISTER'                                      |                 | JL)           |               |             |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------|-----------------------------------------------|-----------------|---------------|---------------|-------------|--|--|--|--|

|           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                        | R/W-0                         | R/W-0                                         | R/W-0           | R/W-0         | R/W-0         | R/W-0       |  |  |  |  |

|           | WCOL                                                                                                                                                                                                                                                                                                                                                                                            | SSPOV                                        | SSPEN                         | СКР                                           | SSPM3           | SSPM2         | SSPM1         | SSPM0       |  |  |  |  |

|           | bit 7                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                               |                                               |                 |               |               | bit 0       |  |  |  |  |

| bit 7     | WCOL: Wr                                                                                                                                                                                                                                                                                                                                                                                        | ite Collision                                | Detect bit (1                 | ransmit mod                                   | de only)        |               |               |             |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                 | be cleared in                                |                               | n while it is s                               | till transmitti | ing the prev  | ious word     |             |  |  |  |  |

| bit 6     | SSPOV: Re                                                                                                                                                                                                                                                                                                                                                                                       | eceive Overl                                 | flow Indicato                 | or bit                                        |                 |               |               |             |  |  |  |  |

|           | <u>SPI Slave r</u>                                                                                                                                                                                                                                                                                                                                                                              | SPI Slave mode:                              |                               |                                               |                 |               |               |             |  |  |  |  |

|           | of over<br>must re                                                                                                                                                                                                                                                                                                                                                                              | flow, the da<br>ead the SSF<br>be cleared ir | ta in SSPSF<br>BUF, even i    | e SSPBUF r<br>R is lost. Ove<br>f only transn | erflow can o    | nly occur in  | Slave mod     | e. The user |  |  |  |  |

|           | Note:                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                               | overflow bit<br>d by writing t                |                 |               |               | eption (and |  |  |  |  |

| bit 5     | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                      | s serial port                                | •                             | nable bit<br>res SCK, SD<br>ires these pi     |                 |               | I port pins   |             |  |  |  |  |

|           | Note:                                                                                                                                                                                                                                                                                                                                                                                           | When enab                                    | led, these p                  | ins must be                                   | properly cor    | nfigured as i | nput or outp  | out.        |  |  |  |  |

| bit 4     | CKP: Clock                                                                                                                                                                                                                                                                                                                                                                                      | Polarity Se                                  | elect bit                     |                                               |                 |               |               |             |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                 |                                              | s a high leve<br>s a low leve |                                               |                 |               |               |             |  |  |  |  |

| bit 3-0   | SSPM3:SS                                                                                                                                                                                                                                                                                                                                                                                        | PM0: Synch                                   | nronous Seri                  | ial Port Mode                                 | e Select bits   |               |               |             |  |  |  |  |

|           | <ul> <li>0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin</li> <li>0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> <li>0000 = SPI Master mode, clock = Fosc/4</li> </ul> |                                              |                               |                                               |                 |               |               |             |  |  |  |  |

|           | Note:                                                                                                                                                                                                                                                                                                                                                                                           | Bit combina<br>I <sup>2</sup> C mode o       |                               | ecifically list                               | ed here are     | either reser  | ved, or impl  | lemented in |  |  |  |  |

|           | Legend:                                                                                                                                                                                                                                                                                                                                                                                         |                                              |                               |                                               |                 |               |               |             |  |  |  |  |

|           | R = Readal                                                                                                                                                                                                                                                                                                                                                                                      | ble bit                                      | W = Writab                    | le bit                                        | U = Unimp       | lemented bi   | t, read as '0 | ,           |  |  |  |  |

|           | - n = Value                                                                                                                                                                                                                                                                                                                                                                                     | at POR                                       | '1' = Bit is s                | set                                           | '0' = Bit is o  | cleared       | x = Bit is u  | nknown      |  |  |  |  |

#### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER1 (SPI MODE)

### 19.4 A/D Conversions

Figure 19-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2 TAD wait is required before the next acquisition is started. After this 2 TAD wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

### 19.5 Use of the CCP2 Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/ DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

#### FIGURE 19-3: A/D CONVERSION TAD CYCLES

| Tcy - Tad           | TAD1    | TAD2     | TAD3   | TAD4   | TAD5   | TAD6     | TAD7      | TAD8     | TAD9    | TAD10   | TAD11       |                     |      |

|---------------------|---------|----------|--------|--------|--------|----------|-----------|----------|---------|---------|-------------|---------------------|------|

| <b>↑</b> ↑ <b>↑</b> | b9      | b8       | b7     | b6     | b5     | b4       | b3        | b2       | b1      | b0      | b0          |                     |      |

|                     | Conver  | sion sta | arts   |        |        |          |           |          |         |         |             |                     |      |

| Holding             | g capad | citor is | discon | nected | from a | inalog i | nput (t   | ypically | / 100 n | ıs)     |             |                     |      |

|                     |         |          |        |        |        |          |           |          |         |         |             |                     |      |

| Set GO I            | bit     |          |        | ↓      |        |          |           |          |         |         |             |                     |      |

|                     |         |          |        | Ne     | xt Q4: |          |           |          |         | '       | ) bit is cl | ,                   |      |

|                     |         |          |        |        |        | ADIF b   | oit is se | et, hold | ing cap | cacitor | is conne    | ected to analog inp | out. |

| Name                 | Bit 7                                 | Bit 6         | Bit 5        | Bit 4     | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|---------------------------------------|---------------|--------------|-----------|-------|--------|---------|--------|----------------------|---------------------------------|

| INTCON               | GIE/<br>GIEH                          | PEIE/<br>GIEL | TMR0IE       | INTOIE    | RBIE  | TMR0IF | INTOIF  | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                 | PSPIF                                 | ADIF          | RCIF         | TXIF      | SSPIF | CCP1IF | TMR2IF  | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                 | PSPIE                                 | ADIE          | RCIE         | TXIE      | SSPIE | CCP1IE | TMR2IE  | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                 | PSPIP                                 | ADIP          | RCIP         | TXIP      | SSPIP | CCP1IP | TMR2IP  | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR2                 | _                                     | CMIF          | _            | _         | BCLIF | LVDIF  | TMR3IF  | CCP2IF | -0 0000              | -0 0000                         |

| PIE2                 | _                                     | CMIE          | _            | _         | BCLIE | LVDIE  | TMR3IE  | CCP2IE | -0 0000              | -0 0000                         |

| IPR2                 | _                                     | CMIP          | _            | _         | BCLIP | LVDIP  | TMR3IP  | CCP2IP | -0 0000              | -0 0000                         |

| ADRESH               | A/D Resul                             | t Register I  | ligh Byte    |           |       |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL               | A/D Resul                             | t Register I  | _ow Byte     |           |       |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADCON0               | _                                     | _             | CHS3         | CHS3      | CHS1  | CHS0   | GO/DONE | ADON   | 00 0000              | 00 0000                         |

| ADCON1               | _                                     | _             | VCFG1        | VCFG0     | PCFG3 | PCFG2  | PCFG1   | PCFG0  | 00 0000              | 00 0000                         |

| ADCON2               | ADFM                                  |               | _            | _         | _     | ADCS2  | ADCS1   | ADCS0  | 0 000                | 0 000                           |

| PORTA                | _                                     | RA6           | RA5          | RA4       | RA3   | RA2    | RA1     | RA0    | 0x 0000              | 0u 0000                         |

| TRISA                | _                                     | PORTA D       | ata Directio | n Registe | r     |        |         |        | 11 1111              | 11 1111                         |

| PORTF                | RF7                                   | RF6           | RF5          | RF4       | RF3   | RF2    | RF1     | RF0    | x000 0000            | u000 0000                       |

| LATF                 | LATF7                                 | LATF6         | LATF5        | LATF4     | LATF3 | LATF2  | LATF1   | LATF0  | xxxx xxxx            | uuuu uuuu                       |

| TRISF                | PORTF Data Direction Control Register |               |              |           |       |        |         |        |                      | 1111 1111                       |

| PORTH <sup>(1)</sup> | RH7                                   | RH6           | RH5          | RH4       | RH3   | RH2    | RH1     | RH0    | 0000 xxxx            | 0000 xxxx                       |

| LATH <sup>(1)</sup>  | LATH7                                 | LATH6         | LATH5        | LATH4     | LATH3 | LATH2  | LATH1   | LATH0  | xxxx xxxx            | uuuu uuuu                       |

| TRISH <sup>(1)</sup> | PORTH Da                              | ata Directio  | n Control R  | egister   |       |        |         |        | 1111 1111            | 1111 1111                       |

#### TABLE 19-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Only available on PIC18F8X20 devices.

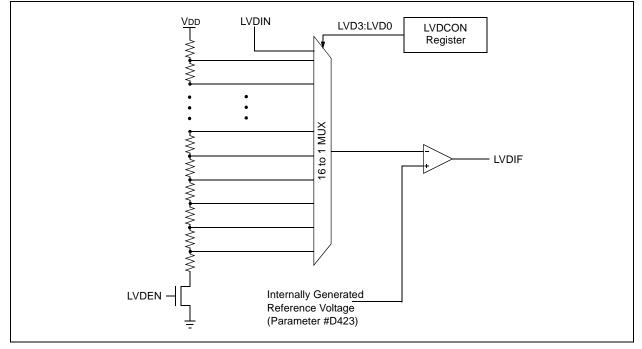

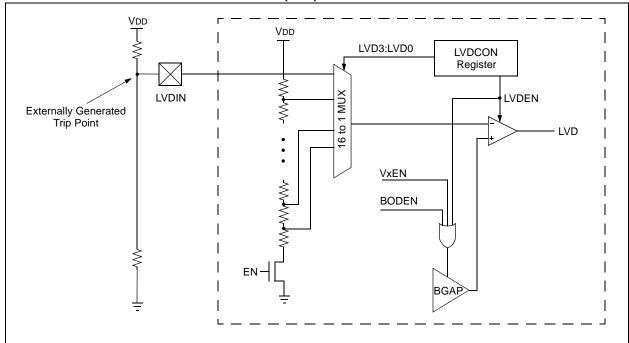

### FIGURE 22-2: LOW-VOLTAGE DETECT (LVD) BLOCK DIAGRAM

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits LVDL3:LVDL0 are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, LVDIN (Figure 22-3). This gives users flexibility because it allows them to configure the Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

FIGURE 22-3: LOW-VOLTAGE DETECT (LVD) WITH EXTERNAL INPUT BLOCK DIAGRAM

| BNC                                                                                                                                              | ;                       | Branch if                                                                                                                                                                                                                                                                           | Not Carry       |                 | BNN                                                                        |                                                                                                                                                                                                                                            | Branch if                                 | Not Negati                                                                             | ive             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------|-----------------|--|

| Syn                                                                                                                                              | tax:                    | [label] B                                                                                                                                                                                                                                                                           | NC n            |                 | Synta                                                                      | x:                                                                                                                                                                                                                                         | [label] B                                 | NN n                                                                                   |                 |  |

| Ope                                                                                                                                              | rands:                  |                                                                                                                                                                                                                                                                                     | 127             |                 | Opera                                                                      | ands:                                                                                                                                                                                                                                      | <br>-128 ≤ n ≤                            | 127                                                                                    |                 |  |

| -                                                                                                                                                | ration:                 | if Carry bit<br>(PC) + 2 +                                                                                                                                                                                                                                                          |                 |                 | Opera                                                                      |                                                                                                                                                                                                                                            |                                           | if Negative bit is '0' (PC) + 2 + 2n $\rightarrow$ PC                                  |                 |  |

| Stat                                                                                                                                             | us Affected:            | None                                                                                                                                                                                                                                                                                |                 |                 | Status                                                                     | Affected:                                                                                                                                                                                                                                  | None                                      |                                                                                        |                 |  |

| Enc                                                                                                                                              | oding:                  | 1110 0011 nnnn nnnn                                                                                                                                                                                                                                                                 |                 | Encod           | ding:                                                                      | 1110                                                                                                                                                                                                                                       | 0111 nr                                   | ınn nnnn                                                                               |                 |  |

| Des                                                                                                                                              | cription:               | If the Carry bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |                 | Descr           | iption:                                                                    | If the Negative bit is '0', the<br>program will branch.<br>The 2's complement number<br>added to the PC. Since the<br>have incremented to fetch t<br>instruction, the new address<br>PC+2+2n. This instruction<br>a two-cycle instruction. |                                           | number '2n' is<br>ce the PC will<br>fetch the next<br>ddress will be<br>action is then |                 |  |

| Wor                                                                                                                                              | ds:                     | 1                                                                                                                                                                                                                                                                                   |                 |                 | Words                                                                      | S:                                                                                                                                                                                                                                         | 1                                         |                                                                                        |                 |  |

| Сус                                                                                                                                              | les:                    | 1(2)                                                                                                                                                                                                                                                                                |                 |                 | Cycle                                                                      | s:                                                                                                                                                                                                                                         | 1(2)                                      |                                                                                        |                 |  |

|                                                                                                                                                  | Cycle Activity:<br>ump: |                                                                                                                                                                                                                                                                                     |                 |                 | Q Cy<br>If Jur                                                             | cle Activity                                                                                                                                                                                                                               | :                                         |                                                                                        |                 |  |

|                                                                                                                                                  | Q1                      | Q2                                                                                                                                                                                                                                                                                  | Q3              | Q4              |                                                                            | Q1                                                                                                                                                                                                                                         | Q2                                        | Q3                                                                                     | Q4              |  |

|                                                                                                                                                  | Decode                  | Read literal<br>'n'                                                                                                                                                                                                                                                                 | Process<br>Data | Write to PC     |                                                                            | Decode                                                                                                                                                                                                                                     | Read literal<br>'n'                       | Process<br>Data                                                                        | Write to PC     |  |

|                                                                                                                                                  | No                      | No                                                                                                                                                                                                                                                                                  | No              | No              |                                                                            | No                                                                                                                                                                                                                                         | No                                        | No                                                                                     | No              |  |

| IF N                                                                                                                                             | operation               | operation                                                                                                                                                                                                                                                                           | operation       | operation       |                                                                            | operation                                                                                                                                                                                                                                  | operation                                 | operation                                                                              | operation       |  |

|                                                                                                                                                  | o Jump:<br>Q1           | Q2                                                                                                                                                                                                                                                                                  | Q3              | Q4              | II NO                                                                      | Jump:<br>Q1                                                                                                                                                                                                                                | Q2                                        | Q3                                                                                     | Q4              |  |

|                                                                                                                                                  | Decode                  | Read literal<br>'n'                                                                                                                                                                                                                                                                 | Process<br>Data | No<br>operation |                                                                            | Decode                                                                                                                                                                                                                                     | Read literal<br>'n'                       | Process<br>Data                                                                        | No<br>operation |  |

| <u>Exa</u>                                                                                                                                       | mple:                   | HERE                                                                                                                                                                                                                                                                                | BNC Jump        |                 | Exam                                                                       | <u>ple</u> :                                                                                                                                                                                                                               | HERE                                      | BNN Jum                                                                                | p               |  |

| Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If Carry = 0;<br>PC = address (Jump)<br>If Carry = 1;<br>PC = address (HERE+2) |                         |                                                                                                                                                                                                                                                                                     |                 |                 | efore Instru<br>PC<br>fter Instruc<br>If Negativ<br>PC<br>If Negativ<br>PC | = ad<br>tion<br>ve = 0;<br>= ad<br>ve = 1;                                                                                                                                                                                                 | dress (HERI<br>dress (Jump<br>dress (HERI | 5)                                                                                     |                 |  |

| Param<br>No. | Symbol | Cł                | aracteristic      | :           | Min                    | Max | Units | Conditions                         |

|--------------|--------|-------------------|-------------------|-------------|------------------------|-----|-------|------------------------------------|

| 50           | TccL   | CCPx Input Low    | No prescal        | er          | 0.5 Tcy + 20           | _   | ns    |                                    |

|              |        | Time              | With              | PIC18FXX20  | 10                     | _   | ns    |                                    |

|              |        |                   | prescaler         | PIC18LFXX20 | 20                     | _   | ns    |                                    |

| 51           | ТссН   | CCPx Input High   | No prescal        | er          | 0.5 TCY + 20           | _   | ns    |                                    |

|              | Time   | With              | PIC18FXX20        | 10          | _                      | ns  |       |                                    |

|              |        |                   | prescaler         | PIC18LFXX20 | 20                     | _   | ns    |                                    |

| 52           | TCCP   | CCPx Input Period | k                 |             | <u>3 Tcy + 40</u><br>N | _   | ns    | N = prescale<br>value (1, 4 or 16) |

| 53           | TCCR   | CCPx Output Rise  | Time              | PIC18FXX20  | _                      | 25  | ns    |                                    |

|              |        |                   |                   | PIC18LFXX20 | _                      | 45  | ns    | VDD = 2.0V                         |

| 54           | TccF   | CCPx Output Fall  | Coutput Fall Time |             | _                      | 25  | ns    |                                    |

|              |        |                   |                   | PIC18LFXX20 | —                      | 45  | ns    | VDD = 2.0V                         |

### TABLE 26-13: CAPTURE/COMPARE/PWM REQUIREMENTS (ALL CCP MODULES)

| Param<br>No. | Symbol | Charac                                    | teristic                                                     | Min      | Мах               | Units    | Conditions                                                                                                                                                             |

|--------------|--------|-------------------------------------------|--------------------------------------------------------------|----------|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD    | A/D Clock Period                          | PIC18FXX20                                                   | 1.6      | 20 <b>(5)</b>     | μS       | Tosc based, VREF $\geq$ 3.0V                                                                                                                                           |

|              |        |                                           | PIC18LFXX20                                                  | 3.0      | 20 <sup>(5)</sup> | μS       | Tosc based, VREF full range                                                                                                                                            |