Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6520-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F6520 PIC18F8520

- PIC18F6620 PIC18F8620

- PIC18F6720 PIC18F8720

This family offers the same advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high endurance Enhanced Flash program memory. The PIC18FXX20 family also provides an enhanced range of program memory options and versatile analog features that make it ideal for complex, high-performance applications.

#### 1.1 Key Features

#### 1.1.1 EXPANDED MEMORY

The PIC18FXX20 family introduces the widest range of on-chip, Enhanced Flash program memory available on PIC<sup>®</sup> microcontrollers – up to 128 Kbyte (or 65,536 words), the largest ever offered by Microchip. For users with more modest code requirements, the family also includes members with 32 Kbyte or 64 Kbyte.

Other memory features are:

- Data RAM and Data EEPROM: The PIC18FXX20 family also provides plenty of room for application data. Depending on the device, either 2048 or 3840 bytes of data RAM are available. All devices have 1024 bytes of data EEPROM for long-term retention of nonvolatile data.

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

#### 1.1.2 EXTERNAL MEMORY INTERFACE

In the event that 128 Kbytes of program memory is inadequate for an application, the PIC18F8X20 members of the family also implement an External Memory Interface. This allows the controller's internal program counter to address a memory space of up to 2 Mbytes, permitting a level of data access that few 8-bit devices can claim. With the addition of new operating modes, the External Memory Interface offers many new options, including:

- Operating the microcontroller entirely from external memory

- Using combinations of on-chip and external memory, up to the 2-Mbyte limit

- Using external Flash memory for reprogrammable application code, or large data tables

- Using external RAM devices for storing large amounts of variable data

#### 1.1.3 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

#### 1.1.4 OTHER SPECIAL FEATURES

- **Communications:** The PIC18FXX20 family incorporates a range of serial communications peripherals, including 2 independent USARTs and a Master SSP module, capable of both SPI and I<sup>2</sup>C (Master and Slave) modes of operation. For PIC18F8X20 devices, one of the general purpose I/O ports can be reconfigured as an 8-bit Parallel Slave Port for direct processor-to-processor communications.

- **CCP Modules:** All devices in the family incorporate five Capture/Compare/PWM modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once.

- Analog Features: All devices in the family feature 10-bit A/D converters, with up to 16 input channels, as well as the ability to perform conversions during Sleep mode. Also included are dual analog comparators with programmable input and output configuration, a programmable Low-Voltage Detect module and a programmable Brown-out Reset module.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

#### 3.0 RESET

The PIC18FXX20 devices differentiate between various kinds of Reset:

- Power-on Reset (POR) a)

- b) MCLR Reset during normal operation

- MCLR Reset during Sleep C)

- Watchdog Timer (WDT) Reset (during normal d) operation)

- Programmable Brown-out Reset (PBOR) e)

- f) **RESET** Instruction

- Stack Full Reset g)

- h) Stack Underflow Reset

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during Sleep and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ , PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the Reset. See Table 3-3 for a full description of the Reset states of all registers.

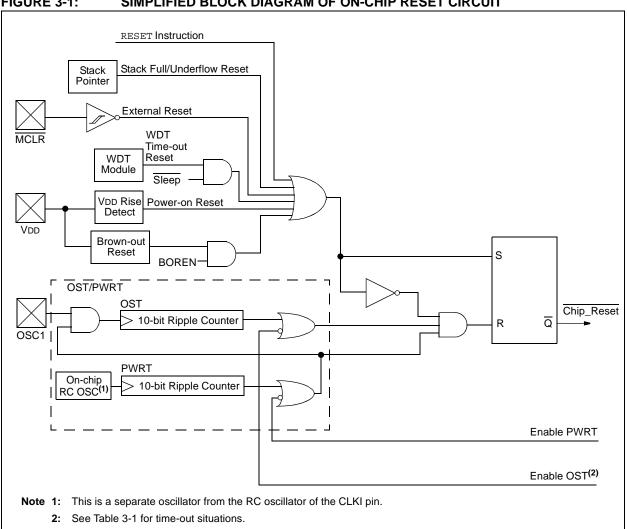

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. The MCLR pin is not driven low by any internal Resets, including the WDT.

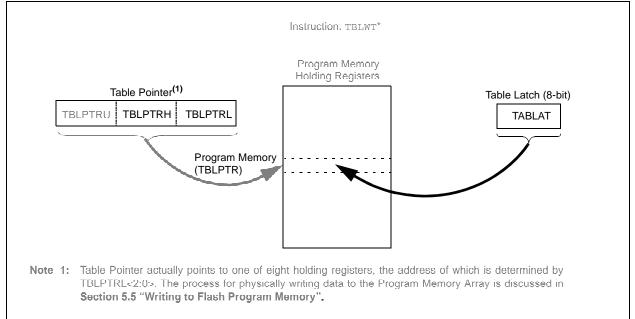

#### FIGURE 5-2: TABLE WRITE OPERATION

#### 5.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- EECON2 register

- TABLAT register

- TBLPTR registers

#### 5.2.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit EEPGD determines if the access will be a program or data EEPROM memory access. When clear, any subsequent operations will operate on the data EEPROM memory. When set, any subsequent operations will operate on the program memory.

Control bit CFGS determines if the access will be to the configuration/calibration registers, or to program memory/data EEPROM memory. When set, subsequent operations will operate on configuration registers, regardless of EEPGD (see Section 23.0 "Special Features of the CPU"). When clear, memory selection access is determined by EEPGD.

The FREE bit, when set, will allow a program memory erase operation. When the FREE bit is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$ Reset, or a WDT Time-out Reset during normal operation. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), due to Reset values of zero.

The WR control bit, initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

| REGISTER 9-8: | PIE2: PER   | IPHERAL                                  | INTERRU         | PT ENABL      | E REGIST     | ER 2      |                |        |

|---------------|-------------|------------------------------------------|-----------------|---------------|--------------|-----------|----------------|--------|

|               | U-0         | R/W-0                                    | U-0             | R/W-0         | R/W-0        | R/W-0     | R/W-0          | R/W-0  |

|               |             | CMIE                                     | _               | EEIE          | BCLIE        | LVDIE     | TMR3IE         | CCP2IE |

|               | bit 7       |                                          |                 |               |              |           |                | bit 0  |

| bit 7         | Unimplem    | ented: Read                              | <b>d as</b> '0' |               |              |           |                |        |

| bit 6         | CMIE: Con   | nparator Inte                            | errupt Enable   | e bit         |              |           |                |        |

|               |             | s the compa<br>es the compa              |                 | •             |              |           |                |        |

| bit 5         | Unimplem    | ented: Read                              | <b>d as</b> '0' |               |              |           |                |        |

| bit 4         | EEIE: Data  | EEPROM/                                  | lash Write      | Operation In  | terrupt Enat | ole bit   |                |        |

|               |             | s the write o<br>es the write o          |                 | •             |              |           |                |        |

| bit 3         | BCLIE: Bu   | s Collision Ir                           | nterrupt Ena    | ble bit       |              |           |                |        |

|               |             | s the bus co<br>is the bus co            |                 | •             |              |           |                |        |

| bit 2         | LVDIE: Lov  | w-Voltage De                             | etect Interru   | pt Enable bit | t            |           |                |        |

|               |             | s the Low-Ves the Low-Ves                |                 |               |              |           |                |        |

| bit 1         | TMR3IE: T   | MR3 Overflo                              | ow Interrupt    | Enable bit    |              |           |                |        |

|               |             | s the TMR3<br>es the TMR3                |                 |               |              |           |                |        |

| bit 0         | 1 = Enable  | CP2 Interru<br>s the CCP2<br>ss the CCP2 | interrupt       | t             |              |           |                |        |

|               | Legend:     |                                          |                 |               |              |           |                |        |

|               | R = Reada   | ble bit                                  | W = W           | ritable bit   | U = Unim     | plemented | bit, read as ' | 0'     |

|               | - n = Value | at POR                                   | '1' = Bi        | it is set     | '0' = Bit is | s cleared | x = Bit is u   | nknown |

| Name    | Bit#  | Buffer Type | Function                                                                             |

|---------|-------|-------------|--------------------------------------------------------------------------------------|

| RJ0/ALE | bit 0 | ST          | Input/output port pin or address latch enable control for external memory interface. |

| RJ1/OE  | bit 1 | ST          | Input/output port pin or output enable control for external memory interface.        |

| RJ2/WRL | bit 2 | ST          | Input/output port pin or write low byte control for external memory interface.       |

| RJ3/WRH | bit 3 | ST          | Input/output port pin or write high byte control for external memory interface.      |

| RJ4/BA0 | bit 4 | ST          | Input/output port pin or byte address 0 control for external memory interface.       |

| RJ5/CE  | bit 5 | ST          | Input/output port pin or chip enable control for external memory interface.          |

| RJ6/LB  | bit 6 | ST          | Input/output port pin or lower byte select control for external memory interface.    |

| RJ7/UB  | bit 7 | ST          | Input/output port pin or upper byte select control for external memory interface.    |

#### TABLE 10-17: PORTJ FUNCTIONS

**Legend:** ST = Schmitt Trigger input

#### TABLE 10-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name  | Bit 7    | Bit 6      | Bit 5      | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|----------|------------|------------|------------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTJ | Read P   | ORTJ pin/  | Write POF  | RTJ Data   | Latch |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| LATJ  | LATJ Da  | ata Output | t Register |            |       |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| TRISJ | Data Dir | ection Co  | ntrol Regi | ster for P | ORTJ  |       |       |       | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

#### 13.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 13-1. Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption. Figure 13-1 is a simplified block diagram of the Timer2 module. Register 13-1 shows the Timer2 Control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

#### 13.1 Timer2 Operation

Timer2 can be used as the PWM time base for the PWM mode of the CCP module. The TMR2 register is readable and writable and is cleared on any device Reset. The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit, TMR2IF (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |  |

|-------|----------|----------|----------|----------|--------|---------|---------|--|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |  |

| bit 7 |          |          |          |          |        |         | bit 0   |  |

#### bit 7 Unimplemented: Read as '0'

bit 6-3 T2OUTPS3:T2OUTPS0: Timer2 Output Postscale Select bits

|   |  | Postscale<br>Postscale |  |

|---|--|------------------------|--|

| • |  |                        |  |

| • |  |                        |  |

| • |  |                        |  |

1111 = 1:16 Postscale

- bit 2 TMR2ON: Timer2 On bit

- 1 = Timer2 is on

- 0 = Timer2 is off

#### bit 1-0 T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits

- 00 =Prescaler is 1

- 01 =Prescaler is 4

- 1x = Prescaler is 16

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

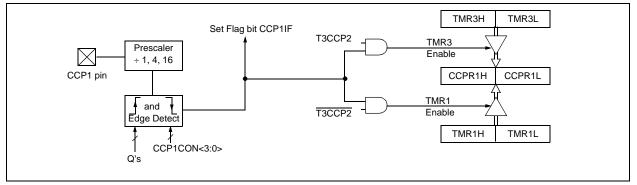

#### 16.2 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 16.2.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-                |

|-------|---------------------------------------------------------|

|       | put, a write to the port can cause a capture condition. |

#### 16.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode, or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 16.1.1 "CCP Modules and Timer Resources").

#### 16.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 16.2.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON, F  | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with   |

|       |             | ; | this value          |

#### FIGURE 16-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

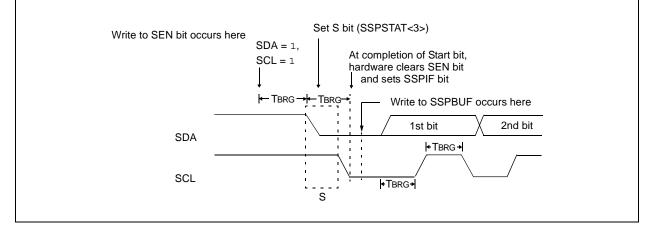

#### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 17-19: FIRST START BIT TIMING

#### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time, after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-21).

After the write to the SSPBUF, each address bit will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 17.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set, or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state, awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 17.4.14 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 17.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

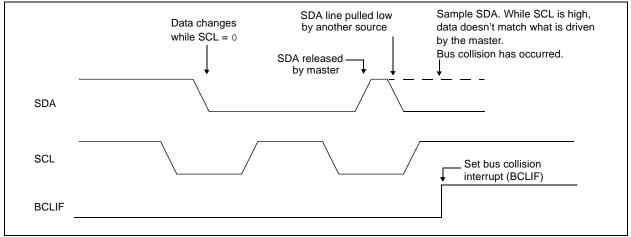

#### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $l^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

© 2003-2013 Microchip Technology Inc.

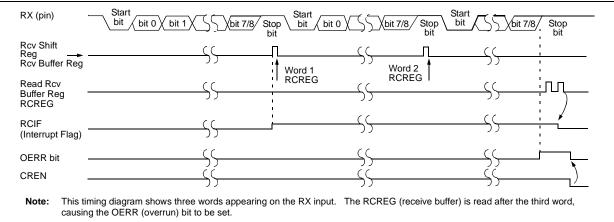

#### FIGURE 18-5: ASYNCHRONOUS RECEPTION

#### TABLE 18-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Value on<br>all other<br>Resets |

|---------------------------------|

| 0 0000 0000                     |

| 0 0000 0000                     |

| 0 0000 0000                     |

| .1 0111 1111                    |

| 000 0000                        |

| 000 0000                        |

| 111 1111                        |

| x 0000 000x                     |

| 0 0000 0000                     |

| 0 0000 -010                     |

| 0 0000 0000                     |

| )<br>)<br>1                     |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

| Name                 | Bit 7        | Bit 6         | Bit 5        | Bit 4     | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|--------------|---------------|--------------|-----------|-------|--------|---------|--------|----------------------|---------------------------------|

| INTCON               | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE       | INTOIE    | RBIE  | TMR0IF | INTOIF  | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                 | PSPIF        | ADIF          | RCIF         | TXIF      | SSPIF | CCP1IF | TMR2IF  | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                 | PSPIE        | ADIE          | RCIE         | TXIE      | SSPIE | CCP1IE | TMR2IE  | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                 | PSPIP        | ADIP          | RCIP         | TXIP      | SSPIP | CCP1IP | TMR2IP  | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR2                 | _            | CMIF          | _            | _         | BCLIF | LVDIF  | TMR3IF  | CCP2IF | -0 0000              | -0 0000                         |

| PIE2                 | _            | CMIE          | _            | _         | BCLIE | LVDIE  | TMR3IE  | CCP2IE | -0 0000              | -0 0000                         |

| IPR2                 | _            | CMIP          | _            | _         | BCLIP | LVDIP  | TMR3IP  | CCP2IP | -0 0000              | -0 0000                         |

| ADRESH               | A/D Resul    | t Register I  | ligh Byte    |           |       |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL               | A/D Resul    | t Register I  | _ow Byte     |           |       |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADCON0               | _            | _             | CHS3         | CHS3      | CHS1  | CHS0   | GO/DONE | ADON   | 00 0000              | 00 0000                         |

| ADCON1               | _            | _             | VCFG1        | VCFG0     | PCFG3 | PCFG2  | PCFG1   | PCFG0  | 00 0000              | 00 0000                         |

| ADCON2               | ADFM         |               | _            | _         | _     | ADCS2  | ADCS1   | ADCS0  | 0 000                | 0 000                           |

| PORTA                | _            | RA6           | RA5          | RA4       | RA3   | RA2    | RA1     | RA0    | 0x 0000              | 0u 0000                         |

| TRISA                | _            | PORTA D       | ata Directio | n Registe | r     |        |         |        | 11 1111              | 11 1111                         |

| PORTF                | RF7          | RF6           | RF5          | RF4       | RF3   | RF2    | RF1     | RF0    | x000 0000            | u000 0000                       |

| LATF                 | LATF7        | LATF6         | LATF5        | LATF4     | LATF3 | LATF2  | LATF1   | LATF0  | xxxx xxxx            | uuuu uuuu                       |

| TRISF                | PORTF Da     | ta Direction  | n Control R  | egister   |       |        |         |        | 1111 1111            | 1111 1111                       |

| PORTH <sup>(1)</sup> | RH7          | RH6           | RH5          | RH4       | RH3   | RH2    | RH1     | RH0    | 0000 xxxx            | 0000 xxxx                       |

| LATH <sup>(1)</sup>  | LATH7        | LATH6         | LATH5        | LATH4     | LATH3 | LATH2  | LATH1   | LATH0  | xxxx xxxx            | uuuu uuuu                       |

| TRISH <sup>(1)</sup> | PORTH Da     | ata Directio  | n Control R  | egister   |       |        |         |        | 1111 1111            | 1111 1111                       |

#### TABLE 19-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Only available on PIC18F8X20 devices.

| ΒZ          |                                      | Branch if Zero                                                     |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

|-------------|--------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--|--|--|--|--|

| Synt        | ax:                                  | [ <i>label</i> ] B                                                 | [ <i>label</i> ] BZ n                                                                                                                                                                                                                                  |       |         |  |  |  |  |  |

| Ope         | rands:                               | -128 ≤ n ≤                                                         | 127                                                                                                                                                                                                                                                    |       |         |  |  |  |  |  |

| Ope         | ration:                              | if Zero bit<br>(PC) + 2 +                                          | is '1'<br>· 2n → PC                                                                                                                                                                                                                                    |       |         |  |  |  |  |  |

| Statu       | us Affected:                         | None                                                               |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

| Enco        | oding:                               | 1110                                                               | 0000 r                                                                                                                                                                                                                                                 | nnn   | nnnn    |  |  |  |  |  |

| Desc        | cription:                            | program w<br>The 2's co<br>added to t<br>have incre<br>instruction | If the Zero bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then |       |         |  |  |  |  |  |

| Word        | ds:                                  | 1                                                                  |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

| Cycl        | es:                                  | 1(2)                                                               | 1(2)                                                                                                                                                                                                                                                   |       |         |  |  |  |  |  |

|             | ycle Activity:                       |                                                                    |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

|             | Q1                                   | Q2                                                                 | Q3                                                                                                                                                                                                                                                     |       | Q4      |  |  |  |  |  |

|             | Decode                               | Read literal<br>'n'                                                | Process<br>Data                                                                                                                                                                                                                                        | Write | e to PC |  |  |  |  |  |

|             | No                                   | No                                                                 | No                                                                                                                                                                                                                                                     |       | No      |  |  |  |  |  |

| IF NL       | operation                            | operation                                                          | operation                                                                                                                                                                                                                                              | n ope | eration |  |  |  |  |  |

|             | o Jump:<br>Q1                        | Q2                                                                 | Q3                                                                                                                                                                                                                                                     |       | Q4      |  |  |  |  |  |

|             | Decode                               | Read literal                                                       | Process                                                                                                                                                                                                                                                |       | No      |  |  |  |  |  |

|             |                                      | 'n'                                                                | Data                                                                                                                                                                                                                                                   | оре   | eration |  |  |  |  |  |

| <u>Exar</u> | <u>nple</u> :<br>Before Instru<br>PC |                                                                    | BZ Jur<br>dress (HEF                                                                                                                                                                                                                                   | -     |         |  |  |  |  |  |

|             | After Instruct                       |                                                                    | uless (ner                                                                                                                                                                                                                                             | (6)   |         |  |  |  |  |  |

|             | If Zero                              | = 1;                                                               |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

|             | PC<br>If Zero                        | = 0;                                                               | dress (Jun                                                                                                                                                                                                                                             | -     |         |  |  |  |  |  |

|             | PC                                   | = ad                                                               | dress (HEF                                                                                                                                                                                                                                             | RE+2) |         |  |  |  |  |  |

|             |                                      |                                                                    |                                                                                                                                                                                                                                                        |       |         |  |  |  |  |  |

| CAL      | .L                                         | Subroutine Call                                                                                                                            |                                                                                            |                                                                |                                                     |                                                           |  |

|----------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------|--|

| Syn      | tax:                                       | [label]                                                                                                                                    | CALL k                                                                                     | [,s]                                                           |                                                     |                                                           |  |

|          |                                            | $0 \le k \le 10$<br>s $\in [0,1]$                                                                                                          | 0 ≤ k ≤ 1048575<br>s ∈ [0,1]                                                               |                                                                |                                                     |                                                           |  |

| Ope      | eration:                                   | $\begin{array}{l} (PC) + 4 \\ k \rightarrow PC < 2 \\ \text{if } s = 1 \\ (W) \rightarrow WS \\ (STATUS) \\ (BSR) \rightarrow \end{array}$ | 20:1>,<br>S,<br>) → STA                                                                    | TUSS                                                           | 5,                                                  |                                                           |  |

| Stat     | us Affected:                               | None                                                                                                                                       |                                                                                            |                                                                |                                                     |                                                           |  |

| 1st v    | oding:<br>word (k<7:0>)<br>word(k<19:8>    |                                                                                                                                            | 110s<br>k <sub>19</sub> kkk                                                                | k <sub>7</sub> k}<br>kkk                                       |                                                     | kkkk <sub>0</sub><br>kkkk <sub>8</sub>                    |  |

|          |                                            | address (I<br>return sta<br>Status and<br>pushed in<br>shadow re<br>and BSRS<br>occurs (de<br>value 'k' is<br>CALL is a                    | ck. If 's'<br>d BSR ro<br>to their f<br>egisters,<br>S. If 's' =<br>efault). T<br>s loaded | = 1, tl<br>egiste<br>respe<br>WS,<br>0, nc<br>hen,<br>i into l | he V<br>ers a<br>ctive<br>STA<br>o up<br>the<br>PC< | V,<br>are also<br>e<br>ATUSS<br>date<br>20-bit<br>:20:1>. |  |

| Wor      | ds:                                        | 2                                                                                                                                          |                                                                                            |                                                                |                                                     |                                                           |  |

| Сус      | les:                                       | 2                                                                                                                                          |                                                                                            |                                                                |                                                     |                                                           |  |

| QC       | Cycle Activity:                            |                                                                                                                                            |                                                                                            |                                                                |                                                     |                                                           |  |

|          | Q1                                         | Q2                                                                                                                                         | Q3                                                                                         | 3                                                              |                                                     | Q4                                                        |  |

|          | Decode                                     | Read literal<br>'k'<7:0>                                                                                                                   | Push P<br>stac                                                                             |                                                                | 'k'                                                 | ad literal<br><19:8>,<br>ite to PC                        |  |

|          | No                                         | No                                                                                                                                         | No                                                                                         |                                                                |                                                     | No                                                        |  |

|          | operation                                  | operation                                                                                                                                  | opera                                                                                      | tion                                                           | op                                                  | peration                                                  |  |

| Example: |                                            | HERE                                                                                                                                       | CALL                                                                                       | THEF                                                           | RΕ,1                                                | -                                                         |  |

|          | Before Instruc                             |                                                                                                                                            |                                                                                            |                                                                |                                                     |                                                           |  |

|          | PC                                         | = address                                                                                                                                  | s (HERE                                                                                    | )                                                              |                                                     |                                                           |  |

|          | After Instructi<br>PC<br>TOS<br>WS<br>BSRS | on<br>= address<br>= address<br>= W<br>= BSR                                                                                               |                                                                                            |                                                                |                                                     |                                                           |  |

BSRS = BSR STATUSS = STATUS

| Syntax:[ label ]CPFSGTf [,a]Operands: $0 \le f \le 255$<br>$a \in [0,1]$ Operation:(f) - (W),<br>skip if (f) > (W)<br>(unsigned comparison)Status Affected:NoneEncoding: $0110$ $010a$ ffffDescription:Compares the contents of data<br>memory location if to the contents<br>of W by performing an unsigned<br>subtraction.If the contents of 'f are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).Words:1Cycles:1(2)<br>Note:Note:3 cycles if skip and followed<br>by a 2-word instruction.Q Cycle Activity:Q1Q2Q3Q1Q2Q3Q4 $\boxed{Pccde}$ Read<br>register 'f' $Process$ No<br>operationIf skip:Q1Q2Q3Q4 $\boxed{Q1}$ Q2Q3Q4 $\boxed{Q2}$ Q3Q4 $\boxed{Q1}$ Q2Q3Q4 $\boxed{Q2}$ Q3Q4 $\boxed{Q1}$ Q2Q3Q4 $\boxed{Q2}$ No <td< th=""><th>CPF</th><th>SGT</th><th>Compare</th><th>f with W, s</th><th>kip if f &gt; W</th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CPF                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SGT            | Compare       | f with W, s         | kip if f > W |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------------|--------------|--|--|--|

| $a \in [0,1]$ Operation: (f) – (W), skip if (f) > (W) (unsigned comparison) Status Affected: None Encoding: 0110 010a ffff ffff Description: Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction. If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is '0', the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default). Words: 1 Cycles: 1(2) Note: 3 cycles if skip and followed by a 2-word instruction. Q Cycle Activity: Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synt                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ax:            | [label] C     | CPFSGT f            | [,a]         |  |  |  |

| skip if (f) > (W)<br>(unsigned comparison)<br>Status Affected: None<br>Encoding: 0110 010a ffff ffff<br>Description: Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).<br>Words: 1<br>Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process No<br>register 'f' Data operation<br>If skip:<br>Q1 Q2 Q3 Q4<br>No<br>operation operation operation<br>If skip and followed by 2-word instruction:<br>Q1 Q2 Q3 Q4<br>No<br>operation operation operation<br>If skip and followed by 2-word instruction:<br>Q1 Q2 Q3 Q4<br>No<br>No<br>operation operation operation<br>If skip and followed by 2-word instruction:<br>Q1 Q2 Q3 Q4<br>No<br>No<br>No<br>operation operation operation<br>If skip and followed by 2-word instruction:<br>Q1 Q2 Q3 Q4<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ope                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rands:         |               | 5                   |              |  |  |  |

| Encoding:0110010affffffffDescription:Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).Words:1Cycles:1(2)<br>Note:3 cycles if skip and followed<br>by a 2-word instruction.Q Cycle Activity:Q1Q1Q2Q3Q4DecodeRead<br>register 'f'DataoperationIf skip:Q1Q1Q2Q3Q4NoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNo <td< td=""><td colspan="2">Operation:</td><td>skip if (f) &gt;</td><td colspan="5">skip if <math>(f) &gt; (W)</math></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                              |                | skip if (f) > | skip if $(f) > (W)$ |              |  |  |  |

| Description:<br>Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).<br>Words: 1<br>Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.<br>Q Cycle Activity:<br>Q1<br>Q2<br>Q3<br>Q4<br>Decode<br>Read<br>register 'f'<br>Data<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                   | us Affected:   | None          |                     |              |  |  |  |

| $\begin{array}{rcl} & \mbox{memory location 'f' to the contents} \\ & \mbox{of W by performing an unsigned} \\ & \mbox{subtraction.} \\ & \mbox{If the contents of 'f' are greater than} \\ & \mbox{the contents of WREG, then the} \\ & \mbox{fetched instruction is discarded and} \\ & \mbox{a NOP is executed instead, making} \\ & \mbox{this a two-cycle instruction. If 'a' is} \\ & \mbox{'o', the Access Bank will be} \\ & \mbox{selected, overriding the BSR value.} \\ & \mbox{If 'a' = 1, then the bank will be} \\ & \mbox{selected as per the BSR value} \\ & \mbox{(default).} \\ \\ \hline & \mbox{Vords: 1} \\ \hline \\ & \mbox{Cycle Activity:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{Read } \mbox{Process } \mbox{No} \\ & \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{Read } \mbox{Process } \mbox{No} \\ & \mbox{operation} \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{No } \mbox{No } \mbox{No} \\ & \mbox{operation} \mbox{operation} \mbox{operation} \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip and followed by 2-word instruction:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{No } \mbox{No } \mbox{No } \mbox{No} \mbox{operation} \mb$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                    | oding:         | 0110          | 010a fi             | ff ffff      |  |  |  |