Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6520t-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Dia Mara                                          | Pin N                    | umber      | Pin Buffer        | Buffer           | Description                                                                                                                       |  |  |

|---------------------------------------------------|--------------------------|------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                          | PIC18F6X20               | PIC18F8X20 | Туре              | Туре             | Description                                                                                                                       |  |  |

|                                                   |                          |            |                   |                  | PORTD is a bidirectional I/O port. These<br>pins have TTL input buffers when externa<br>memory is enabled.                        |  |  |

| RD0/PSP0/AD0<br>RD0<br>PSP0<br>AD0 <sup>(3)</sup> | 58                       | 72         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 0.                                                      |  |  |

| RD1/PSP1/AD1<br>RD1<br>PSP1<br>AD1 <sup>(3)</sup> | 55                       | 69         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 1.                                                      |  |  |

| RD2/PSP2/AD2<br>RD2<br>PSP2<br>AD2 <sup>(3)</sup> | 54                       | 68         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 2.                                                      |  |  |

| RD3/PSP3/AD3<br>RD3<br>PSP3<br>AD3 <sup>(3)</sup> | 53                       | 67         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 3.                                                      |  |  |

| RD4/PSP4/AD4<br>RD4<br>PSP4<br>AD4 <sup>(3)</sup> | 52                       | 66         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 4.                                                      |  |  |

| RD5/PSP5/AD5<br>RD5<br>PSP5<br>AD5 <sup>(3)</sup> | 51                       | 65         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 5.                                                      |  |  |

| RD6/PSP6/AD6<br>RD6<br>PSP6<br>AD6 <sup>(3)</sup> | 50                       | 64         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 6.                                                      |  |  |

| RD7/PSP7/AD7<br>RD7<br>PSP7<br>AD7 <sup>(3)</sup> | 49                       | 63         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 7.                                                      |  |  |

| Legend: TTL = TTL                                 | nmitt Trigger inpu<br>ut |            | evels             | Analog =<br>O =  | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>Open-Drain (no P diode to VDD)</li> </ul> |  |  |

## TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- 4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

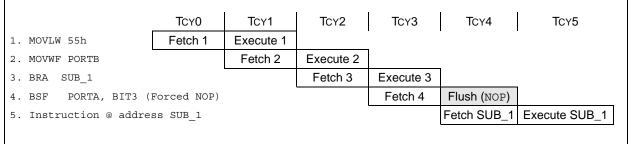

## 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined, such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

## EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

## 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). Figure 4-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4 "PCL, PCLATH and PCLATU").

The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on

word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-5 shows how the instruction "GOTO 00006h" is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 24.0 "Instruction Set Summary"** provides further details of the instruction set.

#### FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

|                |           |                     | <b>LSB</b> = 1 | <b>LSB</b> = 0 | Word Address $\downarrow$ |

|----------------|-----------|---------------------|----------------|----------------|---------------------------|

|                | Program I |                     |                |                | 000000h                   |

|                | Byte Loca | tions $\rightarrow$ |                |                | 000002h                   |

|                | -         |                     |                |                | 000004h                   |

|                |           |                     |                |                | 000006h                   |

| Instruction 1: |           | 055h                | 0Fh            | 55h            | 000008h                   |

| Instruction 2: | GOTO      | 000006h             | EFh            | 03h            | 00000Ah                   |

|                |           |                     | F0h            | 00h            | 00000Ch                   |

| Instruction 3: | MOVFF     | 123h, 456h          | Clh            | 23h            | 00000Eh                   |

|                |           |                     | F4h            | 56h            | 000010h                   |

|                |           |                     |                |                | 000012h                   |

|                |           |                     |                |                | 000014h                   |

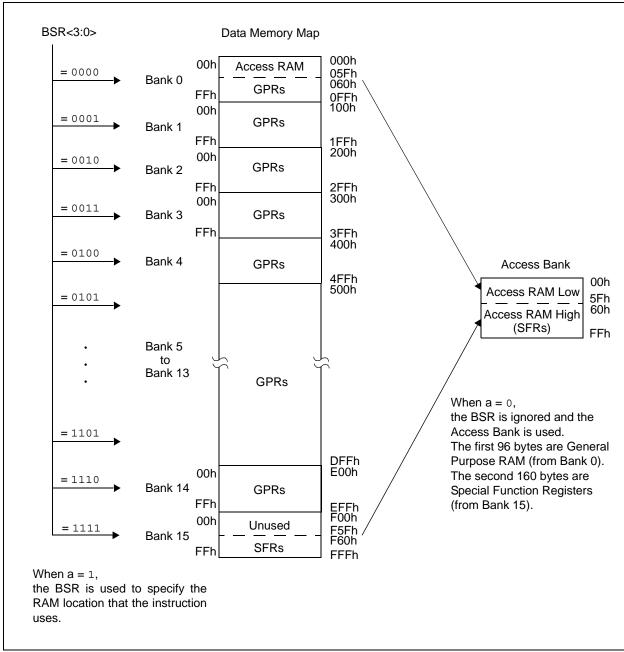

#### FIGURE 4-7: DATA MEMORY MAP FOR PIC18FX620 AND PIC18FX720 DEVICES

#### TABLE 4-2: SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                   | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|------------------------|---------|---------|---------|-----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(3)</sup>   | FBFh    | CCPR1H  | F9Fh    | IPR1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2(3)            | FBEh    | CCPR1L  | F9Eh    | PIR1                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(3)            | FBDh    | CCP1CON | F9Dh    | PIE1                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(3)</sup> | FBCh    | CCPR2H  | F9Ch    | MEMCON <sup>(2)</sup> |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(3)</sup>  | FBBh    | CCPR2L  | F9Bh    | (1)                   |

| FFAh    | PCLATH                  | FDAh    | FSR2H                  | FBAh    | CCP2CON | F9Ah    | TRISJ                 |

| FF9h    | PCL                     | FD9h    | FSR2L                  | FB9h    | CCPR3H  | F99h    | TRISH                 |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                 | FB8h    | CCPR3L  | F98h    | TRISG                 |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                  | FB7h    | CCP3CON | F97h    | TRISF                 |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                  | FB6h    | (1)     | F96h    | TRISE                 |

| FF5h    | TABLAT                  | FD5h    | T0CON                  | FB5h    | CVRCON  | F95h    | TRISD                 |

| FF4h    | PRODH                   | FD4h    | (1)                    | FB4h    | CMCON   | F94h    | TRISC                 |

| FF3h    | PRODL                   | FD3h    | OSCCON                 | FB3h    | TMR3H   | F93h    | TRISB                 |

| FF2h    | INTCON                  | FD2h    | LVDCON                 | FB2h    | TMR3L   | F92h    | TRISA                 |

| FF1h    | INTCON2                 | FD1h    | WDTCON                 | FB1h    | T3CON   | F91h    | LATJ                  |

| FF0h    | INTCON3                 | FD0h    | RCON                   | FB0h    | PSPCON  | F90h    | LATH                  |

| FEFh    | INDF0 <sup>(3)</sup>    | FCFh    | TMR1H                  | FAFh    | SPBRG1  | F8Fh    | LATG                  |

| FEEh    | POSTINC0 <sup>(3)</sup> | FCEh    | TMR1L                  | FAEh    | RCREG1  | F8Eh    | LATF                  |

| FEDh    | POSTDEC0 <sup>(3)</sup> | FCDh    | T1CON                  | FADh    | TXREG1  | F8Dh    | LATE                  |

| FECh    | PREINC0 <sup>(3)</sup>  | FCCh    | TMR2                   | FACh    | TXSTA1  | F8Ch    | LATD                  |

| FEBh    | PLUSW0 <sup>(3)</sup>   | FCBh    | PR2                    | FABh    | RCSTA1  | F8Bh    | LATC                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                  | FAAh    | EEADRH  | F8Ah    | LATB                  |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                 | FA9h    | EEADR   | F89h    | LATA                  |

| FE8h    | WREG                    | FC8h    | SSPADD                 | FA8h    | EEDATA  | F88h    | PORTJ                 |

| FE7h    | INDF1 <sup>(3)</sup>    | FC7h    | SSPSTAT                | FA7h    | EECON2  | F87h    | PORTH                 |

| FE6h    | POSTINC1 <sup>(3)</sup> | FC6h    | SSPCON1                | FA6h    | EECON1  | F86h    | PORTG                 |

| FE5h    | POSTDEC1 <sup>(3)</sup> | FC5h    | SSPCON2                | FA5h    | IPR3    | F85h    | PORTF                 |

| FE4h    | PREINC1 <sup>(3)</sup>  | FC4h    | ADRESH                 | FA4h    | PIR3    | F84h    | PORTE                 |

| FE3h    | PLUSW1 <sup>(3)</sup>   | FC3h    | ADRESL                 | FA3h    | PIE3    | F83h    | PORTD                 |

| FE2h    | FSR1H                   | FC2h    | ADCON0                 | FA2h    | IPR2    | F82h    | PORTC                 |

| FE1h    | FSR1L                   | FC1h    | ADCON1                 | FA1h    | PIR2    | F81h    | PORTB                 |

| FE0h    | BSR                     | FC0h    | ADCON2                 | FA0h    | PIE2    | F80h    | PORTA                 |

Note 1: Unimplemented registers are read as '0'.

2: This register is unused on PIC18F6X20 devices. Always maintain this register clear.

**3:** This is not a physical register.

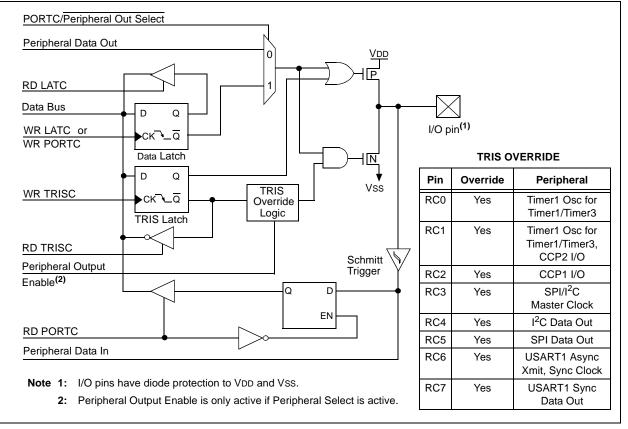

## 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register, read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Note: On a Power-on Reset, these pins are configured as digital inputs.

The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

RC1 is normally configured by configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output<br>; data latches           |

|-------|-------|------------------------------------------------------------------------|

| CLRF  | LATC  | ; Alternate method<br>; to clear output<br>; data latches              |

| MOVLW | 0xCF  | ; Value used to<br>; initialize data<br>; direction                    |

| MOVWF | TRISC | ; Set RC<3:0> as inputs<br>; RC<5:4> as outputs<br>; RC<7:6> as inputs |

|       |       |                                                                        |

## FIGURE 10-8: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

## 10.5 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

PORTE is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. PORTE is multiplexed with the CCP module (Table 10-9).

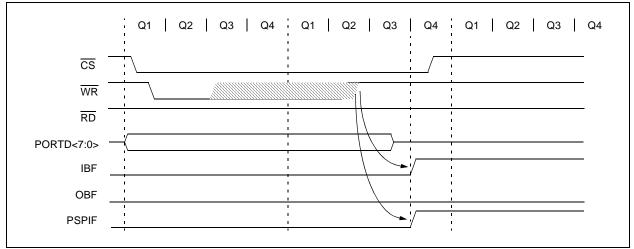

On PIC18F8X20 devices, PORTE is also multiplexed with the system bus as the external memory interface; the I/O bus is available only when the system bus is disabled, by setting the EBDIS bit in the MEMCON register (MEMCON<7>). If the device is configured in Microprocessor or Extended Microcontroller mode, then the PORTE<7:0> becomes the high byte of the address/data bus for the external program memory interface. In Microcontroller mode, the PORTE<2:0> pins become the control inputs for the Parallel Slave Port when bit PSPMODE (PSPCON<4>) is set. (Refer to Section 4.1.1 "PIC18F8X20 Program Memory Modes" for more information on program memory modes.) When the Parallel Slave Port is active, three PORTE pins (RE0/RD/AD8, RE1/WR/AD9 and RE2/CS/AD10) function as its control inputs. This automatically occurs when the PSPMODE bit (PSPCON<4>) is set. Users must also make certain that bits TRISE<2:0> are set to configure the pins as digital inputs and the ADCON1 register is configured for digital I/O. The PORTE PSP control functions are summarized in Table 10-9.

Pin RE7 can be configured as the alternate peripheral pin for CCP module 2 when the device is operating in Microcontroller mode. This is done by clearing the configuration bit, CCP2MX, in configuration register, CONFIG3H (CONFIG3H<0>).

| Note: | For PIC18F8X20 (80-pin) devices operat- |

|-------|-----------------------------------------|

|       | ing in Extended Microcontroller mode,   |

|       | PORTE defaults to the system bus on     |

|       | Power-on Reset.                         |

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE | ; Initialize PORTE by<br>; clearing output                     |

|-------|-------|----------------------------------------------------------------|

| CLRF  | LATE  | ; data latches<br>; Alternate method                           |

|       |       | ; to clear output<br>; data latches                            |

| MOVLW | 0x03  | ; Value used to<br>: initialize data                           |

| MOVWF | TRISE | ; direction<br>; Set RE1:RE0 as inputs<br>; RE7:RE2 as outputs |

|       |       |                                                                |

| REGISTER 10-1: | PSPCON REGISTER                                                                                                                                             |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-----|-----|-----|-------|--|--|

|                | R-0                                                                                                                                                         | R-0                                                                                                                                                                     | R/W-0 | R/W-0   | U-0 | U-0 | U-0 | U-0   |  |  |

|                | IBF                                                                                                                                                         | OBF                                                                                                                                                                     | IBOV  | PSPMODE |     |     |     | _     |  |  |

|                | bit 7                                                                                                                                                       |                                                                                                                                                                         |       |         |     |     |     | bit 0 |  |  |

| bit 7          | 1 = A word                                                                                                                                                  | <ul> <li>IBF: Input Buffer Full Status bit</li> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |       |         |     |     |     |       |  |  |

| bit 6          | 1 = The ou                                                                                                                                                  | <b>OBF:</b> Output Buffer Full Status bit<br>1 = The output buffer still holds a previously written word                                                                |       |         |     |     |     |       |  |  |

| bit 5          | <ul> <li>0 = The output buffer has been read</li> <li>IBOV: Input Buffer Overflow Detect bit</li> </ul>                                                     |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

|                | <ul> <li>1 = A write occurred when a previously input word has not been read<br/>(must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

| bit 4          | PSPMODE                                                                                                                                                     | PSPMODE: Parallel Slave Port Mode Select bit                                                                                                                            |       |         |     |     |     |       |  |  |

|                | <ul><li>1 = Parallel Slave Port mode</li><li>0 = General Purpose I/O mode</li></ul>                                                                         |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

| bit 3-0        | Unimplemented: Read as '0'                                                                                                                                  |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

|                | Legend:                                                                                                                                                     |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

|                | $R = Readable bit \qquad W = Writable bit \qquad U = Unimplemented bit, read as '0'$                                                                        |                                                                                                                                                                         |       |         |     |     |     |       |  |  |

#### FIGURE 10-24: PARALLEL SLAVE PORT WRITE WAVEFORMS

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

| EXAMPLE | 12-1:  | IMPLEMENTIN  | IG A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE |

|---------|--------|--------------|-------------------------------------------------------|

| RTCinit |        |              |                                                       |

|         | MOVLW  | 0x80         | ; Preload TMR1 register pair                          |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                               |

|         | CLRF   | TMR1L        |                                                       |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                       |

|         | MOVWF  | T10SC        | ; Asynchronous operation, external oscillator         |

|         | CLRF   | secs         | ; Initialize timekeeping registers                    |

|         | CLRF   | mins         | ;                                                     |

|         | MOVLW  | .12          |                                                       |

|         | MOVWF  | hours        |                                                       |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                             |

|         | RETURN |              |                                                       |

| RTCisr  |        |              |                                                       |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                          |

|         | BCF    | PIR1, TMR1IF |                                                       |

|         | INCF   | secs, F      | ; Increment seconds                                   |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | secs         | ; Clear seconds                                       |

|         | INCF   | mins, F      | ; Increment minutes                                   |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | mins         | ; clear minutes                                       |

|         | INCF   | hours, F     | ; Increment hours                                     |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                   |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | MOVLW  | .01          | ; Reset hours to 1                                    |

|         | MOVWF  | hours        |                                                       |

|         | RETURN |              | ; Done                                                |

| J       |        |              |                                                       |

#### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

#### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7                                                                       | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|--------|-----------------------------------------------------------------------------|-----------|---------|---------|---------|--------|--------|--------|---------------|------|------|-----------------------|

| INTCON | GIE/GIEH                                                                    | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 0000          | 0000 | 0000 | 0000                  |

| PIR1   | PSPIF                                                                       | ADIF      | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000          | 0000 | 0000 | 0000                  |

| PIE1   | PSPIE                                                                       | ADIE      | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000          | 0000 | 0000 | 0000                  |

| IPR1   | PSPIP                                                                       | ADIP      | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP | 0111          | 1111 | 0111 | 1111                  |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |           |         |         |         |        |        |        | xxxx          | xxxx | uuuu | uuuu                  |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |           |         |         |         |        |        |        | xxxx          | xxxx | uuuu | uuuu                  |

| T1CON  | RD16                                                                        | —         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0-00          | 0000 | u-uu | uuuu                  |

$\label{eq:logend: Legend: Legend: u = unchanged, -= unimplemented, read as `0`. Shaded cells are not used by the Timer1 module.$

### 16.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 16.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode.

#### TABLE 16-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer1 or Timer3 |

| PWM      | Timer2 or Timer4 |

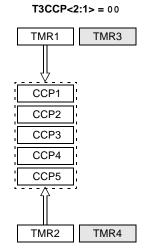

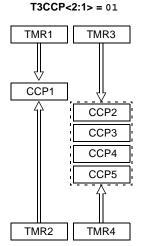

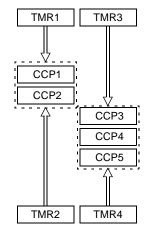

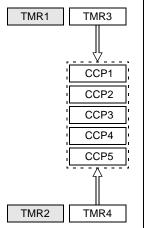

The assignment of a particular timer to a module is determined by the Timer-to-CCP Enable bits in the T3CON register (Register 14-1). Depending on the configuration selected, up to four timers may be active at once, with modules in the same configuration (Capture/Compare or PWM) sharing timer resources. The possible configurations are shown in Figure 16-1.

## FIGURE 16-1: CCP AND TIMER INTERCONNECT CONFIGURATIONS

T3CCP<2:1> = 10

T3CCP<2:1> = 11

Timer1 is used for all Capture and Compare operations for all CCP modules. Timer2 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer3 and Timer4 are not available.

Timer1 and Timer2 are used for Capture and Compare or PWM operations for CCP1 only (depending on selected mode).

All other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base, if they are in Capture/ Compare or PWM modes. Timer1 and Timer2 are used for Capture and Compare or PWM operations for CCP1 and CCP2 only (depending on the mode selected for each module). Both modules may use a timer as a common time base if they are both in Capture/Compare or PWM modes.

The other modules use either Timer3 or Timer4. Modules may share either timer resource as a common time base if they are in Capture/ Compare or PWM modes. Timer3 is used for all Capture and Compare operations for all CCP modules. Timer4 is used for PWM operations for all CCP modules. Modules may share either timer resource as a common time base.

Timer1 and Timer2 are not available.

## 17.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON1<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The MSSP consists of a Transmit/Receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full detect bit, BF (SSPSTAT<0>) and the interrupt flag bit, SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision detect bit, WCOL (SSPCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit, BF (SSPSTAT<0>), indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP Status register (SSPSTAT) indicates the various status conditions.

#### EQUATION 17-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP | BTFSS | SSPSTAT, BF | ;Has data been received (transmit complete)? |

|------|-------|-------------|----------------------------------------------|

|      | BRA   | LOOP        | ; No                                         |

|      | MOVF  | SSPBUF, W   | ;WREG reg = contents of SSPBUF               |

|      | MOVWF | RXDATA      | ;Save in user RAM, if data is meaningful     |

|      | MOVF  | TXDATA, W   | ;W reg = contents of TXDATA                  |

|      | MOVWF | SSPBUF      | ;New data to transmit                        |

|      |       |             |                                              |

## 18.2 USART Asynchronous Mode

In this mode, the USARTs use standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent, but use the same data format and baud rate. The Baud Rate Generator produces a clock, either 16 or 64 times the bit shift rate, depending on bit BRGH (TXSTAx<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTAx<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 18.2.1 USART ASYNCHRONOUS TRANSMITTER

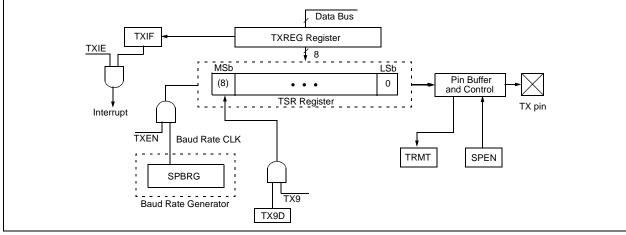

The USART transmitter block diagram is shown in Figure 18-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREGx register (if available). Once the TXREGx register transfers the data to the TSR register (occurs in one Tcr), the TXREGx register is empty and flag bit, TXx1IF (PIR1<4> for USART1,

PIR3<4> for USART2), is set. This interrupt can be enabled/disabled by setting/clearing enable bit, TXxIE (PIE1<4> for USART1, PIE<4> for USART2). Flag bit TXxIF will be set, regardless of the state of enable bit TXxIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register. While flag bit TXIF indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- Note 1: The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set.

To set up an Asynchronous Transmission:

- Initialize the SPBRGx register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 18.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit TXxIE in the appropriate PIE register.

- 4. If 9-bit transmission is desired, set transmit bit TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXxIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREGx register (starts transmission).

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG. The flag bit becomes valid in the second instruction cycle following the load instruction.

### FIGURE 18-1: USART TRANSMIT BLOCK DIAGRAM

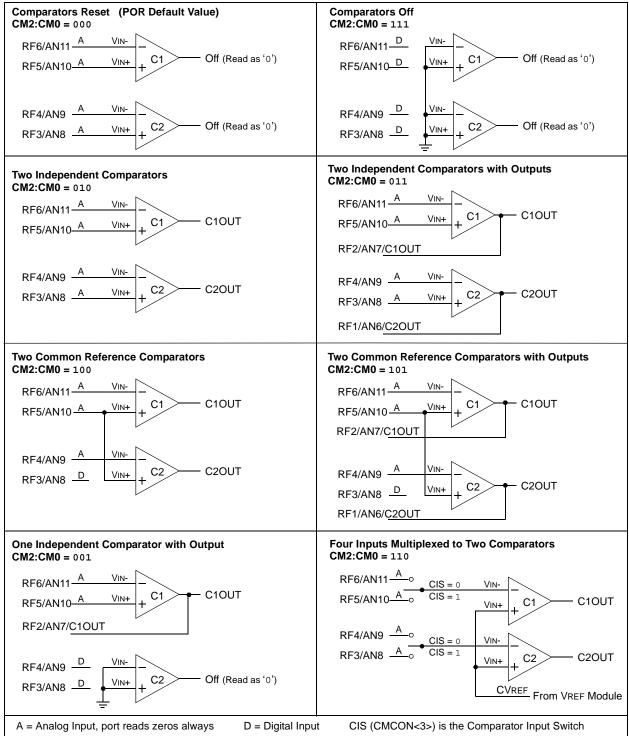

### 20.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select these modes. Figure 20-1 shows the eight possible modes. The TRISF register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in the Electrical Specifications (Section 26.0 "Electrical Characteristics").

**Note:** Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

| Mnemonic,<br>Operands |        | Description                    | Qualas | 16-Bit Instruction Word |      |          |          | Status            | Natas |

|-----------------------|--------|--------------------------------|--------|-------------------------|------|----------|----------|-------------------|-------|

|                       |        | Description                    | Cycles | MSb                     |      |          | LSb      | Affected          | Notes |

| CONTROL               | OPERAT | IONS                           |        |                         |      |          |          |                   |       |

| BC                    | n      | Branch if Carry                | 1 (2)  | 1110                    | 0010 | nnnn     | nnnn     | None              |       |

| BN                    | n      | Branch if Negative             | 1 (2)  | 1110                    | 0110 | nnnn     | nnnn     | None              |       |

| BNC                   | n      | Branch if Not Carry            | 1 (2)  | 1110                    | 0011 | nnnn     | nnnn     | None              |       |

| BNN                   | n      | Branch if Not Negative         | 1 (2)  | 1110                    | 0111 | nnnn     | nnnn     | None              |       |

| BNOV                  | n      | Branch if Not Overflow         | 1 (2)  | 1110                    | 0101 | nnnn     | nnnn     | None              |       |

| BNZ                   | n      | Branch if Not Zero             | 1 (2)  | 1110                    | 0001 | nnnn     | nnnn     | None              |       |

| BOV                   | n      | Branch if Overflow             | 1 (2)  | 1110                    | 0100 | nnnn     | nnnn     | None              |       |

| BRA                   | n      | Branch Unconditionally         | 2      | 1101                    | 0nnn | nnnn     | nnnn     | None              |       |

| BZ                    | n      | Branch if Zero                 | 1 (2)  | 1110                    | 0000 | nnnn     | nnnn     | None              |       |

| CALL                  | n, s   | Call subroutine 1st word       | 2      | 1110                    | 110s | kkkk     | kkkk     | None              |       |

|                       |        | 2nd word                       |        | 1111                    | kkkk | kkkk     | kkkk     |                   |       |

| CLRWDT                | _      | Clear Watchdog Timer           | 1      | 0000                    | 0000 | 0000     | 0100     | TO, PD            |       |

| DAW                   | _      | Decimal Adjust WREG            | 1      | 0000                    | 0000 | 0000     | 0111     | С                 |       |

| GOTO                  | n      | Go to address 1st word         | 2      | 1110                    | 1111 | kkkk     | kkkk     | None              |       |

|                       |        | 2nd word                       |        | 1111                    | kkkk | kkkk     | kkkk     |                   |       |

| NOP                   | —      | No Operation                   | 1      | 0000                    | 0000 | 0000     | 0000     | None              |       |

| NOP                   | —      | No Operation                   | 1      | 1111                    | xxxx | XXXX     | xxxx     | None              | 4     |

| POP                   | —      | Pop top of return stack (TOS)  | 1      | 0000                    | 0000 | 0000     | 0110     | None              |       |

| PUSH                  | _      | Push top of return stack (TOS) | 1      | 0000                    | 0000 | 0000     | 0101     | None              |       |

| RCALL                 | n      | Relative Call                  | 2      | 1101                    | 1nnn | nnnn     | nnnn     | None              |       |

| RESET                 |        | Software device Reset          | 1      | 0000                    | 0000 | 1111     | 1111     | All               |       |

| RETFIE                | S      | Return from interrupt enable   | 2      | 0000                    | 0000 | 0001     | 000s     | GIE/GIEH,         |       |

| RETLW                 | Ŀ      | Return with literal in WREG    | 2      |                         | 1100 | 1_1_1_1_ | 1-1-1-1- | PEIE/GIEL<br>None | 1     |

|                       | k      |                                | 2      | 0000                    | 1100 | kkkk     | kkkk     |                   |       |

| RETURN                | S      | Return from Subroutine         | 2      | 0000                    | 0000 | 0001     | 001s     | None              |       |

| SLEEP                 | _      | Go into Standby mode           | 1      | 0000                    | 0000 | 0000     | 0011     | TO, PD            |       |

#### TABLE 24-1: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note** 1: When a Port register is modified as a function of itself (e.g., MOVF PORTE, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| ΒZ    |                                 | Branch if                                                                      | Branch if Zero                                                                                                                                                                                                                                                                     |     |                 |  |  |  |  |

|-------|---------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|--|--|--|--|

| Synt  | ax:                             | [label] B                                                                      | [ <i>label</i> ] BZ n                                                                                                                                                                                                                                                              |     |                 |  |  |  |  |

| Ope   | rands:                          | -128 ≤ n ≤                                                                     | $-128 \le n \le 127$                                                                                                                                                                                                                                                               |     |                 |  |  |  |  |

| Ope   | ration:                         |                                                                                | if Zero bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                               |     |                 |  |  |  |  |

| Statu | us Affected:                    | None                                                                           | None                                                                                                                                                                                                                                                                               |     |                 |  |  |  |  |

| Enco  | oding:                          | 1110                                                                           | 0000 ni                                                                                                                                                                                                                                                                            | nnn | nnnn            |  |  |  |  |

| Desc  | cription:                       | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | If the Zero bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |     |                 |  |  |  |  |

| Word  | ds:                             | 1                                                                              |                                                                                                                                                                                                                                                                                    |     |                 |  |  |  |  |

| Cycl  | es:                             | 1(2)                                                                           | 1(2)                                                                                                                                                                                                                                                                               |     |                 |  |  |  |  |

|       | cycle Activity:                 |                                                                                |                                                                                                                                                                                                                                                                                    |     |                 |  |  |  |  |

|       | Q1                              | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                 |     | Q4              |  |  |  |  |

|       | Decode                          | Read literal<br>'n'                                                            | Process<br>Data                                                                                                                                                                                                                                                                    | Wri | te to PC        |  |  |  |  |

|       | No                              | No                                                                             | No                                                                                                                                                                                                                                                                                 |     | No              |  |  |  |  |

| If N  | operation<br>o Jump:            | operation                                                                      | operation                                                                                                                                                                                                                                                                          | ор  | operation<br>Q4 |  |  |  |  |

|       | Q1                              | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                 |     |                 |  |  |  |  |

|       | Decode                          | Read literal                                                                   | Process                                                                                                                                                                                                                                                                            |     | No              |  |  |  |  |

|       |                                 | 'n'                                                                            | Data                                                                                                                                                                                                                                                                               | ор  | operation       |  |  |  |  |

|       | <u>mple</u> :<br>Before Instru  | HERE                                                                           | BZ Jum                                                                                                                                                                                                                                                                             | p   |                 |  |  |  |  |

|       | PC                              |                                                                                | = address (HERE)                                                                                                                                                                                                                                                                   |     |                 |  |  |  |  |

|       | After Instruct<br>If Zero<br>PC | = 1;                                                                           | = 1;                                                                                                                                                                                                                                                                               |     |                 |  |  |  |  |

|       | If Zero<br>PC                   | = 0;                                                                           | = 0;                                                                                                                                                                                                                                                                               |     |                 |  |  |  |  |

|       |                                 |                                                                                |                                                                                                                                                                                                                                                                                    |     |                 |  |  |  |  |

| CAL        | .L                                         | Subrouti                                                                                                                                                     | ne Call                                             |                                   |                                          |                                        |  |  |

|------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|------------------------------------------|----------------------------------------|--|--|

| Syn        | tax:                                       | [ <i>label</i> ] CALL k [,s]                                                                                                                                 |                                                     |                                   |                                          |                                        |  |  |

| Ope        | erands:                                    | $0 \le k \le 1048575$<br>s $\in [0,1]$                                                                                                                       |                                                     |                                   |                                          |                                        |  |  |

| Ope        | eration:                                   | $(PC) + 4 \rightarrow TOS,$<br>$k \rightarrow PC<20:1>,$<br>if s = 1<br>$(W) \rightarrow WS,$<br>$(STATUS) \rightarrow STATUSS,$<br>$(BSR) \rightarrow BSRS$ |                                                     |                                   |                                          |                                        |  |  |

| Stat       | us Affected:                               | None                                                                                                                                                         |                                                     |                                   |                                          |                                        |  |  |

| 1st v      | oding:<br>word (k<7:0>)<br>word(k<19:8>    |                                                                                                                                                              | 110s k <sub>7</sub> kkl<br>k <sub>19</sub> kkk kkkk |                                   |                                          | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |  |

|            |                                            | = 1, tl<br>egiste<br>respe<br>WS,<br>0, nc                                                                                                                   | he V<br>ers a<br>ctive<br>STA<br>o up<br>the<br>PC< | ATUSS<br>date<br>20-bit<br>20:1>. |                                          |                                        |  |  |

| Wor        | ds:                                        | 2                                                                                                                                                            |                                                     |                                   |                                          |                                        |  |  |

| Сус        | les:                                       | 2                                                                                                                                                            |                                                     |                                   |                                          |                                        |  |  |

| QC         | Cycle Activity:                            |                                                                                                                                                              |                                                     |                                   |                                          |                                        |  |  |

|            | Q1                                         | Q2                                                                                                                                                           | Q                                                   | 3                                 |                                          | Q4                                     |  |  |

|            | Decode                                     | Read literal<br>'k'<7:0>                                                                                                                                     | Push P<br>stac                                      |                                   | Read litera<br>'k'<19:8>,<br>Write to PC | <19:8>,                                |  |  |

|            | No                                         | No                                                                                                                                                           | No                                                  |                                   |                                          | No                                     |  |  |

|            | operation                                  | operation                                                                                                                                                    | operation operation opera                           |                                   |                                          | peration                               |  |  |

| <u>Exa</u> | mple:                                      | HERE                                                                                                                                                         | HERE CALL THERE, 1                                  |                                   |                                          |                                        |  |  |

|            | Before Instruc                             |                                                                                                                                                              |                                                     |                                   |                                          |                                        |  |  |

|            | PC                                         | = address (HERE)                                                                                                                                             |                                                     |                                   |                                          |                                        |  |  |

|            | After Instructi<br>PC<br>TOS<br>WS<br>BSRS | on<br>= address<br>= address<br>= W<br>= BSR                                                                                                                 |                                                     |                                   |                                          |                                        |  |  |

BSRS = BSR STATUSS = STATUS

## 26.1 DC Characteristics: Supply Voltage PIC18F6520/8520/6620/8620/6720/8720 (Industrial, Extended) PIC18LF6520/8520/6620/8620/6720/8720 (Industrial)

|              | <b>F6520/852</b><br>ustrial) | 0/6620/8620/6720/8720                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |           |       |                                           |  |  |

|--------------|------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------------------------------------------|--|--|

|              | 6520/8520<br>ustrial, Ext    | /6620/8620/6720/8720<br>ended)                                      |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |           |       |                                           |  |  |

| Param<br>No. | Symbol                       | Characteristic                                                      | Min                                                                                                                                | Тур                                                                                                                                                                                     | Max       | Units | Conditions                                |  |  |

| D001         | Vdd                          | Supply Voltage                                                      |                                                                                                                                    |                                                                                                                                                                                         |           |       |                                           |  |  |

|              |                              | PIC18LFXX20                                                         | 2.0                                                                                                                                | _                                                                                                                                                                                       | 5.5       | V     | HS, XT, RC and LP Oscillator mode         |  |  |

|              |                              | PIC18FXX20                                                          | 4.2                                                                                                                                | _                                                                                                                                                                                       | 5.5       | V     |                                           |  |  |

| D001A        | AVdd                         | Analog Supply Voltage                                               | Vdd - 0.3                                                                                                                          | _                                                                                                                                                                                       | VDD + 0.3 | V     |                                           |  |  |

| D002         | Vdr                          | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5                                                                                                                                | —                                                                                                                                                                                       | -         | V     |                                           |  |  |

| D003         | VPOR                         | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                                                                                                  | —                                                                                                                                                                                       | 0.7       | V     | See section on Power-on Reset for details |  |  |

| D004         | Svdd                         | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                               | —                                                                                                                                                                                       | _         | V/ms  | See section on Power-on Reset for details |  |  |

| D005         | VBOR                         | Brown-out Reset Voltage                                             | _                                                                                                                                  |                                                                                                                                                                                         |           |       |                                           |  |  |

|              |                              | BORV1:BORV0 = 11                                                    | N/A                                                                                                                                |                                                                                                                                                                                         | N/A       | V     | Reserved                                  |  |  |

|              |                              | BORV1:BORV0 = 10                                                    | 2.64                                                                                                                               | _                                                                                                                                                                                       | 2.92      | V     |                                           |  |  |

|              |                              | BORV1:BORV0 = 01                                                    | 4.11                                                                                                                               | _                                                                                                                                                                                       | 4.55      | V     |                                           |  |  |

|              |                              | BORV1:BORV0 = 00                                                    | 4.41                                                                                                                               |                                                                                                                                                                                         | 4.87      | V     |                                           |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

| Param<br>No. | Symbol  | Charact                         | eristic                   | Min              | Max  | Units | Conditions                   |

|--------------|---------|---------------------------------|---------------------------|------------------|------|-------|------------------------------|

| 100          | Тнідн   | Clock High Time                 | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|              |         |                                 | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms    |                              |

| 101          | TLOW    | Clock Low Time                  | 100 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                                 | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    |                              |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) |      | ms    |                              |

| 102          | TR      | SDA and SCL                     | 100 kHz mode              | —                | 1000 | ns    | CB is specified to be from   |

|              |         | Rise Time                       | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | _                | 300  | ns    |                              |

| 103          | TF      | SDA and SCL                     | 100 kHz mode              | —                | 300  | ns    | CB is specified to be from   |

|              |         | Fall Time                       | 400 kHz mode              | 20 + 0.1 Св      | 300  | ns    | 10 to 400 pF                 |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | _                | 100  | ns    |                              |

| 90           | TSU:STA | A Start Condition<br>Setup Time | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | Only relevant for            |

|              |         |                                 | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | Repeated Start condition     |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                              |

| 91           | THD:STA | Start Condition<br>Hold Time    | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    | After this period, the first |

|              |         |                                 | 400 kHz mode              | 2(Tosc)(BRG + 1) | _    | ms    | clock pulse is generated     |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                              |

| 106          | THD:DAT | Data Input<br>Hold Time         | 100 kHz mode              | 0                |      | ns    |                              |

|              |         |                                 | 400 kHz mode              | 0                | 0.9  | ms    |                              |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | TBD              | _    | ns    |                              |

| 107          | TSU:DAT | Data Input                      | 100 kHz mode              | 250              | _    | ns    | (Note 2)                     |

|              |         | Setup Time                      | 400 kHz mode              | 100              |      | ns    |                              |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | TBD              | —    | ns    |                              |

| 92           | TSU:STO | Stop Condition                  | 100 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|              |         | Setup Time                      | 400 kHz mode              | 2(Tosc)(BRG + 1) |      | ms    |                              |

|              |         |                                 | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —    | ms    |                              |