Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6520t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The data memory map is in turn divided into 16 banks of 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory space contains both Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (0FFFh) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

PIC18FX520 devices have 2048 bytes of data RAM, extending from Bank 0 to Bank 7 (000h through 7FFh). PIC18FX620 and PIC18FX720 devices have 3840 bytes of data RAM, extending from Bank 0 to Bank 14 (000h through EFFh). The organization of the data memory space for these devices is shown in Figure 4-6 and Figure 4-7.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 4.10** "Access Bank" provides a detailed description of the Access RAM.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12 "Indirect Addressing, INDF and FSR Registers".

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as General Purpose Registers by all instructions. The top section of Bank 15 (F60h to FFFh) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2 and Table 4-3.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature. The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations are unimplemented and read as '0's. The addresses for the SFRs are listed in Table 4-2.

#### 5.4 Erasing Flash Program Memory

The minimum erase block is 32 words or 64 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 64 bytes of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. TBLPTR<5:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 5.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer with address of row being erased.

- 2. Set the EECON1 register for the erase operation:

- set EEPGD bit to point to program memory;

- clear the CFGS bit to access program memory;

- set WREN bit to enable writes;

- set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase (about 2 ms using internal timer).

- 8. Execute a NOP.

- 9. Re-enable interrupts.

|                      | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL | ; load TBLPTR with the base<br>; address of the memory block |  |  |  |  |

|----------------------|----------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| ERASE_ROW            | BSF<br>BCF<br>BSF<br>BSF<br>BCF                    | EECON1, EEPGD<br>EECON1, CFGS<br>EECON1, WREN<br>EECON1, FREE<br>INTCON, GIE        | , 1                                                          |  |  |  |  |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>NOP     | 55h<br>EECON2<br>AAh<br>EECON2<br>EECON1, WR                                        | ; write 55H<br>; write AAH<br>; start erase (CPU stall)      |  |  |  |  |

|                      | BSF                                                | INTCON, GIE                                                                         | ; re-enable interrupts                                       |  |  |  |  |

#### EXAMPLE 5-2: ERASING A FLASH PROGRAM MEMORY ROW

NOTES:

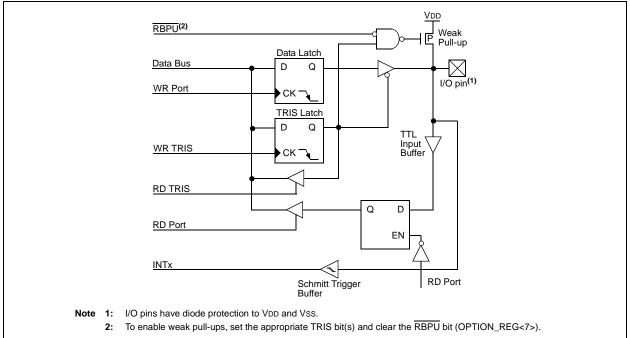

#### FIGURE 10-6: BLOCK DIAGRAM OF RB2:RB0 PINS

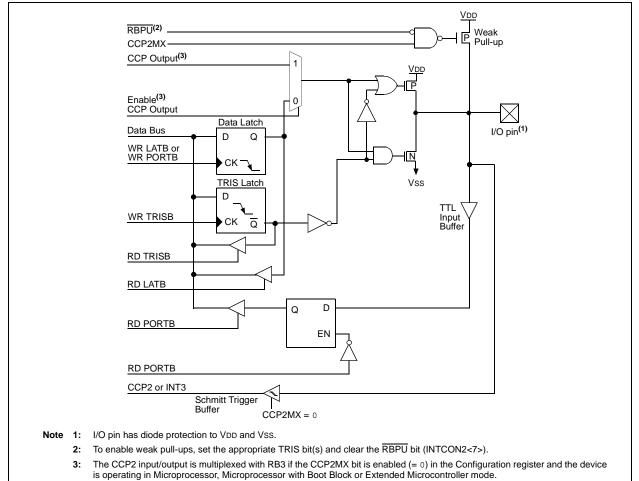

#### FIGURE 10-7: BLOCK DIAGRAM OF RB3 PIN

| Name                          | Bit#  | Buffer Type | Function                                                                                                                                     |

|-------------------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T13CKI              | bit 0 | ST          | Input/output port pin, Timer1 oscillator output or Timer1/Timer3 clock input.                                                                |

| RC1/T1OSI/CCP2 <sup>(1)</sup> | bit 1 | ST          | Input/output port pin, Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM output (when CCP2MX configuration bit is disabled). |

| RC2/CCP1                      | bit 2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                                                                     |

| RC3/SCK/SCL                   | bit 3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $I^2C$ modes.                                                                  |

| RC4/SDI/SDA                   | bit 4 | ST          | RC4 can also be the SPI data in (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                              |

| RC5/SDO                       | bit 5 | ST          | Input/output port pin or synchronous serial port data output.                                                                                |

| RC6/TX1/CK1                   | bit 6 | ST          | Input/output port pin, addressable USART1 asynchronous transmit or addressable USART1 synchronous clock.                                     |

| RC7/RX1/DT1                   | bit 7 | ST          | Input/output port pin, addressable USART1 asynchronous receive or addressable USART1 synchronous data.                                       |

#### TABLE 10-5:PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

Note 1: RB3 is the alternate assignment for CCP2 when CCP2MX is set.

#### TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6     | Bit 5      | Bit 4     | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|--------|-----------|------------|-----------|-----------|-----------|-------|-------|----------------------|---------------------------------|

| PORTC | RC7    | RC6       | RC5        | RC4       | RC3       | RC2       | RC1   | RC0   | xxxx xxxx            | uuuu uuuu                       |

| LATC  | LATC D | ata Outpu |            | xxxx xxxx | uuuu uuuu |           |       |       |                      |                                 |

| TRISC | PORTC  | Data Dire | ection Reg |           | 1111 1111 | 1111 1111 |       |       |                      |                                 |

**Legend:** x = unknown, u = unchanged

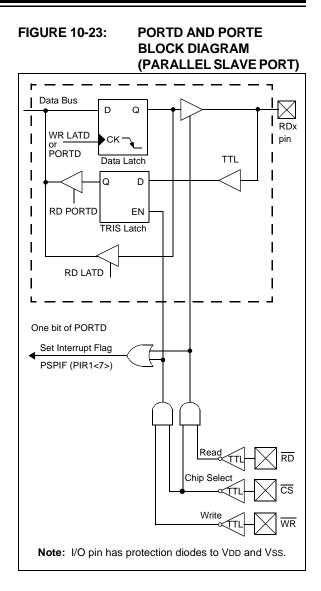

#### 10.10 Parallel Slave Port

PORTD also operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (PSPCON<4>) is set. It is asynchronously readable and writable by the external world through the RD control input pin, RE0/RD/AD8 and the WR control input pin, RE1/WR/AD9.

| Note: | For PIC18F8X20 devices, th | e Para | llel |

|-------|----------------------------|--------|------|

|       | Slave Port is available    | only   | in   |

|       | Microcontroller mode.      |        |      |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AD8 to be the RD input, RE1/WR/AD9 to be the WR input and RE2/ CS/AD10 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG2:PCFG0 (ADCON1<2:0>), must be set which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (PSPCON<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs) and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

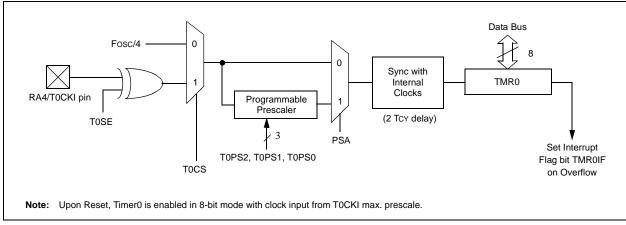

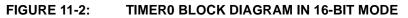

### 11.0 TIMER0 MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/counter

- Readable and writable

- Dedicated 8-bit software programmable prescaler

- · Clock source selectable to be external or internal

- Interrupt-on-overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

Figure 11-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The T0CON register (Register 11-1) is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

#### REGISTER 11-1: T0CON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

- bit 7 TMR0ON: Timer0 On/Off Control bit

- 1 = Enables Timer0

- 0 = Stops Timer0

- bit 6 **T08BIT:** Timer0 8-bit/16-bit Control bit

- 1 = Timer0 is configured as an 8-bit timer/counter

- 0 = Timer0 is configured as a 16-bit timer/counter

- bit 5 **TOCS:** Timer0 Clock Source Select bit

- 1 = Transition on TOCKI pin

- 0 = Internal instruction cycle clock (CLKO)

- bit 4 TOSE: Timer0 Source Edge Select bit

- 1 = Increment on high-to-low transition on T0CKI pin

- 0 = Increment on low-to-high transition on T0CKI pin

- bit 3 **PSA:** Timer0 Prescaler Assignment bit

- 1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.

- 0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.

- bit 2-0 TOPS2:TOPS0: Timer0 Prescaler Select bits

- 111 = 1:256 prescale value

- 110 = 1:128 prescale value

- 101 = 1:64 prescale value

- 100 = 1:32 prescale value

- 011 = 1:16 prescale value

- 010 = 1:8 prescale value

- 001 = 1:4 prescale value

- 000 = 1:2 prescale value

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### FIGURE 11-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

NOTES:

Register 12-1 details the Timer1 Control register. This register controls the operating mode of the Timer1

module and contains the Timer1 Oscillator Enable bit

(T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

Timer1 can also be used to provide Real-Time Clock

(RTC) functionality to applications, with only a minimal addition of external components and code overhead.

### 12.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module special event trigger

Figure 12-1 is a simplified block diagram of the Timer1 module.

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| RD16  | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON |

| bit 7 |     |         |         |         |        |        | bit 0  |

| bit 7   | RD16: 16-bit Read/Write Mode Enable bit                                                |                                                                   |                      |                    |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|--------------------|--|--|--|--|--|

|         | 1 = Enables register read/                                                             | write of Timer1 in one                                            | + 16-bit operation   |                    |  |  |  |  |  |

|         | 0 = Enables register read/\                                                            | write of Timer1 in two                                            | 8-bit operations     |                    |  |  |  |  |  |

| bit 6   | Unimplemented: Read as                                                                 | · ' O '                                                           |                      |                    |  |  |  |  |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits                               |                                                                   |                      |                    |  |  |  |  |  |

|         | 11 = 1:8 Prescale value                                                                |                                                                   |                      |                    |  |  |  |  |  |

|         | 10 = 1:4 Prescale value                                                                |                                                                   |                      |                    |  |  |  |  |  |

|         | 01 = 1:2 Prescale value                                                                |                                                                   |                      |                    |  |  |  |  |  |

|         | 00 = 1:1 Prescale value                                                                |                                                                   |                      |                    |  |  |  |  |  |

| bit 3   | T10SCEN: Timer1 Oscilla                                                                | tor Enable bit                                                    |                      |                    |  |  |  |  |  |

|         | 1 = Timer1 oscillator is ena                                                           | abled                                                             |                      |                    |  |  |  |  |  |

|         | 0 = Timer1 oscillator is shut off                                                      |                                                                   |                      |                    |  |  |  |  |  |

|         | The oscillator inverter and feedback resistor are turned off to eliminate power drain. |                                                                   |                      |                    |  |  |  |  |  |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Select bit                         |                                                                   |                      |                    |  |  |  |  |  |

|         | When TMR1CS = 1:                                                                       |                                                                   |                      |                    |  |  |  |  |  |

|         | 1 = Do not synchronize external clock input                                            |                                                                   |                      |                    |  |  |  |  |  |

|         | 0 = Synchronize external clock input                                                   |                                                                   |                      |                    |  |  |  |  |  |

|         | When TMR1CS = 0:                                                                       |                                                                   |                      |                    |  |  |  |  |  |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.                   |                                                                   |                      |                    |  |  |  |  |  |

| bit 1   | TMR1CS: Timer1 Clock So                                                                | ource Select bit                                                  |                      |                    |  |  |  |  |  |

|         | 1 = External clock from pin                                                            | 1 = External clock from pin RC0/T1OSO/T13CKI (on the rising edge) |                      |                    |  |  |  |  |  |

|         | 0 = Internal clock (Fosc/4)                                                            |                                                                   |                      |                    |  |  |  |  |  |

| bit 0   | TMR1ON: Timer1 On bit                                                                  |                                                                   |                      |                    |  |  |  |  |  |

|         | 1 = Enables Timer1                                                                     |                                                                   |                      |                    |  |  |  |  |  |

|         | 0 = Stops Timer1                                                                       |                                                                   |                      |                    |  |  |  |  |  |

|         |                                                                                        |                                                                   |                      |                    |  |  |  |  |  |

|         | Legend:                                                                                |                                                                   |                      |                    |  |  |  |  |  |

|         | R = Readable bit                                                                       | W = Writable bit                                                  | U = Unimplemented    | l bit, read as '0' |  |  |  |  |  |

|         | - n = Value at POR                                                                     | '1' = Bit is set                                                  | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |  |

#### 12.3 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 Interrupt Enable bit, TMR1IE (PIE1<0>).

#### 12.4 Resetting Timer1 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The special event triggers from the CCP1 |      |      |     |           |      |     |  |  |  |

|-------|------------------------------------------|------|------|-----|-----------|------|-----|--|--|--|

|       | module                                   | will | not  | set | interrupt | flag | bit |  |  |  |

|       | TMR1IF                                   | (PIR | 1<0> | ·). |           |      |     |  |  |  |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

#### 12.5 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 12-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 high byte buffer. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, is valid, due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

#### 12.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 12.2 "Timer1 Oscillator**") gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

#### 13.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

### 13.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the synchronous serial port module, which optionally uses it to generate the shift clock.

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6         | Bit 5    | Bit 4    | Bit 3                                     | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|--------|------------------------|---------------|----------|----------|-------------------------------------------|--------|--------|--------|---------------|------|------|-----------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL     | TMR0IE   | INTOIE   | RBIE                                      | TMR0IF | INT0IF | RBIF   | 0000          | 0000 | 0000 | 0000                  |

| PIR1   | PSPIF                  | ADIF          | RCIF     | TXIF     | SSPIF                                     | CCP1IF | TMR2IF | TMR1IF | 0000          | 0000 | 0000 | 0000                  |

| PIE1   | PSPIE                  | ADIE          | RCIE     | TXIE     | SSPIE                                     | CCP1IE | TMR2IE | TMR1IE | 0000          | 0000 | 0000 | 0000                  |

| IPR1   | PSPIP                  | ADIP          | RCIP     | TXIP     | SSPIP                                     | CCP1IP | TMR2IP | TMR1IP | 0111          | 1111 | 0111 | 1111                  |

| TMR2   | Timer2 Moo             | dule Register |          |          |                                           |        |        |        | 0000          | 0000 | 0000 | 0000                  |

| T2CON  | —                      | T2OUTPS3      | T2OUTPS2 | T2OUTPS1 | 20UTPS1 T2OUTPS0 TMR2ON T2CKPS1 T2CKPS0 - |        | -000   | 0000   | -000          | 0000 |      |                       |

| PR2    | Timer2 Period Register |               |          |          |                                           |        |        |        |               | 1111 | 1111 | 1111                  |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

NOTES:

### 15.0 TIMER4 MODULE

The Timer4 module timer has the following features:

- 8-bit timer (TMR4 register)

- 8-bit period register (PR4)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR4 match of PR4

Timer4 has a control register shown in Register 15-1. Timer4 can be shut-off by clearing control bit, TMR4ON (T4CON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4 are also controlled by this register. Figure 15-1 is a simplified block diagram of the Timer4 module.

#### 15.1 **Timer4 Operation**

Timer4 can be used as the PWM time base for the PWM mode of the CCP module. The TMR4 register is readable and writable and is cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T4CKPS1:T4CKPS0 (T4CON<1:0>). The match output of TMR4 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR4 interrupt, latched in flag bit, TMR4IF (PIR3<3>).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR4 register

- a write to the T4CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR4 is not cleared when T4CON is written.

#### **REGISTER 15-1: T4CON: TIMER4 CONTROL REGISTER**

| 13-1.   | 14001                                                  |               |              |               |             |        |         |         |  |

|---------|--------------------------------------------------------|---------------|--------------|---------------|-------------|--------|---------|---------|--|

|         | U-0                                                    | R/W-0         | R/W-0        | R/W-0         | R/W-0       | R/W-0  | R/W-0   | R/W-0   |  |

|         | _                                                      | T4OUTPS3      | T4OUTPS2     | T4OUTPS1      | T4OUTPS0    | TMR4ON | T4CKPS1 | T4CKPS0 |  |

|         | bit 7                                                  |               |              |               |             |        |         | bit 0   |  |

| bit 7   | Unimple                                                | emented: Re   | ead as '0'   |               |             |        |         |         |  |

| bit 6-3 | T4OUTPS3:T4OUTPS0: Timer4 Output Postscale Select bits |               |              |               |             |        |         |         |  |

|         | 0000 =                                                 | 1:1 Postscale | Э            |               |             |        |         |         |  |

|         | 0001 =                                                 | 1:2 Postscale | e            |               |             |        |         |         |  |

|         | •                                                      |               |              |               |             |        |         |         |  |

|         | •                                                      |               |              |               |             |        |         |         |  |

|         | 1111 =                                                 | 1:16 Postsca  | le           |               |             |        |         |         |  |

| bit 2   | TMR40                                                  | N: Timer4 Or  | n bit        |               |             |        |         |         |  |

|         | 1 = Time                                               | er4 is on     |              |               |             |        |         |         |  |

|         | 0 = Time                                               | er4 is off    |              |               |             |        |         |         |  |

| bit 1-0 | T4CKPS                                                 | S1:T4CKPS0    | : Timer4 Clo | ck Prescale S | Select bits |        |         |         |  |

|         | 00 = Pre                                               | escaler is 1  |              |               |             |        |         |         |  |

|         | 01 = Pre                                               | escaler is 4  |              |               |             |        |         |         |  |

|         | 1x = Pre                                               | escaler is 16 |              |               |             |        |         |         |  |

|         |                                                        |               |              |               |             |        |         |         |  |

|         | Legend                                                 | :             |              |               |             |        |         |         |  |

| Legena.            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 17.3.1 REGISTERS

The MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

#### REGISTER 17-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

|                | R/W-0                                           | R/W-0                                        | R-0                          | R-0          | R-0                         | R-0          | R-0                             | R-0   |

|----------------|-------------------------------------------------|----------------------------------------------|------------------------------|--------------|-----------------------------|--------------|---------------------------------|-------|

|                | SMP                                             | CKE                                          | D/A                          | Р            | S                           | R/W          | UA                              | BF    |

|                | bit 7                                           |                                              |                              |              |                             |              |                                 | bit 0 |

| bit 7<br>bit 6 | 0 = Input da<br><u>SPI Slave r</u><br>SMP must  | <u>mode:</u><br>ata sampled<br>ata sampled   | at middle o<br>/hen SPI is   | f data outpu | t time                      |              |                                 |       |

|                |                                                 | nit occurs on<br>nit occurs on               |                              |              |                             |              |                                 |       |

|                | Note:                                           |                                              |                              |              |                             | PCON1<4>)    | ).                              |       |

| bit 5          | <b>D/A:</b> Data//<br>Used in I <sup>2</sup> C  | Address bit<br>mode only.                    |                              |              |                             |              |                                 |       |

| bit 4          | P: Stop bit                                     | mode only.                                   | This bit is c                | leared wher  | the MSSP                    | module is di | isabled,                        |       |

| bit 3          | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C | c mode only.                                 |                              |              |                             |              |                                 |       |

| bit 2          | R/W: Read                                       | /Write bit info<br>mode only.                | ormation                     |              |                             |              |                                 |       |

| bit 1          | UA: Update                                      | e Address bi<br>mode only.                   | t                            |              |                             |              |                                 |       |

| bit 0          | <b>BF:</b> Buffer<br>1 = Receive                | Full Status b<br>e complete,<br>e not comple | SSPBUF is                    | full         |                             |              |                                 |       |

|                | <b>Legend:</b><br>R = Readal<br>- n = Value     |                                              | W = Writab<br>'1' = Bit is s |              | U = Unimp<br>'0' = Bit is o | lemented bi  | t, read as '0'<br>x = Bit is un | known |

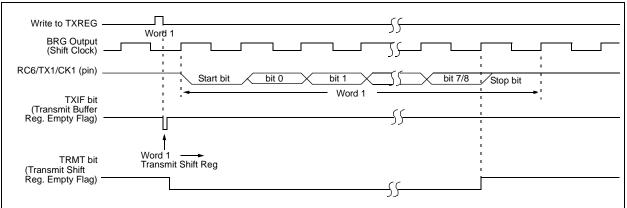

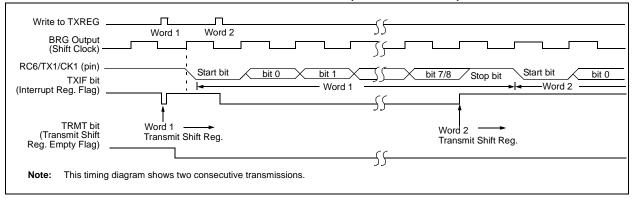

#### FIGURE 18-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 18-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name                  | Bit 7                                              | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|----------------------------------------------------|---------------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON                | GIE/GIEH                                           | PEIE/GIEL     | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF      | 0000 0000            | 0000 0000                       |

| PIR1                  | PSPIF                                              | ADIF          | RC1IF  | TX1IF  | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1                  | PSPIE                                              | ADIE          | RC1IE  | TX1IE  | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1                  | PSPIP                                              | ADIP          | RC1IP  | TX1IP  | SSPIP  | CCP1IP | TMR2IP | TMR1IP    | 0111 1111            | 0111 1111                       |

| PIR3                  | _                                                  | —             | RC2IF  | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF    | 00 0000              | 00 0000                         |

| PIE3                  | _                                                  | _             | RC2IE  | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE    | 00 0000              | 00 0000                         |

| IPR3                  | _                                                  | —             | RC2IP  | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP    | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup> | SPEN                                               | RX9           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

| TXREGx <sup>(1)</sup> | USART Tran                                         | smit Register |        |        |        |        |        |           | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup> | CSRC                                               | TX9           | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> | SPBRGx <sup>(1)</sup> Baud Rate Generator Register |               |        |        |        |        |        | 0000 0000 | 0000 0000            |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

| Syntax:[ label ] CLRF f [,a]Syntax:[ label ] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Operands: $0 \le f \le 255$ Operands:None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| $a \in [0,1]$ Operation: $000h \rightarrow WDT$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| Operation: $000h \rightarrow f$ $000h \rightarrow WDT$ postso $1 \rightarrow Z$ $1 \rightarrow TO$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | aler,          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Status Affected: Z<br>Encoding: $\Box_{110}$ $\Box_{1010}$ $\varepsilon_{555}$ $\varepsilon_{555}$ Status Affected: TO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000 0100       |

| Description:         Clears the contents of the specified<br>register. If 'a' is '0', the Access         Encoding.         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000 </td <td></td> |                |

| Bank will be selected, overriding Watchdog Timer. It a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| the BSR value. If 'a' = 1, then the postscaler of the WE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T. Status bits |

| bank will be selected as per the TO and PD are set.<br>BSR value (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Worde: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| Cycles: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>.</b>       |

| Q Cycle Activity:         Q1         Q2         Q3           Q1         Q2         Q3         Q4         Decode         No         Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q4<br>No       |

| Decode Read Process Write Decode No Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | operation      |

| register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Example: CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Example: CLRF FLAG_REG, 1 Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| Before Instruction     WDT Counter     = ?       FLAG REG     = 0x5A     After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| FLAG_REG = 0x5A After Instruction<br>After Instruction WDT Counter = 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| $FLAG_REG = 0x00$ WDT Postscaler = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| $\frac{\text{TO}}{\text{PD}} = 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| Oper<br>Statu | ax:<br>rands:<br>ration:<br>us Affected: | [ <i>label</i> ] R<br>-1024 ≤ n<br>(PC) + 2 -<br>(PC) + 2 +                                    | ≤ 1023<br>→ TOS,                                                                        | n                                                            |                                                                      |

|---------------|------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------|

| Oper<br>Statu | ration:                                  | (PC) + 2 -                                                                                     | → TOS,                                                                                  |                                                              |                                                                      |

| Statu         |                                          |                                                                                                |                                                                                         |                                                              |                                                                      |

| 0.0.0         | is Affected:                             |                                                                                                | $\cdot 2n \rightarrow F$                                                                | ъС                                                           |                                                                      |

| Enco          |                                          | None                                                                                           |                                                                                         |                                                              |                                                                      |

|               | oding:                                   | 1101                                                                                           | 1nnn                                                                                    | nnnı                                                         | n nnnn                                                               |

| Description:  |                                          | return add<br>onto the s<br>compleme<br>Since the<br>to fetch the<br>new addree<br>instruction | Iress (Pe<br>tack. Th<br>ent numb<br>PC will h<br>e next ir<br>ess will b<br>i is a two | C+2) is<br>en, ac<br>per '2n<br>nave in<br>nstruct<br>pe PC+ | d the 2's<br>i' to the PC.<br>ncremented<br>tion, the<br>+2+2n. This |