Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6620t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

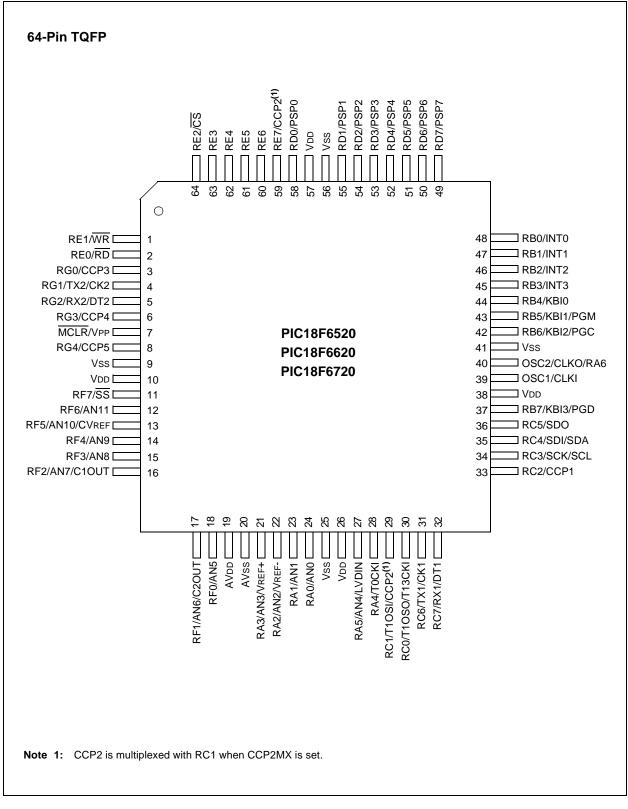

#### **Pin Diagrams**

| Pin Name            | Pin N            | umber      | Pin      | Buffer      | Description                                                                                                                 |  |

|---------------------|------------------|------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name            | PIC18F6X20       | PIC18F8X20 | Туре     | Туре        | Description                                                                                                                 |  |

|                     |                  |            |          |             | PORTC is a bidirectional I/O port.                                                                                          |  |

| RC0/T1OSO/T13CKI    | 30               | 36         |          |             |                                                                                                                             |  |

| RC0                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| T1OSO               |                  |            | 0        | —           | Timer1 oscillator output.                                                                                                   |  |

| T13CKI              |                  |            | I        | ST          | Timer1/Timer3 external clock input.                                                                                         |  |

| RC1/T1OSI/CCP2      | 29               | 35         |          |             |                                                                                                                             |  |

| RC1                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| T1OSI               |                  |            | I        | CMOS        | Timer1 oscillator input.                                                                                                    |  |

| CCP2 <sup>(2)</sup> |                  |            | I/O      | ST          | Capture2 input/Compare2 output/                                                                                             |  |

|                     |                  |            |          |             | PWM2 output.                                                                                                                |  |

| RC2/CCP1            | 33               | 43         |          |             |                                                                                                                             |  |

| RC2                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| CCP1                |                  |            | I/O      | ST          | Capture1 input/Compare1 output/                                                                                             |  |

|                     |                  |            |          |             | PWM1 output.                                                                                                                |  |

| RC3/SCK/SCL         | 34               | 44         |          |             |                                                                                                                             |  |

| RC3                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SCK                 |                  |            | I/O      | ST          | Synchronous serial clock input/outpu                                                                                        |  |

|                     |                  |            |          |             | for SPI mode.                                                                                                               |  |

| SCL                 |                  |            | I/O      | ST          | Synchronous serial clock input/output for I <sup>2</sup> C mode.                                                            |  |

| RC4/SDI/SDA         | 35               | 45         |          |             |                                                                                                                             |  |

| RC4                 |                  | 45         | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SDI                 |                  |            | "/C      | ST          | SPI data in.                                                                                                                |  |

| SDA                 |                  |            | I/O      | ST          | $I^2C$ data I/O.                                                                                                            |  |

| RC5/SDO             | 36               | 46         | ., C     | •           |                                                                                                                             |  |

| RC5/SDO<br>RC5      | 30               | 40         | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SDO                 |                  |            | 0        |             | SPI data out.                                                                                                               |  |

|                     |                  | 07         | Ŭ        |             |                                                                                                                             |  |

| RC6/TX1/CK1         | 31               | 37         | 1/0      | ст          |                                                                                                                             |  |

| RC6<br>TX1          |                  |            | 1/O<br>O | ST          | Digital I/O.<br>USART 1 asynchronous transmit.                                                                              |  |

| CK1                 |                  |            | 1/0      | ST          | USART 1 synchronous clock                                                                                                   |  |

| ONT                 |                  |            | 1/0      | 51          | (see RX1/DT1).                                                                                                              |  |

|                     | 22               | 20         |          |             |                                                                                                                             |  |

| RC7/RX1/DT1         | 32               | 38         | I/O      | ST          | Digital I/O                                                                                                                 |  |

| RC7<br>RX1          |                  |            |          | ST          | Digital I/O.<br>USART 1 asynchronous receive.                                                                               |  |

| DT1                 |                  |            | I/O      | ST          | USART 1 synchronous data                                                                                                    |  |

|                     |                  |            | ",0      |             | (see TX1/CK1).                                                                                                              |  |

| Legend: TTL = TTL   | compatible inp   | L          |          | CMOS -      | = CMOS compatible input or output                                                                                           |  |

|                     | mitt Trigger inp |            | evels    |             | = Analog input                                                                                                              |  |

|                     |                  |            |          | •           |                                                                                                                             |  |

|                     |                  |            |          |             |                                                                                                                             |  |

| I = Inpu<br>P = Pow | it<br>ver        |            |          | O =<br>OD = | <ul> <li>Analog input</li> <li>Output</li> <li>Open-Drain (no P diode to VE</li> <li>(all operating modes except</li> </ul> |  |

### TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 when CCP2MX is not selected (all operating modes except Microcontroller).

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

**6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

### 2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock source switching is performed under software control. The system clock switch bit, SCS (OSCCON<0>), controls the clock switching. When the SCS bit is '0', the system clock source comes from the main oscillator that is selected by the FOSC configuration bits in Configuration Register 1H. When the SCS bit is set, the system clock source will come from the Timer1 oscillator. The SCS bit is cleared on all forms of Reset. Note: The Timer1 oscillator must be enabled and operating to switch the system clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON). If the Timer1 oscillator is not enabled, then any write to the SCS bit will be ignored (SCS bit forced cleared) and the main oscillator will continue to be the system clock source.

### REGISTER 2-1: OSCCON REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | _   | _   | —   | SCS   |

| bit 7 |     |     |     |     |     |     | bit 0 |

bit 7-1 Unimplemented: Read as '0'

bit 0 SCS: System Clock Switch bit

When OSCSEN Configuration bit = 0 and T1OSCEN bit is set:

1 = Switch to Timer1 oscillator/clock pin

0 = Use primary oscillator/clock input pin

When OSCSEN and T1OSCEN are in other states:

Bit is forced clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

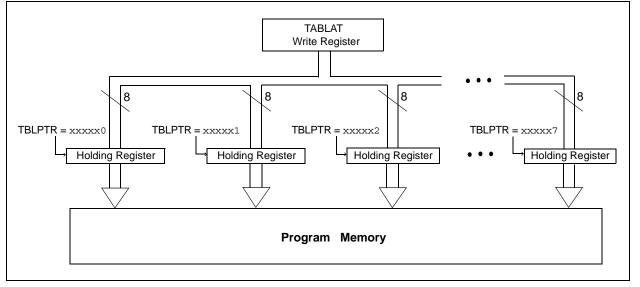

### 5.5 Writing to Flash Program Memory

The minimum programming block is 4 words or 8 bytes. Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 8 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction has to be executed 8 times for each programming operation. All of the table write operations will essentially be short writes, because only the holding registers are written. At the end of updating 8 registers, the EECON1 register must be written to, to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

### FIGURE 5-5: TABLE WRITES TO FLASH PROGRAM MEMORY

#### 5.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer with address being erased.

- 4. Do the row erase procedure.

- 5. Load Table Pointer with address of first byte being written.

- 6. Write the first 8 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- set EEPGD bit to point to program memory

clear the CFGS bit to access program memory

- set WREN to enable byte writes

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Execute a NOP.

- 14. Re-enable interrupts.

- 15. Repeat steps 6-14 seven times, to write 64 bytes.

- 16. Verify the memory (table read).

This procedure will require about 18 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 5-3.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the eight bytes in the holding register.

### 9.3 **PIE Registers**

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2 and PIE3). When the IPEN bit (RCON<7>) is '0', the PEIE bit must be set to enable any of these peripheral interrupts.

| <b>REGISTER 9-7:</b> | PIE1: PER            | IPHERAL                  | INTERRU                        | PT ENABL       | E REGIST      | ER 1   |        |        |  |  |  |  |  |

|----------------------|----------------------|--------------------------|--------------------------------|----------------|---------------|--------|--------|--------|--|--|--|--|--|

|                      | R/W-0                | R/W-0                    | R/W-0                          | R/W-0          | R/W-0         | R/W-0  | R/W-0  | R/W-0  |  |  |  |  |  |

|                      | PSPIE <sup>(1)</sup> | ADIE                     | RC1IE                          | TX1IE          | SSPIE         | CCP1IE | TMR2IE | TMR1IE |  |  |  |  |  |

|                      | bit 7                | bit 7                    |                                |                |               |        |        |        |  |  |  |  |  |

|                      |                      |                          |                                |                |               | (4)    |        |        |  |  |  |  |  |

| bit 7                |                      |                          |                                | Vrite Interrup | ot Enable bit | (1)    |        |        |  |  |  |  |  |

|                      |                      |                          | ead/write int<br>ead/write int |                |               |        |        |        |  |  |  |  |  |

| bit 6                | ADIE: A/D            | Converter I              | nterrupt Ena                   | ble bit        |               |        |        |        |  |  |  |  |  |

|                      |                      | s the A/D in             | -                              |                |               |        |        |        |  |  |  |  |  |

|                      |                      | s the A/D in             |                                |                |               |        |        |        |  |  |  |  |  |

| bit 5                |                      |                          | ive Interrupt                  |                |               |        |        |        |  |  |  |  |  |

|                      |                      |                          | T1 receive in<br>T1 receive i  | •              |               |        |        |        |  |  |  |  |  |

| bit 4                | TX1IE: US            | ART1 Trans               | mit Interrupt                  | t Enable bit   |               |        |        |        |  |  |  |  |  |

|                      |                      |                          | T1 transmit                    | •              |               |        |        |        |  |  |  |  |  |

|                      | 0 = Disable          | s the USAR               | T1 transmit                    | interrupt      |               |        |        |        |  |  |  |  |  |

| bit 3                |                      | •                        |                                | I Port Interru | ipt Enable b  | it     |        |        |  |  |  |  |  |

|                      |                      | s the MSSP<br>s the MSSF | •                              |                |               |        |        |        |  |  |  |  |  |

| bit 2                |                      |                          | pt Enable bi                   | t              |               |        |        |        |  |  |  |  |  |

| 5112                 |                      | s the CCP1               |                                | ·              |               |        |        |        |  |  |  |  |  |

|                      |                      | s the CCP1               |                                |                |               |        |        |        |  |  |  |  |  |

| bit 1                | TMR2IE: T            | MR2 to PR2               | 2 Match Inte                   | rrupt Enable   | bit           |        |        |        |  |  |  |  |  |

|                      |                      |                          | to PR2 mat                     | •              |               |        |        |        |  |  |  |  |  |

|                      | 0 = Disable          | s the TMR2               | to PR2 mat                     | tch interrupt  |               |        |        |        |  |  |  |  |  |

| bit 0                |                      |                          | ow Interrupt                   |                |               |        |        |        |  |  |  |  |  |

|                      |                      |                          | overflow int                   | •              |               |        |        |        |  |  |  |  |  |

|                      | 0 = Disable          | s the IMR1               | overflow in                    | terrupt        |               |        |        |        |  |  |  |  |  |

|                      |                      |                          |                                |                |               |        |        |        |  |  |  |  |  |

Note 1: Enabled only in Microcontroller mode for PIC18F8X20 devices.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

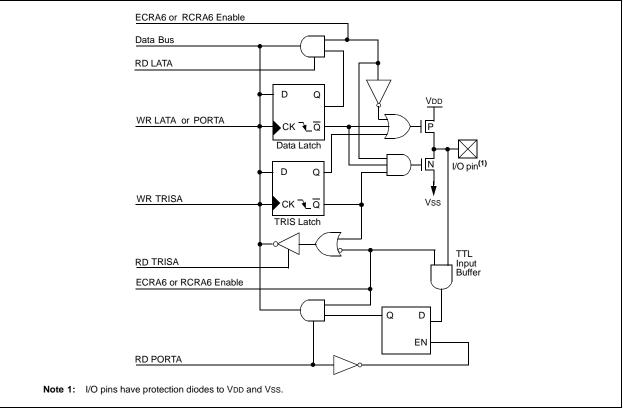

## FIGURE 10-4: BLOCK DIAGRAM OF RA6 PIN (WHEN ENABLED AS I/O)

| Name         | Bit#  | Buffer Type           | Function                                                                    |

|--------------|-------|-----------------------|-----------------------------------------------------------------------------|

| RD0/PSP0/AD0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 0 or address/data bus bit 0. |

| RD1/PSP1/AD1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 1 or address/data bus bit 1. |

| RD2/PSP2/AD2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 2 or address/data bus bit 2. |

| RD3/PSP3/AD3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 3 or address/data bus bit 3. |

| RD4/PSP4/AD4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 4 or address/data bus bit 4. |

| RD5/PSP5/AD5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 5 or address/data bus bit 5. |

| RD6/PSP6/AD6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 6 or address/data bus bit 6. |

| RD7/PSP7/AD7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 7 or address/data bus bit 7. |

#### TABLE 10-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

WAIT1

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in System Bus or Parallel Slave Port mode.

| Name   | Bit 7   | Bit 6    | Bit 5      | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|----------|------------|---------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTD  | RD7     | RD6      | RD5        | RD4     | RD3   | RD2   | RD1   | RD0   | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Da | ata Outp | ut Registe | er      |       |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD   | Data Dir | ection Re  | gister  |       |       |       |       | 1111 1111            | 1111 1111                       |

| PSPCON | IBF     | OBF      | IBOV       | PSPMODE | _     | _     | _     | _     | 0000                 | 0000                            |

TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

WAIT0

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

WM1

WM0

0-00 --00

0-00 --00

MEMCON EBDIS

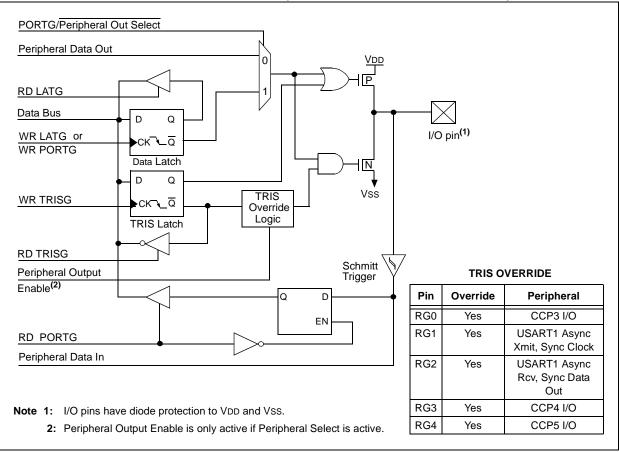

### 10.7 PORTG, TRISG and LATG Registers

PORTG is a 5-bit wide, bidirectional port. The corresponding data direction register is TRISG. Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISG bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATG) is also memory mapped. Read-modify-write operations on the LATG register, read and write the latched output value for PORTG.

PORTG is multiplexed with both CCP and USART functions (Table 10-13). PORTG pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTG pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

| Note: | On a Power-on Reset, these pins are |

|-------|-------------------------------------|

|       | configured as digital inputs.       |

The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

#### EXAMPLE 10-7: INITIALIZING PORTG

| CLRF  | PORTG | ; Initialize PORTG by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATG  | ; Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0x04  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISG | ; Set RG1:RG0 as outputs                   |

|       |       | ; RG2 as input                             |

|       |       | ; RG4:RG3 as inputs                        |

|       |       |                                            |

### FIGURE 10-16: PORTG BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

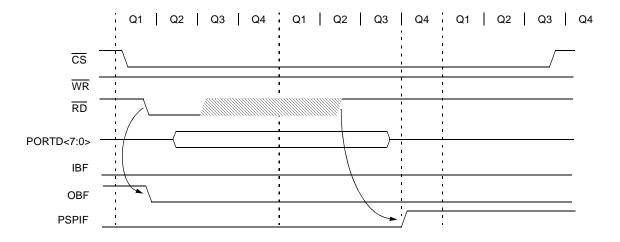

## FIGURE 10-25: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 10-19: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7                | Bit 6         | Bit 5        | Bit 4          | Bit 3 | Bit 2                  | Bit 1                   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------|--------------|----------------|-------|------------------------|-------------------------|-----------|----------------------|---------------------------------|

| PORTD  | Port Data            | Latch whe     | n written; F | Port pins when | read  |                        |                         |           | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data            | a Output b    | its          |                |       |                        |                         |           | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD D              | ata Directi   | on bits      |                |       |                        |                         |           | 1111 1111            | 1111 1111                       |

| PORTE  | -                    | —             | -            | —              | —     | Read POR<br>Write POR  | RTE pin/<br>RTE Data La | itch      | 0000 0000            | 0000 0000                       |

| LATE   | —                    | —             | _            | _              | —     | LATE Data              | a Output bits           | 3         | xxxx xxxx            | uuuu uuuu                       |

| TRISE  | _                    | _             | _            | _              | —     | PORTE Da               | ata Directio            | n bits    | 1111 1111            | 1111 1111                       |

| PSPCON | IBF                  | OBF           | IBOV         | PSPMODE        | —     | —                      | —                       | —         | 0000                 | 0000                            |

| INTCON | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IF       | INTOIE         | RBIE  | TMR0IF                 | INTOIF                  | RBIF      | 0000 0000            | 0000 0000                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF         | TXIF           | SSPIF | CCP1IF                 | CCP1IF TMR2IF TMR1IF    |           | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE           | SSPIE | E CCP1IE TMR2IE TMR1IE |                         | 0000 0000 | 0000 0000            |                                 |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP           | SSPIP | CCP1IP                 | TMR2IP                  | TMR1IP    | 0111 1111            | 0111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Enabled only in Microcontroller mode for PIC18F8X20 devices.

NOTES:

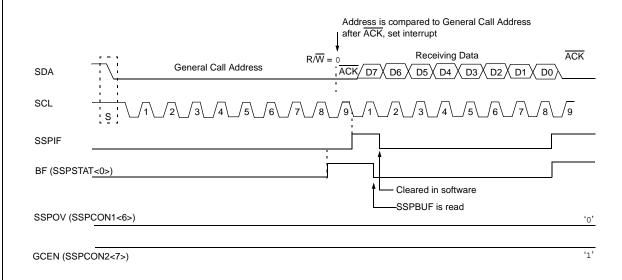

#### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-15).

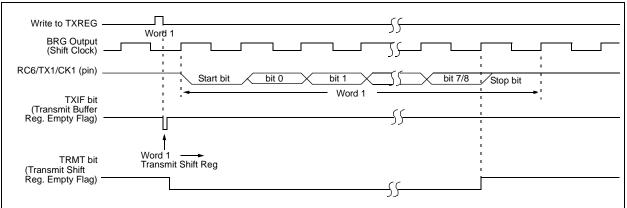

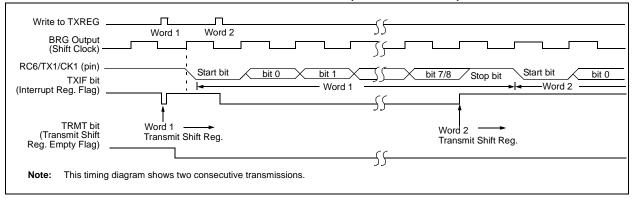

#### FIGURE 18-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 18-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name                  | Bit 7       | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-------------|---------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                | GIE/GIEH    | PEIE/GIEL     | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                  | PSPIF       | ADIF          | RC1IF  | TX1IF  | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                  | PSPIE       | ADIE          | RC1IE  | TX1IE  | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                  | PSPIP       | ADIP          | RC1IP  | TX1IP  | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR3                  | _           | —             | RC2IF  | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 00 0000              | 00 0000                         |

| PIE3                  | _           | _             | RC2IE  | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 00 0000              | 00 0000                         |

| IPR3                  | _           | —             | RC2IP  | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup> | SPEN        | RX9           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TXREGx <sup>(1)</sup> | USART Tran  | smit Register |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup> | CSRC        | TX9           | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> | Baud Rate G | Senerator Reg | gister |        |        |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

NOTES:

#### 23.4.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 23.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write-protected. The WRTC bit controls protection of the configuration registers. In user mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 23.5 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

### 23.6 In-Circuit Serial Programming

PIC18FX520/X620/X720 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

| Note: | When     | performing           | In-Circuit            | Serial  |

|-------|----------|----------------------|-----------------------|---------|

|       | Progran  | nming, verify        | that power            | is con- |

|       | nected   | to <b>all</b> VDD ar | nd AVDD pins          | of the  |

|       | microco  | ntroller and th      | nat <b>all</b> Vss an | d AVss  |

|       | pins are | grounded.            |                       |         |

## 23.7 In-Circuit Debugger

When the DEBUG bit in the CONFIG4L Configuration register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 23-4 shows which features are consumed by the background debugger.

### TABLE 23-4: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7       |

|----------------|----------------|

| Stack          | 2 levels       |

| Program Memory | Last 576 bytes |

| Data Memory    | Last 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## 23.8 Low-Voltage ICSP Programming

The LVP bit in the CONFIG4L Configuration register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM pin, provided the LVP bit is set. The LVP bit defaults to a '1' from the factory.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin and should be held low during normal operation.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 5 in the TRISB register must be cleared to disable the pull-up on RB5 and ensure the proper operation of the device.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only High-Voltage Programming mode can be used to program the device.

When using Low-Voltage ICSP Programming, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the codeprotect bits from an on state to an off state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs or user code can be reprogrammed or added.

| BNOV                                                                                  | Branch if Not Overflow                                                          |                                            | w                                                                                 | BNZ          |                                                                           | Branch if                                                                      | Branch if Not Zero                        |                                                                                  |  |  |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------|--|--|

| Syntax:                                                                               | [label] B                                                                       | NOV n                                      |                                                                                   | Synt         | ax:                                                                       | [ <i>label</i> ] B                                                             | NZ n                                      |                                                                                  |  |  |

| Operands:                                                                             | -128 ≤ n ≤                                                                      | 127                                        |                                                                                   | Ope          | rands:                                                                    | -128 ≤ n ≤                                                                     | $\textbf{-128} \leq n \leq 127$           |                                                                                  |  |  |

| Operation:                                                                            | if Overflow bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC                        |                                            | Ope                                                                               | Operation:   |                                                                           | is '0'<br>· 2n → PC                                                            |                                           |                                                                                  |  |  |

| Status Affected:                                                                      | None                                                                            |                                            | Statu                                                                             | us Affected: | None                                                                      |                                                                                |                                           |                                                                                  |  |  |

| Encoding:                                                                             | 1110                                                                            | 0101 nn:                                   | nn nnnn                                                                           | Enco         | oding:                                                                    | 1110                                                                           | 0001 nn                                   | nn nnnn                                                                          |  |  |

| Description:                                                                          | program w<br>The 2's co<br>added to tl<br>have incre<br>instruction<br>PC+2+2n. | mplement no<br>he PC. Sinc<br>mented to fe | umber '2n' is<br>e the PC will<br>etch the next<br>dress will be<br>ction is then | Desc         | cription:                                                                 | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | mplement n<br>he PC. Sinc<br>mented to fe | umber '2n' is<br>the PC will<br>etch the next<br>ldress will be<br>ction is then |  |  |

| Words:                                                                                | 1                                                                               |                                            |                                                                                   | Word         | ds:                                                                       | 1                                                                              |                                           |                                                                                  |  |  |

| Cycles:                                                                               | 1(2)                                                                            |                                            |                                                                                   | Cycl         | es:                                                                       | 1(2)                                                                           |                                           |                                                                                  |  |  |

| Q Cycle Activity:<br>If Jump:                                                         |                                                                                 |                                            |                                                                                   |              | ycle Activity                                                             | :                                                                              |                                           |                                                                                  |  |  |

| Q1                                                                                    | Q2                                                                              | Q3                                         | Q4                                                                                |              | Q1                                                                        | Q2                                                                             | Q3                                        | Q4                                                                               |  |  |

| Decode                                                                                | Read literal<br>'n'                                                             | Process<br>Data                            | Write to PC                                                                       |              | Decode                                                                    | Read literal<br>'n'                                                            | Process<br>Data                           | Write to PC                                                                      |  |  |

| No<br>operation                                                                       | No<br>operation                                                                 | No<br>operation                            | No<br>operation                                                                   |              | No<br>operation                                                           | No<br>operation                                                                | No<br>operation                           | No<br>operation                                                                  |  |  |

| If No Jump:                                                                           |                                                                                 |                                            |                                                                                   | If N         | o Jump:                                                                   |                                                                                |                                           |                                                                                  |  |  |

| Q1                                                                                    | Q2                                                                              | Q3                                         | Q4                                                                                |              | Q1                                                                        | Q2                                                                             | Q3                                        | Q4                                                                               |  |  |

| Decode                                                                                | Read literal<br>'n'                                                             | Process<br>Data                            | No<br>operation                                                                   |              | Decode                                                                    | Read literal<br>'n'                                                            | Process<br>Data                           | No<br>operation                                                                  |  |  |

| Example:<br>Before Instru<br>PC<br>After Instruct<br>If Overflov<br>PC<br>If Overflov | = add<br>ion<br>w = 0;<br>= add                                                 | BNOV Jump<br>dress (HERE<br>dress (Jump    | )                                                                                 |              | nple:<br>Before Instru<br>PC<br>After Instruc<br>If Zero<br>PC<br>If Zero | = ado<br>tion<br>= 0;                                                          | BNZ Jump<br>dress (HERE)<br>dress (Jump)  |                                                                                  |  |  |

MOVLB

| MOVFF                                                | Move f to                                                                                                                                                                                                       | o f                                                                                                                                                                      |                                                                                                                                                                                             |                                                                                                                   |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                              | [ label ]                                                                                                                                                                                                       | MOVFF                                                                                                                                                                    | f <sub>s</sub> ,f <sub>d</sub>                                                                                                                                                              |                                                                                                                   |  |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 4095 \\ 0 \leq f_d \leq 4095 \end{array}$                                                                                                                                     |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Operation:                                           | $(f_s) \to f_d$                                                                                                                                                                                                 |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                            |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                    | ffff<br>ffff                                                                                                                                                             | ffff<br>ffff                                                                                                                                                                                | ffff <sub>s</sub><br>ffff <sub>d</sub>                                                                            |  |  |

|                                                      | are move<br>'f <sub>d</sub> '. Locat<br>anywhere<br>space (00<br>of destina<br>anywhere<br>Either sou<br>W (a use<br>MOVFF is<br>transferrin<br>to a perip<br>transmit b<br>The MOVE<br>the PCL,<br>the destina | tion of sc<br>in the 4<br>20h to FF<br>ation 'f <sub>d</sub> ' (<br>in form 00<br>urce or d<br>ful specia<br>particula<br>heral reg<br>puffer or<br>FF instru<br>TOSU, T | ource 'f <sub>s</sub> ' of<br>096-byte<br>Fh) and<br>can also<br>00h to FF<br>lestination<br>al situation<br>arity usefut<br>a memory<br>gister (suc<br>an I/O po<br>ction can<br>'OSH or ' | can be<br>data<br>location<br>be<br>Fh.<br>n can be<br>on).<br>I for<br>location<br>ch as the<br>ort).<br>not use |  |  |

| Words:                                               | 2                                                                                                                                                                                                               |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Cycles:                                              | 2 (3)                                                                                                                                                                                                           |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                 |                                                                                                                                                                          |                                                                                                                                                                                             |                                                                                                                   |  |  |

| Q1                                                   | Q2                                                                                                                                                                                                              | Q3                                                                                                                                                                       | 3                                                                                                                                                                                           | Q4                                                                                                                |  |  |

| Q1     | Q1 Q2 Q3                             |                 | Q4                              |

|--------|--------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)        | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation,<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

REG1, REG2

#### Example: MOVFF

| Before Instruction |   |       |  |  |

|--------------------|---|-------|--|--|

| REG1               | = | 0x33  |  |  |

| REG2               | = | 0x11  |  |  |

| After Instruction  |   |       |  |  |

| REG1               | = | 0x33, |  |  |

| REG2               | = | 0x33  |  |  |

| Synt                                   | ax:            | [ label ]           | MOVLB             | k   |      |                            |  |

|----------------------------------------|----------------|---------------------|-------------------|-----|------|----------------------------|--|

| Operands:                              |                | $0 \le k \le 25$    | $0 \le k \le 255$ |     |      |                            |  |

| Ope                                    | ration:        | $k \rightarrow BSR$ |                   |     |      |                            |  |

| Statu                                  | us Affected:   | None                |                   |     |      |                            |  |

| Enco                                   | oding:         | 0000                | 0001              | kk} | ck   | kkkk                       |  |

| Description: The 8-bit I<br>the Bank S |                |                     |                   |     |      |                            |  |

| Wor                                    | ds:            | 1                   |                   |     |      |                            |  |

| Cycl                                   | es:            | 1                   |                   |     |      |                            |  |

| QC                                     | ycle Activity: |                     |                   |     |      |                            |  |

|                                        | Q1             | Q2                  | Q3                |     |      | Q4                         |  |

|                                        | Decode         | Read literal<br>'k' | Proce<br>Data     |     | lite | Write<br>ral 'k' to<br>BSR |  |

Move literal to low nibble in BSR

Example: MOVLB 5

| =                         |   |      |

|---------------------------|---|------|

| <b>Before Instruction</b> |   |      |

| BSR register              | = | 0x02 |

| After Instruction         |   |      |

| BSR register              | = | 0x05 |

### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F6520/8520/6620/8620/6720/8720 (Industrial, Extended) PIC18LF6520/8520/6620/8620/6720/8720 (Industrial) (Continued)

| PIC18LF(<br>(Indu | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                          |                                                                                                                                                                                         |    |       |            |                                |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|------------|--------------------------------|--|

|                   | <b>520/8520/6620/8620/6720/8720</b><br>strial, Extended)                                                                           |                          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |    |       |            |                                |  |

| Param<br>No.      | Device                                                                                                                             | Typ Max Units Conditions |                                                                                                                                                                                         |    |       | ons        |                                |  |

|                   | Supply Current (IDD) <sup>(2,3)</sup>                                                                                              |                          |                                                                                                                                                                                         |    |       |            |                                |  |

|                   | PIC18LFXX20                                                                                                                        | 165                      | 350                                                                                                                                                                                     | μΑ | -40°C |            |                                |  |

|                   |                                                                                                                                    | 165                      | 350                                                                                                                                                                                     | μΑ | +25°C | VDD = 2.0V |                                |  |

|                   |                                                                                                                                    | 170                      | 350                                                                                                                                                                                     | μΑ | +85°C |            |                                |  |

|                   | PIC18LFXX20                                                                                                                        | 360                      | 750                                                                                                                                                                                     | μΑ | -40°C | Vdd = 3.0V |                                |  |

|                   |                                                                                                                                    | 340                      | 750                                                                                                                                                                                     | μΑ | +25°C |            | Fosc = 1 MHz,<br>EC oscillator |  |

|                   |                                                                                                                                    | 300                      | 750                                                                                                                                                                                     | μΑ | +85°C |            | 20 000                         |  |

|                   | All devices                                                                                                                        | 800                      | 1700                                                                                                                                                                                    | μΑ | -40°C |            |                                |  |

|                   |                                                                                                                                    | 730                      | 1700                                                                                                                                                                                    | μΑ | +25°C | VDD = 5.0V |                                |  |

|                   |                                                                                                                                    | 700                      | 1700                                                                                                                                                                                    | μΑ | +85°C |            |                                |  |

|                   | PIC18LFXX20                                                                                                                        | 600                      | 1200                                                                                                                                                                                    | μΑ | -40°C |            |                                |  |

|                   |                                                                                                                                    | 600                      | 1200                                                                                                                                                                                    | μΑ | +25°C | VDD = 2.0V |                                |  |

|                   |                                                                                                                                    | 640                      | 1300                                                                                                                                                                                    | μΑ | +85°C |            |                                |  |

|                   | PIC18LFXX20                                                                                                                        | 1000                     | 2500                                                                                                                                                                                    | μΑ | -40°C |            |                                |  |

|                   |                                                                                                                                    | 1000                     | 2500                                                                                                                                                                                    | μΑ | +25°C | VDD = 3.0V | Fosc = 4 MHz,<br>EC oscillator |  |

|                   |                                                                                                                                    | 1000                     | 2500                                                                                                                                                                                    | μΑ | +85°C |            |                                |  |

|                   | All devices                                                                                                                        | 2.2                      | 5.0                                                                                                                                                                                     | mA | -40°C |            |                                |  |

|                   |                                                                                                                                    | 2.1                      | 5.0                                                                                                                                                                                     | mA | +25°C | VDD = 5.0V |                                |  |

|                   |                                                                                                                                    | 2.0                      | 5.0                                                                                                                                                                                     | mA | +85°C |            |                                |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- $\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

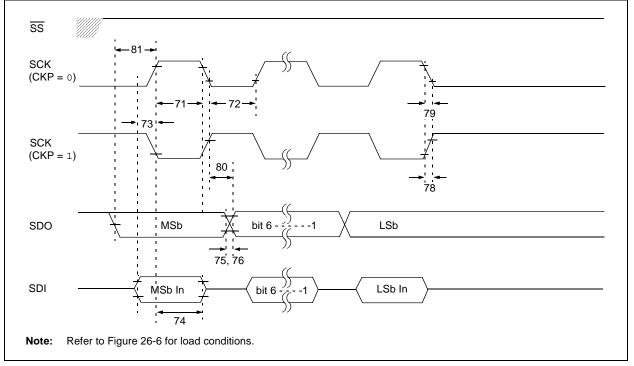

| Param<br>No. | Symbol                | Characteristic                                                         |             | Min           | Max | Units | Conditions |

|--------------|-----------------------|------------------------------------------------------------------------|-------------|---------------|-----|-------|------------|

| 70           | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input |             | Тсү           |     | ns    |            |

| 71           | TscH                  | SCK Input High Time                                                    | Continuous  | 1.25 TCY + 30 | _   | ns    |            |

| 71A          |                       | (Slave mode)                                                           | Single Byte | 40            | _   | ns    | (Note 1)   |

| 72           | TscL                  | SCK Input Low Time                                                     | Continuous  | 1.25 TCY + 30 | _   | ns    |            |

| 72A          |                       | (Slave mode)                                                           | Single Byte | 40            | _   | ns    | (Note 1)   |

| 73           | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDI Data Input to SCK Edge                               |             | 100           | _   | ns    |            |

| 73A          | Тв2в                  | Last Clock Edge of Byte 1 to the 1st Clock Edge of Byte 2              |             | 1.5 Tcy + 40  |     | ns    | (Note 2)   |

| 74           | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                                |             | 100           | _   | ns    |            |

| 75           | TDOR                  | SDO Data Output Rise Time                                              | PIC18FXX20  | —             | 25  | ns    |            |

|              |                       |                                                                        | PIC18LFXX20 | —             | 45  | ns    | VDD = 2.0V |

| 76           | TDOF                  | SDO Data Output Fall Time                                              |             | —             | 25  | ns    |            |

| 78           | TscR                  | SCK Output Rise Time                                                   | PIC18FXX20  | —             | 25  | ns    |            |

|              |                       | (Master mode)                                                          | PIC18LFXX20 | —             | 45  | ns    | VDD = 2.0V |

| 79           | TscF                  | SCK Output Fall Time (Master mode)                                     |             | —             | 25  | ns    |            |

| 80           | TscH2doV,             | SDO Data Output Valid after SCK                                        | PIC18FXX20  | —             | 50  | ns    |            |

|              | TscL2doV              | Edge                                                                   | PIC18LFXX20 | —             | 100 | ns    | VDD = 2.0V |

| TABLE 26-15: | EXAMPLE SPI MODE REQUIREMENTS | (MASTER MODE. CKE = $0$ ) |

|--------------|-------------------------------|---------------------------|

|              |                               |                           |

**Note 1:** Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

© 2003-2013 Microchip Technology Inc.