Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

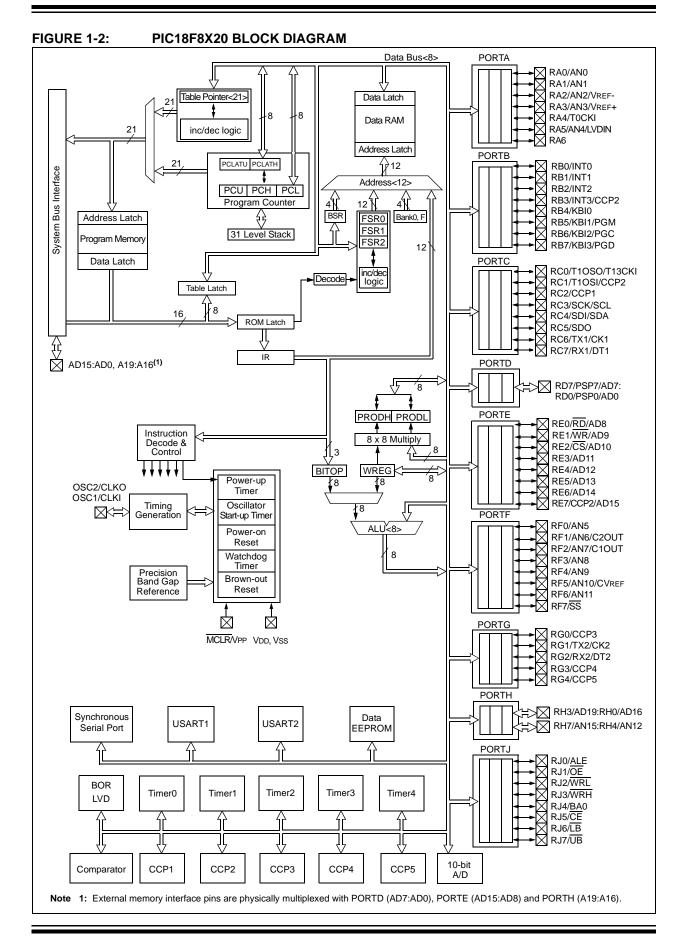

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6720-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

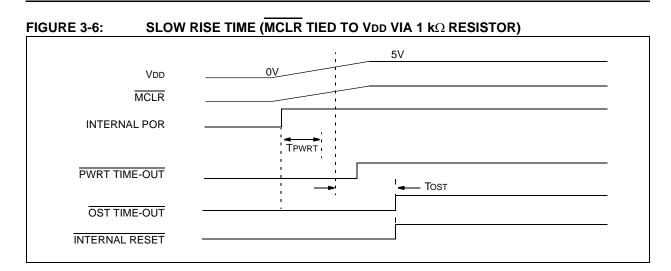

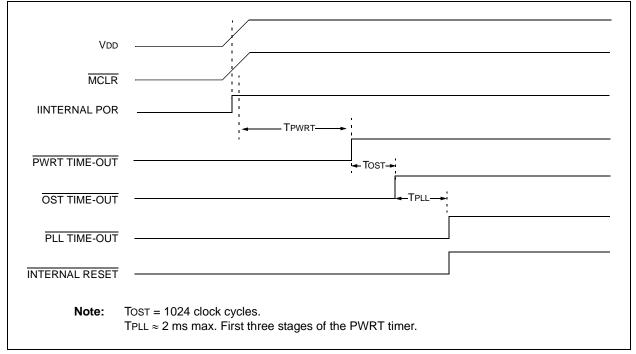

# FIGURE 3-7:TIME-OUT SEQUENCE ON POR W/PLL ENABLED<br/>(MCLR TIED TO VDD VIA 1 k $\Omega$ RESISTOR)

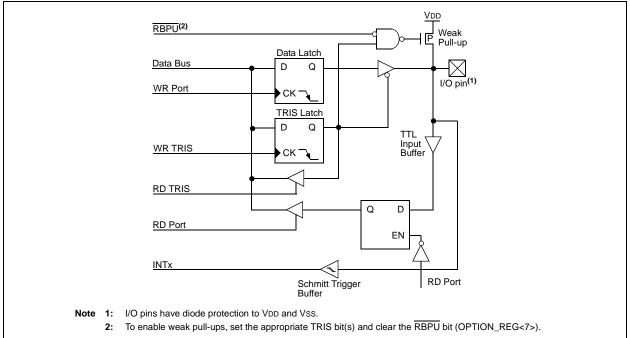

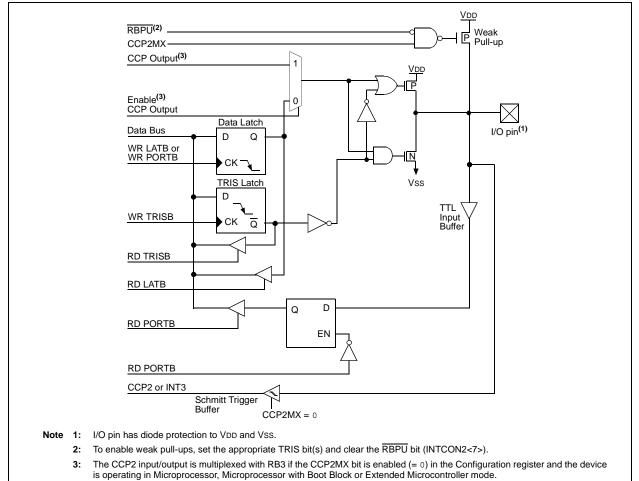

### FIGURE 10-6: BLOCK DIAGRAM OF RB2:RB0 PINS

#### FIGURE 10-7: BLOCK DIAGRAM OF RB3 PIN

| TABLE 10-3. PU               |       |                       |                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|------------------------------|-------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Name                         | Bit#  | Buffer                | Function                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| RB0/INT0                     | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 0.<br>Internal software programmable weak pull-up.                                                                                                                                                |  |  |  |  |  |  |  |  |

| RB1/INT1                     | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 1.<br>Internal software programmable weak pull-up.                                                                                                                                                |  |  |  |  |  |  |  |  |

| RB2/INT2                     | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                                                                                                |  |  |  |  |  |  |  |  |

| RB3/INT3/CCP2 <sup>(3)</sup> | bit 3 | TTL/ST <sup>(4)</sup> | Input/output pin or external interrupt input 3. Capture2 input/Compare2 output/PWM output (when CCP2MX configuration bit is enabled, all PIC18F8X20 operating modes except Microcontroller mode). Internal software programmable weak pull-up. |  |  |  |  |  |  |  |  |

| RB4/KBI0                     | bit 4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                                                                                                                   |  |  |  |  |  |  |  |  |

| RB5/KBI1/PGM                 | bit 5 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Low-voltage ICSP enable pin.                                                                                                                   |  |  |  |  |  |  |  |  |

| RB6/KBI2/PGC                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming clock.                                                                                                                      |  |  |  |  |  |  |  |  |

| RB7/KBI3/PGD                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming data.                                                                                                                       |  |  |  |  |  |  |  |  |

#### TABLE 10-3 PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: RC1 is the alternate assignment for CCP2 when CCP2MX is not set (all operating modes except Microcontroller mode).

- 4: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

INT2IE

| TADLL   | TABLE 10-4. SUMMART OF REGISTERS ASSOCIATED WITH FORTB |               |            |           |           |        |        |       |                      |                                 |  |  |  |

|---------|--------------------------------------------------------|---------------|------------|-----------|-----------|--------|--------|-------|----------------------|---------------------------------|--|--|--|

| Name    | Bit 7                                                  | Bit 6         | Bit 5      | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |  |  |

| PORTB   | RB7                                                    | RB6           | RB5        | RB4       | RB3       | RB2    | RB1    | RB0   | xxxx xxxx            | uuuu uuuu                       |  |  |  |

| LATB    | LATB Data                                              | a Output Re   |            | xxxx xxxx | uuuu uuuu |        |        |       |                      |                                 |  |  |  |

| TRISB   | PORTB D                                                | ata Directior | n Register |           |           |        |        |       | 1111 1111            | 1111 1111                       |  |  |  |

| INTCON  | GIE/<br>GIEH                                           | PEIE/<br>GIEL | TMR0IE     | INTOIE    | RBIE      | TMR0IF | INTOIF | RBIF  | 0000 0000            | 0000 0000                       |  |  |  |

| INTCON2 | RBPU                                                   | INTEDG0       | INTEDG1    | INTEDG2   | INTEDG3   | TMR0IP | INT3IP | RBIP  | 1111 1111            | 1111 1111                       |  |  |  |

INT1IE

INT3IF

INT2IF

INT1IF

#### TABLE 10-1. SUMMARY OF REGISTERS ASSOCIATED WITH PORTR

INT3IE x = unknown, u = unchanged. Shaded cells are not used by PORTB. Legend:

INTCON3

INT2IP

INT1IP

1100 0000

1100 0000

| Name         | Bit#  | Buffer Type           | Function                                                                    |

|--------------|-------|-----------------------|-----------------------------------------------------------------------------|

| RD0/PSP0/AD0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 0 or address/data bus bit 0. |

| RD1/PSP1/AD1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 1 or address/data bus bit 1. |

| RD2/PSP2/AD2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 2 or address/data bus bit 2. |

| RD3/PSP3/AD3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 3 or address/data bus bit 3. |

| RD4/PSP4/AD4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 4 or address/data bus bit 4. |

| RD5/PSP5/AD5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 5 or address/data bus bit 5. |

| RD6/PSP6/AD6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 6 or address/data bus bit 6. |

| RD7/PSP7/AD7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 7 or address/data bus bit 7. |

### TABLE 10-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

WAIT1

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in System Bus or Parallel Slave Port mode.

| Name   | Bit 7   | Bit 6    | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|----------|-------|-----------|-----------|-------|-------|-------|----------------------|---------------------------------|

| PORTD  | RD7     | RD6      | RD5   | RD4       | RD3       | RD2   | RD1   | RD0   | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Da | ata Outp |       | xxxx xxxx | uuuu uuuu |       |       |       |                      |                                 |

| TRISD  | PORTD   | Data Dir |       | 1111 1111 | 1111 1111 |       |       |       |                      |                                 |

| PSPCON | IBF     | OBF      | IBOV  | PSPMODE   | _         | _     | _     | _     | 0000                 | 0000                            |

TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

WAIT0

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

WM1

WM0

0-00 --00

0-00 --00

MEMCON EBDIS

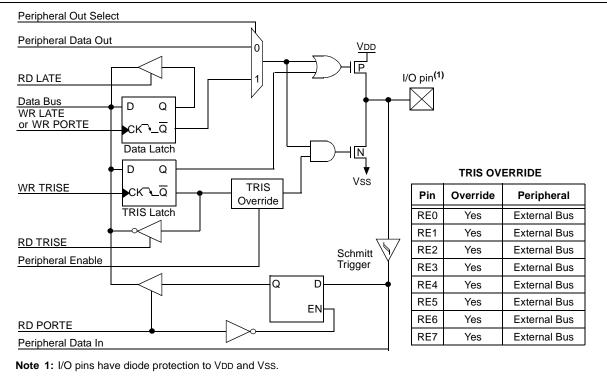

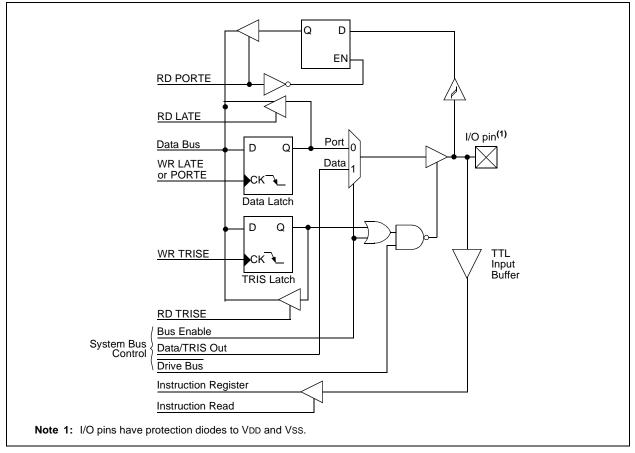

### FIGURE 10-11: PORTE BLOCK DIAGRAM IN I/O MODE

### FIGURE 10-12: PORTE BLOCK DIAGRAM IN SYSTEM BUS MODE

© 2003-2013 Microchip Technology Inc.

| EXAMPLE | 12-1:  | IMPLEMENTIN  | IG A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE |

|---------|--------|--------------|-------------------------------------------------------|

| RTCinit |        |              |                                                       |

|         | MOVLW  | 0x80         | ; Preload TMR1 register pair                          |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                               |

|         | CLRF   | TMR1L        |                                                       |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                       |

|         | MOVWF  | T10SC        | ; Asynchronous operation, external oscillator         |

|         | CLRF   | secs         | ; Initialize timekeeping registers                    |

|         | CLRF   | mins         | ;                                                     |

|         | MOVLW  | .12          |                                                       |

|         | MOVWF  | hours        |                                                       |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                             |

|         | RETURN |              |                                                       |

| RTCisr  |        |              |                                                       |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                          |

|         | BCF    | PIR1, TMR1IF |                                                       |

|         | INCF   | secs, F      | ; Increment seconds                                   |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | secs         | ; Clear seconds                                       |

|         | INCF   | mins, F      | ; Increment minutes                                   |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | mins         | ; clear minutes                                       |

|         | INCF   | hours, F     | ; Increment hours                                     |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                   |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | MOVLW  | .01          | ; Reset hours to 1                                    |

|         | MOVWF  | hours        |                                                       |

|         | RETURN |              | ; Done                                                |

| J       |        |              |                                                       |

### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7       | Bit 6          | Bit 5       | Bit 4         | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|--------|-------------|----------------|-------------|---------------|----------------|-----------|--------|--------|---------------|------|------|-----------------------|

| INTCON | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE        | RBIE           | TMR0IF    | INT0IF | RBIF   | 0000          | 0000 | 0000 | 0000                  |

| PIR1   | PSPIF       | ADIF           | RCIF        | TXIF          | SSPIF          | CCP1IF    | TMR2IF | TMR1IF | 0000          | 0000 | 0000 | 0000                  |

| PIE1   | PSPIE       | ADIE           | RCIE        | TXIE          | SSPIE          | CCP1IE    | TMR2IE | TMR1IE | 0000          | 0000 | 0000 | 0000                  |

| IPR1   | PSPIP       | ADIP           | RCIP        | TXIP          | SSPIP          | CCP1IP    | TMR2IP | TMR1IP | 0111          | 1111 | 0111 | 1111                  |

| TMR1L  | Holding Reg | gister for the | Least Signi | ficant Byte o | of the 16-bit  | TMR1 Regi | ster   |        | xxxx          | xxxx | uuuu | uuuu                  |

| TMR1H  | Holding Reg | gister for the | Most Signif | icant Byte o  | f the 16-bit T | MR1 Regis | ster   |        | xxxx          | xxxx | uuuu | uuuu                  |

| T1CON  | RD16        | —              | T1CKPS1     | T1CKPS0       | T1OSCEN        | T1SYNC    | TMR1CS | TMR10N | 0-00          | 0000 | u-uu | uuuu                  |

$\label{eq:logend: Legend: Legend: u = unchanged, -= unimplemented, read as `0`. Shaded cells are not used by the Timer1 module.$

# 16.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The PIC18FXX20 devices all have five CCP (Capture/ Compare/PWM) modules. Each module contains a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a Pulse Width Modulation (PWM) Master/Slave Duty Cycle register. Table 16-1 shows the timer resources of the CCP module modes.

The operation of all CCP modules are identical, with the exception of the special event trigger present on CCP1 and CCP2. For the sake of clarity, CCP module operation in the following sections is described with respect to CCP1. The descriptions can be applied (with the exception of the special event triggers) to any of the modules.

Note: Throughout this section, references to register and bit names that may be associated with a specific CCP module are referred to generically by the use of 'x' or 'y' in place of the specific module number. Thus, "CCPxCON" might refer to the control register for CCP1, CCP2, CCP3, CCP4 or CCP5.

### REGISTER 16-1: CCPxCON REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

|       | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 DCxB1:DCxB0: PWM Duty Cycle bit 1 and bit 0 for CCP Module x

- Capture mode:

- Unused.

- Compare mode: Unused.

- PWM mode:

These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCx9:DCx2) of the duty cycle are found in CCPRxL.

#### bit 3-0 CCPxM3:CCPxM0: CCP Module x Mode Select bits

- 0000 = Capture/Compare/PWM disabled (resets CCPx module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match (CCPxIF bit is set)

- 0011 = Reserved

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, Initialize CCP pin Low; on compare match, force CCP pin High (CCPIF bit is set)

- 1001 = Compare mode, Initialize CCP pin High; on compare match, force CCP pin Low (CCPIF bit is set)

- 1010 = Compare mode, Generate software interrupt on compare match (CCPIF bit is set, (CCP pin is unaffected)

- 1011 = Compare mode, trigger special event (CCPIF bit is set):

- For CCP1 and CCP2:

- Timer1 or Timer3 is reset on event.

- For all other modules:

- CCPx pin is unaffected and is configured as an I/O port

- (same as CCPxM<3:0> = 1010, above).

- 11xx = PWM mode

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

### EQUATION 16-3:

PWM Resolution (max) =  $\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### 16.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

### TABLE 16-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

bits

| PWM Frequency              | 2.44 kHz            | 9.77 kHz            | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|---------------------|---------------------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16                  | 4                   | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh                 | FFh                 | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | $14 \rightarrow 10$ | $12 \rightarrow 10$ | 10        | 8          | 7          | 6.58       |

### TABLE 16-4: REGISTERS ASSOCIATED WITH PWM, TIMER2 AND TIMER4

| Name                   | Bit 7      | Bit 6 Bit 5   |              | Bit 4 Bit 3 |          | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|------------|---------------|--------------|-------------|----------|--------|---------|---------|----------------------|---------------------------------|

| INTCON                 | GIE/GIEH   | PEIE/GIEL     | TMR0IE       | INT0IE      | RBIE     | TMR0IF | INT0IF  | RBIF    | 0000 0000            | 0000 0000                       |

| RCON                   | IPEN       | _             | _            | RI          | TO       | PD     | POR     | BOR     | 01 11qq              | 0q qquu                         |

| PIR1                   | PSPIF      | ADIF          | RCIF         | TXIF        | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000            | 0000 0000                       |

| PIE1                   | PSPIE      | ADIE          | RCIE         | TXIE        | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000            | 0000 0000                       |

| IPR1                   | PSPIP      | ADIP          | RCIP         | TXIP        | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 0111 1111            | 0111 1111                       |

| PIR2                   | _          | CMIE          |              | EEIE        | BCLIF    | LVDIF  | TMR3IF  | CCP2IF  | -0-0 0000            | 0 0000                          |

| PIE2                   | _          | CMIF          |              | EEIF        | BCLIE    | LVDIE  | TMR3IE  | CCP2IE  | -0-0 0000            | 0 0000                          |

| IPR2                   | _          | CMIP          |              | EEIP        | BCLIP    | LVDIP  | TMR3IP  | CCP2IP  | -1-1 1111            | 1 1111                          |

| PIR3                   | _          | _             | RC2IF        | TX2IF       | TMR4IF   | CCP5IF | CCP4IF  | CCP3IF  | 00 0000              | 00 0000                         |

| PIE3                   |            | _             | RC2IE        | TX2IE       | TMR4IE   | CCP5IE | CCP4IE  | CCP3IE  | 00 0000              | 00 0000                         |

| IPR3                   |            | _             | RC2IP        | TX2IP       | TMR4IP   | CCP5IP | CCP4IP  | CCP3IP  | 11 1111              | 11 1111                         |

| TMR2                   | Timer2 Mo  | dule Registe  | r            |             |          |        |         |         | 0000 0000            | 0000 0000                       |

| PR2                    | Timer2 Mo  | dule Period I | Register     |             |          |        |         |         | 1111 1111            | 1111 1111                       |

| T2CON                  | _          | T2OUTPS3      | T2OUTPS2     | T2OUTPS1    | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| T3CON                  | RD16       | T3CCP2        | T3CKPS1      | T3CKPS0     | T3CCP1   | T3SYNC | TMR3CS  | TMR3ON  | 0000 0000            | uuuu uuuu                       |

| TMR4                   | Timer4 Re  | gister        |              |             |          |        |         |         | 0000 0000            | uuuu uuuu                       |

| PR4                    | Timer4 Per | riod Register |              |             |          |        |         |         | 1111 1111            | uuuu uuuu                       |

| T4CON                  | _          | T4OUTPS3      | T4OUTPS2     | T4OUTPS1    | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | -000 0000            | uuuu uuuu                       |

| CCPRxL <sup>(1)</sup>  | Capture/Co | ompare/PWN    | I Register x | (LSB)       |          |        |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPRxH <sup>(1)</sup>  | Capture/Co | ompare/PWN    | I Register x | (MSB)       |          |        |         |         | xxxx xxxx            | uuuu uuuu                       |

| CCPxCON <sup>(1)</sup> | —          | _             | DCxB1        | DCxB0       | CCPxM3   | CCPxM2 | CCPxM1  | CCPxM0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM, Timer2, or Timer4.

Note 1: Generic term for all of the identical registers of this name for all CCP modules, where 'x' identifies the individual module (CCP1 through CCP5). Bit assignments and Reset values for all registers of the same generic name are identical.

### 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate Generator"**, for more information.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop enable bit PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

### 18.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the TXx pin (RC6/TX1/CK1 or RG1/TX2/CK2), instead of being supplied internally in Master mode. TRISC<6> must be set for this mode. This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTAx<7>).

#### 18.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXxIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit TXxIF will now be set.

- e) If enable bit TXxIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXxIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name                  | Bit 7        | Bit 6         | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|--------------|---------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE     | INT0IE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                  | PSPIF        | ADIF          | RC1IF      | TX1IF  | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                  | PSPIE        | ADIE          | RC1IE      | TX1IE  | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                  | PSPIP        | ADIP          | RC1IP      | TX1IP  | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR3                  | _            | _             | RC2IF      | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 00 0000              | 00 0000                         |

| PIE3                  | _            |               | RC2IE      | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 00 0000              | 00 0000                         |

| IPR3                  | _            | _             | RC2IP      | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup> | SPEN         | RX9           | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TXREGx <sup>(1)</sup> | USART Tra    | ansmit Reg    | gister     |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup> | CSRC         | TX9           | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> | Baud Rate    | Generato      | r Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

### TABLE 18-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

### **19.1** A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 19-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

| Note: | When    | the    | conversion      | is  | started,   | the |

|-------|---------|--------|-----------------|-----|------------|-----|

|       | holding | g capa | acitor is disco | nne | ected from | the |

|       | input p | in.    |                 |     |            |     |

To calculate the minimum acquisition time, Equation 19-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution. Example 19-1 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 120 pF                             |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $5V \rightarrow Rss = 7 \ k\Omega$ |

| Temperature      | =      | 50°C (system max.)                 |

| VHOLD            | =      | 0V @ time = 0                      |

|                  |        |                                    |

**Note:** When using external voltage references with the A/D converter, the source impedance of the external voltage references must be less than  $20\Omega$  to obtain the A/D performance specified in parameters A01-A06. Higher reference source impedances will increase both offset and gain errors. Resistive voltage dividers will not provide a sufficiently low source impedance.

To maintain the best possible performance in A/D conversions, external VREF inputs should be buffered with an operational amplifier or other low output impedance circuit.

If deviating from the operating conditions specified for parameters A03-A06, the effect of parameter A50 (VREF input current) must be considered.

### EQUATION 19-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|------|---|-------------------------------------------------------------------------------------|

= TAMP + TC + TCOFF

#### EQUATION 19-2: A/D MINIMUM CHARGING TIME

| VHOLD    | ) = | $(\text{VREF} - (\text{VREF}/2048)) \bullet (1 - e^{(-\text{Tc/Chold}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|----------|-----|----------------------------------------------------------------------------------------------------------------|

| or       |     |                                                                                                                |

| or<br>TC | =   | $-(120 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/2047)$                                    |

### EXAMPLE 19-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =       | TAMP + TC + TCOFF                                                                                                                                                                                           |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tempera | ature c | coefficient is only required for temperatures $> 25^{\circ}$ C.                                                                                                                                             |

| TACQ    | =       | $2 \mu s + TC + [(Temp - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$                                                                                                                                               |

| Тс      | =       | -CHOLD (RIC + RSS + RS) $\ln(1/2047)$<br>-120 pF (1 k $\Omega$ + 7 k $\Omega$ + 2.5 k $\Omega$ ) $\ln(0.0004885)$<br>-120 pF (10.5 k $\Omega$ ) $\ln(0.0004885)$<br>-1.26 $\mu$ s (-7.6241)<br>9.61 $\mu$ s |

| TACQ    | =       | 2 μs + 9.61 μs + [(50°C – 25°C)(0.05 μs/°C)]<br>11.61 μs + 1.25 μs<br>12.86 μs                                                                                                                              |

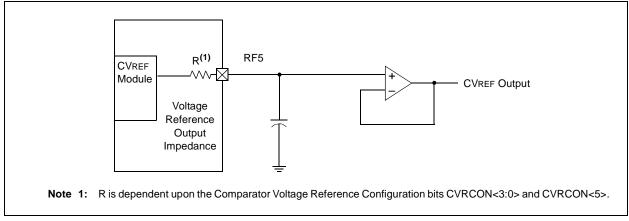

### FIGURE 21-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

### TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| CVRCON | CVREN  | CVROE  | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 0000 0000       | 0000 0000                       |

| CMCON  | C2OUT  | C1OUT  | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| TRISF  | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 1111 1111       | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

| BTG               | Bit Toggle                                                                                                                                                                                                                        | e f               |                       | BOV                                                                                                                                                                                                                                            | Branch if                 | Overflow                  |             |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|-------------|--|--|

| Syntax:           | [label] BTG f,b[,a]                                                                                                                                                                                                               |                   |                       | Syntax:                                                                                                                                                                                                                                        | [ <i>label</i> ] B        | [ <i>label</i> ] BOV n    |             |  |  |

| Operands:         | $0 \leq f \leq 255$                                                                                                                                                                                                               |                   |                       | Operands:                                                                                                                                                                                                                                      | -128 ≤ n ≤                | 127                       |             |  |  |

|                   | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                            |                   |                       | Operation:                                                                                                                                                                                                                                     | if Overflov<br>(PC) + 2 + | v bit is '1'<br>- 2n → PC |             |  |  |

| Operation:        | $(f < b >) \rightarrow f$                                                                                                                                                                                                         | <b></b>           |                       | Status Affected:                                                                                                                                                                                                                               | None                      |                           |             |  |  |

| Status Affected:  | None                                                                                                                                                                                                                              |                   |                       | Encoding:                                                                                                                                                                                                                                      | 1110                      | 0100 nn                   | nn nnnn     |  |  |

| Encoding:         | 0111                                                                                                                                                                                                                              | bbba f            | fff ffff              | Description:                                                                                                                                                                                                                                   | If the Ove                | rflow bit is '1           | ' then the  |  |  |

|                   | escription: Bit 'b' in data memory location 'f' is<br>inverted. If 'a' is '0', the Access Bank<br>will be selected, overriding the BSR<br>value. If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |                   |                       | program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |                           |                           |             |  |  |

| Words:            | 1                                                                                                                                                                                                                                 |                   |                       | Words:                                                                                                                                                                                                                                         | 1                         |                           | •           |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                 |                   |                       |                                                                                                                                                                                                                                                |                           |                           |             |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                   |                   |                       | Cycles:                                                                                                                                                                                                                                        | 1(2)                      |                           |             |  |  |

| Q1                | Q2                                                                                                                                                                                                                                | Q3                | Q4                    | Q Cycle Activity<br>If Jump:                                                                                                                                                                                                                   |                           |                           |             |  |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                              | Process<br>Data   | Write<br>register 'f' | Q1                                                                                                                                                                                                                                             | Q2                        | Q3                        | Q4          |  |  |

| Example:          | BTG F                                                                                                                                                                                                                             | PORTC, 4,         | 0                     | Decode                                                                                                                                                                                                                                         | Read literal<br>'n'       | Process<br>Data           | Write to PC |  |  |

| Before Instru     |                                                                                                                                                                                                                                   |                   |                       | No                                                                                                                                                                                                                                             | No                        | No                        | No          |  |  |

| PORTC             |                                                                                                                                                                                                                                   | 101 <b>[0x75]</b> |                       | operation                                                                                                                                                                                                                                      | operation                 | operation                 | operation   |  |  |

| After Instruct    | ion:                                                                                                                                                                                                                              |                   |                       | If No Jump:<br>Q1                                                                                                                                                                                                                              | Q2                        | Q3                        | Q4          |  |  |

| PORTC             | = 0110 0                                                                                                                                                                                                                          | 101 <b>[0x65]</b> |                       | Decode                                                                                                                                                                                                                                         | Read literal              | Process                   | No          |  |  |

|                   |                                                                                                                                                                                                                                   |                   |                       |                                                                                                                                                                                                                                                | 'n'                       | Data                      | operation   |  |  |

|                   |                                                                                                                                                                                                                                   |                   |                       | Example:                                                                                                                                                                                                                                       | HERE                      | BOV Jump                  | )           |  |  |

|                   |                                                                                                                                                                                                                                   |                   |                       | Before Instru                                                                                                                                                                                                                                  | uction                    |                           |             |  |  |

PC

After Instruction

If Overflow = PC = If Overflow = PC =

=

1;

address (HERE)

address (Jump) 0; address (HERE+2)

| © 2003-2013 Microchip | Technology Inc. |

|-----------------------|-----------------|

|-----------------------|-----------------|

### 26.2 DC Characteristics: Power-Down and Supply Current PIC18F6520/8520/6620/8620/6720/8720 (Industrial, Extended) PIC18LF6520/8520/6620/8620/6720/8720 (Industrial) (Continued)

| PIC18LF6520/8520/6620/8620/6720/8720<br>(Industrial) |                                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |                 |            |                                   |  |  |  |

|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------|------------|-----------------------------------|--|--|--|

| PIC18F65<br>(Indu                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                    |     |       |                 |            |                                   |  |  |  |

| Param<br>No.                                         | Device                                               | Тур                                                                                                                                | Max | Units |                 | Conditio   | ons                               |  |  |  |

|                                                      | Supply Current (IDD) <sup>(2,3)</sup>                |                                                                                                                                    |     |       |                 |            |                                   |  |  |  |

|                                                      | PIC18FX620, PIC18FX720                               | 9.3                                                                                                                                | 15  | mA    | -40°C           |            |                                   |  |  |  |

|                                                      |                                                      | 9.5                                                                                                                                | 15  | mA    | +25°C           | VDD = 4.2V |                                   |  |  |  |

|                                                      |                                                      | 10                                                                                                                                 | 15  | mA    | +85°C           |            | Fosc = 25 MHz,                    |  |  |  |

|                                                      | PIC18FX620, PIC18FX720                               | 11.8                                                                                                                               | 20  | mA    | -40°C           |            | EC oscillator                     |  |  |  |

|                                                      |                                                      | 12                                                                                                                                 | 20  | mA    | +25°C           | VDD = 5.0V |                                   |  |  |  |

|                                                      |                                                      | 12                                                                                                                                 | 20  | mA    | +85°C           |            |                                   |  |  |  |

|                                                      | PIC18FX520                                           | 16                                                                                                                                 | 20  | mA    | -40°C           |            |                                   |  |  |  |

|                                                      |                                                      | 16                                                                                                                                 | 20  | mA    | +25°C           | VDD = 4.2V |                                   |  |  |  |

|                                                      |                                                      | 16                                                                                                                                 | 20  | mA    | +85°C           |            | Fosc = 40 MHz,                    |  |  |  |

|                                                      | PIC18FX520                                           | 19                                                                                                                                 | 25  | mA    | -40°C           |            | EC oscillator                     |  |  |  |

|                                                      |                                                      | 19                                                                                                                                 | 25  | mA    | +25°C           | VDD = 5.0V |                                   |  |  |  |

|                                                      |                                                      | 19                                                                                                                                 | 25  | mA    | +85°C           |            |                                   |  |  |  |

| D014                                                 | PIC18FX620/X720                                      | 15                                                                                                                                 | 55  | μA    | -40°C to +85°C  | VDD = 2.0V | Fosc = 32 kHz,<br>Timer1 as clock |  |  |  |

|                                                      | PIC18LF8520                                          | 13                                                                                                                                 | 18  | μA    | -40°C to +85°C  | VDD = 2.0V |                                   |  |  |  |

|                                                      |                                                      | 20                                                                                                                                 | 35  | μΑ    | -40°C to +85°C  | VDD = 3.0V | Fosc = 32 kHz,<br>Timer1 as clock |  |  |  |

|                                                      |                                                      | 50                                                                                                                                 | 85  | μΑ    | -40°C to +85°C  | VDD = 5.0V |                                   |  |  |  |

|                                                      | PIC18FXX20                                           | —                                                                                                                                  | 200 | μΑ    | -40°C to +85°C  | VDD = 4.2V | Fosc = 32 kHz,                    |  |  |  |

|                                                      |                                                      | _                                                                                                                                  | 250 | μA    | -40°C to +125°C | VDD = 4.2V | Timer1 as clock                   |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

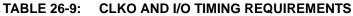

| Param<br>No. | Symbol   | Characteristics                                                           | Min            | Тур       | Max            | Units |

|--------------|----------|---------------------------------------------------------------------------|----------------|-----------|----------------|-------|

| 150          | TADV2ALL | Address Out Valid to ALE $\downarrow$ (address setup time)                | 0.25 Tcy – 10  |           | —              | ns    |

| 151          | TalL2adl | ALE $\downarrow$ to Address Out Invalid (address hold time)               | 5              |           | —              | ns    |

| 155          | TALL20EL | ALE $\downarrow$ to $\overline{OE} \downarrow$                            | 10             | 0.125 TCY | —              | ns    |

| 160          | TADZ2OEL | AD high-Z to $\overline{OE} \downarrow$ (bus release to $\overline{OE}$ ) | 0              |           | —              | ns    |

| 161          | TOEH2ADD | OE ↑ to AD Driven                                                         | 0.125 Tcy – 5  |           | —              | ns    |

| 162          | TADV20EH | LS Data Valid before $\overline{OE}$ $\uparrow$ (data setup time)         | 20             |           | —              | ns    |

| 163          | TOEH2ADL | OE ↑ to Data In Invalid (data hold time)                                  | 0              |           | —              | ns    |

| 164          | TALH2ALL | ALE Pulse Width                                                           | —              | 0.25 TCY  | —              | ns    |

| 165          | Toel2oeH | OE Pulse Width                                                            | 0.5 Tcy – 5    | 0.5 TCY   | _              | ns    |

| 166          | TalH2alH | ALE $\uparrow$ to ALE $\uparrow$ (cycle time)                             | —              | Тсү       | —              | ns    |

| 167          | TACC     | Address Valid to Data Valid                                               | 0.75 Tcy – 25  |           | —              | ns    |

| 168          | Toe      | $\overline{OE}\downarrow$ to Data Valid                                   |                |           | 0.5 Tcy – 25   | ns    |

| 169          | TALL20EH | ALE ↓ to OE ↑                                                             | 0.625 Tcy - 10 |           | 0.625 TCY + 10 | ns    |

| 171          | TALH2CSL | Chip Enable Active to ALE $\downarrow$                                    | —              | -         | 10             | ns    |

| 171A         | TUBL20EH | AD Valid to Chip Enable Active                                            | 0.25 Tcy – 20  |           | _              | ns    |

**PROGRAM MEMORY WRITE TIMING DIAGRAM**

© 2003-2013 Microchip Technology Inc.

| Param<br>No. | Symbol   | Characteristic                                                             | Min          | Max | Units    | Conditions           |                      |

|--------------|----------|----------------------------------------------------------------------------|--------------|-----|----------|----------------------|----------------------|

| 62           | TdtV2wrH | Data In Valid before $\overline{WR} \uparrow or \overline{C}$ (setup time) | 20<br>25     | _   | ns<br>ns | Extended Temp. range |                      |

| 63           | TwrH2dtl | $\overline{WR}$ $\uparrow$ or $\overline{CS}$ $\uparrow$ to Data–In        | PIC18FXX20   | 20  | _        | ns                   |                      |

|              |          | Invalid (hold time)                                                        | PIC18LFXX20  | 35  | _        | ns                   | VDD = 2.0V           |

| 64           | TrdL2dtV | $\overline{RD} \downarrow and \overline{CS} \downarrow to Data-Out V$      | alid         | _   | 80       | ns                   |                      |

|              |          |                                                                            |              | _   | 90       | ns                   | Extended Temp. range |

| 65           | TrdH2dtI | $\overline{RD}$ $\uparrow$ or $\overline{CS} \downarrow$ to Data–Out Inv   | alid         | 10  | 30       | ns                   |                      |

| 66           | TibfINH  | Inhibit of the IBF flag bit being WR $\uparrow$ or CS $\uparrow$           | cleared from |     | 3 TCY    |                      |                      |

### TABLE 26-14: PARALLEL SLAVE PORT REQUIREMENTS (PIC18F8X20)

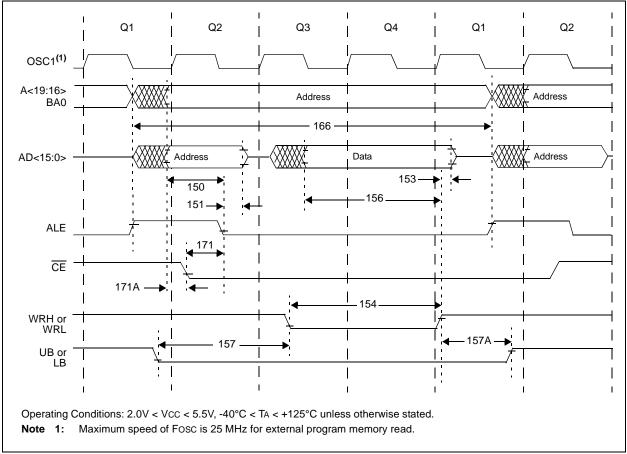

## FIGURE 26-16: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

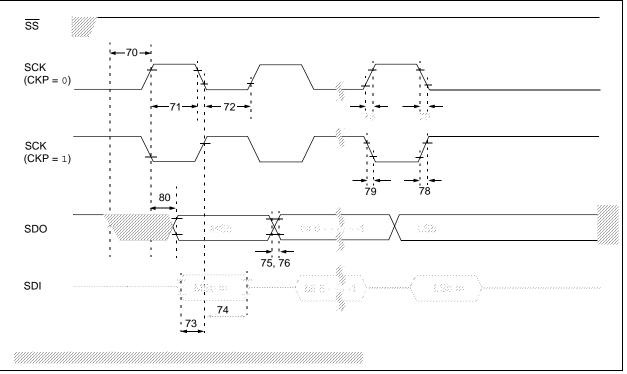

# TABLE 26-25: A/D CONVERTER CHARACTERISTICS: PIC18FXX20 (INDUSTRIAL, EXTENDED) PIC18LFXX20 (INDUSTRIAL) PIC18LFXX20 (INDUSTRIAL)

| Param<br>No. | Symbol | Characteristic                                    | Min                        | Тур      | Мах                        | Units    | Conditions                                                  |

|--------------|--------|---------------------------------------------------|----------------------------|----------|----------------------------|----------|-------------------------------------------------------------|

| A01          | NR     | Resolution                                        | —                          | _        | 10                         | bit      |                                                             |

| A03          | EIL    | Integral Linearity Error                          | —                          | _        | <±1                        | LSb      | Vref = Vdd = 5.0V                                           |

| A04          | Edl    | Differential Linearity Error                      | —                          | _        | <±1                        | LSb      | Vref = Vdd = 5.0V                                           |

| A05          | EG     | Gain Error                                        | —                          | _        | <±1                        | LSb      | Vref = Vdd = 5.0V                                           |

| A06          | EOFF   | Offset Error                                      | —                          | _        | <±1.5                      | LSb      | Vref = Vdd = 5.0V                                           |

| A10          | —      | Monotonicity                                      | gu                         | aranteed | j(2)                       |          | $VSS \leq VAIN \leq VREF$                                   |

| A20<br>A20A  | Vref   | Reference Voltage<br>(VREFH – VREFL)              | 1.8V<br>3V                 | _        |                            | V<br>V   | Vdd < 3.0V<br>Vdd ≥ 3.0V                                    |

| A21          | Vrefh  | Reference Voltage High                            | AVss                       | _        | AVDD + 0.3V                | V        |                                                             |

| A22          | Vrefl  | Reference Voltage Low                             | AVss - 0.3V <sup>(5)</sup> |          | Vrefh                      | V        |                                                             |

| A25          | VAIN   | Analog Input Voltage                              | AVss - 0.3V <sup>(5)</sup> |          | AVDD + 0.3V <sup>(5)</sup> | V        | VDD ≥ 2.5V (Note 3)                                         |

| A30          | ZAIN   | Recommended Impedance of<br>Analog Voltage Source | —                          | —        | 2.5                        | kΩ       | (Note 4)                                                    |

| A50          | IREF   | VREF Input Current (Note 1)                       | —                          | _        | 5<br>150                   | μΑ<br>μΑ | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

Note 1: Vss  $\leq$  Vain  $\leq$  Vref

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: For VDD < 2.5V, VAIN should be limited to <.5 VDD.

4: Maximum allowed impedance for analog voltage source is 10 kΩ. This requires higher acquisition times.

5: IVDD – AVDDI must be <3.0V and IAVSS – VSSI must be <0.3V.

### FIGURE 26-26: A/D CONVERSION TIMING

Note 1: If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

2: This is a minimal RC delay (typically 100 ns), which also disconnects the holding capacitor from the analog input.

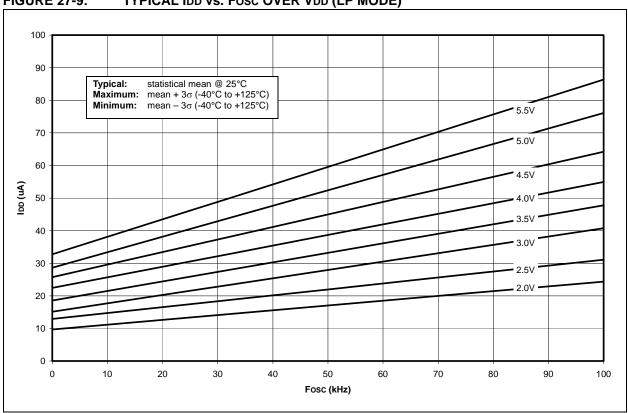

FIGURE 27-9: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

| with PLL)27                                          |

|------------------------------------------------------|

| Transition Between Timer1 and OSC1 (HS, XT, LP) . 26 |

| Transition Between Timer1 and OSC1 (RC, EC) 27       |

| Transition from OSC1 to Timer1 Oscillator            |

| USART Asynchronous Reception                         |

| USART Asynchronous Transmission                      |

| USART Asynchronous Transmission (Back to Back)       |

| 205                                                  |

| USART Synchronous Receive (Master/Slave) 337         |

| USART SynchronousTransmission (Master/Slave) . 337   |

| Wake-up from Sleep via Interrupt 253                 |

| TRISE Register                                       |

| PSPMODE Bit 111, 128                                 |

| TSTFSZ                                               |

| Two-Word Instructions                                |

| Example Cases 46                                     |

| TXSTA Register                                       |

| BRGH Bit                                             |

Universal Synchronous Asynchronous Receiver Transmitter.

## U

| See USART                                    |       |

|----------------------------------------------|-------|

| USART                                        |       |

| Asynchronous Mode                            |       |

| Associated Registers, Receive                | . 207 |

| Associated Registers, Transmit               |       |

| Receiver                                     |       |

| Setting up 9-bit Mode with Address Detect    | . 206 |

| Transmitter                                  |       |

| Baud Rate Generator (BRG)                    | . 200 |

| Associated Registers                         |       |

| Baud Rate Error, Calculating                 |       |

| Baud Rate Formula                            |       |

| Baud Rates for Asynchronous Mode (BRGH = 202 | :0).  |

| Baud Rates for Asynchronous Mode (BRGH = 203 | :1).  |

| Baud Rates for Synchronous Mode              | . 201 |

| High Baud Rate Select (BRGH Bit)             | . 200 |

| Sampling                                     | . 200 |

| Serial Port Enable (SPEN Bit)                | . 197 |

| Synchronous Master Mode                      | . 208 |

| Associated Registers, Reception              |       |

| Associated Registers, Transmit               |       |

| Reception                                    | .210  |

| Transmission                                 |       |

| Synchronous Slave Mode                       |       |

| Associated Registers, Receive                |       |

| Associated Registers, Transmit               |       |

| Reception                                    |       |

| Transmission                                 |       |

| USART Synchronous Receive Requirements       |       |

| USART Synchronous Transmission Requirements  | . 337 |

| V                                            |       |

| Voltage Reference Specifications             | . 315 |

| W                                            |       |

| Wake-up from Sleep239                        | , 252 |

| Using Interrupts                             |       |

| Watchdog Timer (WDT)239                      |       |

| Associated Registers                         |       |

| Control Register                             | . 250 |

| Postscaler                                   |       |

| Programming Considerations                   | . 250 |

| Time-out Period      | 250                  |

|----------------------|----------------------|

| WCOL                 | 185                  |

| WCOL Status Flag     | . 185, 186, 187, 190 |

| WDT Postscaler       | 250                  |

| WWW Address          | 375                  |

| WWW, On-Line Support | 5                    |

| х                    |                      |

| XORLW                | 299                  |

| XORWF                | 300                  |