Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Product Status             | Active                                                                    |  |  |  |  |

| Core Processor             | PIC                                                                       |  |  |  |  |

| Core Size                  | 8-Bit                                                                     |  |  |  |  |

| Speed                      | 25MHz                                                                     |  |  |  |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |  |  |  |  |

| Number of I/O              | 52                                                                        |  |  |  |  |

| Program Memory Size        | 128KB (64K x 16)                                                          |  |  |  |  |

| Program Memory Type        | FLASH                                                                     |  |  |  |  |

| EEPROM Size                | 1K x 8                                                                    |  |  |  |  |

| RAM Size                   | 3.75K x 8                                                                 |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |  |  |  |  |

| Data Converters            | A/D 12x10b                                                                |  |  |  |  |

| Oscillator Type            | External                                                                  |  |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |  |  |  |  |

| Mounting Type              | Surface Mount                                                             |  |  |  |  |

| Package / Case             | 64-TQFP                                                                   |  |  |  |  |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6720-i-pt |  |  |  |  |

|                            |                                                                           |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

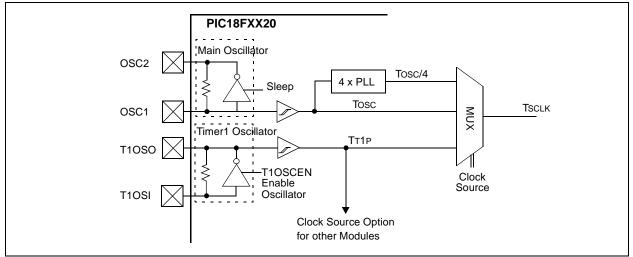

### 2.6 Oscillator Switching Feature

The PIC18FXX20 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low-frequency clock source. For the PIC18FXX20 devices, this alternate clock source is the Timer1 oscillator. If a low-frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a low-power execution mode. Figure 2-7 shows a block diagram of the system clock sources. The clock switching feature is enabled by programming the Oscillator Switching Enable (OSCSEN) bit in Configuration Register 1H to a '0'. Clock switching is disabled in an erased device. See Section 12.0 "Timer1 Module" for further details of the Timer1 oscillator. See Section 23.0 "Special Features of the CPU" for Configuration register details.

#### FIGURE 2-7: DEVICE CLOCK SOURCES

### 4.3 Fast Register Stack

A "fast interrupt return" option is available for interrupts. A Fast Register Stack is provided for the Status, WREG and BSR registers and is only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the FAST RETURN instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the Status, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a FAST CALL instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

#### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1            |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

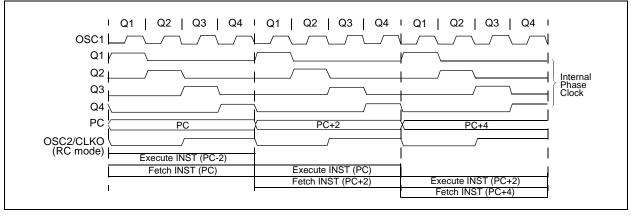

#### FIGURE 4-4: CLOCK/INSTRUCTION CYCLE

#### 4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide. The low byte is called the PCL register; this register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable; updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable; updates to the PCH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable; updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of the PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 4.8.1** "**Computed GOTO**").

### 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-4.

#### 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18FXX20 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to '1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to **Section 24.0 "Instruction Set Summary"** for further details of the instruction set.

| EXAMPLE 4-3: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

|              |                       |

| CASE   | 1:   |      |      |             |             |                                     |  |  |  |  |

|--------|------|------|------|-------------|-------------|-------------------------------------|--|--|--|--|

| Object | Code |      |      | Source Co   | Source Code |                                     |  |  |  |  |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ      | REG1        | ; is RAM location 0?                |  |  |  |  |

| 1100   | 0001 | 0010 | 0011 | MOVFF       | REG1, REG2  | ; No, execute 2-word instruction    |  |  |  |  |

| 1111   | 0100 | 0101 | 0110 |             |             | ; 2nd operand holds address of REG2 |  |  |  |  |

| 0010   | 0100 | 0000 | 0000 | ADDWF       | REG3        | ; continue code                     |  |  |  |  |

| CASE   | 2:   |      |      |             |             |                                     |  |  |  |  |

| Object | Code |      |      | Source Code |             |                                     |  |  |  |  |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ      | REG1        | ; is RAM location 0?                |  |  |  |  |

| 1100   | 0001 | 0010 | 0011 | MOVFF       | REG1, REG2  | ; Yes                               |  |  |  |  |

| 1111   | 0100 | 0101 | 0110 |             |             | ; 2nd operand becomes NOP           |  |  |  |  |

| 0010   | 0100 | 0000 | 0000 | ADDWF       | REG3        | ; continue code                     |  |  |  |  |

## 4.8 Look-up Tables

Look-up tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

#### 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

## 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Look-up table data may be stored 2 bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

A description of the table read/table write operation is shown in **Section 5.0 "Flash Program Memory"**.

#### 5.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 5.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the configuration bits.

The Table Pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways, based on the table operation. These operations are shown in Table 5-1. These operations on the TBLPTR only affect the low-order 21 bits.

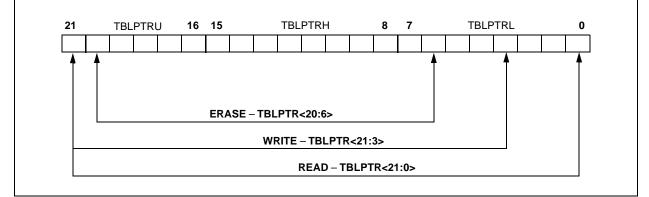

#### 5.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer, TBLPTR (TBLPTR<21:3>), will determine which program memory block of 8 bytes is written to. For more detail, see Section 5.5 "Writing to Flash Program Memory".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 5-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

#### FIGURE 5-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

#### 6.0 EXTERNAL MEMORY **INTERFACE**

| Note: | The            | External | Me | mory | Interface | is   | not   |

|-------|----------------|----------|----|------|-----------|------|-------|

|       | imple<br>devic |          | on | PIC1 | 8F6X20    | (64- | ·pin) |

The External Memory Interface is a feature of the PIC18F8X20 devices that allows the controller to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory.

The physical implementation of the interface uses 27 pins. These pins are reserved for external address/data bus functions; they are multiplexed with I/O port pins on four ports. Three I/O ports are multiplexed with the address/data bus, while the fourth port is multiplexed with the bus control signals. The I/O port functions are enabled when the EBDIS bit in the MEMCON register is set (see Register 6-1). A list of the multiplexed pins and their functions is provided in Table 6-1.

As implemented in the PIC18F8X20 devices, the interface operates in a similar manner to the external memory interface introduced on PIC18C601/801 microcontrollers. The most notable difference is that the interface on PIC18F8X20 devices only operates in 16-bit modes. The 8-bit mode is not supported.

For a more complete discussion of the operating modes that use the external memory interface, refer to Section 4.1.1 "PIC18F8X20 Program Memory Modes".

R/W-0

U-0

R/W-0

#### 6.1 **Program Memory Modes and the External Memory Interface**

As previously noted, PIC18F8X20 controllers are capable of operating in any one of four program memory modes, using combinations of on-chip and external program memory. The functions of the multiplexed port pins depend on the program memory mode selected, as well as the setting of the EBDIS bit.

In Microprocessor Mode, the external bus is always active and the port pins have only the external bus function.

In Microcontroller Mode, the bus is not active and the pins have their port functions only. Writes to the MEMCOM register are not permitted.

In Microprocessor with Boot Block or Extended Microcontroller Mode, the external program memory bus shares I/O port functions on the pins. When the device is fetching or doing table read/table write operations on the external program memory space, the pins will have the external bus function. If the device is fetching and accessing internal program memory locations only, the EBDIS control bit will change the pins from external memory to I/O port functions. When EBDIS = 0, the pins function as the external bus. When EBDIS = 1, the pins function as I/O ports.

Note: Maximum Fosc for the PIC18FX520 is limited to 25 MHz when using the external memory interface.

R/W-0

R/W-0

U-0

|         | EBDIS                                                                                                                                                                                                                                                   | —                                                                                                                                                                          | WAIT1   | WAIT0        | —           | —          | WM1          | WM0    |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-------------|------------|--------------|--------|--|

|         | bit7                                                                                                                                                                                                                                                    | L                                                                                                                                                                          | I       | 1            |             | I          |              | bit0   |  |

|         |                                                                                                                                                                                                                                                         |                                                                                                                                                                            |         |              |             |            |              |        |  |

| bit 7   | EBDIS: Ex                                                                                                                                                                                                                                               | EBDIS: External Bus Disable bit                                                                                                                                            |         |              |             |            |              |        |  |

|         |                                                                                                                                                                                                                                                         | <ul> <li>1 = External system bus disabled, all external bus drivers are mapped as I/O ports</li> <li>0 = External system bus enabled and I/O ports are disabled</li> </ul> |         |              |             |            |              |        |  |

| bit 6   | Unimplem                                                                                                                                                                                                                                                | Unimplemented: Read as '0'                                                                                                                                                 |         |              |             |            |              |        |  |

| bit 5-4 | WAIT<1:0>: Table Reads and Writes Bus Cycle Wait Count bits<br>11 = Table reads and writes will wait 0 TcY<br>10 = Table reads and writes will wait 1 TcY<br>01 = Table reads and writes will wait 2 TcY<br>00 = Table reads and writes will wait 3 TcY |                                                                                                                                                                            |         |              |             |            |              |        |  |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                              |                                                                                                                                                                            |         |              |             |            |              |        |  |

| bit 1-0 | WM<1:0>: TBLWRT Operation with 16-bit Bus bits                                                                                                                                                                                                          |                                                                                                                                                                            |         |              |             |            |              |        |  |

|         | <ul> <li>1x = Word Write mode: TABLAT&lt;0&gt; and TABLAT&lt;1&gt; word output, WRH active when TABLAT&lt;1&gt; written</li> <li>01 = Byte Select mode: TABLAT data copied on both MSB and LSB, WRH and (UB or LB) will activate</li> </ul>             |                                                                                                                                                                            |         |              |             |            |              |        |  |

|         | 00 = Byte Write mode: TABLAT data copied on both MSB and LSB, WRH or WRL will activate                                                                                                                                                                  |                                                                                                                                                                            |         |              |             |            |              |        |  |

|         | Legend:                                                                                                                                                                                                                                                 |                                                                                                                                                                            |         |              |             |            |              |        |  |

|         | R = Reada                                                                                                                                                                                                                                               | ble bit                                                                                                                                                                    | W = W   | /ritable bit | U = Unim    | nplemented | bit, read as | '0'    |  |

|         | - n = Value                                                                                                                                                                                                                                             | at POR                                                                                                                                                                     | '1' = B | it is set    | '0' = Bit i | s cleared  | x = Bit is u | nknown |  |

R/W-0

U-0

#### **REGISTER 6-1:** MEMCON REGISTER

| REGISTER 7-1: | EECON1 F                                                                                                                                                                                                                                                                                                                 | REGISTER                      | (ADDRES                                 | S FA6h)       |                              |           |             |        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|---------------|------------------------------|-----------|-------------|--------|

|               | R/W-x                                                                                                                                                                                                                                                                                                                    | R/W-x                         | U-0                                     | R/W-0         | R/W-x                        | R/W-0     | R/S-0       | R/S-0  |

|               | EEPGD                                                                                                                                                                                                                                                                                                                    | CFGS                          |                                         | FREE          | WRERR                        | WREN      | WR          | RD     |

|               | bit 7                                                                                                                                                                                                                                                                                                                    |                               |                                         |               |                              |           |             | bit 0  |

|               |                                                                                                                                                                                                                                                                                                                          |                               |                                         |               |                              |           |             |        |

| bit 7         |                                                                                                                                                                                                                                                                                                                          | -                             |                                         |               | ry Select bit                |           |             |        |

|               |                                                                                                                                                                                                                                                                                                                          | s Flash prog<br>s data EEPR   |                                         |               |                              |           |             |        |

| bit 6         |                                                                                                                                                                                                                                                                                                                          | •                             |                                         |               | guration Sel                 | lect bit  |             |        |

|               |                                                                                                                                                                                                                                                                                                                          | s configurati<br>s Flash prog |                                         |               |                              |           |             |        |

| bit 5         | Unimplem                                                                                                                                                                                                                                                                                                                 | ented: Read                   | <b>as</b> '0'                           |               |                              |           |             |        |

| bit 4         |                                                                                                                                                                                                                                                                                                                          | sh Row Eras                   |                                         |               |                              |           |             |        |

|               | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul>                                                                                                                                           |                               |                                         |               |                              |           | hand        |        |

| bit 3         | WRERR: Flash Program/Data EEPROM Error Flag bit                                                                                                                                                                                                                                                                          |                               |                                         |               |                              |           |             |        |

|               | <ul> <li>1 = A write operation is prematurely terminated<br/>(any MCLR or any WDT Reset during self-timed programming in normal operation)</li> <li>0 = The write operation completed</li> </ul>                                                                                                                         |                               |                                         |               |                              |           |             | ation) |

|               | <b>Note:</b> When a WRERR occurs, the EEPGD or FREE bits are not cleared. This allows tracing of the error condition.                                                                                                                                                                                                    |                               |                                         |               |                              |           |             |        |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                                | ish Program                   | /Data EEPR                              | OM Write E    | nable bit                    |           |             |        |

|               |                                                                                                                                                                                                                                                                                                                          | write cycles<br>write cycles  | •                                       | •             |                              |           |             |        |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                                | Control bit                   |                                         |               |                              |           |             |        |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle, or a program memory erase cycle or write cycle.<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                               |                                         |               |                              |           |             |        |

| bit 0         | RD: Read                                                                                                                                                                                                                                                                                                                 | Control bit                   |                                         |               |                              |           |             |        |

|               | can on                                                                                                                                                                                                                                                                                                                   |                               | ot cleared) ir                          | n software. F | ne cycle. RD<br>RD bit canno |           |             |        |

|               |                                                                                                                                                                                                                                                                                                                          |                               |                                         |               |                              |           |             |        |

|               | Legend:                                                                                                                                                                                                                                                                                                                  |                               |                                         |               |                              |           |             |        |

|               | P - Roodo                                                                                                                                                                                                                                                                                                                | hla hit                       | $\lambda \Lambda I = \lambda \Lambda I$ | ritable bit   |                              | nlomontod | hit road as | ·^'    |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

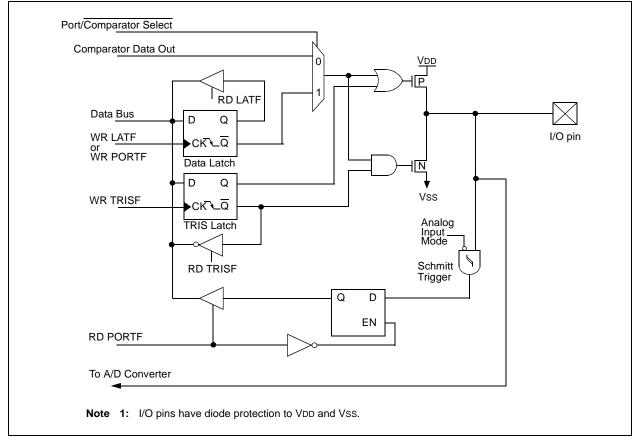

### 10.6 PORTF, LATF and TRISF Registers

PORTF is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISF. Setting a TRISF bit (= 1) will make the corresponding PORTF pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISF bit (= 0) will make the corresponding PORTF pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATF register, read and write the latched output value for PORTF.

PORTF is multiplexed with several analog peripheral functions, including the A/D converter inputs and comparator inputs, outputs and voltage reference.

- Note 1: On a Power-on Reset, the RF6:RF0 pins are configured as inputs and read as '0'.

- **2:** To configure PORTF as digital I/O, turn off comparators and set ADCON1 value.

#### EXAMPLE 10-6: INITIALIZING PORTF

| CLRF  | PORTF  | ; Initialize PORTF by      |

|-------|--------|----------------------------|

|       |        | ; clearing output          |

|       |        | ; data latches             |

| CLRF  | LATF   | ; Alternate method         |

|       |        | ; to clear output          |

|       |        | ; data latches             |

| MOVLW | 0x07   | ;                          |

| MOVWF | CMCON  | ; Turn off comparators     |

| MOVLW | 0x0F   | i                          |

| MOVWF | ADCON1 | ; Set PORTF as digital I/O |

| MOVLW | 0xCF   | ; Value used to            |

|       |        | ; initialize data          |

|       |        | ; direction                |

| MOVWF | TRISF  | ; Set RF3:RF0 as inputs    |

|       |        | ; RF5:RF4 as outputs       |

|       |        | ; RF7:RF6 as inputs        |

|       |        |                            |

### FIGURE 10-13: PORTF RF1/AN6/C2OUT, RF2/AN7/C1OUT PINS BLOCK DIAGRAM

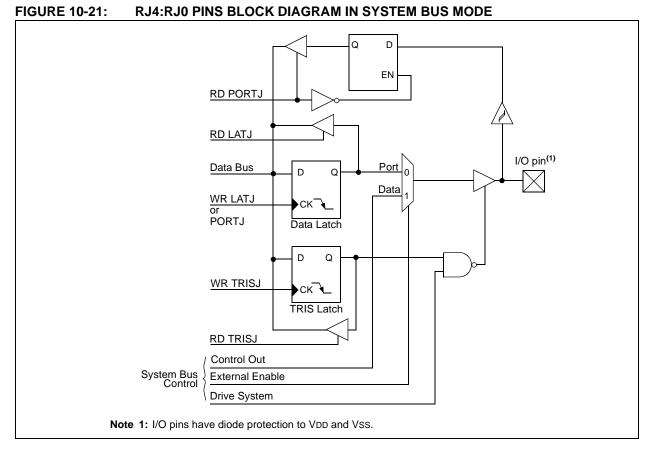

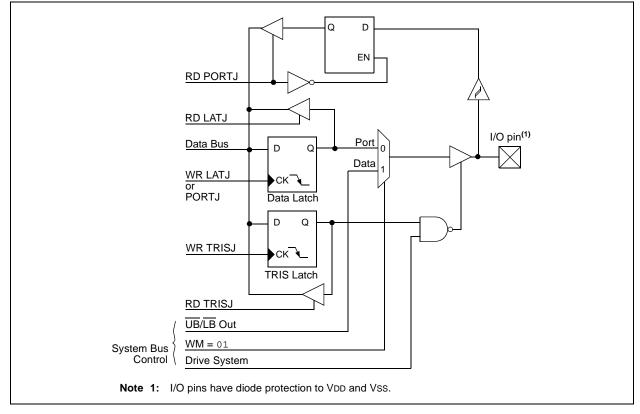

#### FIGURE 10-22: RJ7:RJ6 PINS BLOCK DIAGRAM IN SYSTEM BUS MODE

| Name    | Bit#  | Buffer Type | Function                                                                             |

|---------|-------|-------------|--------------------------------------------------------------------------------------|

| RJ0/ALE | bit 0 | ST          | Input/output port pin or address latch enable control for external memory interface. |

| RJ1/OE  | bit 1 | ST          | Input/output port pin or output enable control for external memory interface.        |

| RJ2/WRL | bit 2 | ST          | Input/output port pin or write low byte control for external memory interface.       |

| RJ3/WRH | bit 3 | ST          | Input/output port pin or write high byte control for external memory interface.      |

| RJ4/BA0 | bit 4 | ST          | Input/output port pin or byte address 0 control for external memory interface.       |

| RJ5/CE  | bit 5 | ST          | Input/output port pin or chip enable control for external memory interface.          |

| RJ6/LB  | bit 6 | ST          | Input/output port pin or lower byte select control for external memory interface.    |

| RJ7/UB  | bit 7 | ST          | Input/output port pin or upper byte select control for external memory interface.    |

#### TABLE 10-17: PORTJ FUNCTIONS

**Legend:** ST = Schmitt Trigger input

#### TABLE 10-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name  | Bit 7                                 | Bit 6     | Bit 5      | Bit 4      | Bit 3     | Bit 2     | Bit 1     | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|---------------------------------------|-----------|------------|------------|-----------|-----------|-----------|-------|----------------------|---------------------------------|

| PORTJ | Read PORTJ pin/Write PORTJ Data Latch |           |            |            |           | xxxx xxxx | uuuu uuuu |       |                      |                                 |

| LATJ  | LATJ Data Output Register             |           |            |            | xxxx xxxx | uuuu uuuu |           |       |                      |                                 |

| TRISJ | Data Dir                              | ection Co | ntrol Regi | ster for P | ORTJ      |           |           |       | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

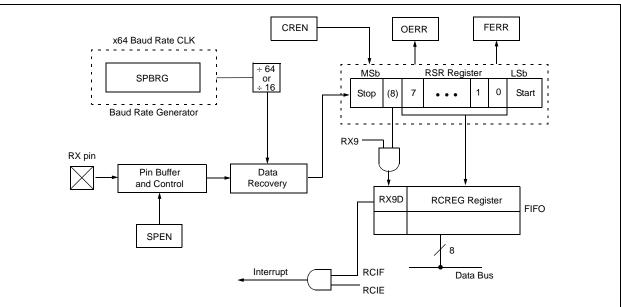

#### 18.2.2 USART ASYNCHRONOUS RECEIVER

The USART receiver block diagram is shown in Figure 18-4. The data is received on the pin (RC7/RX1/DT1 or RG2/RX2/DT2) and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 18.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCxIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit RCxIF will be set when reception is complete and an interrupt will be generated if enable bit RCxIE was set.

- 7. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### 18.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGx register for the appropriate baud rate. If a high-speed baud rate is required, set the BRGH bit.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### FIGURE 18-4: USART RECEIVE BLOCK DIAGRAM

### 20.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM<2:0> = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 20.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered down during the Reset interval.

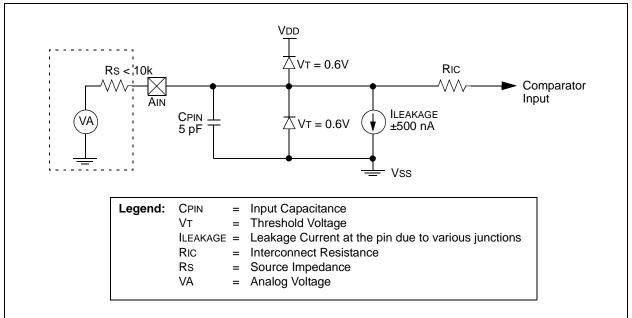

### 20.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 20-4: COMPARATOR ANALOG INPUT MODEL

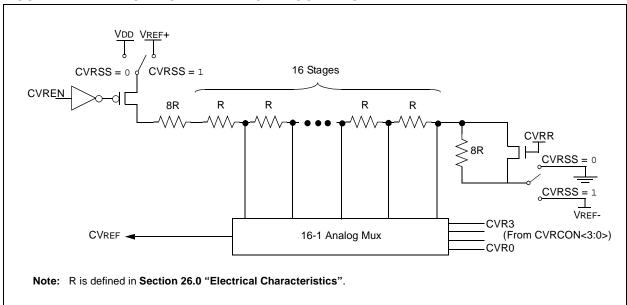

#### FIGURE 21-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### 21.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 21-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

### 21.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 21.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit CVRR (CVRCON<5>). The VRSS value select bits, CVRCON<3:0>, are also cleared.

#### 21.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RF5 pin if the TRISF<5> bit is set and the CVROE bit is set. Enabling the voltage reference output onto the RF5 pin, configured as a digital input, will increase current consumption. Connecting RF5 as a digital output with VRSS enabled will also increase current consumption.

The RF5 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 21-2 shows an example buffering technique.

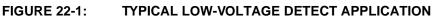

## 22.0 LOW-VOLTAGE DETECT

In many applications, the ability to determine if the device voltage (VDD) is below a specified voltage level is a desirable feature. A window of operation for the application can be created, where the application software can do "housekeeping tasks" before the device voltage exits the valid operating range. This can be done using the Low-Voltage Detect module.

This module is a software programmable circuitry, where a device voltage trip point can be specified. When the voltage of the device becomes lower then the specified point, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to that interrupt source. The Low-Voltage Detect circuitry is completely under software control. This allows the circuitry to be "turned off" by the software, which minimizes the current consumption for the device.

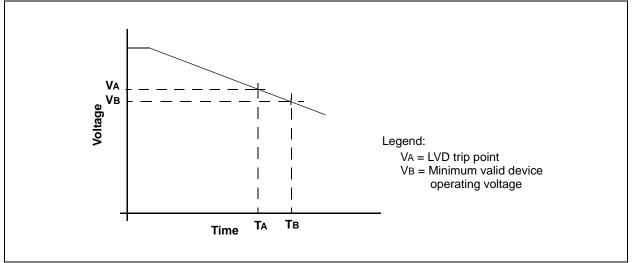

Figure 22-1 shows a possible application voltage curve (typically for batteries). Over time, the device voltage decreases. When the device voltage equals voltage VA, the LVD logic generates an interrupt. This occurs at time TA. The application software then has the time, until the device voltage is no longer in valid operating range, to shut down the system. Voltage point VB is the minimum valid operating voltage specification. This occurs at time TB. The difference TB – TA is the total time for shutdown.

The block diagram for the LVD module is shown in Figure 22-2. A comparator uses an internally generated reference voltage as the set point. When the selected tap output of the device voltage crosses the set point (is lower than), the LVDIF bit is set.

Each node in the resistor divider represents a "trip point" voltage. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the 1.2V internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal, setting the LVDIF bit. This voltage is software programmable to any one of 16 values (see Figure 22-2). The trip point is selected by programming the LVDL3:LVDL0 bits (LVDCON<3:0>).

| Syntax:[ label ]CPFSGTf [,a]Operands: $0 \le f \le 255$<br>$a \in [0,1]$ Operation:(f) - (W),<br>skip if (f) > (W)<br>(unsigned comparison)Status Affected:NoneEncoding: $0110$ $010a$ ffffDescription:Compares the contents of data<br>memory location f' to the contents<br>of W by performing an unsigned<br>subtraction.If the contents of 'f are greater than<br>the contents of 'f are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).Words:1Cycles:1(2)<br>Note:Note:3 cycles if skip and followed<br>by a 2-word instruction.Q Cycle Activity:Q1Q1Q2Q3Q4NoNoNo<br>operationIf skip:Q1Q2Q1Q2Q3Q4NoNo<br>operationNoNoNo<br>operationIf skip and followed by 2-word instruction:Q1Q2Q3Q4NoNo<br>operationNoNo<br>operationNo<br>operationMoNo<br>operationNo<br>operationMoNo<br>operationNo<br>operationMoNo<br>operationNo<br>operationMoNo<br>operationNo<br>operationMoNo<br>operationNo<br>operationPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CPF         | SGT            | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                 | f with W, s   | kip if f > W |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--|--|--|--|--|

| $a \in [0,1]$ Operation: (f) – (W), skip if (f) > (W) (unsigned comparison) Status Affected: None Encoding: 0110 010a ffff ffff Description: Compares the contents of data memory location 'f' to the contents of W by performing an unsigned subtraction. If the contents of 'f' are greater than the contents of WREG, then the fetched instruction is discarded and a NOP is executed instead, making this a two-cycle instruction. If 'a' is 'o', the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the BSR value (default). Words: 1 Cycles: 1(2) Note: 3 cycles if skip and followed by a 2-word instruction. Q Cycle Activity: Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synt        | ax:            | [label] C                                                                                                                                                                                                                                                                                                                                                                                                                               | CPFSGT f      | [,a]         |  |  |  |  |  |

| skip if (f) > (W)<br>(unsigned comparison)<br>Status Affected: None<br>Encoding: 0110 010a ffff ffff<br>Description: Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).<br>Words: 1<br>Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.<br>Q Cycle Activity:<br>Q1 Q2 Q3 Q4<br>Decode Read Process No<br>operation operation<br>If skip:<br>Q1 Q2 Q3 Q4<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Ope         | rands:         |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5             |              |  |  |  |  |  |

| Encoding:0110010affffffffDescription:Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of WEG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).Words:1Cycles:1(2)<br>Note:Q1Q2Q3Q4Decode<br>register 'f'DecodeRead<br>register 'f'DataoperationIf skip:Q1Q2Q3Q4DecodeRead<br>register 'f'DataoperationIf skip and followed by 2-word instruction:Q1Q2Q3Q4Q4NoNo<br>operationIf skip and followed by 2-word instruction:Q1Q2Q3Q4Q4No<br>operationNo<br>operationIf skip and followed by 2-word instruction:Q1Q2Q3Q4Q4No<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operationNo<br>operation <td>Ope</td> <td>ration:</td> <td>skip if (f) &gt;</td> <td></td> <td>۱)</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ope         | ration:        | skip if (f) >                                                                                                                                                                                                                                                                                                                                                                                                                           |               | ۱)           |  |  |  |  |  |

| Description:<br>Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default).<br>Words: 1<br>Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.<br>Q Cycle Activity:<br>Q1<br>Q2<br>Q3<br>Q4<br>Decode<br>Read<br>register 'f'<br>Data<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>operation<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Statu       | us Affected:   | None                                                                                                                                                                                                                                                                                                                                                                                                                                    | None          |              |  |  |  |  |  |

| $\begin{array}{rcl} & \mbox{memory location 'f' to the contents} \\ & \mbox{of W by performing an unsigned} \\ & \mbox{subtraction.} \\ & \mbox{If the contents of 'f' are greater than} \\ & \mbox{the contents of WREG, then the} \\ & \mbox{fetched instruction is discarded and} \\ & \mbox{a NOP is executed instead, making} \\ & \mbox{this a two-cycle instruction. If 'a' is} \\ & \mbox{'o', the Access Bank will be} \\ & \mbox{selected, overriding the BSR value.} \\ & \mbox{If 'a' = 1, then the bank will be} \\ & \mbox{selected as per the BSR value} \\ & \mbox{(default).} \\ \\ \hline & \mbox{Vords: 1} \\ \hline \\ & \mbox{Cycle Activity:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{Read } \mbox{Process } \mbox{No} \\ & \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{Read } \mbox{Process } \mbox{No} \\ & \mbox{operation} \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{Decode } \mbox{No } \mbox{No } \mbox{No} \\ & \mbox{operation} \mbox{operation} \mbox{operation} \mbox{operation} \mbox{operation} \\ \hline \\ & \mbox{If skip and followed by 2-word instruction:} \\ \hline \\ & \mbox{Q 1 } \mbox{Q 2 } \mbox{Q 3 } \mbox{Q 4} \\ \hline \\ & \mbox{No } \mbox{No } \mbox{No } \mbox{No} \mbox{operation} \mb$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Enco        | oding:         | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                    | 010a fi       | ff ffff      |  |  |  |  |  |

| $(default).$ Words: 1 Cycles: 1(2) Note: 3 cycles if skip and followed by a 2-word instruction. Q Cycle Activity: $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Des         | cription:      | Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If the contents of 'f' are greater than<br>the contents of WREG, then the<br>fetched instruction is discarded and<br>a NOP is executed instead, making<br>this a two-cycle instruction. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be |               |              |  |  |  |  |  |

| Cycles:1(2)Note:3 cycles if skip and followed<br>by a 2-word instruction.Q Cycle Activity: $Q1$ Q1Q2Q3Q4DecodeRead<br>register 'f'DataoperationIf skip: $Q1$ Q1Q2Q3Q4NoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNoNo </td <td>10/</td> <td>da .</td> <td></td> <td>·</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10/         | da .           |                                                                                                                                                                                                                                                                                                                                                                                                                                         | ·             |              |  |  |  |  |  |