Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6720t-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

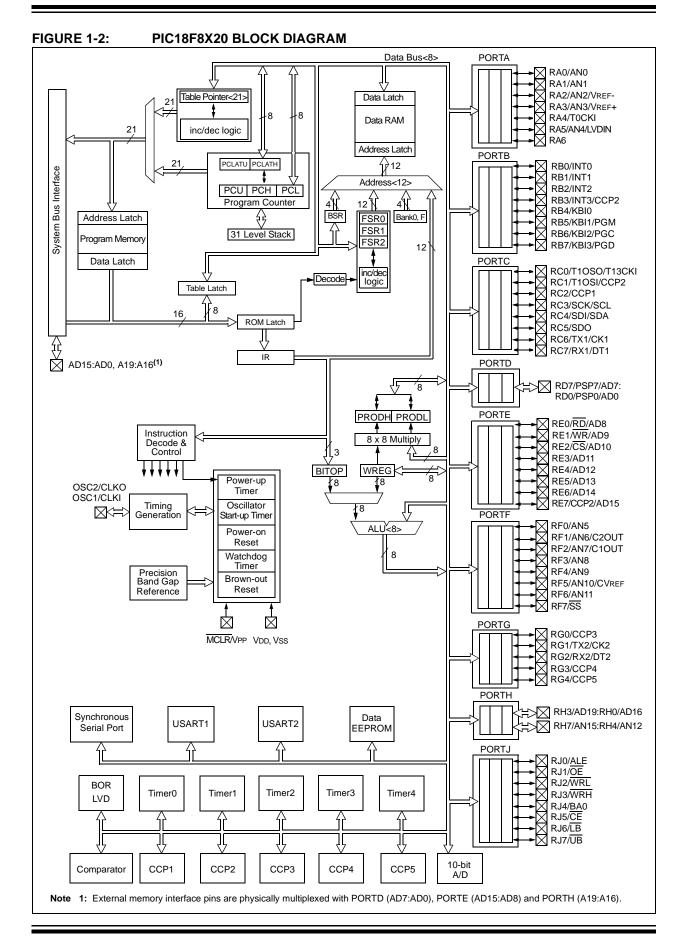

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F6520 PIC18F8520

- PIC18F6620 PIC18F8620

- PIC18F6720 PIC18F8720

This family offers the same advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high endurance Enhanced Flash program memory. The PIC18FXX20 family also provides an enhanced range of program memory options and versatile analog features that make it ideal for complex, high-performance applications.

#### 1.1 Key Features

#### 1.1.1 EXPANDED MEMORY

The PIC18FXX20 family introduces the widest range of on-chip, Enhanced Flash program memory available on PIC<sup>®</sup> microcontrollers – up to 128 Kbyte (or 65,536 words), the largest ever offered by Microchip. For users with more modest code requirements, the family also includes members with 32 Kbyte or 64 Kbyte.

Other memory features are:

- Data RAM and Data EEPROM: The PIC18FXX20 family also provides plenty of room for application data. Depending on the device, either 2048 or 3840 bytes of data RAM are available. All devices have 1024 bytes of data EEPROM for long-term retention of nonvolatile data.

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

#### 1.1.2 EXTERNAL MEMORY INTERFACE

In the event that 128 Kbytes of program memory is inadequate for an application, the PIC18F8X20 members of the family also implement an External Memory Interface. This allows the controller's internal program counter to address a memory space of up to 2 Mbytes, permitting a level of data access that few 8-bit devices can claim. With the addition of new operating modes, the External Memory Interface offers many new options, including:

- Operating the microcontroller entirely from external memory

- Using combinations of on-chip and external memory, up to the 2-Mbyte limit

- Using external Flash memory for reprogrammable application code, or large data tables

- Using external RAM devices for storing large amounts of variable data

#### 1.1.3 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

#### 1.1.4 OTHER SPECIAL FEATURES

- **Communications:** The PIC18FXX20 family incorporates a range of serial communications peripherals, including 2 independent USARTs and a Master SSP module, capable of both SPI and I<sup>2</sup>C (Master and Slave) modes of operation. For PIC18F8X20 devices, one of the general purpose I/O ports can be reconfigured as an 8-bit Parallel Slave Port for direct processor-to-processor communications.

- **CCP Modules:** All devices in the family incorporate five Capture/Compare/PWM modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once.

- Analog Features: All devices in the family feature 10-bit A/D converters, with up to 16 input channels, as well as the ability to perform conversions during Sleep mode. Also included are dual analog comparators with programmable input and output configuration, a programmable Low-Voltage Detect module and a programmable Brown-out Reset module.

- Self-programmability: These devices can write to their own program memory spaces under internal software control. By using a bootloader routine located in the protected Boot Block at the top of program memory, it becomes possible to create an application that can update itself in the field.

### TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

|      | Ranges Tested: |          |          |  |  |  |  |  |  |  |  |  |

|------|----------------|----------|----------|--|--|--|--|--|--|--|--|--|

| Mode | Freq           | C1       | C2       |  |  |  |  |  |  |  |  |  |

| LP   | 32 kHz         | 15-22 pF | 15-22 nE |  |  |  |  |  |  |  |  |  |

|      | 200 kHz        | 10-22 pi | 15-22 pF |  |  |  |  |  |  |  |  |  |

| XT   | 1 MHz          | 15-22 pF | 15-22 pF |  |  |  |  |  |  |  |  |  |

|      | 4 MHz          | 13-22 pr | 10-22 pr |  |  |  |  |  |  |  |  |  |

| HS   | 4 MHz          |          |          |  |  |  |  |  |  |  |  |  |

|      | 8 MHz          | 15-22 pF | 15-22 pF |  |  |  |  |  |  |  |  |  |

|      | 20 MHz         |          |          |  |  |  |  |  |  |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the above crystal frequencies for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- **Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components, or verify oscillator performance.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- 5: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

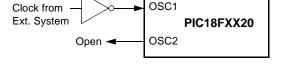

An external clock source may also be connected to the OSC1 pin in the HS, XT and LP modes, as shown in Figure 2-2.

### FIGURE 2-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LPOSC CONFIGURATION)

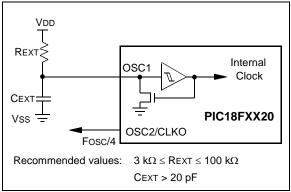

### 2.3 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit, due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-3 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

#### FIGURE 2-3: RC OSCILLATOR MODE

The RCIO Oscillator mode functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

#### TABLE 4-2: SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                   | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|------------------------|---------|---------|---------|-----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(3)</sup>   | FBFh    | CCPR1H  | F9Fh    | IPR1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2(3)            | FBEh    | CCPR1L  | F9Eh    | PIR1                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(3)            | FBDh    | CCP1CON | F9Dh    | PIE1                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(3)</sup> | FBCh    | CCPR2H  | F9Ch    | MEMCON <sup>(2)</sup> |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(3)</sup>  | FBBh    | CCPR2L  | F9Bh    | (1)                   |

| FFAh    | PCLATH                  | FDAh    | FSR2H                  | FBAh    | CCP2CON | F9Ah    | TRISJ                 |

| FF9h    | PCL                     | FD9h    | FSR2L                  | FB9h    | CCPR3H  | F99h    | TRISH                 |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                 | FB8h    | CCPR3L  | F98h    | TRISG                 |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                  | FB7h    | CCP3CON | F97h    | TRISF                 |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                  | FB6h    | (1)     | F96h    | TRISE                 |

| FF5h    | TABLAT                  | FD5h    | T0CON                  | FB5h    | CVRCON  | F95h    | TRISD                 |

| FF4h    | PRODH                   | FD4h    | (1)                    | FB4h    | CMCON   | F94h    | TRISC                 |

| FF3h    | PRODL                   | FD3h    | OSCCON                 | FB3h    | TMR3H   | F93h    | TRISB                 |

| FF2h    | INTCON                  | FD2h    | LVDCON                 | FB2h    | TMR3L   | F92h    | TRISA                 |

| FF1h    | INTCON2                 | FD1h    | WDTCON                 | FB1h    | T3CON   | F91h    | LATJ                  |

| FF0h    | INTCON3                 | FD0h    | RCON                   | FB0h    | PSPCON  | F90h    | LATH                  |

| FEFh    | INDF0 <sup>(3)</sup>    | FCFh    | TMR1H                  | FAFh    | SPBRG1  | F8Fh    | LATG                  |

| FEEh    | POSTINC0 <sup>(3)</sup> | FCEh    | TMR1L                  | FAEh    | RCREG1  | F8Eh    | LATF                  |

| FEDh    | POSTDEC0 <sup>(3)</sup> | FCDh    | T1CON                  | FADh    | TXREG1  | F8Dh    | LATE                  |

| FECh    | PREINC0 <sup>(3)</sup>  | FCCh    | TMR2                   | FACh    | TXSTA1  | F8Ch    | LATD                  |

| FEBh    | PLUSW0 <sup>(3)</sup>   | FCBh    | PR2                    | FABh    | RCSTA1  | F8Bh    | LATC                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                  | FAAh    | EEADRH  | F8Ah    | LATB                  |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                 | FA9h    | EEADR   | F89h    | LATA                  |

| FE8h    | WREG                    | FC8h    | SSPADD                 | FA8h    | EEDATA  | F88h    | PORTJ                 |

| FE7h    | INDF1 <sup>(3)</sup>    | FC7h    | SSPSTAT                | FA7h    | EECON2  | F87h    | PORTH                 |

| FE6h    | POSTINC1 <sup>(3)</sup> | FC6h    | SSPCON1                | FA6h    | EECON1  | F86h    | PORTG                 |

| FE5h    | POSTDEC1 <sup>(3)</sup> | FC5h    | SSPCON2                | FA5h    | IPR3    | F85h    | PORTF                 |

| FE4h    | PREINC1 <sup>(3)</sup>  | FC4h    | ADRESH                 | FA4h    | PIR3    | F84h    | PORTE                 |

| FE3h    | PLUSW1 <sup>(3)</sup>   | FC3h    | ADRESL                 | FA3h    | PIE3    | F83h    | PORTD                 |

| FE2h    | FSR1H                   | FC2h    | ADCON0                 | FA2h    | IPR2    | F82h    | PORTC                 |

| FE1h    | FSR1L                   | FC1h    | ADCON1                 | FA1h    | PIR2    | F81h    | PORTB                 |

| FE0h    | BSR                     | FC0h    | ADCON2                 | FA0h    | PIE2    | F80h    | PORTA                 |

Note 1: Unimplemented registers are read as '0'.

2: This register is unused on PIC18F6X20 devices. Always maintain this register clear.

**3:** This is not a physical register.

#### 7.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADRH:EEADR register pair, clear the EEPGD control bit (EECON1<7>), clear the CFGS

EXAMPLE 7-1: DATA EEPROM READ

control bit (EECON1<6>) and then set the RD control bit (EECON1<0>). The data is available for the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

|   | MOVLW | DATA_EE_ADDRH |                              |               |

|---|-------|---------------|------------------------------|---------------|

|   | MOVWF | EEADRH        | Jpper bits of Data Memory Ad | dress to read |

|   | MOVLW | DATA_EE_ADDR  |                              |               |

|   | MOVWF | EEADR         | Lower bits of Data Memory Ad | dress to read |

|   | BCF   | EECON1, EEPGD | Point to DATA memory         |               |

|   | BCF   | EECON1, CFGS  | Access EEPROM                |               |

|   | BSF   | EECON1, RD    | EEPROM Read                  |               |

|   | MOVF  | EEDATA, W     | N = EEDATA                   |               |

| I |       |               |                              |               |

#### 7.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADRH:EEADR register pair and the data written to the EEDATA register. Then the sequence in Example 7-2 must be followed to initiate the write cycle.

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, EECON1, EEADRH, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Write Complete Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | ;                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EEPGD | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | i                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | AAh           | ;                                             |

|          | MOVWF | EECON2        | ; Write AAh                                   |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

|          |       |               |                                               |

EXAMPLE 7-2: DATA EEPROM WRITE

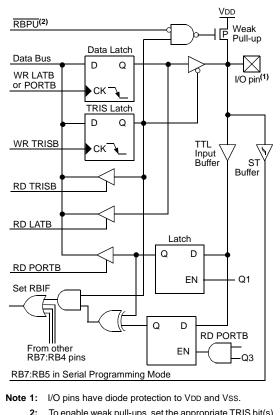

#### 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register, read and write the latched output value for PORTB.

#### **EXAMPLE 10-2:** INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATB  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0xCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISB | ; Set RB<3:0> as inputs |

|       |       | ; RB<5:4> as outputs    |

|       |       | ; RB<7:6> as inputs     |

|       |       | , 1                     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

On a Power-on Reset, these pins are Note: configured as digital inputs.

Four of the PORTB pins (RB3:RB0) are the external interrupt pins, INT3 through INT0. In order to use these pins as external interrupts, the corresponding TRISB bit must be set to '1'.

The other four PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- Clear flag bit RBIF. b)

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB3 can be configured by the configuration bit CCP2MX, as the alternate peripheral pin for the CCP2 module. This is only available when the device is configured in Microprocessor, Microprocessor with Boot Block, or Extended Microcontroller operating modes.

The RB5 pin is used as the LVP programming pin. When the LVP configuration bit is programmed, this pin loses the I/O function and become a programming test function.

Note: When LVP is enabled, the weak pull-up on RB5 is disabled.

#### **FIGURE 10-5: BLOCK DIAGRAM OF RB7:RB4 PINS**

<sup>2:</sup> To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (INTCON2<7>).

NOTES:

#### 14.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a lowpower oscillator rated up to 200 kHz. See **Section 12.0 "Timer1 Module"** for further details.

#### 14.3 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 14.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3.

| Note: | The special event triggers from the CO | СР   |

|-------|----------------------------------------|------|

|       | module will not set interrupt flag t   | oit, |

|       | TMR3IF (PIR1<0>).                      |      |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this Reset operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer3.

| Name   | Bit 7      | Bit 6          | Bit 5      | Bit 4          | Bit 3         | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------|----------------|------------|----------------|---------------|----------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH   | PEIE/GIEL      | TMR0IE     | INT0IE         | RBIE          | TMR0IF   | INT0IF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR2   | —          | _              | _          | EEIF           | BCLIF         | LVDIF    | TMR3IF | CCP2IF | 0 0000               | 0 0000                          |

| PIE2   | —          | _              | _          | EEIE           | BCLIE         | LVDIE    | TMR3IE | CCP2IE | 0 0000               | 0 0000                          |

| IPR2   | —          | —              | _          | EEIP           | BCLIP         | LVDIP    | TMR3IP | CCP2IP | 1 1111               | 1 1111                          |

| TMR3L  | Holding Re | gister for the | Least Sign | ificant Byte   | of the 16-bit | TMR3 Re  | gister |        | xxxx xxxx            | uuuu uuuu                       |

| TMR3H  | Holding Re | gister for the | Most Signi | ficant Byte of | of the 16-bit | TMR3 Reg | gister |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16       | _              | T1CKPS1    | T1CKPS0        | T1OSCEN       | T1SYNC   | TMR1CS | TMR1ON | 0-00 0000            | u-uu uuuu                       |

| T3CON  | RD16       | T3CCP2         | T3CKPS1    | T3CKPS0        | T3CCP1        | T3SYNC   | TMR3CS | TMR3ON | 0000 0000            | uuuu uuuu                       |

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### EQUATION 16-3:

PWM Resolution (max) =  $\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 16.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 16-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

bits

| PWM Frequency              | 2.44 kHz            | 9.77 kHz            | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|---------------------|---------------------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16                  | 4                   | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh                 | FFh                 | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | $14 \rightarrow 10$ | $12 \rightarrow 10$ | 10        | 8          | 7          | 6.58       |

#### TABLE 16-4: REGISTERS ASSOCIATED WITH PWM, TIMER2 AND TIMER4

| Name                   | Bit 7                                                        | Bit 6                               | Bit 5     | Bit 4     | Bit 3    | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------------------------------------------------------------|-------------------------------------|-----------|-----------|----------|--------|---------|-----------|----------------------|---------------------------------|

| INTCON                 | GIE/GIEH                                                     | PEIE/GIEL                           | TMR0IE    | INT0IE    | RBIE     | TMR0IF | INT0IF  | RBIF      | 0000 0000            | 0000 0000                       |

| RCON                   | IPEN                                                         | _                                   | _         | RI        | TO       | PD     | POR     | BOR       | 01 11qq              | 0q qquu                         |

| PIR1                   | PSPIF                                                        | ADIF                                | RCIF      | TXIF      | SSPIF    | CCP1IF | TMR2IF  | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1                   | PSPIE                                                        | ADIE                                | RCIE      | TXIE      | SSPIE    | CCP1IE | TMR2IE  | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1                   | PSPIP                                                        | ADIP                                | RCIP      | TXIP      | SSPIP    | CCP1IP | TMR2IP  | TMR1IP    | 0111 1111            | 0111 1111                       |

| PIR2                   | _                                                            | CMIE                                |           | EEIE      | BCLIF    | LVDIF  | TMR3IF  | CCP2IF    | -0-0 0000            | 0 0000                          |

| PIE2                   | _                                                            | CMIF                                |           | EEIF      | BCLIE    | LVDIE  | TMR3IE  | CCP2IE    | -0-0 0000            | 0 0000                          |

| IPR2                   | _                                                            | CMIP                                |           | EEIP      | BCLIP    | LVDIP  | TMR3IP  | CCP2IP    | -1-1 1111            | 1 1111                          |

| PIR3                   | _                                                            | _                                   | RC2IF     | TX2IF     | TMR4IF   | CCP5IF | CCP4IF  | CCP3IF    | 00 0000              | 00 0000                         |

| PIE3                   |                                                              | _                                   | RC2IE     | TX2IE     | TMR4IE   | CCP5IE | CCP4IE  | CCP3IE    | 00 0000              | 00 0000                         |

| IPR3                   |                                                              | _                                   | RC2IP     | TX2IP     | TMR4IP   | CCP5IP | CCP4IP  | CCP3IP    | 11 1111              | 11 1111                         |

| TMR2                   | Timer2 Mo                                                    | dule Registe                        | r         |           |          |        |         |           | 0000 0000            | 0000 0000                       |

| PR2                    | Timer2 Mo                                                    | dule Period I                       | Register  |           |          |        |         |           | 1111 1111            | 1111 1111                       |

| T2CON                  | _                                                            | T2OUTPS3                            | T2OUTPS2  | T2OUTPS1  | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000            | -000 0000                       |

| T3CON                  | RD16                                                         | T3CCP2                              | T3CKPS1   | T3CKPS0   | T3CCP1   | T3SYNC | TMR3CS  | TMR3ON    | 0000 0000            | uuuu uuuu                       |

| TMR4                   | Timer4 Re                                                    | gister                              |           |           |          |        |         |           | 0000 0000            | uuuu uuuu                       |

| PR4                    | Timer4 Per                                                   | riod Register                       |           |           |          |        |         |           | 1111 1111            | uuuu uuuu                       |

| T4CON                  | - T4OUTPS3 T4OUTPS2 T4OUTPS1 T4OUTPS0 TMR4ON T4CKPS1 T4CKPS0 |                                     |           |           |          |        |         | -000 0000 | uuuu uuuu            |                                 |

| CCPRxL <sup>(1)</sup>  | Capture/Co                                                   | apture/Compare/PWM Register x (LSB) |           |           |          |        |         |           |                      | uuuu uuuu                       |

| CCPRxH <sup>(1)</sup>  | Capture/Co                                                   | ompare/PWN                          | xxxx xxxx | uuuu uuuu |          |        |         |           |                      |                                 |

| CCPxCON <sup>(1)</sup> | —                                                            | _                                   | DCxB1     | DCxB0     | CCPxM3   | CCPxM2 | CCPxM1  | CCPxM0    | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM, Timer2, or Timer4.

Note 1: Generic term for all of the identical registers of this name for all CCP modules, where 'x' identifies the individual module (CCP1 through CCP5). Bit assignments and Reset values for all registers of the same generic name are identical.

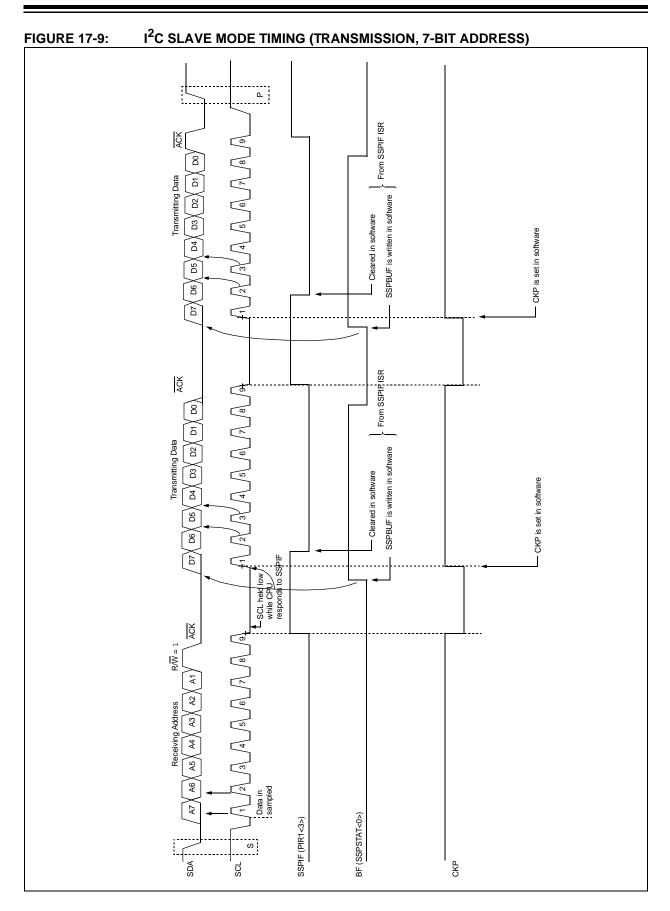

#### 17.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 17.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 17-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

#### 17.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence, as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 17.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 17-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit.

#### 17.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled as in 7-bit Slave Transmit mode (see Figure 17-11).

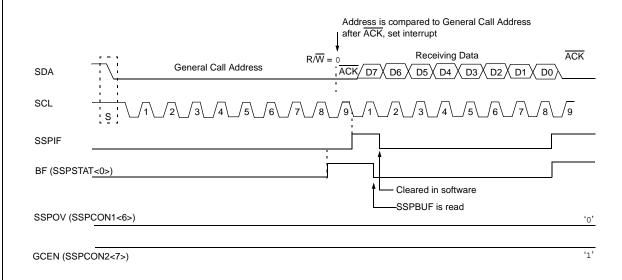

#### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address, which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the I<sup>2</sup>C protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-15).

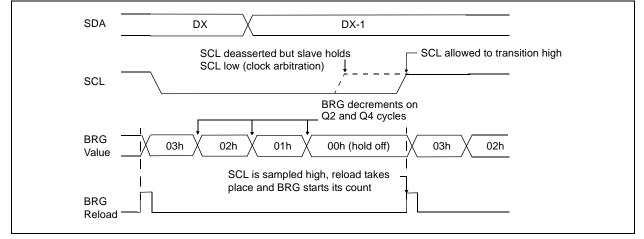

#### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 15-18).

| R/W-0                  | R/W-0                                                                  | R/W-0        | R/W-0                          | R/W-0        | R-0          | R-0          | R-x        |

|------------------------|------------------------------------------------------------------------|--------------|--------------------------------|--------------|--------------|--------------|------------|

| SPEN                   | RX9                                                                    | SREN         | CREN                           | ADDEN        | FERR         | OERR         | RX9D       |

| bit 7                  |                                                                        |              |                                |              |              |              | bit (      |

| SPEN: Se               | erial Port Enab                                                        | le bit       |                                |              |              |              |            |

|                        | port enabled (<br>port disabled                                        | configures   | RX/DT and                      | TX/CK pins   | as serial po | rt pins)     |            |

| <b>RX9</b> : 9-bi      | t Receive Enat                                                         | ole bit      |                                |              |              |              |            |

|                        | ts 9-bit receptients 8-bit receptients 8-bit receptients               |              |                                |              |              |              |            |

| SREN: Si               | ngle Receive E                                                         | Enable bit   |                                |              |              |              |            |

| Asynchro<br>Don't care | nous mode:<br>e.                                                       |              |                                |              |              |              |            |

| 1 = Enab<br>0 = Disal  | ous mode – M<br>les single rece<br>bles single rece<br>cleared after r | ive<br>eive  | s complete.                    |              |              |              |            |

|                        | <u>ous mode – Sl</u>                                                   | -            | ·                              |              |              |              |            |

| CREN: C                | ontinuous Rec                                                          | eive Enable  | e bit                          |              |              |              |            |

| 1 = Enab               | nous mode:<br>les receiver<br>les receiver                             |              |                                |              |              |              |            |

| Synchron<br>1 = Enab   | ous mode:<br>les continuous<br>les continuous                          |              | til enable bit                 | CREN is cle  | eared (CREI  | N overrides  | SREN)      |

| ADDEN:                 | Address Detec                                                          | t Enable bi  | it                             |              |              |              |            |

| 1 = Enat<br>is set     | nous mode 9-b<br>les address de<br>bles address de                     | tection, en  | ables interru                  |              |              |              |            |

|                        | aming Error bit                                                        |              | · · · <b>)</b> · · · · · · · · |              |              |              |            |

| 1 = Fram               | ng error (can b<br>aming error                                         |              | by reading                     | RCREG regi   | ster and rec | eive next va | alid byte) |

|                        | verrun Error bi                                                        | t            |                                |              |              |              |            |

|                        | un error (can b<br>rerrun error                                        | e cleared    | by clearing b                  | oit CREN)    |              |              |            |

| RX9D: 9t               | h bit of Receive                                                       | ed Data      |                                |              |              |              |            |

| This can               | be address/dat                                                         | a bit or a p | arity bit and                  | must be cale | culated by u | ser firmwar  | э.         |

| Legend:                |                                                                        |              |                                |              |              |              |            |

| R = Read               | able bit                                                               | W = W        | /ritable bit                   | U = Unim     | plemented    | bit, read as | '0'        |

|                        |                                                                        |              |                                |              |              |              |            |

'1' = Bit is set

'0' = Bit is cleared

### **REGISTER 18-**

- n = Value at POR

x = Bit is unknown

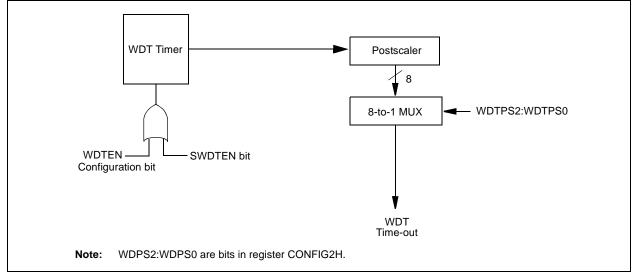

#### 23.2.2 WDT POSTSCALER

The WDT has a postscaler that can extend the WDT Reset period. The postscaler is selected at the time of the device programming by the value written to the CONFIG2H Configuration register.

#### TABLE 23-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| CONFIG2H | —     | —     | —     | —     | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | _     | _     | RI    | TO     | PD     | POR    | BOR    |

| WDTCON   | —     | —     | —     | —     | —      |        | _      | SWDTEN |

**Legend:** Shaded cells are not used by the Watchdog Timer.

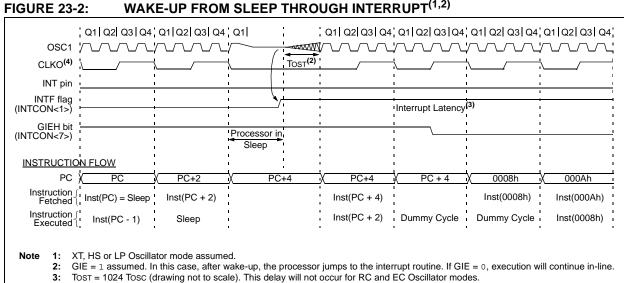

4: CLKO is not available in these oscillator modes, but shown here for timing reference

#### 23.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $PIC^{\textcircled{B}}$  devices. The user program memory is divided on binary boundaries into individual blocks, each of which has three separate code protection bits associated with it:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

The code protection bits are located in Configuration Registers 5L through 7H. Their locations within the registers are summarized in Table 23-3.

In the PIC18FXX20 family, the block size varies with the size of the user program memory. For PIC18FX520 devices, program memory is divided into four blocks of 8 Kbytes each. The first block is further divided into a boot block of 2 Kbytes and a second block (Block 0) of 6 Kbytes, for a total of five blocks. The organization of the blocks and their associated code protection bits are shown in Figure 23-3.

For PIC18FX620 and PIC18FX720 devices, program memory is divided into blocks of 16 Kbytes. The first block is further divided into a boot block of 512 bytes and a second block (Block 0) of 15.5 Kbytes, for a total of nine blocks. This produces five blocks for 64-Kbyte devices and nine for 128-Kbyte devices. The organization of the blocks and their associated code protection bits are shown in Figure 23-4.

| File Name |          | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|----------|----------------------|----------------------|----------------------|----------------------|-------|-------|-------|-------|

| 300008h   | CONFIG5L | CP7 <sup>(1)</sup>   | CP6 <sup>(1)</sup>   | CP5 <sup>(1)</sup>   | CP4 <sup>(1)</sup>   | CP3   | CP2   | CP1   | CP0   |

| 300009h   | CONFIG5H | CPD                  | CPB                  | _                    | —                    | _     |       | _     | _     |

| 30000Ah   | CONFIG6L | WRT7 <sup>(1)</sup>  | WRT6 <sup>(1)</sup>  | WRT5 <sup>(1)</sup>  | WRT4 <sup>(1)</sup>  | WRT3  | WRT2  | WRT1  | WRT0  |

| 30000Bh   | CONFIG6H | WRTD                 | WRTB                 | WRTC                 | —                    |       | _     | _     | _     |

| 30000Ch   | CONFIG7L | EBTR7 <sup>(1)</sup> | EBTR6 <sup>(1)</sup> | EBTR5 <sup>(1)</sup> | EBTR4 <sup>(1)</sup> | EBTR3 | EBTR2 | EBTR1 | EBTR0 |

| 30000Dh   | CONFIG7H | _                    | EBTRB                | _                    | _                    |       |       | _     | _     |

TABLE 23-3: SUMMARY OF CODE PROTECTION REGISTERS

**Legend:** Shaded cells are unimplemented.

Note 1: Unimplemented in PIC18FX520 and PIC18FX620 devices.

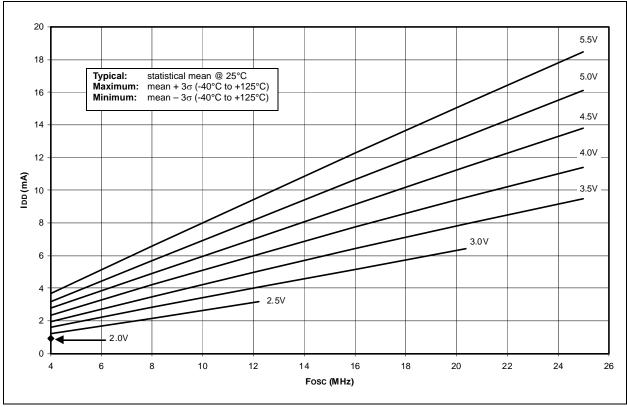

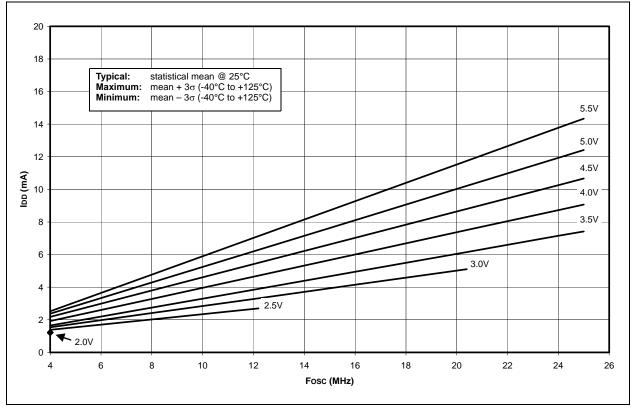

#### FIGURE 27-3: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE) EXTENDED

Example

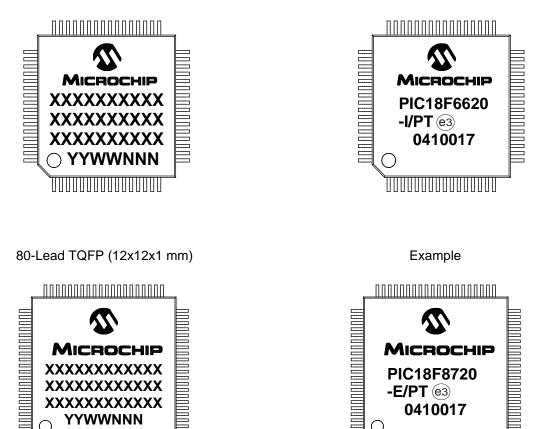

### 28.0 PACKAGING INFORMATION

### 28.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

|    |   | XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|----|---|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No | b | e carried                                | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>for customer-specific information.                                                                                                                                                                                              |

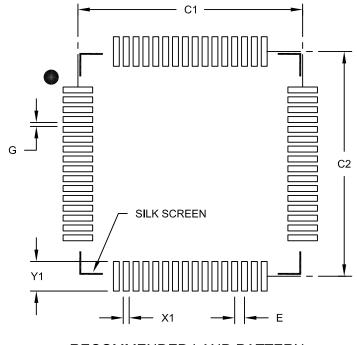

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension                | MIN         | NOM  | MAX      |      |  |

| Contact Pitch            | E           |      | 0.50 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 11.40    |      |  |

| Contact Pad Spacing      | C2          |      | 11.40    |      |  |

| Contact Pad Width (X64)  | X1          |      |          | 0.30 |  |

| Contact Pad Length (X64) | Y1          |      |          | 1.50 |  |

| Distance Between Pads    | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

NOTES: