Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6720t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| PIC18F6X20              | PIC18F8X20                                                                                                                                     | Pin<br>Type                                                                                                                                                                                                                                                                                                    | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                | Type                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                         |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                               | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                           |  |  |

| 48                      | 58                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                       | TTL<br>ST                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O.<br>External interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 47                      | 57                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                       | TTL<br>ST                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O.<br>External interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 46                      | 56                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                       | TTL<br>ST                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O.<br>External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 45                      | 55                                                                                                                                             | I/O<br>I/O<br>I/O                                                                                                                                                                                                                                                                                              | TTL<br>ST<br>ST                                                                                                                                                                                                                                                                                                                                                               | Digital I/O.<br>External interrupt 3.<br>Capture2 input, Compare2 output,<br>PWM2 output.                                                                                                                                                                                                                                                                                                                               |  |  |

| 44                      | 54                                                                                                                                             | I/O<br>I                                                                                                                                                                                                                                                                                                       | TTL<br>ST                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O.<br>Interrupt-on-change pin.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 43                      | 53                                                                                                                                             | I/O<br>I<br>I/O                                                                                                                                                                                                                                                                                                | TTL<br>ST<br>ST                                                                                                                                                                                                                                                                                                                                                               | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP Programming enabl<br>pin.                                                                                                                                                                                                                                                                                                                                  |  |  |

| 42                      | 52                                                                                                                                             | I/O<br>I<br>I/O                                                                                                                                                                                                                                                                                                | TTL<br>ST<br>ST                                                                                                                                                                                                                                                                                                                                                               | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and<br>ICSP programming clock.                                                                                                                                                                                                                                                                                                                          |  |  |

| 37                      | 47                                                                                                                                             | I/O<br>I/O                                                                                                                                                                                                                                                                                                     | TTL<br>ST                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and<br>ICSP programming data.                                                                                                                                                                                                                                                                                                                           |  |  |

| mitt Trigger inpu<br>it |                                                                                                                                                | evels                                                                                                                                                                                                                                                                                                          | Analog =<br>O =                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>CMOS compatible input or output</li> <li>Analog input</li> <li>Output</li> <li>Open-Drain (no P diode to VDD)</li> </ul>                                                                                                                                                                                                                                                                                       |  |  |

| ller).<br>gnment when C | CP2MX is set.                                                                                                                                  |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                         | 46<br>45<br>44<br>43<br>42<br>37<br>compatible inpumit<br>rer<br>ssignment for Culler).<br>gnment when Comony interface<br>iltiplexed with the | 46       56         45       55         44       54         43       53         42       52         37       47         compatible input<br>mitt Trigger input with CMOS late<br>rer         ssignment for CCP2 when CCF<br>iller).         gnment when CCP2MX is set.         emory interface functions are o | 4757I/O4656I/O4555I/O4555I/O4454I/O4353I/O4252I/O4252I/O3747I/O100I/OI/O101I/O10252103I/O103100104100105100106100107100107100108100109100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100100 | 4757 $I/O$ TTL<br>ST4656 $I/O$ TTL<br>ST4555 $I/O$ TTL<br>ST4555 $I/O$ TTL<br>I4454 $I/O$ TTL<br>ST4353 $I/O$ TTL<br>I4252 $I/O$ TTL<br>ST4252 $I/O$ TTL<br>ST3747 $I/O$ TTL<br>ST3747 $I/O$ TTL<br>STareO=compatible inputCMOS levelsAnalog =rerO=ssignment for CCP2 when CCP2MX is not selected<br>ller).Set.gnment when CCP2MX is set.en only available on Plu<br>utiplexed with this pin by default when configured |  |  |

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- 6: AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

| Pin Name            | Pin N            | umber      | Pin      | Buffer      | Description                                                                                                                 |  |  |

|---------------------|------------------|------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name            | PIC18F6X20       | PIC18F8X20 | Туре     | Туре        | Description                                                                                                                 |  |  |

|                     |                  |            |          |             | PORTC is a bidirectional I/O port.                                                                                          |  |  |

| RC0/T1OSO/T13CKI    | 30               | 36         |          |             |                                                                                                                             |  |  |

| RC0                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| T1OSO               |                  |            | 0        | —           | Timer1 oscillator output.                                                                                                   |  |  |

| T13CKI              |                  |            | I        | ST          | Timer1/Timer3 external clock input.                                                                                         |  |  |

| RC1/T1OSI/CCP2      | 29               | 35         |          |             |                                                                                                                             |  |  |

| RC1                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| T1OSI               |                  |            | I        | CMOS        | Timer1 oscillator input.                                                                                                    |  |  |

| CCP2 <sup>(2)</sup> |                  |            | I/O      | ST          | Capture2 input/Compare2 output/                                                                                             |  |  |

|                     |                  |            |          |             | PWM2 output.                                                                                                                |  |  |

| RC2/CCP1            | 33               | 43         |          |             |                                                                                                                             |  |  |

| RC2                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| CCP1                |                  |            | I/O      | ST          | Capture1 input/Compare1 output/                                                                                             |  |  |

|                     |                  |            |          |             | PWM1 output.                                                                                                                |  |  |

| RC3/SCK/SCL         | 34               | 44         |          |             |                                                                                                                             |  |  |

| RC3                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| SCK                 |                  |            | I/O      | ST          | Synchronous serial clock input/outpu                                                                                        |  |  |

|                     |                  |            |          |             | for SPI mode.                                                                                                               |  |  |

| SCL                 |                  |            | I/O      | ST          | Synchronous serial clock input/output for I <sup>2</sup> C mode.                                                            |  |  |

| RC4/SDI/SDA         | 35               | 45         |          |             |                                                                                                                             |  |  |

| RC4                 |                  | 45         | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| SDI                 |                  |            | "/C      | ST          | SPI data in.                                                                                                                |  |  |

| SDA                 |                  |            | I/O      | ST          | $I^2C$ data I/O.                                                                                                            |  |  |

| RC5/SDO             | 36               | 46         | ., C     | •           |                                                                                                                             |  |  |

| RC5/SDO<br>RC5      | 30               | 40         | I/O      | ST          | Digital I/O.                                                                                                                |  |  |

| SDO                 |                  |            | 0        |             | SPI data out.                                                                                                               |  |  |

|                     |                  | 07         | Ŭ        |             |                                                                                                                             |  |  |

| RC6/TX1/CK1         | 31               | 37         | 1/0      | ст          |                                                                                                                             |  |  |

| RC6<br>TX1          |                  |            | 1/O<br>O | ST          | Digital I/O.<br>USART 1 asynchronous transmit.                                                                              |  |  |

| CK1                 |                  |            | 1/0      | ST          | USART 1 synchronous clock                                                                                                   |  |  |

| ONT                 |                  |            | 1/0      | 51          | (see RX1/DT1).                                                                                                              |  |  |

|                     | 22               | 20         |          |             |                                                                                                                             |  |  |

| RC7/RX1/DT1         | 32               | 38         | I/O      | ST          | Digital I/O                                                                                                                 |  |  |

| RC7<br>RX1          |                  |            |          | ST          | Digital I/O.<br>USART 1 asynchronous receive.                                                                               |  |  |

| DT1                 |                  |            | I/O      | ST          | USART 1 synchronous data                                                                                                    |  |  |

|                     |                  |            | ",0      |             | (see TX1/CK1).                                                                                                              |  |  |

| Legend: TTL = TTL   | compatible inp   | L          |          | CMOS -      | = CMOS compatible input or output                                                                                           |  |  |

|                     | mitt Trigger inp |            | evels    |             | = Analog input                                                                                                              |  |  |

|                     |                  |            |          | •           |                                                                                                                             |  |  |

|                     |                  |            |          |             |                                                                                                                             |  |  |

| I = Inpu<br>P = Pow | it<br>ver        |            |          | O =<br>OD = | <ul> <li>Analog input</li> <li>Output</li> <li>Open-Drain (no P diode to VE</li> <li>(all operating modes except</li> </ul> |  |  |

#### TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 when CCP2MX is not selected (all operating modes except Microcontroller).

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

**6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

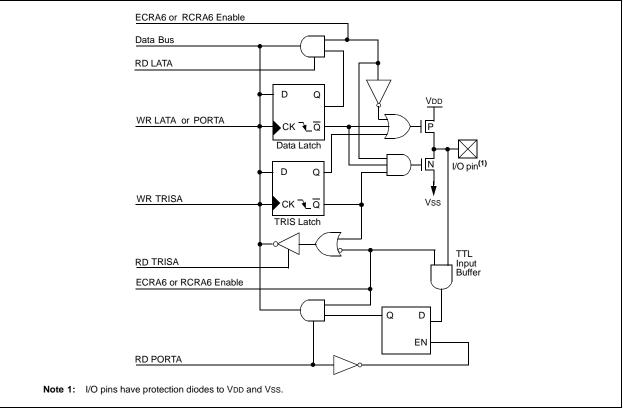

#### FIGURE 10-4: BLOCK DIAGRAM OF RA6 PIN (WHEN ENABLED AS I/O)

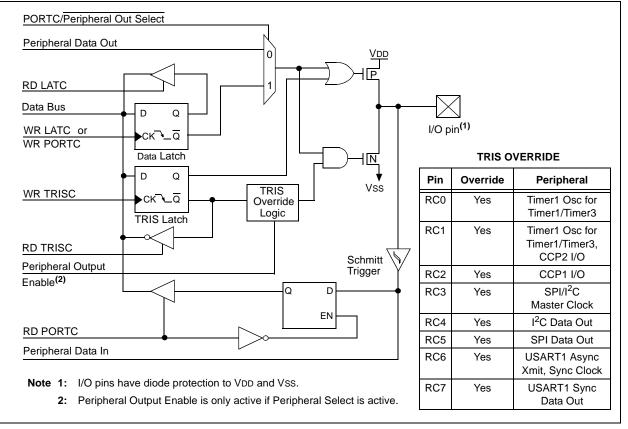

#### 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register, read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Note: On a Power-on Reset, these pins are configured as digital inputs.

The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

RC1 is normally configured by configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output<br>; data latches           |

|-------|-------|------------------------------------------------------------------------|

| CLRF  | LATC  | ; Alternate method<br>; to clear output<br>; data latches              |

| MOVLW | 0xCF  | ; Value used to<br>; initialize data<br>; direction                    |

| MOVWF | TRISC | ; Set RC<3:0> as inputs<br>; RC<5:4> as outputs<br>; RC<7:6> as inputs |

|       |       |                                                                        |

#### FIGURE 10-8: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

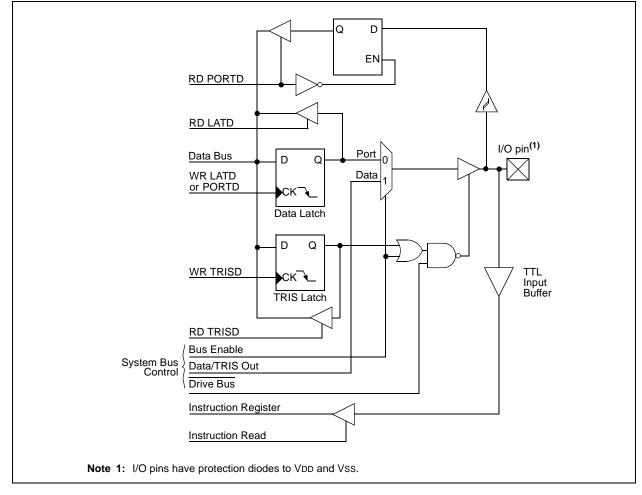

#### FIGURE 10-10: PORTD BLOCK DIAGRAM IN SYSTEM BUS MODE

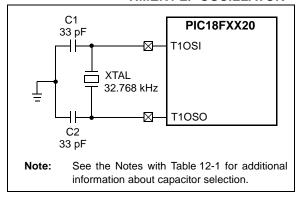

#### 12.2 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit, T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 12-3. Table 12-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator

#### FIGURE 12-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

#### TABLE 12-1: CAPACITOR SELECTION FOR THE ALTERNATE OSCILLATOR

| Osc Type              | Freq                                      | C1                 | C2                 |  |  |  |  |  |  |  |

|-----------------------|-------------------------------------------|--------------------|--------------------|--|--|--|--|--|--|--|

| LP                    | 32 kHz                                    | TBD <sup>(1)</sup> | TBD <sup>(1)</sup> |  |  |  |  |  |  |  |

| Crystal to be Tested: |                                           |                    |                    |  |  |  |  |  |  |  |

| 32.768 kHz            | 32.768 kHz Epson C-001R32.768K-A ± 20 PPM |                    |                    |  |  |  |  |  |  |  |

- **Note 1:** Microchip suggests 33 pF as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

#### 12.2.1 LOW-POWER TIMER1 OPTION (PIC18FX520 DEVICES ONLY)

The Timer1 oscillator for PIC18LFX520 devices incorporates a low-power feature, which allows the oscillator to automatically reduce its power consumption when the microcontroller is in Sleep mode.

As high noise environments may cause excessive oscillator instability in Sleep mode, this option is best suited for low noise applications where power conservation is an important design consideration. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 12-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

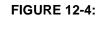

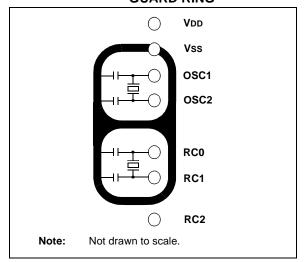

If a high-speed circuit must be located near the oscillator (such as the CCP1 pin in output compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as shown in Figure 12-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

#### OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

Note: PIC18FX620/X720 devices have the standard Timer1 oscillator permanently selected. PIC18LFX620/X720 devices have the low-power Timer1 oscillator permanently selected.

NOTES:

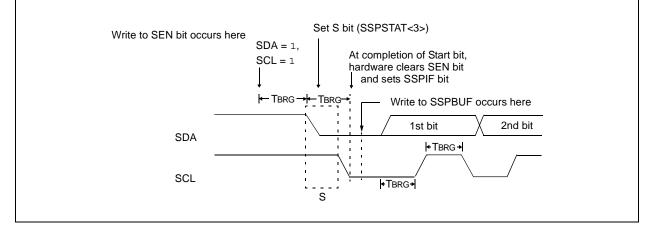

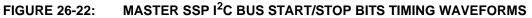

#### 17.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Condition Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low, while SCL is high, is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

**Note:** If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 17.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 17-19: FIRST START BIT TIMING

| R/W-0                  | R/W-0                                                                  | R/W-0        | R/W-0                          | R/W-0        | R-0          | R-0          | R-x        |

|------------------------|------------------------------------------------------------------------|--------------|--------------------------------|--------------|--------------|--------------|------------|

| SPEN                   | RX9                                                                    | SREN         | CREN                           | ADDEN        | FERR         | OERR         | RX9D       |

| bit 7                  |                                                                        |              |                                |              |              |              | bit (      |

| SPEN: Se               | erial Port Enab                                                        | le bit       |                                |              |              |              |            |

|                        | port enabled (<br>port disabled                                        | configures   | RX/DT and                      | TX/CK pins   | as serial po | rt pins)     |            |

| <b>RX9</b> : 9-bi      | t Receive Enat                                                         | ole bit      |                                |              |              |              |            |

|                        | ts 9-bit receptients 8-bit receptients 8-bit receptients               |              |                                |              |              |              |            |

| SREN: Si               | ngle Receive E                                                         | Enable bit   |                                |              |              |              |            |

| Asynchro<br>Don't care | nous mode:<br>e.                                                       |              |                                |              |              |              |            |

| 1 = Enab<br>0 = Disal  | ous mode – M<br>les single rece<br>bles single rece<br>cleared after r | ive<br>eive  | s complete.                    |              |              |              |            |

|                        | <u>ous mode – Sl</u>                                                   | -            | ·                              |              |              |              |            |

| CREN: C                | ontinuous Rec                                                          | eive Enable  | e bit                          |              |              |              |            |

| 1 = Enab               | nous mode:<br>les receiver<br>les receiver                             |              |                                |              |              |              |            |

| Synchron<br>1 = Enab   | ous mode:<br>les continuous<br>les continuous                          |              | til enable bit                 | CREN is cle  | eared (CREI  | N overrides  | SREN)      |

| ADDEN:                 | Address Detec                                                          | t Enable bi  | it                             |              |              |              |            |

| 1 = Enat<br>is set     | nous mode 9-b<br>les address de<br>bles address de                     | tection, en  | ables interru                  |              |              |              |            |

|                        | aming Error bit                                                        |              | · · · <b>)</b> · · · · · · · · |              |              |              |            |

| 1 = Fram               | ng error (can b<br>aming error                                         |              | by reading                     | RCREG regi   | ster and rec | eive next va | alid byte) |

|                        | verrun Error bi                                                        | t            |                                |              |              |              |            |

|                        | un error (can b<br>rerrun error                                        | e cleared    | by clearing b                  | oit CREN)    |              |              |            |

| RX9D: 9t               | h bit of Receive                                                       | ed Data      |                                |              |              |              |            |

| This can               | pe address/dat                                                         | a bit or a p | arity bit and                  | must be cale | culated by u | ser firmwar  | э.         |

| Legend:                |                                                                        |              |                                |              |              |              |            |

| R = Read               | able bit                                                               | W = W        | /ritable bit                   | U = Unim     | plemented    | bit, read as | '0'        |

|                        |                                                                        |              |                                |              |              |              |            |

'1' = Bit is set

'0' = Bit is cleared

#### **REGISTER 18-**

- n = Value at POR

x = Bit is unknown

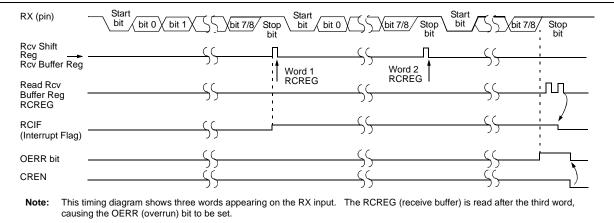

#### FIGURE 18-5: ASYNCHRONOUS RECEPTION

#### TABLE 18-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name                  | Bit 7        | Bit 6         | Bit 5     | Bit 4  | Bit 3  | t 3 Bit 2 Bit 1 |        | Bit 0         | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|-----------------------|--------------|---------------|-----------|--------|--------|-----------------|--------|---------------|----------------------|---------------------------------|--|

| INTCON                | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE    | INTOIE | RBIE   | TMR0IF          | INTOIF | RBIF          | 0000 0000            | 0000 0000                       |  |

| PIR1                  | PSPIF        | ADIF          | RC1IF     | TXIF   | SSPIF  | CCP1IF          | TMR2IF | TMR1IF        | 0000 0000            | 0000 0000                       |  |

| PIE1                  | PSPIE        | ADIE          | RC1IE     | TXIE   | SSPIE  | CCP1IE          | TMR2IE | TMR1IE        | 0000 0000            | 0000 0000                       |  |

| IPR1                  | PSPIP        | ADIP          | RC1IP     | TXIP   | SSPIP  | CCP1IP          | TMR2IP | TMR1IP        | 0111 1111            | 0111 1111                       |  |

| PIR3                  | —            | —             | RC2IF     | TX2IF  | TMR4IF | CCP5IF          | CCP4IF | <b>CCP3IF</b> | 00 0000              | 00 0000                         |  |

| PIE3                  | —            | —             | RC2IE     | TX2IE  | TMR4IE | CCP5IE          | CCP4IE | CCP3IE        | 00 0000              | 00 0000                         |  |

| IPR3                  | —            | —             | RC2IP     | TX2IP  | TMR4IP | CCP5IP          | CCP4IP | CCP3IP        | 11 1111              | 11 1111                         |  |

| RCSTAx <sup>(1)</sup> | SPEN         | RX9           | SREN      | CREN   | ADDEN  | FERR            | OERR   | RX9D          | x000 0000x           | x000 0000x                      |  |

| RCREGx <sup>(1)</sup> | USART Rec    | eive Regis    | ter       |        |        |                 |        |               | 0000 0000            | 0000 0000                       |  |

| TXSTAx <sup>(1)</sup> | CSRC         | TX9           | TXEN      | SYNC   | —      | BRGH            | TRMT   | TX9D          | 0000 -010            | 0000 -010                       |  |

| SPBRGx <sup>(1)</sup> | Baud Rate C  | 0000 0000     | 0000 0000 |        |        |                 |        |               |                      |                                 |  |

|                       |              |               |           |        |        |                 |        |               |                      |                                 |  |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

#### **REGISTER 19-2: ADCON1 REGISTER**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

|       | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

#### bit 7-6 Unimplemented: Read as '0'

#### bit 5-4 VCFG1:VCFG0: Voltage Reference Configuration bits:

| VCFG1<br>VCFG0 | A/D Vref+      | A/D VREF-      |

|----------------|----------------|----------------|

| 00             | AVdd           | AVss           |

| 01             | External VREF+ | AVss           |

| 10             | AVDD           | External VREF- |

| 11             | External VREF+ | External VREF- |

#### bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3<br>PCFG0 | AN15                                    | AN14 | AN13 | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 | ANG | AN5 | AN4 | AN3 | AN2 | AN1 | ANO |

|----------------|-----------------------------------------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000           | Α                                       | Α    | А    | Α    | Α    | Α    | Α   | Α   | А   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0001           | D                                       | D    | А    | Α    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | Α   |

| 0010           | D                                       | D    | D    | А    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0011           | D                                       | D    | D    | D    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0100           | D                                       | D    | D    | D    | D    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | Α   |

| 0101           | D                                       | D    | D    | D    | D    | D    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0110           | D                                       | D    | D    | D    | D    | D    | D   | Α   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 0111           | D                                       | D    | D    | D    | D    | D    | D   | D   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 1000           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | А   | А   | А   | Α   | А   | А   | А   |

| 1001           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | А   | А   | Α   | А   | А   | А   |

| 1010           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | А   | Α   | А   | Α   | А   |

| 1011           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | А   | А   | А   | А   |

| 1100           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | А   | А   | А   |

| 1101           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | А   | А   |

| 1110           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111           | D                                       | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

| A _ Ana        | $\Delta = Analog input D = Digital I/O$ |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

A = Analog input D = Digital I/O

Note: Shaded cells indicate A/D channels available only on PIC18F8X20 devices.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The value in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ ADRESL registers will contain unknown data after a Power-on Reset.

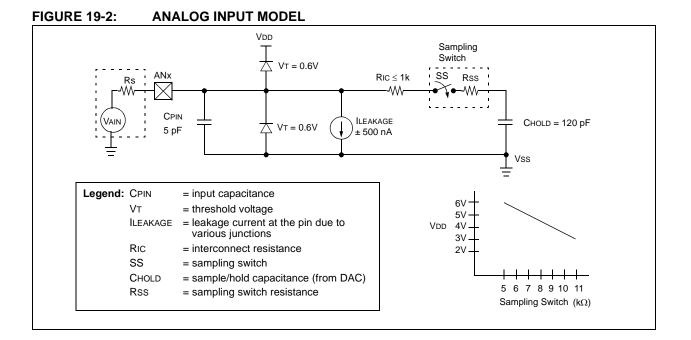

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 19.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started.

The following steps should be followed to do an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- · Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit ADIF, if required.

- 7. For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

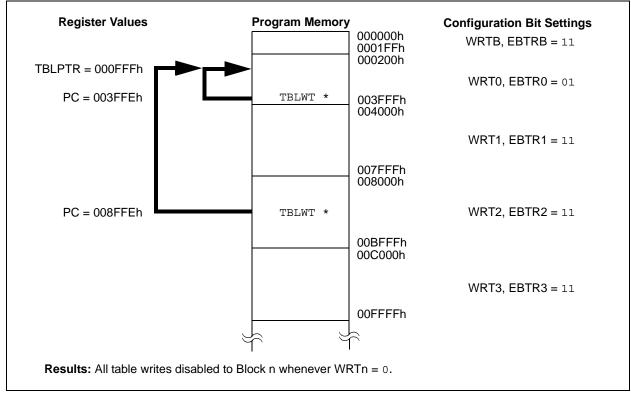

#### 23.4.1 PROGRAM MEMORY CODE PROTECTION

The user memory may be read to, or written from, any location using the table read and table write instructions. The device ID may be read with table reads. The configuration registers may be read and written with the table read and table write instructions.

In user mode, the CPn bits have no direct effect. CPn bits inhibit external reads and writes. A block of user memory may be protected from table writes if the WRTn configuration bit is '0'. The EBTRn bits control table reads. For a block of user memory with the EBTRn bit set to '0', a table read instruction that executes from within that block is allowed to read. A table read instruction that executes from a location out-

side of that block is not allowed to read and will result in reading '0's. Figures 23-5 through 23-7 illustrate table write and table read protection using devices with a 16-Kbyte block size as the models. The principles illustrated are identical for devices with an 8-Kbyte block size.

Note: Code protection bits may only be written to a '0' from a '1' state. It is not possible to write a '1' to a bit in the '0' state. Code protection bits are only set to '1' by a full chip erase or block erase function. The full chip erase and block erase functions can only be initiated via ICSP or an external programmer.

#### FIGURE 23-5: TABLE WRITE (WRTn) DISALLOWED

#### 23.4.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 23.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write-protected. The WRTC bit controls protection of the configuration registers. In user mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

#### 23.5 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

#### 23.6 In-Circuit Serial Programming

PIC18FX520/X620/X720 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

| Note: | When                                      | performing    | In-Circuit | Serial  |  |  |

|-------|-------------------------------------------|---------------|------------|---------|--|--|

|       | Progran                                   | nming, verify | that power | is con- |  |  |

|       | nected to all VDD and AVDD pins of the    |               |            |         |  |  |

|       | microcontroller and that all Vss and AVss |               |            |         |  |  |

|       | pins are                                  | grounded.     |            |         |  |  |

#### 23.7 In-Circuit Debugger

When the DEBUG bit in the CONFIG4L Configuration register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 23-4 shows which features are consumed by the background debugger.

#### TABLE 23-4: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7       |  |  |  |

|----------------|----------------|--|--|--|

| Stack          | 2 levels       |  |  |  |

| Program Memory | Last 576 bytes |  |  |  |

| Data Memory    | Last 10 bytes  |  |  |  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

#### 23.8 Low-Voltage ICSP Programming

The LVP bit in the CONFIG4L Configuration register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM pin, provided the LVP bit is set. The LVP bit defaults to a '1' from the factory.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin and should be held low during normal operation.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 5 in the TRISB register must be cleared to disable the pull-up on RB5 and ensure the proper operation of the device.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only High-Voltage Programming mode can be used to program the device.

When using Low-Voltage ICSP Programming, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the codeprotect bits from an on state to an off state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs or user code can be reprogrammed or added.

| CLRF                                 | Clear f                                                                  | CLRWDT                    | Clear Watchdog Timer                                             |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------|--|--|--|

| Syntax:                              | [ label ] CLRF f [,a]                                                    | Syntax:                   | [label] CLRWDT                                                   |  |  |  |

| Operands:                            | $0 \leq f \leq 255$                                                      | Operands:                 | None                                                             |  |  |  |

|                                      | a ∈ [0,1]                                                                | Operation:                | 000h $\rightarrow$ WDT,                                          |  |  |  |

| Operation:                           | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$     |                           | $000h \rightarrow WDT$ postscaler,                               |  |  |  |

|                                      | . , _                                                                    |                           | $1 \rightarrow \underline{TO},$<br>$1 \rightarrow \overline{PD}$ |  |  |  |

| Status Affected:                     | Z                                                                        | Status Affected:          | TO, PD                                                           |  |  |  |

| Encoding:                            | 0110 101a ffff ffff                                                      | Encoding:                 |                                                                  |  |  |  |

| Description:                         | Clears the contents of the specified register. If 'a' is '0', the Access | Description:              | CLRWDT instruction resets the                                    |  |  |  |

|                                      | Bank will be selected, overriding                                        |                           | Watchdog Timer. It also resets the                               |  |  |  |

|                                      | the BSR value. If 'a' = 1, then the                                      |                           | postscaler of the WDT. Status bits                               |  |  |  |

|                                      | bank will be selected as per the BSR value (default).                    |                           | TO and PD are set.                                               |  |  |  |

| Words:                               | 1                                                                        | Words:                    | 1                                                                |  |  |  |

| Cycles:                              | 1                                                                        | Cycles:                   | 1                                                                |  |  |  |

| -                                    | I                                                                        | Q Cycle Activity:         |                                                                  |  |  |  |

| Q Cycle Activity:<br>Q1              | Q2 Q3 Q4                                                                 | Q1<br>Decode              | Q2 Q3 Q4                                                         |  |  |  |

| Decode                               | Read Process Write                                                       | Decode                    | operation Data operation                                         |  |  |  |

|                                      | register 'f' Data register 'f'                                           | <u> </u>                  | ,                                                                |  |  |  |

|                                      |                                                                          | Example:                  | CLRWDT                                                           |  |  |  |

| Example:                             | CLRF FLAG_REG,1                                                          | Before Instru             |                                                                  |  |  |  |

| Before Instruc                       |                                                                          | WDT Cou                   |                                                                  |  |  |  |

| FLAG_REG = 0x5A<br>After Instruction |                                                                          | After Instruct<br>WDT Cou |                                                                  |  |  |  |

| $FLAG_REG = 0x00$                    |                                                                          | WDT Pos                   |                                                                  |  |  |  |

|                                      |                                                                          | TO<br>PD                  | = 1<br>= 1                                                       |  |  |  |

| FLAG_KE                              |                                                                          | TO                        | = 1                                                              |  |  |  |

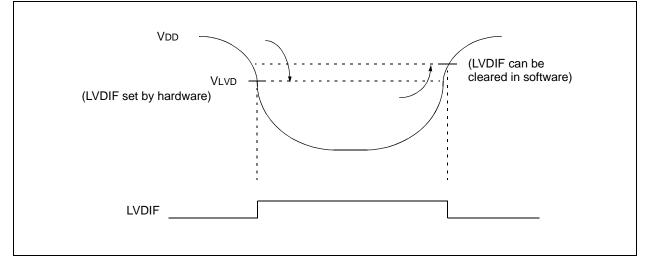

#### FIGURE 26-5: LOW-VOLTAGE DETECT CHARACTERISTICS

#### TABLE 26-3: LOW-VOLTAGE DETECT CHARACTERISTICS

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $~-40^\circ C \le TA \le +85^\circ C$  for industrial  $-40^\circ C ~\le TA \le +125^\circ C$  for extended

| Param<br>No. | Symbol | Characteristic                   |            | Min  | Тур† | Max  | Units | Conditions |

|--------------|--------|----------------------------------|------------|------|------|------|-------|------------|

| D420         |        | LVD Voltage on VDD               | LVV = 0001 | 1.96 | 2.06 | 2.16 | V     |            |

|              |        | Transition high-to-low           | LVV = 0010 | 2.16 | 2.27 | 2.38 | V     |            |

|              |        |                                  | LVV = 0011 | 2.35 | 2.47 | 2.59 | V     |            |

|              |        |                                  | LVV = 0100 | 2.45 | 2.58 | 2.71 | V     |            |

|              |        |                                  | LVV = 0101 | 2.64 | 2.78 | 2.92 | V     |            |

|              |        |                                  | LVV = 0110 | 2.75 | 2.89 | 3.03 | V     |            |

|              |        |                                  | LVV = 0111 | 2.95 | 3.1  | 3.26 | V     |            |

|              |        |                                  | LVV = 1000 | 3.24 | 3.41 | 3.58 | V     |            |

|              |        |                                  | LVV = 1001 | 3.43 | 3.61 | 3.79 | V     |            |

|              |        |                                  | LVV = 1010 | 3.53 | 3.72 | 3.91 | V     |            |

|              |        |                                  | LVV = 1011 | 3.72 | 3.92 | 4.12 | V     |            |

|              |        |                                  | LVV = 1100 | 3.92 | 4.13 | 4.34 | V     |            |

|              |        |                                  | LVV = 1101 | 4.11 | 4.33 | 4.55 | V     |            |

|              |        |                                  | LVV = 1110 | 4.41 | 4.64 | 4.87 | V     |            |

| D423         | Vbg    | Band Gap Reference Voltage Value |            |      | 1.22 | —    | V     |            |

† Production tested at TAMB = 25°C. Specifications over temperature limits ensured by characterization.

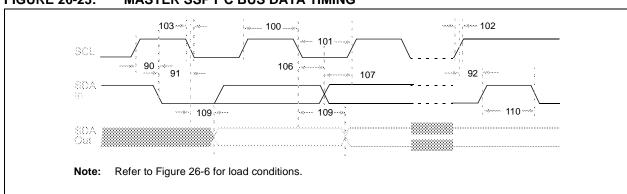

| TABLE 26-21: MASTER SSP I <sup>2</sup> C BUS START/STOP BITS REQUIREMENT |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Param<br>No. | Symbol     | Characteristic                |                           | Min              | Max | Units | Conditions                                            |

|--------------|------------|-------------------------------|---------------------------|------------------|-----|-------|-------------------------------------------------------|

| 90           | TSU:STA    | Start Condition<br>Setup Time | 100 kHz mode              | 2(Tosc)(BRG + 1) | —   |       | Only relevant for<br>Repeated Start condition         |

|              |            |                               | 400 kHz mode              | 2(Tosc)(BRG + 1) | —   |       |                                                       |

|              |            |                               | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —   |       |                                                       |

| 91           | 91 Thd:sta | Start Condition<br>Hold Time  | 100 kHz mode              | 2(Tosc)(BRG + 1) | —   | ns    | After this period, the first clock pulse is generated |

|              |            |                               | 400 kHz mode              | 2(Tosc)(BRG + 1) | —   |       |                                                       |

|              |            |                               | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —   |       |                                                       |

| 92           | 2 Tsu:sto  | Stop Condition<br>Setup Time  | 100 kHz mode              | 2(Tosc)(BRG + 1) | —   | ns    |                                                       |

|              |            |                               | 400 kHz mode              | 2(Tosc)(BRG + 1) | —   |       |                                                       |

|              |            |                               | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | —   |       |                                                       |

| 93           | THD:STO    | Stop Condition<br>Hold Time   | 100 kHz mode              | 2(Tosc)(BRG + 1) | —   | ns    |                                                       |

|              |            |                               | 400 kHz mode              | 2(Tosc)(BRG + 1) | —   |       |                                                       |

|              |            |                               | 1 MHz mode <sup>(1)</sup> | 2(Tosc)(BRG + 1) | _   |       |                                                       |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2C$  pins.

### FIGURE 26-23: MASTER SSP I<sup>2</sup>C BUS DATA TIMING

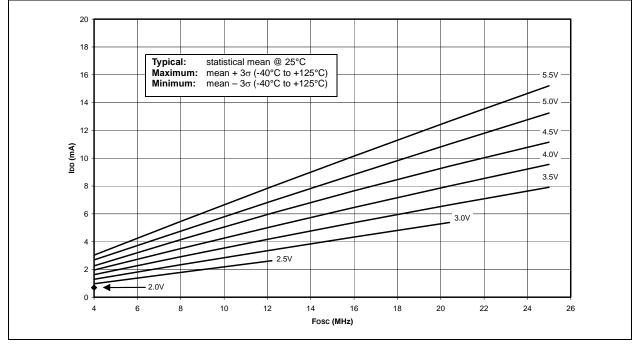

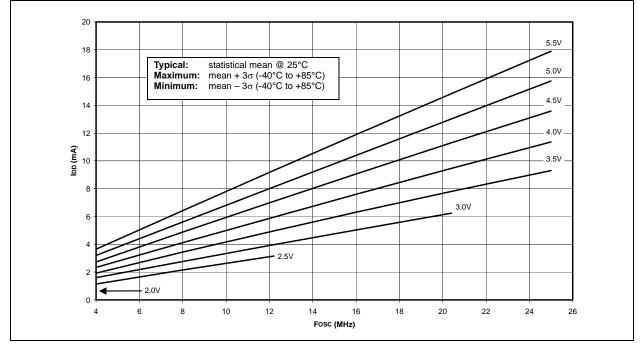

#### 27.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

# **Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean –  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

MAXIMUM IDD vs. Fosc OVER VDD (HS MODE) INDUSTRIAL

#### APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC17C756 to a PIC18F8720.

Not Currently Available

#### APPENDIX D: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442".* The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available as Literature Number DS00716.