Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 68                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8520-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The data memory map is in turn divided into 16 banks of 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory space contains both Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (0FFFh) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

PIC18FX520 devices have 2048 bytes of data RAM, extending from Bank 0 to Bank 7 (000h through 7FFh). PIC18FX620 and PIC18FX720 devices have 3840 bytes of data RAM, extending from Bank 0 to Bank 14 (000h through EFFh). The organization of the data memory space for these devices is shown in Figure 4-6 and Figure 4-7.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 4.10** "Access Bank" provides a detailed description of the Access RAM.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12 "Indirect Addressing, INDF and FSR Registers".

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as General Purpose Registers by all instructions. The top section of Bank 15 (F60h to FFFh) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2 and Table 4-3.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature. The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations are unimplemented and read as '0's. The addresses for the SFRs are listed in Table 4-2.

#### TABLE 4-2: SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                   | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|------------------------|---------|---------|---------|-----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(3)</sup>   | FBFh    | CCPR1H  | F9Fh    | IPR1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2(3)            | FBEh    | CCPR1L  | F9Eh    | PIR1                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(3)            | FBDh    | CCP1CON | F9Dh    | PIE1                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(3)</sup> | FBCh    | CCPR2H  | F9Ch    | MEMCON <sup>(2)</sup> |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(3)</sup>  | FBBh    | CCPR2L  | F9Bh    | (1)                   |

| FFAh    | PCLATH                  | FDAh    | FSR2H                  | FBAh    | CCP2CON | F9Ah    | TRISJ                 |

| FF9h    | PCL                     | FD9h    | FSR2L                  | FB9h    | CCPR3H  | F99h    | TRISH                 |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                 | FB8h    | CCPR3L  | F98h    | TRISG                 |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                  | FB7h    | CCP3CON | F97h    | TRISF                 |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                  | FB6h    | (1)     | F96h    | TRISE                 |

| FF5h    | TABLAT                  | FD5h    | T0CON                  | FB5h    | CVRCON  | F95h    | TRISD                 |

| FF4h    | PRODH                   | FD4h    | (1)                    | FB4h    | CMCON   | F94h    | TRISC                 |

| FF3h    | PRODL                   | FD3h    | OSCCON                 | FB3h    | TMR3H   | F93h    | TRISB                 |

| FF2h    | INTCON                  | FD2h    | LVDCON                 | FB2h    | TMR3L   | F92h    | TRISA                 |

| FF1h    | INTCON2                 | FD1h    | WDTCON                 | FB1h    | T3CON   | F91h    | LATJ                  |

| FF0h    | INTCON3                 | FD0h    | RCON                   | FB0h    | PSPCON  | F90h    | LATH                  |

| FEFh    | INDF0 <sup>(3)</sup>    | FCFh    | TMR1H                  | FAFh    | SPBRG1  | F8Fh    | LATG                  |

| FEEh    | POSTINC0 <sup>(3)</sup> | FCEh    | TMR1L                  | FAEh    | RCREG1  | F8Eh    | LATF                  |

| FEDh    | POSTDEC0 <sup>(3)</sup> | FCDh    | T1CON                  | FADh    | TXREG1  | F8Dh    | LATE                  |

| FECh    | PREINC0 <sup>(3)</sup>  | FCCh    | TMR2                   | FACh    | TXSTA1  | F8Ch    | LATD                  |

| FEBh    | PLUSW0 <sup>(3)</sup>   | FCBh    | PR2                    | FABh    | RCSTA1  | F8Bh    | LATC                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                  | FAAh    | EEADRH  | F8Ah    | LATB                  |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                 | FA9h    | EEADR   | F89h    | LATA                  |

| FE8h    | WREG                    | FC8h    | SSPADD                 | FA8h    | EEDATA  | F88h    | PORTJ                 |

| FE7h    | INDF1 <sup>(3)</sup>    | FC7h    | SSPSTAT                | FA7h    | EECON2  | F87h    | PORTH                 |

| FE6h    | POSTINC1 <sup>(3)</sup> | FC6h    | SSPCON1                | FA6h    | EECON1  | F86h    | PORTG                 |

| FE5h    | POSTDEC1 <sup>(3)</sup> | FC5h    | SSPCON2                | FA5h    | IPR3    | F85h    | PORTF                 |

| FE4h    | PREINC1 <sup>(3)</sup>  | FC4h    | ADRESH                 | FA4h    | PIR3    | F84h    | PORTE                 |

| FE3h    | PLUSW1 <sup>(3)</sup>   | FC3h    | ADRESL                 | FA3h    | PIE3    | F83h    | PORTD                 |

| FE2h    | FSR1H                   | FC2h    | ADCON0                 | FA2h    | IPR2    | F82h    | PORTC                 |

| FE1h    | FSR1L                   | FC1h    | ADCON1                 | FA1h    | PIR2    | F81h    | PORTB                 |

| FE0h    | BSR                     | FC0h    | ADCON2                 | FA0h    | PIE2    | F80h    | PORTA                 |

Note 1: Unimplemented registers are read as '0'.

2: This register is unused on PIC18F6X20 devices. Always maintain this register clear.

**3:** This is not a physical register.

| REGISTER 7-1: | EECON1 F                                                                                                                                                                       | REGISTER                                      | (ADDRES                                 | S FA6h)                        |                                         |              |             |             |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|--------------------------------|-----------------------------------------|--------------|-------------|-------------|

|               | R/W-x                                                                                                                                                                          | R/W-x                                         | U-0                                     | R/W-0                          | R/W-x                                   | R/W-0        | R/S-0       | R/S-0       |

|               | EEPGD                                                                                                                                                                          | CFGS                                          |                                         | FREE                           | WRERR                                   | WREN         | WR          | RD          |

|               | bit 7                                                                                                                                                                          |                                               |                                         |                                |                                         |              |             | bit 0       |

|               |                                                                                                                                                                                |                                               |                                         |                                |                                         |              |             |             |

| bit 7         |                                                                                                                                                                                | -                                             |                                         |                                | ry Select bit                           |              |             |             |

|               |                                                                                                                                                                                | s Flash prog<br>s data EEPR                   |                                         |                                |                                         |              |             |             |

| bit 6         |                                                                                                                                                                                | •                                             |                                         |                                | guration Sel                            | lect bit     |             |             |

|               |                                                                                                                                                                                | s configurati<br>s Flash prog                 |                                         |                                |                                         |              |             |             |

| bit 5         | Unimplem                                                                                                                                                                       | ented: Read                                   | <b>as</b> '0'                           |                                |                                         |              |             |             |

| bit 4         |                                                                                                                                                                                | sh Row Eras                                   |                                         |                                |                                         |              |             |             |

|               | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul> |                                               |                                         |                                |                                         |              |             | hand        |

| bit 3         | WRERR: F                                                                                                                                                                       | lash Progra                                   | m/Data EEF                              | ROM Error                      | Flag bit                                |              |             |             |

|               | (any M                                                                                                                                                                         | operation is<br>ICLR or any<br>rite operation | WDT Reset                               | t during self-                 | d<br>timed progra                       | amming in n  | ormal opera | ation)      |

|               | Note:                                                                                                                                                                          | When a Wittracing of the                      |                                         | •                              | GD or FRE                               | E bits are n | ot cleared. | This allows |

| bit 2         | WREN: Fla                                                                                                                                                                      | ish Program                                   | /Data EEPR                              | OM Write E                     | nable bit                               |              |             |             |

|               |                                                                                                                                                                                | write cycles<br>write cycles                  | •                                       | •                              |                                         |              |             |             |

| bit 1         | WR: Write                                                                                                                                                                      | Control bit                                   |                                         |                                |                                         |              |             |             |

|               | (The o<br>WR bit                                                                                                                                                               |                                               | elf-timed an<br>set (not cle            | d the bit is c<br>ared) in sof | or a progran<br>leared by ha<br>tware.) |              |             |             |

| bit 0         | RD: Read                                                                                                                                                                       | Control bit                                   |                                         |                                |                                         |              |             |             |

|               | can on                                                                                                                                                                         |                                               | ot cleared) ir                          | n software. F                  | ne cycle. RD<br>RD bit canno            |              |             |             |

|               |                                                                                                                                                                                |                                               |                                         |                                |                                         |              |             |             |

|               | Legend:                                                                                                                                                                        |                                               |                                         |                                |                                         |              |             |             |

|               | P - Roodo                                                                                                                                                                      | hla hit                                       | $\lambda \Lambda I = \lambda \Lambda I$ | ritable bit                    |                                         | nlomontod    | hit road as | ·^'         |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in four registers, RES3:RES0.

#### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L<br>(ARG1H • ARG2H • $2^{16}$ ) +<br>(ARG1H • ARG2L • $2^{8}$ ) + |

|-----------|---|--------------------------------------------------------------------------------------------|

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                                                      |

|           |   | $(ARG1L \bullet ARG2L)$                                                                    |

#### EXAMPLE 8-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                    |

|---|--------|-------------|--------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L -> |

|   |        |             | ; PRODH:PRODL      |

|   | MOVFF  | PRODH, RES1 | ;                  |

|   | MOVFF  | PRODL, RESO | ;                  |

| ; |        |             |                    |

|   | MOVF   | ARG1H, W    |                    |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H -> |

|   |        |             | ; PRODH:PRODL      |

|   | MOVFF  | PRODH, RES3 | ;                  |

|   | MOVFF  | PRODL, RES2 | ;                  |

| ; |        |             |                    |

|   | MOVF   | ARG1L, W    |                    |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H -> |

|   |        |             | ; PRODH:PRODL      |

|   |        | PRODL, W    | ;                  |

|   | ADDWF  | RES1, F     | ; Add cross        |

|   |        | PRODH, W    | ; products         |

|   | ADDWFC | RES2, F     | ;                  |

|   | CLRF   |             | ;                  |

|   | ADDWFC | RES3, F     | ;                  |

| ; |        |             |                    |

|   |        | ARG1H, W    | ;                  |

|   | MULWF  | ARG2L       | ; ARG1H * ARG2L -> |

|   |        |             | ; PRODH:PRODL      |

|   | MOVF   | -           | ;                  |

|   |        | RES1, F     |                    |

|   |        | PRODH, W    | ; products         |

|   |        | RES2, F     | ;                  |

|   | CLRF   |             | ;                  |

|   | ADDWFC | RES3, F     | ;                  |

|   |        |             |                    |

Example 8-4 shows the sequence to do a 16 x 16 signed multiply. Equation 8-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs' Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION

| RES3:RE | ES0 |

|---------|-----|

| =       | AI  |

### 0 ARG1H:ARG1L • ARG2H:ARG2L

| = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                        |

|---|-----------------------------------------------------------------|

|   | $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

|   | $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

|   | $(ARG1L \bullet ARG2L) +$                                       |

|   | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

|   | $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

|   |                                                                 |

#### EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF ARG1L, W      |                    |

|--------------------|--------------------|

| MULWF ARG2L        | ; ARG1L * ARG2L -> |

|                    | ; PRODH:PRODL      |

| MOVFF PRODH, RES1  | ;                  |

| MOVFF PRODL, RESO  | ;                  |

| ;                  |                    |

| MOVF ARG1H, W      |                    |

| MULWF ARG2H        | ; ARG1H * ARG2H -> |

|                    | ; PRODH:PRODL      |

| MOVFF PRODH, RES3  |                    |

| MOVFF PRODL, RES2  |                    |

| ;                  | 7                  |

| ,<br>MOVF ARG1L, W |                    |

| MULWF ARG2H        | ; ARG1L * ARG2H -> |

| MOLWF ARG2H        |                    |

|                    | ; PRODH:PRODL      |

| MOVF PRODL, W      | ;                  |

| ADDWF RES1, F      | ; Add cross        |

| MOVF PRODH, W      | ; products         |

| ADDWFC RES2, F     | ;                  |

| CLRF WREG          | ;                  |

| ADDWFC RES3, F     | ;                  |

| ;                  |                    |

| MOVF ARG1H, W      | ;                  |

| MULWF ARG2L        | ; ARG1H * ARG2L -> |

|                    | ; PRODH:PRODL      |

| MOVF PRODL, W      | ;                  |

| ADDWF RES1, F      | ; Add cross        |

|                    | ; products         |

| ADDWFC RES2, F     | ;                  |

| CLRF WREG          | i                  |

| ADDWFC RES3, F     | i                  |

| ;                  | 7                  |

|                    | · APC2H·APC2L neg2 |

|                    | ; ARG2H:ARG2L neg? |

|                    | ; no, check ARG1   |

| MOVF ARG1L, W      | ;                  |

| SUBWF RES2         | ;                  |

| MOVF ARG1H, W      | ;                  |

| SUBWFB RES3        |                    |

| ;                  |                    |

| SIGN_ARG1          |                    |

|                    | ; ARG1H:ARG1L neg? |

| BRA CONT_CODE      | ; no, done         |

| MOVF ARG2L, W      | ;                  |

| SUBWF RES2         | ;                  |

| MOVF ARG2H, W      | ;                  |

| SUBWFB RES3        |                    |

| ;                  |                    |

| CONT_CODE          |                    |

| :                  |                    |

| Name           | Bit#  | Buffer Type | Function                                                                             |

|----------------|-------|-------------|--------------------------------------------------------------------------------------|

| RF0/AN5        | bit 0 | ST          | Input/output port pin or analog input.                                               |

| RF1/AN6/C2OUT  | bit 1 | ST          | Input/output port pin, analog input or comparator 2 output.                          |

| RF2/AN7/C1OUT  | bit 2 | ST          | Input/output port pin, analog input or comparator 1 output.                          |

| RF3/AN8        | bit 3 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF4/AN9        | bit 4 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF5/AN10/CVREF | bit 5 | ST          | Input/output port pin, analog input/comparator input or comparator reference output. |

| RF6/AN11       | bit 6 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF7/SS         | bit 7 | ST/TTL      | Input/output port pin or slave select pin for synchronous serial port.               |

#### TABLE 10-11: PORTF FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

#### TABLE 10-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Name   | Bit 7   | Bit 6      | Bit 5     | Bit 4       | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|------------|-----------|-------------|-----------|-------|-------|-------|----------------------|---------------------------------|

| TRISF  | PORTF I | Data Direc | tion Con  | trol Regist | ter       |       |       |       | 1111 1111            | 1111 1111                       |

| PORTF  | Read PC | ORTF pin/  | Nrite PO  | RTF Data    | Latch     |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| LATF   | Read PC | ORTF Data  | a Latch/W | /rite POR   | FF Data L | atch. |       |       | 0000 0000            | uuuu uuuu                       |

| ADCON1 |         | _          | VCFG1     | VCFG0       | PCFG3     | PCFG2 | PCFG1 | PCFG0 | 00 0000              | 00 0000                         |

| CMCON  | C2OUT   | C1OUT      | C2INV     | C1INV       | CIS       | CM2   | CM1   | CM0   | 0000 0000            | 0000 0000                       |

| CVRCON | CVREN   | CVROE      | CVRR      | CVRSS       | CVR3      | CVR2  | CVR1  | CVR0  | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTF.

| Name        | Bit#  | Buffer Type | Function                                                                                                 |

|-------------|-------|-------------|----------------------------------------------------------------------------------------------------------|

| RG0/CCP3    | bit 0 | ST          | Input/output port pin or Capture3 input/Compare3 output/PWM3 output.                                     |

| RG1/TX2/CK2 | bit 1 | ST          | Input/output port pin, addressable USART2 asynchronous transmit or addressable USART2 synchronous clock. |

| RG2/RX2/DT2 | bit 2 | ST          | Input/output port pin, addressable USART2 asynchronous receive or addressable USART2 synchronous data.   |

| RG3/CCP4    | bit 3 | ST          | Input/output port pin or Capture4 input/Compare4 output/PWM4 output.                                     |

| RG4/CCP5    | bit 4 | ST          | Input/output port pin or Capture5 input/Compare5 output/PWM5 output.                                     |

#### TABLE 10-13: PORTG FUNCTIONS

Legend: ST = Schmitt Trigger input

#### TABLE 10-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4                                               | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-------|-------|-------|-----------------------------------------------------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTG | _     | _     |       | Read PORTF pin/Write PORTF Data Latch               |       |       |       |       |                      | u uuuu                          |

| LATG  | —     | _     |       | LATG Data Output Register x xxxxu uuu               |       |       |       |       |                      | u uuuu                          |

| TRISG | _     | _     | _     | Data Direction Control Register for PORTG1 11111 11 |       |       |       |       | 1 1111               |                                 |

**Legend:** x = unknown, u = unchanged

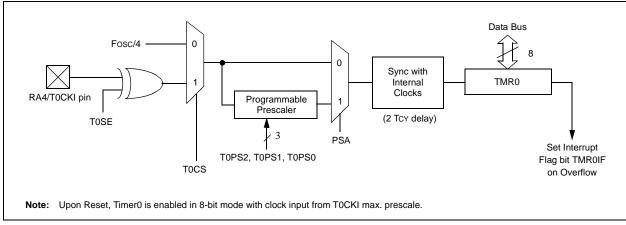

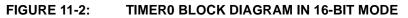

#### FIGURE 11-1: TIMER0 BLOCK DIAGRAM IN 8-BIT MODE

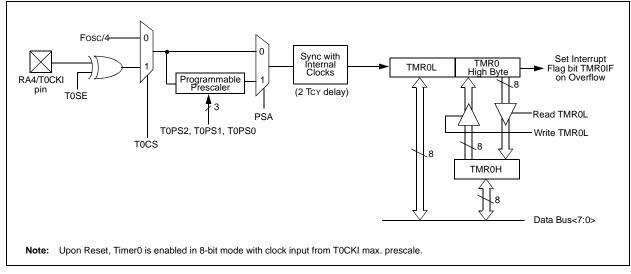

#### FIGURE 17-27: BUS COLLISION DURING START CONDITION (SCL = 0)

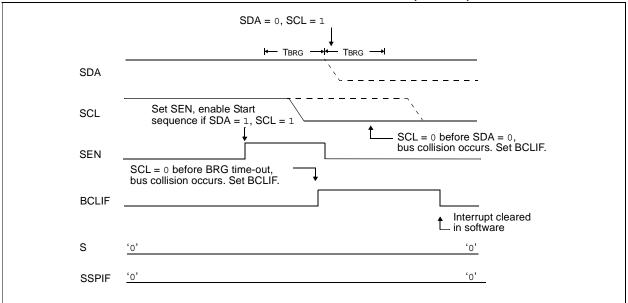

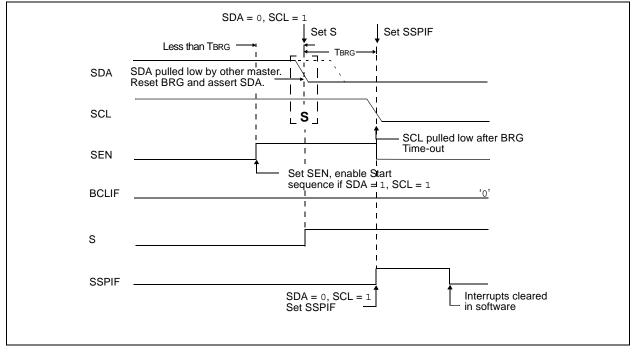

#### FIGURE 17-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

#### **REGISTER 19-2: ADCON1 REGISTER**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

|       | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

#### bit 7-6 Unimplemented: Read as '0'

#### bit 5-4 VCFG1:VCFG0: Voltage Reference Configuration bits:

| VCFG1<br>VCFG0 | A/D Vref+      | A/D VREF-      |  |  |  |

|----------------|----------------|----------------|--|--|--|

| 00             | AVdd           | AVss           |  |  |  |

| 01             | External VREF+ | AVss           |  |  |  |

| 10             | AVDD           | External VREF- |  |  |  |

| 11             | External VREF+ | External VREF- |  |  |  |

#### bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3<br>PCFG0 | AN15                                     | AN14 | AN13 | AN12 | AN11 | AN10 | AN9 | AN8 | AN7 | ANG | AN5 | AN4 | AN3 | AN2 | AN1 | ANO |

|----------------|------------------------------------------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000           | Α                                        | Α    | А    | Α    | Α    | Α    | Α   | Α   | А   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0001           | D                                        | D    | А    | А    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | Α   | А   |

| 0010           | D                                        | D    | D    | А    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | Α   | А   | А   |

| 0011           | D                                        | D    | D    | D    | Α    | А    | А   | Α   | А   | А   | А   | А   | Α   | Α   | А   | А   |

| 0100           | D                                        | D    | D    | D    | D    | А    | А   | Α   | А   | А   | А   | А   | Α   | А   | А   | Α   |

| 0101           | D                                        | D    | D    | D    | D    | D    | А   | Α   | А   | А   | А   | А   | Α   | Α   | А   | А   |

| 0110           | D                                        | D    | D    | D    | D    | D    | D   | Α   | А   | А   | А   | А   | А   | Α   | А   | А   |

| 0111           | D                                        | D    | D    | D    | D    | D    | D   | D   | А   | А   | А   | А   | Α   | А   | А   | А   |

| 1000           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | А   | А   | А   | А   | Α   | А   | А   |

| 1001           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | А   | А   | А   | Α   | А   | А   |

| 1010           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | А   | Α   | А   | Α   | А   |

| 1011           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | А   | А   | А   | А   |

| 1100           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | А   | А   | А   |

| 1101           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | А   | А   |

| 1110           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111           | D                                        | D    | D    | D    | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

| A _ Ana        | $\Delta = A palog input D = Digital I/O$ |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

A = Analog input D = Digital I/O

Note: Shaded cells indicate A/D channels available only on PIC18F8X20 devices.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

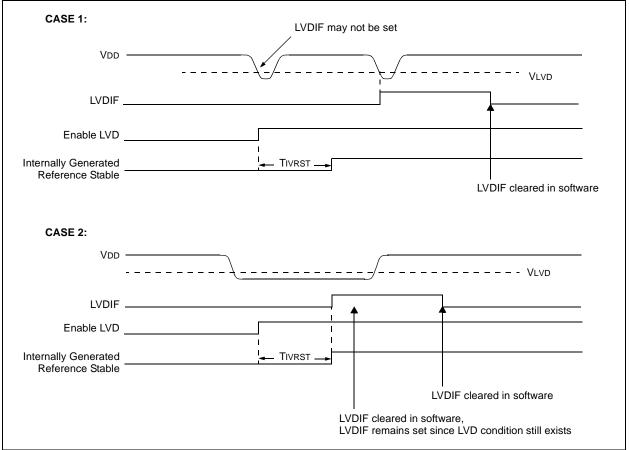

#### 22.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register), which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- Clear the LVD interrupt flag, which may have falsely become set, until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 22-4 shows typical waveforms that the LVD module may be used to detect.

### FIGURE 22-4: LOW-VOLTAGE DETECT WAVEFORMS

#### CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)<sup>(1)</sup> REGISTER 23-4: R/P-1 U-0 U-0 U-0 U-0 U-0 R/P-1 **R/P-1** WAIT PM1 PM0 bit 7 bit 0 bit 7 WAIT: External Bus Data Wait Enable bit 1 = Wait selections unavailable for table reads and table writes 0 = Wait selections for table reads and table writes are determined by the WAIT1:WAIT0 bits (MEMCOM<5:4>) bit 6-2 Unimplemented: Read as '0' PM1:PM0: Processor Mode Select bits bit 1-0 11 = Microcontroller mode 10 = Microprocessor mode 01 = Microprocessor with Boot Block mode 00 = Extended Microcontroller mode Note 1: This register is unimplemented in PIC18F6X20 devices; maintain these bits set. Legend: R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0' - n = Value when device is unprogrammed u = Unchanged from programmed state

#### REGISTER 23-5: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/P-1 | R/P-1  |

|-------|-----|-----|-----|-----|-----|-------|--------|

|       | —   | —   | —   | —   | —   | r(1)  | CCP2MX |

| bit 7 |     |     |     |     |     |       | bit 0  |

- bit 7-2 Unimplemented: Read as '0'

- bit 1 Reserved: Read as unknown<sup>(1)</sup>

- bit 0 CCP2MX: CCP2 Mux bit

- In Microcontroller mode:

- 1 = CCP2 input/output is multiplexed with RC1

- 0 = CCP2 input/output is multiplexed with RE7

In Microprocessor, Microprocessor with Boot Block and Extended Microcontroller modes (PIC18F8X20 devices only):

- 1 = CCP2 input/output is multiplexed with RC1

- 0 = CCP2 input/output is multiplexed with RB3

Note 1: Unimplemented in PIC18FX620 and PIC18FX720 devices; read as '0'.

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device | ce is unprogrammed   | u = Unchanged from programmed state |

#### REGISTER 23-12: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

| U-0   | R/P-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

|       | EBTRB |     | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

- bit 7 Unimplemented: Read as '0'

- bit 6 **EBTRB:** Boot Block Table Read Protection bit

For PIC18FX520 devices:

- 1 = Boot Block (000000-0007FFh) not protected from table reads executed in other blocks

- 0 = Boot Block (000000-0007FFh) protected from table reads executed in other blocks

- For PIC18FX620 and PIC18FX720 devices:

- 1 = Boot Block (000000-0001FFh) not protected from table reads executed in other blocks

- 0 = Boot Block (000000-0001FFh) protected from table reads executed in other blocks

- bit 5-0 Unimplemented: Read as '0'

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

#### REGISTER 23-13: DEVICE ID REGISTER 1 FOR PIC18FXX20 DEVICES (ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-5 **DEV2:DEV0:** Device ID bits

| 000 | = | PIC18F8720 |

|-----|---|------------|

| 001 | = | PIC18F6720 |

| 010 | = | PIC18F8620 |

| 011 | = | PIC18F6620 |

#### bit 4-0 REV4:REV0: Revision ID bits

These bits are used to indicate the device revision.

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

#### REGISTER 23-14: DEVICE ID REGISTER 2 FOR PIC18FXX20 DEVICES (ADDRESS 3FFFFFh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

| ΒZ                                                                 |                | Branch if                                                                      | Branch if Zero                                                                                                                                                                                                                                                                     |       |         |  |  |

|--------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--|--|

| Synt                                                               | ax:            | [ <i>label</i> ] B                                                             | Zn                                                                                                                                                                                                                                                                                 |       |         |  |  |

| Ope                                                                | rands:         | -128 ≤ n ≤                                                                     | 127                                                                                                                                                                                                                                                                                |       |         |  |  |

| Ope                                                                | ration:        | if Zero bit<br>(PC) + 2 +                                                      | is '1'<br>· 2n → PC                                                                                                                                                                                                                                                                |       |         |  |  |

| Statu                                                              | us Affected:   | None                                                                           |                                                                                                                                                                                                                                                                                    |       |         |  |  |

| Enco                                                               | oding:         | 1110                                                                           | 0000 r                                                                                                                                                                                                                                                                             | nnn   | nnnn    |  |  |

| Desc                                                               | cription:      | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | If the Zero bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |       |         |  |  |

| Word                                                               | ds:            | 1                                                                              |                                                                                                                                                                                                                                                                                    |       |         |  |  |

| Cycl                                                               | es:            | 1(2)                                                                           |                                                                                                                                                                                                                                                                                    |       |         |  |  |

|                                                                    | ycle Activity: |                                                                                |                                                                                                                                                                                                                                                                                    |       |         |  |  |

|                                                                    | Q1             | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                 |       | Q4      |  |  |

|                                                                    | Decode         | Read literal<br>'n'                                                            | Process<br>Data                                                                                                                                                                                                                                                                    | Write | e to PC |  |  |

|                                                                    | No             | No                                                                             | No                                                                                                                                                                                                                                                                                 |       | No      |  |  |

| IF NL                                                              | operation      | operation                                                                      | operation                                                                                                                                                                                                                                                                          | n ope | eration |  |  |

|                                                                    | o Jump:<br>Q1  | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                 |       | Q4      |  |  |

|                                                                    | Decode         | Read literal                                                                   | Process                                                                                                                                                                                                                                                                            |       | No      |  |  |

|                                                                    |                | 'n'                                                                            | Data                                                                                                                                                                                                                                                                               | оре   | eration |  |  |

| Example: HERE BZ Jump<br>Before Instruction<br>PC = address (HERE) |                |                                                                                |                                                                                                                                                                                                                                                                                    |       |         |  |  |

| PC = address (HERE)<br>After Instruction                           |                |                                                                                |                                                                                                                                                                                                                                                                                    |       |         |  |  |

|                                                                    | If Zero        | = 1;                                                                           |                                                                                                                                                                                                                                                                                    |       |         |  |  |

|                                                                    | PC<br>If Zero  | = 0;                                                                           | dress (Jun                                                                                                                                                                                                                                                                         | -     |         |  |  |

|                                                                    | PC             | = ad                                                                           | dress (HEF                                                                                                                                                                                                                                                                         | RE+2) |         |  |  |

|                                                                    |                |                                                                                |                                                                                                                                                                                                                                                                                    |       |         |  |  |

| CAL        | .L                                                                                                                                                                                                                                                                                                                             | Subrouti                                                               | Subroutine Call                                          |                          |                                                           |                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|-----------------------------------------------------------|----------------------------------------|

| Syn        | tax:                                                                                                                                                                                                                                                                                                                           | [label]                                                                | CALL k                                                   | [,s]                     |                                                           |                                        |

| Ope        | erands:                                                                                                                                                                                                                                                                                                                        | $0 \le k \le 10$<br>s $\in [0,1]$                                      | 0 ≤ k ≤ 1048575                                          |                          |                                                           |                                        |

| Ope        | eration:                                                                                                                                                                                                                                                                                                                       | $k \rightarrow PC < 2$<br>if s = 1<br>(W) $\rightarrow$ WS<br>(STATUS) | $(PC) + 4 \rightarrow TOS,$<br>$k \rightarrow PC<20:1>,$ |                          |                                                           |                                        |

| Stat       | us Affected:                                                                                                                                                                                                                                                                                                                   | None                                                                   |                                                          |                          |                                                           |                                        |

| 1st v      | oding:<br>word (k<7:0>)<br>word(k<19:8>                                                                                                                                                                                                                                                                                        |                                                                        | 110s<br>k <sub>19</sub> kkk                              | k <sub>7</sub> k}<br>kkk |                                                           | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |

|            | address (PC+ 4) is pushed onto th<br>return stack. If 's' = 1, the W,<br>Status and BSR registers are also<br>pushed into their respective<br>shadow registers, WS, STATUSS<br>and BSRS. If 's' = 0, no update<br>occurs (default). Then, the 20-bit<br>value 'k' is loaded into PC<20:1>.<br>CALL is a two-cycle instruction. |                                                                        |                                                          |                          | V,<br>are also<br>e<br>ATUSS<br>date<br>20-bit<br>:20:1>. |                                        |

| Wor        | ds:                                                                                                                                                                                                                                                                                                                            | 2                                                                      |                                                          |                          |                                                           |                                        |

| Сус        | les:                                                                                                                                                                                                                                                                                                                           | 2                                                                      |                                                          |                          |                                                           |                                        |

| QC         | Cycle Activity:                                                                                                                                                                                                                                                                                                                |                                                                        |                                                          |                          |                                                           |                                        |

|            | Q1                                                                                                                                                                                                                                                                                                                             | Q2                                                                     | Q                                                        | 3                        |                                                           | Q4                                     |

|            | Decode                                                                                                                                                                                                                                                                                                                         | Read literal<br>'k'<7:0>                                               | Push P<br>stac                                           |                          | 'k'                                                       | ad literal<br><19:8>,<br>ite to PC     |

|            | No                                                                                                                                                                                                                                                                                                                             | No                                                                     | No                                                       |                          |                                                           | No                                     |

|            | operation                                                                                                                                                                                                                                                                                                                      | operation                                                              | opera                                                    | tion                     | op                                                        | peration                               |

| <u>Exa</u> | mple:                                                                                                                                                                                                                                                                                                                          | HERE                                                                   | HERE CALL THERE, 1                                       |                          |                                                           |                                        |

|            | Before Instruc                                                                                                                                                                                                                                                                                                                 |                                                                        |                                                          |                          |                                                           |                                        |

|            | PC                                                                                                                                                                                                                                                                                                                             | = address                                                              | S (HERE                                                  | )                        |                                                           |                                        |

|            | After Instructi<br>PC<br>TOS<br>WS<br>BSRS                                                                                                                                                                                                                                                                                     | on<br>= address<br>= address<br>= W<br>= BSR                           |                                                          |                          |                                                           |                                        |

BSRS = BSR STATUSS = STATUS

| INCF            | -SZ                             | Incremer                                                                                                                                | nt f, skip                                                                                                                                                                                                                                                                                               | if O           |                        |  |  |

|-----------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|--|--|

| Synt            | ax:                             | [ label ]                                                                                                                               | INCFSZ                                                                                                                                                                                                                                                                                                   | <u>f</u> f [,c | l [,a]                 |  |  |

| Ope             | rands:                          | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                     | 5                                                                                                                                                                                                                                                                                                        |                |                        |  |  |

| Ope             | ration:                         | (f) + 1 $\rightarrow$ skip if res                                                                                                       |                                                                                                                                                                                                                                                                                                          |                |                        |  |  |

| Statu           | us Affected:                    | None                                                                                                                                    |                                                                                                                                                                                                                                                                                                          |                |                        |  |  |

| Enco            | oding:                          | 0011                                                                                                                                    | 11da                                                                                                                                                                                                                                                                                                     | fff            | f ffff                 |  |  |

| Desc            | cription:                       | increment<br>is placed<br>(default).<br>If the resu<br>instruction<br>is discard<br>instead, n<br>instruction<br>Bank will<br>the BSR v | If the result is '0', the next<br>instruction which is already fetched<br>is discarded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the |                |                        |  |  |

| Word            | ds:                             | 1                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                        |                |                        |  |  |

| Cycl            |                                 | by                                                                                                                                      | ycles if s<br>a 2-wore                                                                                                                                                                                                                                                                                   |                | nd followed<br>uction. |  |  |

| QU              | ycle Activity:<br>Q1            | Q2                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                       | R              | Q4                     |  |  |

|                 | Decode                          | Read<br>register 'f'                                                                                                                    | Proce                                                                                                                                                                                                                                                                                                    | SS             | Write to destination   |  |  |

| lf sk           | kip:                            | .09.000                                                                                                                                 | Duk                                                                                                                                                                                                                                                                                                      |                | acculation             |  |  |

|                 | Q1                              | Q2                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                       | 3              | Q4                     |  |  |

|                 | No                              | No                                                                                                                                      | No                                                                                                                                                                                                                                                                                                       |                | No                     |  |  |

| lfck            | operation                       | operation                                                                                                                               | operat<br>operat                                                                                                                                                                                                                                                                                         |                | operation              |  |  |

| 11 51           | Q1                              | Q2                                                                                                                                      | Q3                                                                                                                                                                                                                                                                                                       |                | Q4                     |  |  |

| 1               | No                              | No                                                                                                                                      | No                                                                                                                                                                                                                                                                                                       |                | No                     |  |  |

|                 | operation                       | operation                                                                                                                               | operat                                                                                                                                                                                                                                                                                                   | ion            | operation              |  |  |

| No<br>operation |                                 | No<br>operation                                                                                                                         | No<br>operat                                                                                                                                                                                                                                                                                             |                | No<br>operation        |  |  |

| Example:        |                                 | HERE<br>NZERO<br>ZERO                                                                                                                   | INCFSZ<br>:<br>:                                                                                                                                                                                                                                                                                         | CNI            | 2, 1, 0                |  |  |