Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8520t-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

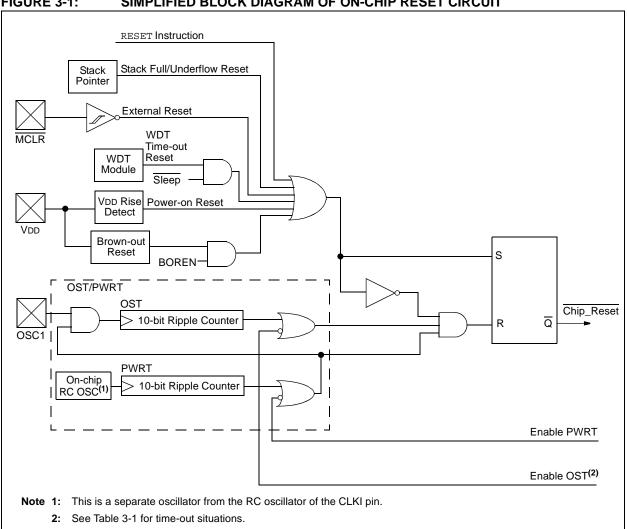

#### 3.0 RESET

The PIC18FXX20 devices differentiate between various kinds of Reset:

- Power-on Reset (POR) a)

- b) MCLR Reset during normal operation

- MCLR Reset during Sleep C)

- Watchdog Timer (WDT) Reset (during normal d) operation)

- Programmable Brown-out Reset (PBOR) e)

- f) **RESET** Instruction

- Stack Full Reset g)

- h) Stack Underflow Reset

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" on Power-on Reset, MCLR, WDT Reset, Brownout Reset, MCLR Reset during Sleep and by the RESET instruction.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ , PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 3-2. These bits are used in software to determine the nature of the Reset. See Table 3-3 for a full description of the Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The Enhanced MCU devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses. The MCLR pin is not driven low by any internal Resets, including the WDT.

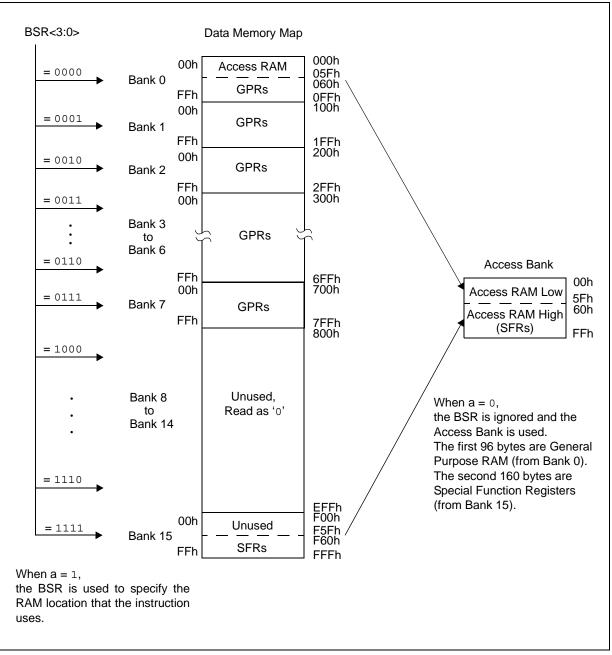

#### FIGURE 4-6: DATA MEMORY MAP FOR PIC18FX520 DEVICES

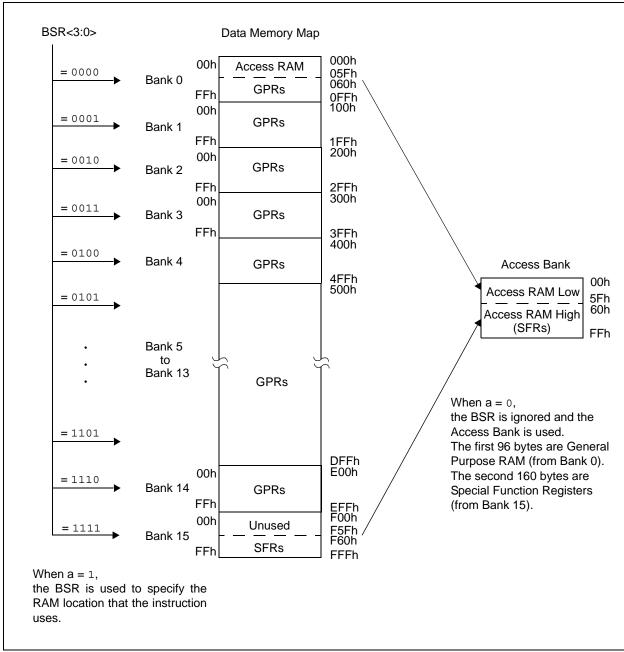

#### FIGURE 4-7: DATA MEMORY MAP FOR PIC18FX620 AND PIC18FX720 DEVICES

| File Name | Bit 7                                                                                                  | Bit 6                              | Bit 5                 | Bit 4          | Bit 3                       | Bit 2          | Bit 1            | Bit 0     | Value on<br>POR, BOR | Details on page: |  |  |

|-----------|--------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|----------------|-----------------------------|----------------|------------------|-----------|----------------------|------------------|--|--|

| TOSU      | _                                                                                                      | 0 0000                             | 32, 42                |                |                             |                |                  |           |                      |                  |  |  |

| TOSH      | Top-of-Stack                                                                                           | Fop-of-Stack High Byte (TOS<15:8>) |                       |                |                             |                |                  |           |                      |                  |  |  |

| TOSL      | Top-of-Stack                                                                                           | Low Byte (TC                       | )S<7:0>)              |                |                             |                |                  |           | 0000 0000            | 32, 42           |  |  |

| STKPTR    | STKFUL                                                                                                 | STKUNF                             | —                     | Return Stack   | Pointer                     |                |                  |           | 00-0 0000            | 32, 43           |  |  |

| PCLATU    | —                                                                                                      |                                    | bit 21                | Holding Regi   | ster for PC<20              | ):16>          |                  |           | 10 0000              | 32, 44           |  |  |

| PCLATH    | Holding Reg                                                                                            | Holding Register for PC<15:8>      |                       |                |                             |                |                  |           |                      |                  |  |  |

| PCL       | PC Low Byte                                                                                            | e (PC<7:0>)                        |                       |                |                             |                |                  |           | 0000 0000            | 32, 44           |  |  |

| TBLPTRU   | —                                                                                                      | _                                  | bit 21 <sup>(2)</sup> | Program Mer    | nory Table Poi              | nter Upper By  | te (TBLPTR<2     | 0:16>)    | 00 0000              | 32, 64           |  |  |

| TBLPTRH   | Program Me                                                                                             | mory Table Po                      | ointer High By        | te (TBLPTR<    | 15:8>)                      |                |                  |           | 0000 0000            | 32, 64           |  |  |

| TBLPTRL   | Program Me                                                                                             | mory Table Po                      | ointer Low Byt        | e (TBLPTR<7    | ':0>)                       |                |                  |           | 0000 0000            | 32, 64           |  |  |

| TABLAT    | Program Me                                                                                             | mory Table La                      | itch                  |                |                             |                |                  |           | 0000 0000            | 32, 64           |  |  |

| PRODH     | Product Reg                                                                                            | ister High Byte                    | Э                     |                |                             |                |                  |           | xxxx xxxx            | 32, 85           |  |  |

| PRODL     | Product Reg                                                                                            | ister Low Byte                     | )                     |                |                             |                |                  |           | xxxx xxxx            | 32, 85           |  |  |

| INTCON    | GIE/GIEH                                                                                               | PEIE/GIEL                          | TMR0IE                | INT0IE         | RBIE                        | TMR0IF         | <b>INT0IF</b>    | RBIF      | 0000 0000            | 32, 89           |  |  |

| INTCON2   | RBPU                                                                                                   | INTEDG0                            | INTEDG1               | INTEDG2        | INTEDG3                     | TMR0IP         | INT3IP           | RBIP      | 1111 1111            | 32, 90           |  |  |

| INTCON3   | INT2IP                                                                                                 | INT1IP                             | INT3IE                | INT2IE         | INT1IE                      | INT3IF         | INT2IF           | INT1IF    | 1100 0000            | 32, 91           |  |  |

| INDF0     | Uses conten                                                                                            | ts of FSR0 to a                    | iddress data n        | nemory – value | e of FSR0 not o             | changed (not a | physical regis   | ter)      | n/a                  | 57               |  |  |

| POSTINC0  | Uses content<br>(not a physic                                                                          |                                    | iddress data n        | nemory – value | e of FSR0 post              | -incremented   |                  |           | n/a                  | 57               |  |  |

| POSTDEC0  |                                                                                                        | ts of FSR0 to a                    | iddress data n        | nemory – value | e of FSR0 post              | -decremented   |                  |           | n/a                  | 57               |  |  |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) |                                    |                       |                |                             |                |                  |           |                      | 57               |  |  |

| PLUSW0    | Uses conten                                                                                            |                                    | address data          | memory – val   | ue of FSR0 pr               |                |                  |           | n/a                  | 57               |  |  |

| FSR0H     | —                                                                                                      | _                                  | _                     | _              |                             | Memory Addr    | ess Pointer 0    | High Byte | 0000                 | 32, 57           |  |  |

| FSR0L     | Indirect Data                                                                                          | Memory Add                         | ress Pointer (        | Low Byte       |                             | ,              |                  | <u> </u>  | xxxx xxxx            | 32, 57           |  |  |

| WREG      | Working Reg                                                                                            | gister                             |                       |                |                             |                |                  |           | xxxx xxxx            | 32               |  |  |

| INDF1     |                                                                                                        | -                                  | address data          | memory – val   | ue of FSR1 no               | t changed (no  | t a physical re  | gister)   | n/a                  | 57               |  |  |

| POSTINC1  |                                                                                                        | ts of FSR1 to                      |                       | -              | ue of FSR1 po               |                |                  | <u> </u>  | n/a                  | 57               |  |  |

| POSTDEC1  |                                                                                                        | ts of FSR1 to                      | address data          | memory – val   | ue of FSR1 po               | st-decrement   | ed               |           | n/a                  | 57               |  |  |

| PREINC1   | Uses conten<br>(not a physic                                                                           |                                    | address data          | memory – val   | ue of FSR1 pr               | e-incremented  | 1                |           | n/a                  | 57               |  |  |

| PLUSW1    |                                                                                                        | ts of FSR1 to<br>al register) – v  |                       |                | ue of FSR1 pr<br>ie in WREG | e-incremented  | 1                |           | n/a                  | 57               |  |  |

| FSR1H     | —                                                                                                      | —                                  | —                     | —              |                             | Memory Addr    | ess Pointer 1    | High Byte | 0000                 | 33, 57           |  |  |

| FSR1L     | Indirect Data                                                                                          | Memory Add                         | ress Pointer 1        | Low Byte       |                             |                |                  |           | xxxx xxxx            | 33, 57           |  |  |

| BSR       |                                                                                                        | —                                  | —                     | —              | Bank Select I               | Register       |                  |           | 0000                 | 33, 56           |  |  |

| INDF2     | Uses conten                                                                                            | ts of FSR2 to                      | address data          | memory – val   | ue of FSR2 no               | t changed (no  | ot a physical re | egister)  | n/a                  | 57               |  |  |

| POSTINC2  | Uses conten<br>(not a physic                                                                           |                                    | address data          | memory – val   | ue of FSR2 po               | st-incremente  | ed               |           | n/a                  | 57               |  |  |

| POSTDEC2  |                                                                                                        | ts of FSR2 to                      | address data          | memory – val   | ue of FSR2 po               | st-decrement   | ed               |           | n/a                  | 57               |  |  |

### TABLE 4-3: REGISTER FILE SUMMARY

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator modes only and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers are unused on PIC18F6X20 devices; always maintain these clear.

## 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

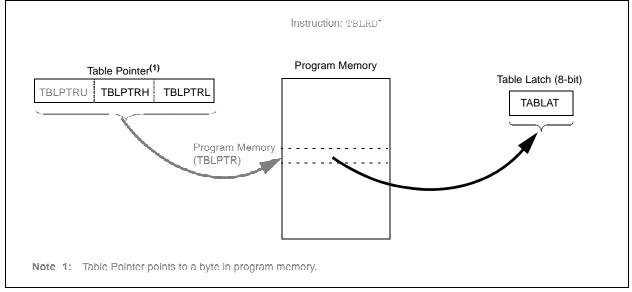

### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

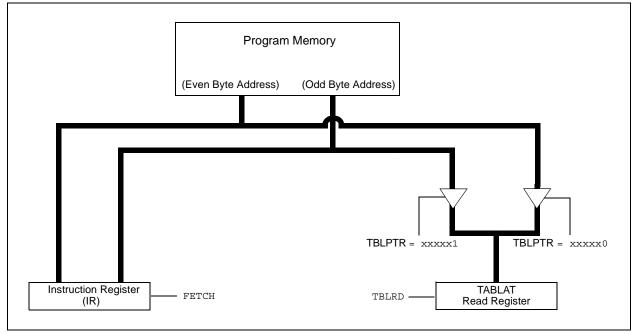

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

## FIGURE 5-1: TABLE READ OPERATION

#### 5.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 5-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 5-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 5-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE ADDR HIGH |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------|----------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                   | TBLPTRH                                      |   |                                                  |

|           | MOVLW                   | CODE_ADDR_LOW                                |   |                                                  |

|           | MOVWF                   | TBLPTRL                                      |   |                                                  |

| READ_WORD |                         |                                              |   |                                                  |

|           | TBLRD*-                 | F                                            | ; | read into TABLAT and increment                   |

|           | MOVF                    | TABLAT, W                                    | ; | get data                                         |

|           | MOVWF                   | WORD_EVEN                                    |   |                                                  |

|           | TBLRD*-                 | F                                            | ; | read into TABLAT and increment                   |

|           | MOVFW                   | TABLAT, W                                    | ; | get data                                         |

|           | MOVWF                   | WORD_ODD                                     |   |                                                  |

## 8.0 8 X 8 HARDWARE MULTIPLIER

### 8.1 Introduction

An 8 x 8 hardware multiplier is included in the ALU of the PIC18FXX20 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored in the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the ALUSTA register.

Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between enhanced devices using the single-cycle hardware multiply and performing the same function without the hardware multiply.

### 8.2 Operation

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

## EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |                |

|-------|-------|---|---|----------------|

| MULWF | ARG2  |   | ; | ARG1 * ARG2 -> |

|       |       |   | ; | PRODH:PRODL    |

|       |       |   |   |                |

## EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY

| _ |       |          | RC | DUTINE         |

|---|-------|----------|----|----------------|

|   | MOVF  | ARG1, W  | ;  |                |

|   | MULWF | ARG2     | ;  | ARG1 * ARG2 -> |

|   |       |          | ;  | PRODH: PRODL   |

|   | BTFSC | ARG2, SB | ;  | Test Sign Bit  |

|   | SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|   |       |          | ;  | - ARG1         |

|   | MOVF  | ARG2, W  | ;  |                |

|   | BTFSC | ARG1, SB | ;  | Test Sign Bit  |

|   | SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|   |       |          | ;  | - ARG2         |

|   |       |          |    |                |

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| Q v Q uppignod   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 9 x 9 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16 x 16 uppigpod | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4.0 μs   | 16.0 μs  | 40 μs   |  |

## TABLE 8-1: PERFORMANCE COMPARISON

| =R 9-12: | IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3                                                        |             |          |             |          |           |                |        |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------|-------------|----------|-------------|----------|-----------|----------------|--------|--|--|--|--|--|

|          | U-0                                                                                                   | U-0         | R/W-1    | R/W-1       | R/W-1    | R/W-1     | R/W-1          | R/W-1  |  |  |  |  |  |

|          |                                                                                                       | —           | RC2IP    | TX2IP       | TMR4IP   | CCP5IP    | CCP4IP         | CCP3IP |  |  |  |  |  |

|          | bit 7                                                                                                 |             |          |             |          |           |                | bit 0  |  |  |  |  |  |

|          |                                                                                                       |             |          |             |          |           |                |        |  |  |  |  |  |

| bit 7-6  | Unimplem                                                                                              | ented: Read | d as '0' |             |          |           |                |        |  |  |  |  |  |

| bit 5    | RC2IP: USART2 Receive Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                 |             |          |             |          |           |                |        |  |  |  |  |  |

| bit 4    | <b>TX2IP:</b> USART2 Transmit Interrupt Priority bit<br>1 = High priority<br>0 = Low priority         |             |          |             |          |           |                |        |  |  |  |  |  |

| bit 3    | <b>TMR4IP:</b> TMR4 to PR4 Match Interrupt Priority bit<br>1 = High priority<br>0 = Low priority      |             |          |             |          |           |                |        |  |  |  |  |  |

| bit 2-0  | CCPxIP: CCPx Interrupt Priority bit (CCP Modules 3, 4 and 5)<br>1 = High priority<br>0 = Low priority |             |          |             |          |           |                |        |  |  |  |  |  |

|          | Legend:                                                                                               |             |          |             |          |           |                |        |  |  |  |  |  |

|          | R = Reada                                                                                             | ble bit     | W = W    | ritable bit | U = Unim | plemented | bit, read as ' | 0'     |  |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 9-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

- n = Value at POR

| REGISTER 17-3: | SSPSTA                                                                | T: MSSP S                                                                                                                                                                                                                                 | TATUS RE                 | GISTER (I   | <sup>2</sup> C MODE)         |                                    |                |            |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|------------------------------|------------------------------------|----------------|------------|--|--|--|--|--|

|                | R/W-0                                                                 | R/W-0                                                                                                                                                                                                                                     | R-0                      | R-0         | ,<br>R-0                     | R-0                                | R-0            | R-0        |  |  |  |  |  |

|                | SMP                                                                   | CKE                                                                                                                                                                                                                                       | D/A                      | Р           | S                            | R/W                                | UA             | BF         |  |  |  |  |  |

|                | bit 7                                                                 | bit 7                                                                                                                                                                                                                                     |                          |             |                              |                                    |                |            |  |  |  |  |  |

| bit 7          | In Master of<br>1 = Slew r                                            | <ul> <li>SMP: Slew Rate Control bit</li> <li>In Master or Slave mode:</li> <li>1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)</li> <li>0 = Slew rate control enabled for high-speed mode (400 kHz)</li> </ul> |                          |             |                              |                                    |                |            |  |  |  |  |  |

| bit 6          | CKE: SMB                                                              | CKE: SMBus Select bit                                                                                                                                                                                                                     |                          |             |                              |                                    |                |            |  |  |  |  |  |

| bit 5          | 1 = Enable<br>0 = Disable                                             | In Master or Slave mode:<br>1 = Enable SMBus specific inputs<br>0 = Disable SMBus specific inputs<br>D/A: Data/Address bit                                                                                                                |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                | <u>In Master r</u><br>Reserved.                                       | <u>node:</u>                                                                                                                                                                                                                              |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                |                                                                       | es that the la                                                                                                                                                                                                                            |                          |             | smitted was<br>smitted was   |                                    |                |            |  |  |  |  |  |

| bit 4          | P: Stop bit                                                           |                                                                                                                                                                                                                                           |                          |             | 1                            |                                    |                |            |  |  |  |  |  |

|                | 0 = Stop bi                                                           | es that a Sto<br>t was not de                                                                                                                                                                                                             | tected last              |             |                              |                                    |                |            |  |  |  |  |  |

|                | Note:                                                                 |                                                                                                                                                                                                                                           | leared on Re             | eset and wh | ien SSPEN i                  | s cleared.                         |                |            |  |  |  |  |  |

| bit 3          | S: Start bit                                                          |                                                                                                                                                                                                                                           |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                | 0 = Start bi                                                          | es that a Sta<br>t was not de                                                                                                                                                                                                             | tected last              |             |                              |                                    |                |            |  |  |  |  |  |

|                | Note:                                                                 |                                                                                                                                                                                                                                           |                          |             | ien SSPEN i                  | s cleared.                         |                |            |  |  |  |  |  |

| bit 2          |                                                                       | I/Write bit Inf                                                                                                                                                                                                                           | ormation (I <sup>2</sup> | C mode onl  | y)                           |                                    |                |            |  |  |  |  |  |

|                | <u>In Slave m</u><br>1 = Read<br>0 = Write                            | <u>ode:</u>                                                                                                                                                                                                                               |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                | Note:                                                                 |                                                                                                                                                                                                                                           |                          |             |                              | ne last addres<br>bit, Stop bit, o |                |            |  |  |  |  |  |

|                |                                                                       | <u>node:</u><br>nit is in progr<br>nit is not in p                                                                                                                                                                                        |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                | Note:                                                                 | ORing this in active mo                                                                                                                                                                                                                   |                          | I, RSEN, PE | EN, RCEN o                   | r ACKEN will                       | indicate if th | ie MSSP is |  |  |  |  |  |

| bit 1          | -                                                                     | e Address b                                                                                                                                                                                                                               | -                        |             |                              |                                    |                |            |  |  |  |  |  |

|                |                                                                       | es that the u<br>is does not r                                                                                                                                                                                                            |                          |             | address in t                 | he SSPADD                          | register       |            |  |  |  |  |  |

| bit 0          |                                                                       | Full Status b                                                                                                                                                                                                                             | bit                      |             |                              |                                    |                |            |  |  |  |  |  |

|                | <u>In Transmit mode:</u><br>1 = SSPBUF is full<br>0 = SSPBUF is empty |                                                                                                                                                                                                                                           |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                |                                                                       | JF is full (do                                                                                                                                                                                                                            |                          |             | and Stop bits<br>CK and Stop |                                    |                |            |  |  |  |  |  |

|                | Legend:                                                               |                                                                                                                                                                                                                                           |                          |             |                              |                                    |                |            |  |  |  |  |  |

|                | R = Reada                                                             | ble bit                                                                                                                                                                                                                                   | W = Writab               | le bit      | U = Unimp                    | lemented bit,                      | , read as '0'  |            |  |  |  |  |  |

|                | - n = Value                                                           | at POR                                                                                                                                                                                                                                    | '1' = Bit is s           | set         | '0' = Bit is                 | cleared                            | x = Bit is un  | known      |  |  |  |  |  |

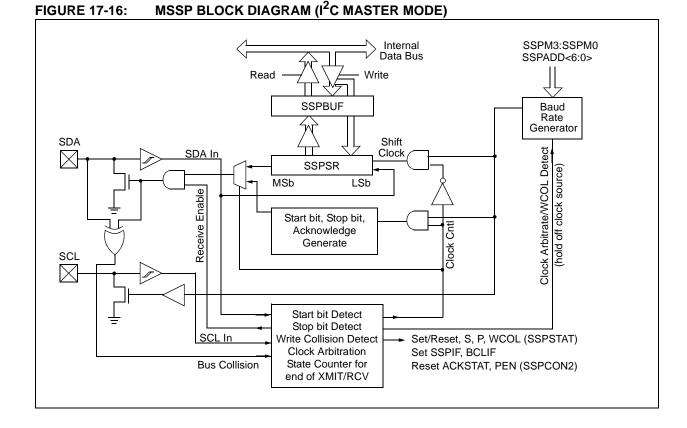

#### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- Start Condition

- Stop Condition

- Data Transfer Byte Transmitted/received

- Acknowledge Transmit

- Repeated Start

© 2003-2013 Microchip Technology Inc.

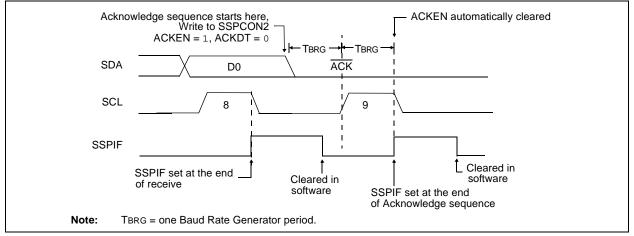

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

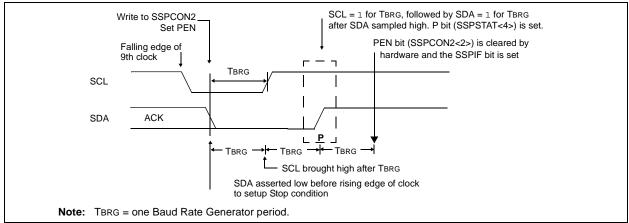

#### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

#### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 17-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, Figure 17-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

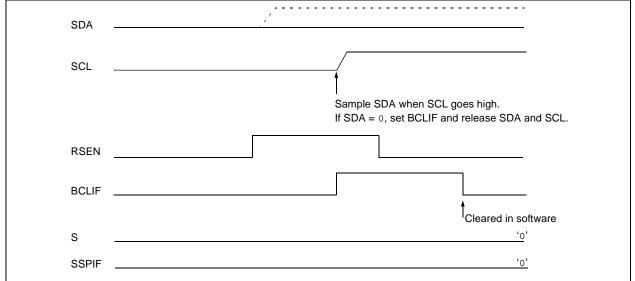

#### FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

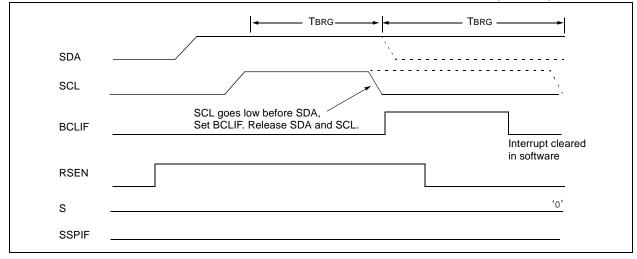

#### FIGURE 17-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### 18.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USARTs. It is a dedicated 8-bit Baud Rate Generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTAx<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGx register can be calculated using the formula in Table 18-1. From this, the error in baud rate can be determined. Example 18-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the equation in Example 18-1 can reduce the baud rate error in some cases.

Writing a new value to the SPBRGx register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 18.1.1 SAMPLING

The data on the RXx pin (either RC7/RX1/DT1 or RG2/ RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the pin.

| EXAMPLE 18-1: CALCULATING BAUD RATE ER |

|----------------------------------------|

|----------------------------------------|

| $\mathbf{L}$         |                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Desired Baud Rate    | = Fosc/(64 (X + 1))                                                                                                                    |

| Solving for X:       |                                                                                                                                        |

| X<br>X<br>X<br>X     | = ((Fosc/Desired Baud Rate)/64) - 1<br>= ((16000000/9600)/64) - 1<br>= [25.042] = 25                                                   |

| Calculated Baud Rate | = 1600000/(64 (25 + 1)) = 9615                                                                                                         |

| Error                | <ul> <li><u>(Calculated Baud Rate – Desired Baud Rate)</u><br/>Desired Baud Rate</li> <li>(9615 – 9600)/9600</li> <li>0.16%</li> </ul> |

|                      |                                                                                                                                        |

#### TABLE 18-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                        | BRGH = 1 (High Speed)        |

|------|---------------------------------------------|------------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X + 1)) | Baud Rate = Fosc/(16(X + 1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X + 1))   | N/A                          |

**Legend:** X = value in SPBRGx (0 to 255)

### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name   | Bit 7    | Bit 6                                            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |  |

|--------|----------|--------------------------------------------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|--|--|

| TXSTAx | CSRC     | TX9                                              | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |  |  |

| RCSTAx | SPEN     | RX9                                              | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x            | 0000 000x                       |  |  |

| SPBRGx | Baud Rat | Baud Rate Generator Register 0000 0000 0000 0000 |       |       |       |       |       |       |                      |                                 |  |  |

| 1      |          |                                                  |       |       |       |       |       |       |                      |                                 |  |  |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

**Note 1:** Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

| 5151ER 23-2:                       | CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h) |                   |               |             |           |            |              |          |

|------------------------------------|---------------------------------------------------------------|-------------------|---------------|-------------|-----------|------------|--------------|----------|

|                                    | U-0                                                           | U-0               | U-0           | U-0         | R/P-1     | R/P-1      | R/P-1        | R/P-1    |

|                                    | —                                                             | —                 | —             | —           | BORV1     | BORV0      | BOREN        | PWRTEN   |

|                                    | bit 7                                                         |                   |               |             |           |            |              | bit 0    |

|                                    |                                                               |                   | <i>.</i> .    |             |           |            |              |          |

| bit 7-4 Unimplemented: Read as '0' |                                                               |                   |               |             |           |            |              |          |

| bit 3-2                            | BORV1:BO                                                      | RV0: Brown        | -out Reset Ve | oltage bits |           |            |              |          |

|                                    | 11 = VBOR :                                                   | set to 2.5V       |               |             |           |            |              |          |

|                                    | 10 = VBOR :                                                   | set to 2.7V       |               |             |           |            |              |          |

|                                    | 01 = VBOR S                                                   | set to 4.2V       |               |             |           |            |              |          |

|                                    | 00 = VBOR                                                     | set to 4.5V       |               |             |           |            |              |          |

| bit 1                              | bit 1 BOREN: Brown-out Reset Enable bit                       |                   |               |             |           |            |              |          |

|                                    | 1 = Brown-o                                                   | out Reset ena     | abled         |             |           |            |              |          |

| 0 = Brown-out Reset disabled       |                                                               |                   |               |             |           |            |              |          |

| bit 0                              | PWRTEN: Power-up Timer Enable bit                             |                   |               |             |           |            |              |          |

|                                    | 1 = PWRT (                                                    | 1 = PWRT disabled |               |             |           |            |              |          |

| 0 = PWRT enabled                   |                                                               |                   |               |             |           |            |              |          |

|                                    |                                                               |                   |               |             |           |            |              |          |

|                                    | Legend:                                                       |                   |               |             |           |            |              |          |

|                                    | R = Reada                                                     | ble bit           | P = Progra    | mmable bit  | U = Unim  | plemented  | bit, read as | s 'O'    |

|                                    | - n = Value                                                   | when device       | is unprogra   | mmed        | u = Uncha | anged from | programm     | ed state |

#### REGISTER 23-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

#### REGISTER 23-3: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

| U-0   | U-0 | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  | R/P-1 |

|-------|-----|-----|-----|--------|--------|--------|-------|

| —     | —   | —   | —   | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN |

| bit 7 |     |     |     |        |        |        | bit 0 |

- bit 7-4 Unimplemented: Read as '0'

- bit 3-1 WDTPS2:WDTPS0: Watchdog Timer Postscale Select bits

- 111 = 1:128 110 = 1:64 101 = 1:32 100 = 1:16 011 = 1:8 010 = 1:4

- 001 = 1:2

- 000 = 1:1

- bit 0 WDTEN: Watchdog Timer Enable bit

- 1 = WDT enabled

- 0 = WDT disabled (control is placed on the SWDTEN bit)

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devi | ce is unprogrammed   | u = Unchanged from programmed state |

#### 23.4.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 23.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write-protected. The WRTC bit controls protection of the configuration registers. In user mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 23.5 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

### 23.6 In-Circuit Serial Programming

PIC18FX520/X620/X720 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

| Note: | When     | performing           | In-Circuit            | Serial  |

|-------|----------|----------------------|-----------------------|---------|

|       | Progran  | nming, verify        | that power            | is con- |

|       | nected   | to <b>all</b> VDD ar | nd AVDD pins          | of the  |

|       | microco  | ntroller and th      | nat <b>all</b> Vss an | d AVss  |

|       | pins are | grounded.            |                       |         |

## 23.7 In-Circuit Debugger

When the DEBUG bit in the CONFIG4L Configuration register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 23-4 shows which features are consumed by the background debugger.

#### TABLE 23-4: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7       |

|----------------|----------------|

| Stack          | 2 levels       |

| Program Memory | Last 576 bytes |

| Data Memory    | Last 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## 23.8 Low-Voltage ICSP Programming

The LVP bit in the CONFIG4L Configuration register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM pin, provided the LVP bit is set. The LVP bit defaults to a '1' from the factory.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin and should be held low during normal operation.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 5 in the TRISB register must be cleared to disable the pull-up on RB5 and ensure the proper operation of the device.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only High-Voltage Programming mode can be used to program the device.

When using Low-Voltage ICSP Programming, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the codeprotect bits from an on state to an off state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs or user code can be reprogrammed or added.

| Byte-oriented file register operations                                                                                                                                                                                                                                             | Example Instruction  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                                                      |                      |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                                              | ADDWF MYREG, W, B    |

| $      d = 0 \ \text{for result destination to be WREG register} \\      d = 1 \ \text{for result destination to be file register (f)} \\      a = 0 \ \text{to force Access Bank} \\      a = 1 \ \text{for BSR to select bank} \\      f = 8 \text{-bit file register address} $ |                      |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                              |                      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                                                  |                      |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                                                           | MOVFF MYREG1, MYREG2 |

| 15 12 11 0                                                                                                                                                                                                                                                                         |                      |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                                                        |                      |

| f = 12-bit file register address                                                                                                                                                                                                                                                   |                      |

| Bit-oriented file register operations                                                                                                                                                                                                                                              |                      |

| <u>15 12 11 9 8 7 0</u>                                                                                                                                                                                                                                                            |                      |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                                      | BSF MYREG, bit, B    |

| b = 3-bit position of bit in file register (f)<br>a = 0 to force Access Bank<br>a = 1 for BSR to select bank<br>f = 8-bit file register address                                                                                                                                    |                      |

| Literal operations                                                                                                                                                                                                                                                                 |                      |

| <u>15 8 7 0</u>                                                                                                                                                                                                                                                                    |                      |

| OPCODE k (literal)                                                                                                                                                                                                                                                                 | MOVLW 0x7F           |

| k = 8-bit immediate value                                                                                                                                                                                                                                                          |                      |

| Control operations                                                                                                                                                                                                                                                                 |                      |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                   |                      |

| 15 8 7 0                                                                                                                                                                                                                                                                           |                      |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                            | GOTO Label           |

| 15 12 11 0                                                                                                                                                                                                                                                                         |                      |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                                             |                      |

| n = 20-bit immediate value                                                                                                                                                                                                                                                         |                      |

| 15 8 7 0                                                                                                                                                                                                                                                                           |                      |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                                                          | CALL MYFUNC          |

| 15 12 11 0                                                                                                                                                                                                                                                                         |                      |

| n<19:8> (literal)                                                                                                                                                                                                                                                                  |                      |

| S = Fast bit                                                                                                                                                                                                                                                                       |                      |

| 15 11 10 0                                                                                                                                                                                                                                                                         |                      |

| OPCODE n<10:0> (literal)                                                                                                                                                                                                                                                           | BRA MYFUNC           |

|                                                                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                                                    |                      |

| 15 8 7 0<br>OPCODE n<7:0> (literal)                                                                                                                                                                                                                                                | BC MYFUNC            |

#### 26.3 DC Characteristics: PIC18F6520/8520/6620/8620/6720/8720 (Industrial, Extended) PIC18LF6520/8520/6620/8620/6720/8720 (Industrial)

| DC CHA       | ARACT | ERISTICS                                   | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |                    |        |                                            |  |

|--------------|-------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------------------------------|--|

| Param<br>No. | Sym   | Characteristic                             | Min                                                                                                                                                                                                                                                             | Мах                | Units  | Conditions                                 |  |

|              | VIL   | Input Low Voltage                          |                                                                                                                                                                                                                                                                 |                    |        |                                            |  |

|              |       | I/O ports:                                 |                                                                                                                                                                                                                                                                 |                    |        |                                            |  |

| D030         |       | with TTL buffer                            | Vss                                                                                                                                                                                                                                                             | 0.15 Vdd           | V      | Vdd < 4.5V                                 |  |

| D030A        |       |                                            | —                                                                                                                                                                                                                                                               | 0.8                | V      | $4.5V \le V\text{dd} \le 5.5V$             |  |

| D031         |       | with Schmitt Trigger buffer<br>RC3 and RC4 | Vss<br>Vss                                                                                                                                                                                                                                                      | 0.2 Vdd<br>0.3 Vdd | V<br>V |                                            |  |

| D032         |       | MCLR                                       | Vss                                                                                                                                                                                                                                                             | 0.2 VDD            | V      |                                            |  |

| D032A        |       | OSC1 (in XT, HS and LP modes)<br>and T1OSI | Vss                                                                                                                                                                                                                                                             | 0.2 VDD            | V      |                                            |  |