Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8520t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.6.2 OSCILLATOR TRANSITIONS

PIC18FXX20 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

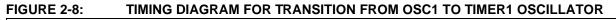

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-8. The Timer1 oscillator is assumed to be running all the time. After the SCS bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

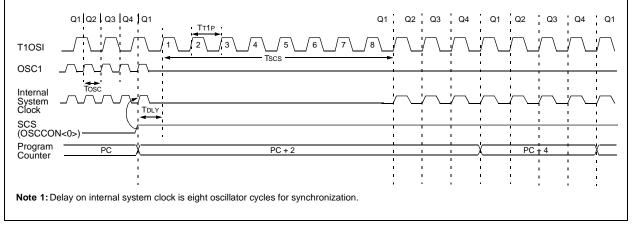

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place. If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes, is shown in Figure 2-9.

| TABLE 3-3: |            |            | <b>_</b>                           | MCLR Resets                                    | JED)<br>Wake-up via WDT<br>or Interrupt |  |

|------------|------------|------------|------------------------------------|------------------------------------------------|-----------------------------------------|--|

| Register   | Applicabl  | e Devices  | Power-on Reset,<br>Brown-out Reset | WDT Reset<br>RESET Instruction<br>Stack Resets |                                         |  |

| ADRESH     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| ADRESL     | PIC18F6X20 | PIC18F8X20 | xxxx xxxx                          | սսսս սսսս                                      | սսսս սսսս                               |  |

| ADCON0     | PIC18F6X20 | PIC18F8X20 | 00 0000                            | 00 0000                                        | uu uuuu                                 |  |

| ADCON1     | PIC18F6X20 | PIC18F8X20 | 00 0000                            | 00 0000                                        | uu uuuu                                 |  |

| ADCON2     | PIC18F6X20 | PIC18F8X20 | 0000                               | 0000                                           | uuuu                                    |  |

| CCPR1H     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCPR1L     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCP1CON    | PIC18F6X20 | PIC18F8X20 | 00 0000                            | 00 0000                                        | uu uuuu                                 |  |

| CCPR2H     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCPR2L     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCP2CON    | PIC18F6X20 | PIC18F8X20 | 00 0000                            | 00 0000                                        | uu uuuu                                 |  |

| CCPR3H     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCPR3L     | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| CCP3CON    | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| CVRCON     | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| CMCON      | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| TMR3H      | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| TMR3L      | PIC18F6X20 | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| T3CON      | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | uuuu uuuu                                      | uuuu uuuu                               |  |

| PSPCON     | PIC18F6X20 | PIC18F8X20 | 0000                               | 0000                                           | uuuu                                    |  |

| SPBRG1     | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| RCREG1     | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| TXREG1     | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| TXSTA1     | PIC18F6X20 | PIC18F8X20 | 0000 -010                          | 0000 -010                                      | uuuu -uuu                               |  |

| RCSTA1     | PIC18F6X20 | PIC18F8X20 | 0000 000x                          | 0000 000x                                      | uuuu uuuu                               |  |

| EEADRH     | PIC18F6X20 | PIC18F8X20 | 00                                 | 00                                             | uu                                      |  |

| EEADR      | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| EEDATA     | PIC18F6X20 | PIC18F8X20 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                               |  |

| EECON2     | PIC18F6X20 | PIC18F8X20 |                                    |                                                |                                         |  |

| EECON1     | PIC18F6X20 | PIC18F8X20 | xx-0 x000                          | uu-0 u000                                      | uu-0 u000                               |  |

### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for Reset value for specific condition.

5: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

### 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18FXX20 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to '1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to **Section 24.0 "Instruction Set Summary"** for further details of the instruction set.

| EXAMPLE 4-3: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

|              |                       |

| CASE   | 1:   |      |      |           |            |                                     |

|--------|------|------|------|-----------|------------|-------------------------------------|

| Object | Code |      |      | Source Co | de         |                                     |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ    | REG1       | ; is RAM location 0?                |

| 1100   | 0001 | 0010 | 0011 | MOVFF     | REG1, REG2 | ; No, execute 2-word instruction    |

| 1111   | 0100 | 0101 | 0110 |           |            | ; 2nd operand holds address of REG2 |

| 0010   | 0100 | 0000 | 0000 | ADDWF     | REG3       | ; continue code                     |

| CASE   | 2:   |      |      |           |            |                                     |

| Object | Code |      |      | Source Co | de         |                                     |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ    | REG1       | ; is RAM location 0?                |

| 1100   | 0001 | 0010 | 0011 | MOVFF     | REG1, REG2 | ; Yes                               |

| 1111   | 0100 | 0101 | 0110 |           |            | ; 2nd operand becomes NOP           |

| 0010   | 0100 | 0000 | 0000 | ADDWF     | REG3       | ; continue code                     |

# 4.8 Look-up Tables

Look-up tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

#### 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

# 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

Look-up table data may be stored 2 bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

A description of the table read/table write operation is shown in **Section 5.0 "Flash Program Memory"**.

#### TABLE 4-2: SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                   | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|------------------------|---------|---------|---------|-----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(3)</sup>   | FBFh    | CCPR1H  | F9Fh    | IPR1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2(3)            | FBEh    | CCPR1L  | F9Eh    | PIR1                  |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(3)            | FBDh    | CCP1CON | F9Dh    | PIE1                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(3)</sup> | FBCh    | CCPR2H  | F9Ch    | MEMCON <sup>(2)</sup> |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(3)</sup>  | FBBh    | CCPR2L  | F9Bh    | (1)                   |

| FFAh    | PCLATH                  | FDAh    | FSR2H                  | FBAh    | CCP2CON | F9Ah    | TRISJ                 |

| FF9h    | PCL                     | FD9h    | FSR2L                  | FB9h    | CCPR3H  | F99h    | TRISH                 |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                 | FB8h    | CCPR3L  | F98h    | TRISG                 |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                  | FB7h    | CCP3CON | F97h    | TRISF                 |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                  | FB6h    | (1)     | F96h    | TRISE                 |

| FF5h    | TABLAT                  | FD5h    | T0CON                  | FB5h    | CVRCON  | F95h    | TRISD                 |

| FF4h    | PRODH                   | FD4h    | (1)                    | FB4h    | CMCON   | F94h    | TRISC                 |

| FF3h    | PRODL                   | FD3h    | OSCCON                 | FB3h    | TMR3H   | F93h    | TRISB                 |

| FF2h    | INTCON                  | FD2h    | LVDCON                 | FB2h    | TMR3L   | F92h    | TRISA                 |

| FF1h    | INTCON2                 | FD1h    | WDTCON                 | FB1h    | T3CON   | F91h    | LATJ                  |

| FF0h    | INTCON3                 | FD0h    | RCON                   | FB0h    | PSPCON  | F90h    | LATH                  |

| FEFh    | INDF0 <sup>(3)</sup>    | FCFh    | TMR1H                  | FAFh    | SPBRG1  | F8Fh    | LATG                  |

| FEEh    | POSTINC0 <sup>(3)</sup> | FCEh    | TMR1L                  | FAEh    | RCREG1  | F8Eh    | LATF                  |

| FEDh    | POSTDEC0 <sup>(3)</sup> | FCDh    | T1CON                  | FADh    | TXREG1  | F8Dh    | LATE                  |

| FECh    | PREINC0 <sup>(3)</sup>  | FCCh    | TMR2                   | FACh    | TXSTA1  | F8Ch    | LATD                  |

| FEBh    | PLUSW0 <sup>(3)</sup>   | FCBh    | PR2                    | FABh    | RCSTA1  | F8Bh    | LATC                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                  | FAAh    | EEADRH  | F8Ah    | LATB                  |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                 | FA9h    | EEADR   | F89h    | LATA                  |

| FE8h    | WREG                    | FC8h    | SSPADD                 | FA8h    | EEDATA  | F88h    | PORTJ                 |

| FE7h    | INDF1 <sup>(3)</sup>    | FC7h    | SSPSTAT                | FA7h    | EECON2  | F87h    | PORTH                 |

| FE6h    | POSTINC1 <sup>(3)</sup> | FC6h    | SSPCON1                | FA6h    | EECON1  | F86h    | PORTG                 |

| FE5h    | POSTDEC1 <sup>(3)</sup> | FC5h    | SSPCON2                | FA5h    | IPR3    | F85h    | PORTF                 |

| FE4h    | PREINC1 <sup>(3)</sup>  | FC4h    | ADRESH                 | FA4h    | PIR3    | F84h    | PORTE                 |

| FE3h    | PLUSW1 <sup>(3)</sup>   | FC3h    | ADRESL                 | FA3h    | PIE3    | F83h    | PORTD                 |

| FE2h    | FSR1H                   | FC2h    | ADCON0                 | FA2h    | IPR2    | F82h    | PORTC                 |

| FE1h    | FSR1L                   | FC1h    | ADCON1                 | FA1h    | PIR2    | F81h    | PORTB                 |

| FE0h    | BSR                     | FC0h    | ADCON2                 | FA0h    | PIE2    | F80h    | PORTA                 |

Note 1: Unimplemented registers are read as '0'.

2: This register is unused on PIC18F6X20 devices. Always maintain this register clear.

**3:** This is not a physical register.

#### EXAMPLE 5-3: WRITING TO FLASH PROGRAM MEMORY

| EXAMPLE 5-3:   | WRI             | TING TO FLASH PROC            |                                                                      |

|----------------|-----------------|-------------------------------|----------------------------------------------------------------------|

|                | MOVLW           | D'64                          | ; number of bytes in erase block                                     |

|                | MOVWF           | COUNTER                       |                                                                      |

|                | MOVLW           | BUFFER_ADDR_HIGH              | ; point to buffer                                                    |

|                | MOVWF<br>MOVLW  | FSR0H<br>BUFFER ADDR LOW      |                                                                      |

|                | MOVWF           | FSROL                         |                                                                      |

|                | MOVLW           | CODE_ADDR_UPPER               | ; Load TBLPTR with the base                                          |

|                | MOVWF           | TBLPTRU                       | ; address of the memory block                                        |

|                | MOVLW           | CODE_ADDR_HIGH                |                                                                      |

|                | MOVWF<br>MOVLW  | TBLPTRH<br>CODE ADDR LOW      |                                                                      |

|                | MOVHW           | CODE_ADDR_LOW<br>TBLPTRL      |                                                                      |

| READ_BLOCK     |                 |                               |                                                                      |

|                | TBLRD*+         | ÷                             | ; read into TABLAT, and inc                                          |

|                | MOVF            | TABLAT, W                     | ; get data                                                           |

|                | MOVWF           | POSTINCO<br>COUNTER           | ; store data<br>; done?                                              |

|                | BRA             | READ BLOCK                    | ; repeat                                                             |

| MODIFY_WORD    |                 |                               |                                                                      |

| _              | MOVLW           | DATA_ADDR_HIGH                | ; point to buffer                                                    |

|                | MOVWF           | FSROH                         |                                                                      |

|                | MOVLW<br>MOVWF  | DATA_ADDR_LOW<br>FSR0L        |                                                                      |

|                | MOVWF<br>MOVLW  | NEW DATA LOW                  | ; update buffer word                                                 |

|                | MOVWF           | POSTINC0                      | , apaaoo barror nora                                                 |

|                | MOVLW           | NEW_DATA_HIGH                 |                                                                      |

|                | MOVWF           | INDF0                         |                                                                      |

| ERASE_BLOCK    | MOLITIN         |                               |                                                                      |

|                | MOVLW<br>MOVWF  | CODE_ADDR_UPPER<br>TBLPTRU    | ; load TBLPTR with the base<br>; address of the memory block         |

|                | MOVLW           | CODE ADDR HIGH                | , address of the memory brock                                        |

|                | MOVWF           | TBLPTRH                       |                                                                      |

|                | MOVLW           | CODE_ADDR_LOW                 |                                                                      |

|                | MOVWF           | TBLPTRL                       |                                                                      |

|                | BSF<br>BCF      | EECON1, EEPGD<br>EECON1, CFGS | ; point to Flash program memory<br>; access Flash program memory     |

|                | BSF             | EECON1, WREN                  | ; enable write to memory                                             |

|                | BSF             | EECON1, FREE                  | ; enable Row Erase operation                                         |

|                | BCF             | INTCON, GIE                   | ; disable interrupts                                                 |

|                | MOVLW           | 55h                           |                                                                      |

| Required       | MOVWF<br>MOVLW  | EECON2<br>AAh                 | ; write 55H                                                          |

| Sequence       | MOVWF           | EECON2                        | ; write AAH                                                          |

| -              | BSF             | EECON1, WR                    | ; start erase (CPU stall)                                            |

|                | NOP             |                               |                                                                      |

|                | BSF<br>TDIDD+   | INTCON, GIE                   | ; re-enable interrupts<br>; dummy read decrement                     |

| WRITE BUFFER B | TBLRD*-<br>BACK | -                             | ; dummy read decrement                                               |

|                | MOVLW           | 8                             | ; number of write buffer groups of 8 bytes                           |

|                | MOVWF           | COUNTER_HI                    |                                                                      |

|                | MOVLW           | BUFFER_ADDR_HIGH              | ; point to buffer                                                    |

|                | MOVWF           | FSROH                         |                                                                      |

|                | MOVLW<br>MOVWF  | BUFFER_ADDR_LOW<br>FSR0L      |                                                                      |

| PROGRAM LOOP   | 110 V W1        | IDROL                         |                                                                      |

|                | MOVLW           | 8                             | ; number of bytes in holding register                                |

|                | MOVWF           | COUNTER                       |                                                                      |

| WRITE_WORD_TO_ | -               |                               |                                                                      |

|                | MOVFF           | POSTINCO, WREG                | ; get low byte of buffer data<br>; present data to table latch       |

|                | TBLWT+*         | •                             | ; present data to table latch<br>; write data, perform a short write |

|                |                 |                               | ; to internal TBLWT holding register.                                |

|                | DECFSZ          | COUNTER                       | ; loop until buffers are full                                        |

|                | BRA             | WRITE_WORD_TO_HREGS           |                                                                      |

| r              |                 |                               |                                                                      |

| REGISTER 7-1: | EECON1 F                                                                                                                                                                                                                                                                                                                     | REGISTER                                      | (ADDRES                                 | S FA6h)        |                              |              |             |             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|----------------|------------------------------|--------------|-------------|-------------|

|               | R/W-x                                                                                                                                                                                                                                                                                                                        | R/W-x                                         | U-0                                     | R/W-0          | R/W-x                        | R/W-0        | R/S-0       | R/S-0       |

|               | EEPGD                                                                                                                                                                                                                                                                                                                        | CFGS                                          |                                         | FREE           | WRERR                        | WREN         | WR          | RD          |

|               | bit 7                                                                                                                                                                                                                                                                                                                        |                                               |                                         |                |                              |              |             | bit 0       |

|               |                                                                                                                                                                                                                                                                                                                              |                                               |                                         |                |                              |              |             |             |

| bit 7         |                                                                                                                                                                                                                                                                                                                              | -                                             |                                         |                | ry Select bit                |              |             |             |

|               |                                                                                                                                                                                                                                                                                                                              | s Flash prog<br>s data EEPR                   |                                         |                |                              |              |             |             |

| bit 6         |                                                                                                                                                                                                                                                                                                                              | •                                             |                                         |                | guration Sel                 | lect bit     |             |             |

|               |                                                                                                                                                                                                                                                                                                                              | s configurati<br>s Flash prog                 |                                         |                |                              |              |             |             |

| bit 5         | Unimplem                                                                                                                                                                                                                                                                                                                     | ented: Read                                   | <b>as</b> '0'                           |                |                              |              |             |             |

| bit 4         |                                                                                                                                                                                                                                                                                                                              | sh Row Eras                                   |                                         |                |                              |              |             |             |

|               | (cleare                                                                                                                                                                                                                                                                                                                      | the program<br>d by comple<br>m write only    |                                         |                | d by TBLPT                   | R on the ne  | kt WR comn  | hand        |

| bit 3         | WRERR: F                                                                                                                                                                                                                                                                                                                     | lash Progra                                   | m/Data EEF                              | ROM Error      | Flag bit                     |              |             |             |

|               | (any M                                                                                                                                                                                                                                                                                                                       | operation is<br>ICLR or any<br>rite operation | WDT Reset                               | t during self- | d<br>timed progra            | amming in n  | ormal opera | ation)      |

|               | Note:                                                                                                                                                                                                                                                                                                                        | When a Wittracing of the                      |                                         | •              | GD or FRE                    | E bits are n | ot cleared. | This allows |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                                    | ish Program                                   | /Data EEPR                              | OM Write E     | nable bit                    |              |             |             |

|               |                                                                                                                                                                                                                                                                                                                              | write cycles<br>write cycles                  | •                                       | •              |                              |              |             |             |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                                    | Control bit                                   |                                         |                |                              |              |             |             |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle, or a program memory erase cycle or write cycle.<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The<br/>WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                               |                                         |                |                              |              |             |             |

| bit 0         | RD: Read                                                                                                                                                                                                                                                                                                                     | Control bit                                   |                                         |                |                              |              |             |             |

|               | can on                                                                                                                                                                                                                                                                                                                       |                                               | ot cleared) ir                          | n software. F  | ne cycle. RD<br>RD bit canno |              |             |             |

|               |                                                                                                                                                                                                                                                                                                                              |                                               |                                         |                |                              |              |             |             |

|               | Legend:                                                                                                                                                                                                                                                                                                                      |                                               |                                         |                |                              |              |             |             |

|               | P - Roodo                                                                                                                                                                                                                                                                                                                    | hla hit                                       | $\lambda \Lambda I = \lambda \Lambda I$ | ritable bit    |                              | nlomontod    | hit road as | ·^'         |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 7.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADRH:EEADR register pair, clear the EEPGD control bit (EECON1<7>), clear the CFGS

EXAMPLE 7-1: DATA EEPROM READ

control bit (EECON1<6>) and then set the RD control bit (EECON1<0>). The data is available for the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

|   | MOVLW | DATA_EE_ADDRH |                              |               |

|---|-------|---------------|------------------------------|---------------|

|   | MOVWF | EEADRH        | Jpper bits of Data Memory Ad | dress to read |

|   | MOVLW | DATA_EE_ADDR  |                              |               |

|   | MOVWF | EEADR         | Lower bits of Data Memory Ad | dress to read |

|   | BCF   | EECON1, EEPGD | Point to DATA memory         |               |

|   | BCF   | EECON1, CFGS  | Access EEPROM                |               |

|   | BSF   | EECON1, RD    | EEPROM Read                  |               |

|   | MOVF  | EEDATA, W     | N = EEDATA                   |               |

| I |       |               |                              |               |

### 7.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADRH:EEADR register pair and the data written to the EEDATA register. Then the sequence in Example 7-2 must be followed to initiate the write cycle.

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, EECON1, EEADRH, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Write Complete Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | ;                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EEPGD | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | i                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | AAh           | ;                                             |

|          | MOVWF | EECON2        | ; Write AAh                                   |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

|          |       |               |                                               |

EXAMPLE 7-2: DATA EEPROM WRITE

| <b>REGISTER 9-3:</b> | INTCON3                                       | REGISTER                                                                                                           | र             |              |                 |               |              |         |  |

|----------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------|--------------|-----------------|---------------|--------------|---------|--|

|                      | R/W-1                                         | R/W-1                                                                                                              | R/W-0         | R/W-0        | R/W-0           | R/W-0         | R/W-0        | R/W-0   |  |

|                      | INT2IP                                        | INT1IP                                                                                                             | INT3IE        | INT2IE       | INT1IE          | INT3IF        | INT2IF       | INT1IF  |  |

|                      | bit 7                                         |                                                                                                                    |               |              |                 |               |              | bit 0   |  |

|                      |                                               |                                                                                                                    |               |              |                 |               |              |         |  |

| bit 7                |                                               | T2 External                                                                                                        | Interrupt Pr  | iority bit   |                 |               |              |         |  |

|                      | 1 = High p<br>0 = Low p                       | •                                                                                                                  |               |              |                 |               |              |         |  |

| bit 6                |                                               | T1 External                                                                                                        | Interrunt Pr  | iority bit   |                 |               |              |         |  |

| bit 0                | 1 = High p                                    |                                                                                                                    | menuptri      | ionty bit    |                 |               |              |         |  |

|                      | 0 = Low p                                     |                                                                                                                    |               |              |                 |               |              |         |  |

| bit 5                | INT3IE: IN                                    | T3 External                                                                                                        | Interrupt Er  | able bit     |                 |               |              |         |  |

|                      |                                               | es the INT3                                                                                                        |               |              |                 |               |              |         |  |

|                      |                                               | les the INT3                                                                                                       |               | •            |                 |               |              |         |  |

| bit 4                |                                               | T2 External                                                                                                        | •             |              |                 |               |              |         |  |

|                      |                                               | es the INT2<br>les the INT2                                                                                        |               |              |                 |               |              |         |  |

| bit 3                |                                               | T1 External                                                                                                        |               | •            |                 |               |              |         |  |

| Sit O                |                                               | es the INT1                                                                                                        | •             |              |                 |               |              |         |  |

|                      |                                               | les the INT1                                                                                                       |               | •            |                 |               |              |         |  |

| bit 2                | INT3IF: IN                                    | T3 External                                                                                                        | Interrupt Fla | ag bit       |                 |               |              |         |  |

|                      |                                               |                                                                                                                    |               | curred (mus  | t be cleared    | l in software | )            |         |  |

|                      |                                               | NT3 external                                                                                                       | •             |              |                 |               |              |         |  |

| bit 1                |                                               | T2 External                                                                                                        | •             | •            | 4 h a ala ana d |               | <b>`</b>     |         |  |

|                      |                                               | NT2 external                                                                                                       | •             | curred (mus  | st be cleared   | i in software | )            |         |  |

| bit 0                |                                               |                                                                                                                    | •             |              |                 |               |              |         |  |

|                      |                                               | INT1IF: INT1 External Interrupt Flag bit<br>1 = The INT1 external interrupt occurred (must be cleared in software) |               |              |                 |               |              |         |  |

|                      | 0 = The INT1 external interrupt did not occur |                                                                                                                    |               |              |                 |               |              |         |  |

|                      |                                               |                                                                                                                    |               |              |                 |               |              |         |  |

|                      | Legend:                                       |                                                                                                                    |               |              |                 |               |              |         |  |

|                      | R = Reada                                     | ble bit                                                                                                            |               | Vritable bit |                 | •             | bit, read as | '0'     |  |

|                      | - n = Value                                   | at POR                                                                                                             | '1' = E       | Bit is set   | '0' = Bit       | is cleared    | x = Bit is u | unknown |  |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| LIN 3-11. | IF NZ. FLN                                       | IFILINAL                                                                            |                 |                | I I KLOIS     |           |              |        |  |  |  |  |

|-----------|--------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|----------------|---------------|-----------|--------------|--------|--|--|--|--|

|           | U-0                                              | R/W-1                                                                               | U-0             | R/W-1          | R/W-1         | R/W-1     | R/W-1        | R/W-1  |  |  |  |  |

|           | —                                                | CMIP                                                                                | _               | EEIP           | BCLIP         | LVDIP     | TMR3IP       | CCP2IP |  |  |  |  |

|           | bit 7                                            |                                                                                     |                 |                |               |           |              | bit 0  |  |  |  |  |

| bit 7     | Unimpleme                                        | ented: Rea                                                                          | <b>d as</b> '0' |                |               |           |              |        |  |  |  |  |

| bit 6     | <b>CMIP:</b> Com<br>1 = High pri<br>0 = Low pri  | iority                                                                              | errupt Priorit  | y bit          |               |           |              |        |  |  |  |  |

| bit 5     | Unimpleme                                        | ented: Rea                                                                          | <b>d as</b> '0' |                |               |           |              |        |  |  |  |  |

| bit 4     | <b>EEIP:</b> Data<br>1 = High pri<br>0 = Low pri | iority                                                                              | Flash Write     | Operation In   | terrupt Prior | ity bit   |              |        |  |  |  |  |

| bit 3     | <b>BCLIP:</b> Bus<br>1 = High pri<br>0 = Low pri | iority                                                                              | nterrupt Prio   | rity bit       |               |           |              |        |  |  |  |  |

| bit 2     | <b>LVDIP:</b> Low<br>1 = High pri<br>0 = Low pri | iority                                                                              | etect Interru   | pt Priority bi | t             |           |              |        |  |  |  |  |

| bit 1     | <b>TMR3IP:</b> T<br>1 = High pr<br>0 = Low pri   | iority                                                                              | ow Interrupt    | Priority bit   |               |           |              |        |  |  |  |  |

| bit 0     | 1 = High pr                                      | <b>CCP2IP:</b> CCP2 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |                 |                |               |           |              |        |  |  |  |  |

|           | Legend:                                          |                                                                                     |                 |                |               |           |              |        |  |  |  |  |

|           | R = Readal                                       | ole bit                                                                             | W = W           | ritable bit    | U = Unin      | plemented | bit, read as | '0'    |  |  |  |  |

|           | 1                                                |                                                                                     |                 |                |               |           |              |        |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

### REGISTER 9-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

- n = Value at POR

x = Bit is unknown

NOTES:

Register 12-1 details the Timer1 Control register. This register controls the operating mode of the Timer1

module and contains the Timer1 Oscillator Enable bit

(T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

Timer1 can also be used to provide Real-Time Clock

(RTC) functionality to applications, with only a minimal addition of external components and code overhead.

# 12.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers: TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module special event trigger

Figure 12-1 is a simplified block diagram of the Timer1 module.

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0 | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| RD16  | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON |

| bit 7 |     |         |         |         |        |        | bit 0  |

| bit 7   | RD16: 16-bit Read/Write M                                            | lode Enable bit        |                         |                    |  |  |

|---------|----------------------------------------------------------------------|------------------------|-------------------------|--------------------|--|--|

|         | 1 = Enables register read/                                           | write of Timer1 in one | + 16-bit operation      |                    |  |  |

|         | 0 = Enables register read/\                                          | write of Timer1 in two | 8-bit operations        |                    |  |  |

| bit 6   | Unimplemented: Read as                                               | · ' O '                |                         |                    |  |  |

| bit 5-4 | T1CKPS1:T1CKPS0: Time                                                | er1 Input Clock Preso  | ale Select bits         |                    |  |  |

|         | 11 = 1:8 Prescale value                                              |                        |                         |                    |  |  |

|         | 10 = 1:4 Prescale value                                              |                        |                         |                    |  |  |

|         | 01 = 1:2 Prescale value                                              |                        |                         |                    |  |  |

|         | 00 = 1:1 Prescale value                                              |                        |                         |                    |  |  |

| bit 3   | T10SCEN: Timer1 Oscilla                                              | tor Enable bit         |                         |                    |  |  |

|         | 1 = Timer1 oscillator is ena                                         | abled                  |                         |                    |  |  |

|         | 0 = Timer1 oscillator is shu                                         | it off                 |                         |                    |  |  |

|         | The oscillator inverter and                                          | feedback resistor are  | turned off to eliminate | power drain.       |  |  |

| bit 2   | T1SYNC: Timer1 External                                              | Clock Input Synchro    | nization Select bit     |                    |  |  |

|         | <u>When TMR1CS = 1:</u>                                              |                        |                         |                    |  |  |

|         | 1 = Do not synchronize ext                                           | ternal clock input     |                         |                    |  |  |

|         | 0 = Synchronize external o                                           | lock input             |                         |                    |  |  |

|         | When TMR1CS = 0:                                                     |                        |                         |                    |  |  |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. |                        |                         |                    |  |  |

| bit 1   | TMR1CS: Timer1 Clock So                                              | ource Select bit       |                         |                    |  |  |

|         | 1 = External clock from pin                                          | RC0/T1OSO/T13Ck        | (I (on the rising edge) |                    |  |  |

|         | 0 = Internal clock (Fosc/4)                                          |                        |                         |                    |  |  |

| bit 0   | TMR1ON: Timer1 On bit                                                |                        |                         |                    |  |  |

|         | 1 = Enables Timer1                                                   |                        |                         |                    |  |  |

|         | 0 = Stops Timer1                                                     |                        |                         |                    |  |  |

|         |                                                                      |                        |                         |                    |  |  |

|         | Legend:                                                              |                        |                         |                    |  |  |

|         | R = Readable bit                                                     | W = Writable bit       | U = Unimplemented       | l bit, read as '0' |  |  |

|         | - n = Value at POR                                                   | '1' = Bit is set       | '0' = Bit is cleared    | x = Bit is unknown |  |  |

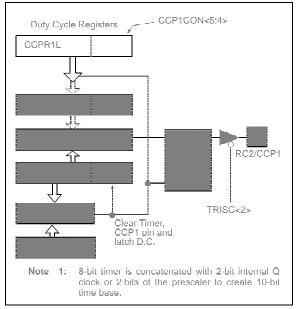

### 16.4 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force<br>the CCP1 PWM output latch to the default |

|-------|--------------------------------------------------------------------------------------|

|       | low level. This is not the PORTC I/O data latch.                                     |

Figure 16-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 16.4.3** "Setup for PWM Operation".

#### FIGURE 16-4: SIMPLIFIED PWM BLOCK DIAGRAM

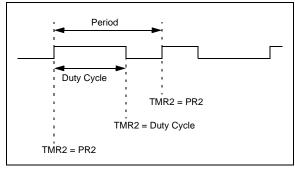

A PWM output (Figure 16-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 16-5: PWM OUTPUT

### 16.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### **EQUATION 16-1:**

$PWM Period = (PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

### 16.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 16-2:**

```

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This doublebuffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

MOVLB

| MOVFF                                                | Move f to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | o f          |                                |                                        |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------|----------------------------------------|--|

| Syntax:                                              | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MOVFF        | f <sub>s</sub> ,f <sub>d</sub> |                                        |  |

| Operands:                                            | $\begin{array}{l} 0 \leq f_s \leq 4095 \\ 0 \leq f_d \leq 4095 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |                                |                                        |  |

| Operation:                                           | $(f_s) \to f_d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                |                                        |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                |                                        |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.) | 1100<br>1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ffff<br>ffff | ffff<br>ffff                   | ffff <sub>s</sub><br>ffff <sub>d</sub> |  |

|                                                      | tion: The contents of source register 'f <sub>s</sub> ' are moved to destination register 'f <sub>d</sub> '. Location of source 'f <sub>s</sub> ' can be anywhere in the 4096-byte data space (000h to FFFh) and location of destination 'f <sub>d</sub> ' can also be anywhere from 000h to FFFh. Either source or destination can be W (a useful special situation). MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port). The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register. |              |                                |                                        |  |

| Words:                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                |                                        |  |

| Cycles:                                              | 2 (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                |                                        |  |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |                                |                                        |  |

| Q1                                                   | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q3           | 3                              | Q4                                     |  |

| Q1     | Q2                                   | Q3              | Q4                              |

|--------|--------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)        | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation,<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

REG1, REG2

#### Example: MOVFF

| Before Instructio | n |       |

|-------------------|---|-------|

| REG1              | = | 0x33  |

| REG2              | = | 0x11  |

| After Instruction |   |       |

| REG1              | = | 0x33, |

| REG2              | = | 0x33  |

| Syntax:    |                | [ label ]             | MOVLB               | k   |      |                            |  |

|------------|----------------|-----------------------|---------------------|-----|------|----------------------------|--|

| Ope        | rands:         | $0 \le k \le 25$      | $0 \leq k \leq 255$ |     |      |                            |  |

| Operation: |                | $k \rightarrow BSR$   | $k \rightarrow BSR$ |     |      |                            |  |

| Statu      | us Affected:   | None                  |                     |     |      |                            |  |

| Enco       | oding:         | 0000                  | 0001                | kkk | ck   | kkkk                       |  |

| Des        | cription:      | The 8-bit<br>the Bank |                     |     |      |                            |  |

| Wor        | ds:            | 1                     |                     |     |      |                            |  |

| Cycl       | es:            | 1                     |                     |     |      |                            |  |