Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 68                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

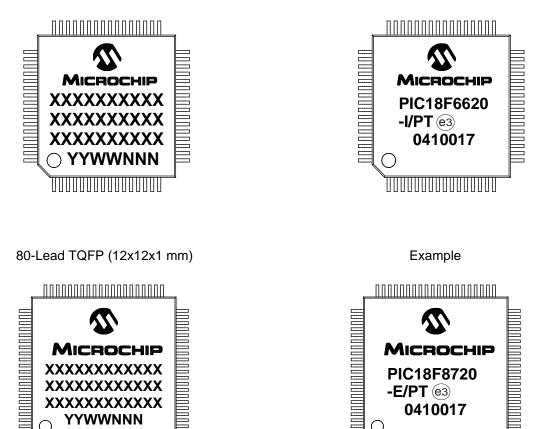

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8720-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name            | Pin N            | Pin        | Buffer   | Description |                                                                                                                             |  |

|---------------------|------------------|------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name            | PIC18F6X20       | PIC18F8X20 | Туре     | Туре        | Description                                                                                                                 |  |

|                     |                  |            |          |             | PORTC is a bidirectional I/O port.                                                                                          |  |

| RC0/T1OSO/T13CKI    | 30               | 36         |          |             |                                                                                                                             |  |

| RC0                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| T1OSO               |                  |            | 0        | —           | Timer1 oscillator output.                                                                                                   |  |

| T13CKI              |                  |            | I        | ST          | Timer1/Timer3 external clock input.                                                                                         |  |

| RC1/T1OSI/CCP2      | 29               | 35         |          |             |                                                                                                                             |  |

| RC1                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| T1OSI               |                  |            | I        | CMOS        | Timer1 oscillator input.                                                                                                    |  |

| CCP2 <sup>(2)</sup> |                  |            | I/O      | ST          | Capture2 input/Compare2 output/                                                                                             |  |

|                     |                  |            |          |             | PWM2 output.                                                                                                                |  |

| RC2/CCP1            | 33               | 43         |          |             |                                                                                                                             |  |

| RC2                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| CCP1                |                  |            | I/O      | ST          | Capture1 input/Compare1 output/                                                                                             |  |

|                     |                  |            |          |             | PWM1 output.                                                                                                                |  |

| RC3/SCK/SCL         | 34               | 44         |          |             |                                                                                                                             |  |

| RC3                 |                  |            | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SCK                 |                  |            | I/O      | ST          | Synchronous serial clock input/outpu                                                                                        |  |

|                     |                  |            |          |             | for SPI mode.                                                                                                               |  |

| SCL                 |                  |            | I/O      | ST          | Synchronous serial clock input/output for I <sup>2</sup> C mode.                                                            |  |

| RC4/SDI/SDA         | 35               | 45         |          |             |                                                                                                                             |  |

| RC4                 |                  | 45         | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SDI                 |                  |            | "/C      | ST          | SPI data in.                                                                                                                |  |

| SDA                 |                  |            | I/O      | ST          | $I^2C$ data I/O.                                                                                                            |  |

| RC5/SDO             | 36               | 46         | ., C     | •           |                                                                                                                             |  |

| RC5/SDO<br>RC5      | 30               | 40         | I/O      | ST          | Digital I/O.                                                                                                                |  |

| SDO                 |                  |            | 0        |             | SPI data out.                                                                                                               |  |

|                     |                  | 07         | Ŭ        |             |                                                                                                                             |  |

| RC6/TX1/CK1         | 31               | 37         | 1/0      | ст          |                                                                                                                             |  |

| RC6<br>TX1          |                  |            | 1/O<br>O | ST          | Digital I/O.<br>USART 1 asynchronous transmit.                                                                              |  |

| CK1                 |                  |            | 1/0      | ST          | USART 1 synchronous clock                                                                                                   |  |

| ONT                 |                  |            | 1/0      | 51          | (see RX1/DT1).                                                                                                              |  |

|                     | 22               | 20         |          |             |                                                                                                                             |  |

| RC7/RX1/DT1         | 32               | 38         | I/O      | ST          | Digital I/O                                                                                                                 |  |

| RC7<br>RX1          |                  |            |          | ST          | Digital I/O.<br>USART 1 asynchronous receive.                                                                               |  |

| DT1                 |                  |            | I/O      | ST          | USART 1 synchronous data                                                                                                    |  |

|                     |                  |            | ",0      |             | (see TX1/CK1).                                                                                                              |  |

| Legend: TTL = TTL   | compatible inp   | L          |          | CMOS -      | = CMOS compatible input or output                                                                                           |  |

|                     | mitt Trigger inp |            | evels    |             | = Analog input                                                                                                              |  |

|                     |                  |            |          | •           |                                                                                                                             |  |

|                     |                  |            |          |             |                                                                                                                             |  |

| I = Inpu<br>P = Pow | it<br>ver        |            |          | O =<br>OD = | <ul> <li>Analog input</li> <li>Output</li> <li>Open-Drain (no P diode to VE</li> <li>(all operating modes except</li> </ul> |  |

#### TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 when CCP2MX is not selected (all operating modes except Microcontroller).

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

**6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

### 2.7 Effects of Sleep Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the onchip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, Sleep mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The user can wake from Sleep through external Reset, Watchdog Timer Reset or through an interrupt.

### 2.8 Power-up Delays

Power up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply and clock are stable. For additional information on Reset operation, see **Section 3.0 "Reset**".

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of 72 ms (nominal) on power-up only (POR and BOR). The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable.

With the PLL enabled (HS/PLL Oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: First, the PWRT time-out is invoked after a POR time delay has expired. Then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional fixed 2 ms (nominal) time-out to allow the PLL ample time to lock to the incoming clock frequency.

TABLE 2-3:

OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode      | OSC1 Pin                                              | OSC2 Pin                                              |  |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------|--|--|

| RC            | Floating, external resistor should pull high          | At logic low                                          |  |  |

| RCIO          | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |  |  |

| ECIO          | Floating                                              | Configured as PORTA, bit 6                            |  |  |

| EC            | Floating                                              | At logic low                                          |  |  |

| LP, XT and HS | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |  |

Note: See Table 3-1 in Section 3.0 "Reset" for time-outs due to Sleep and MCLR Reset.

# 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

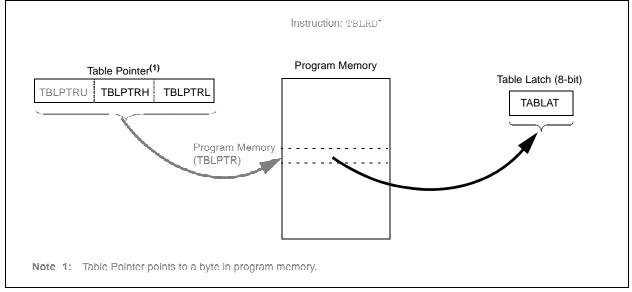

### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

# FIGURE 5-1: TABLE READ OPERATION

### REGISTER 9-2: INTCON2 REGISTER

| 9-2:  | INTCON2               | REGISTE                       | २             |                    |                |             |                |       |

|-------|-----------------------|-------------------------------|---------------|--------------------|----------------|-------------|----------------|-------|

|       | R/W-1                 | R/W-1                         | R/W-1         | R/W-1              | R/W-1          | R/W-1       | R/W-1          | R/W-1 |

|       | RBPU                  | INTEDG0                       | INTEDG1       | INTEDG2            | INTEDG3        | TMR0IP      | INT3IP         | RBIP  |

|       | bit 7                 |                               |               |                    |                |             |                | bit 0 |

| bit 7 | RBPU: PO              | ORTB Pull-u                   | o Enable bit  |                    |                |             |                |       |

|       |                       | ORTB pull-up<br>TB pull-ups a |               |                    | port latch va  | lues        |                |       |

| bit 6 |                       | : External In                 |               | •                  | portilatori va |             |                |       |

| SIL U |                       | upt on rising                 |               |                    |                |             |                |       |

|       |                       | upt on falling                | •             |                    |                |             |                |       |

| bit 5 |                       | : External In                 |               | e Select bit       |                |             |                |       |

|       |                       | upt on rising                 |               | ,                  |                |             |                |       |

|       |                       | upt on falling                |               |                    |                |             |                |       |

| bit 4 | INTEDG2               | : External In                 | terrupt 2 Edg | ge Select bit      |                |             |                |       |

|       |                       | upt on rising                 |               |                    |                |             |                |       |

|       | 0 = Interr            | upt on falling                | l edge        |                    |                |             |                |       |

| bit 3 |                       | : External In                 |               | ge Select bit      |                |             |                |       |

|       |                       | upt on rising                 | •             |                    |                |             |                |       |

|       |                       | upt on falling                | -             | <b>B</b> · · · · · |                |             |                |       |

| bit 2 |                       | TMR0 Overf                    | ow Interrupt  | Priority bit       |                |             |                |       |

|       | 1 = High<br>0 = Low p |                               |               |                    |                |             |                |       |

| bit 1 |                       | NT3 External                  | Interrunt Pri | ority hit          |                |             |                |       |

|       | 1 = High              |                               | menuptri      |                    |                |             |                |       |

|       | 0 = Low p             | • •                           |               |                    |                |             |                |       |

| bit 0 | -                     | Port Chang                    | e Interrupt P | riority bit        |                |             |                |       |

|       | 1 = High              | •                             |               | ,                  |                |             |                |       |

|       | 0 = Low p             | oriority                      |               |                    |                |             |                |       |

|       | Legend:               |                               |               |                    |                |             |                |       |

|       | R = Read              | able bit                      | W = V         | Vritable bit       | U = Unim       | plemented b | oit, read as ' | 0'    |

|       |                       |                               |               |                    |                |             |                |       |

- n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown)

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| <b>REGISTER 9-3:</b> | INTCON3                 | INTCON3 REGISTER            |               |              |                 |               |              |         |

|----------------------|-------------------------|-----------------------------|---------------|--------------|-----------------|---------------|--------------|---------|

|                      | R/W-1                   | R/W-1                       | R/W-0         | R/W-0        | R/W-0           | R/W-0         | R/W-0        | R/W-0   |

|                      | INT2IP                  | INT1IP                      | INT3IE        | INT2IE       | INT1IE          | INT3IF        | INT2IF       | INT1IF  |

|                      | bit 7                   |                             |               |              |                 |               |              | bit 0   |

|                      |                         |                             |               |              |                 |               |              |         |

| bit 7                |                         | T2 External                 | Interrupt Pr  | iority bit   |                 |               |              |         |

|                      | 1 = High p<br>0 = Low p | •                           |               |              |                 |               |              |         |

| bit 6                |                         | T1 External                 | Interrunt Pr  | iority bit   |                 |               |              |         |

| bit 0                | 1 = High p              |                             | menuptri      | ionty bit    |                 |               |              |         |

|                      | 0 = Low p               |                             |               |              |                 |               |              |         |

| bit 5                | INT3IE: IN              | T3 External                 | Interrupt Er  | able bit     |                 |               |              |         |

|                      |                         | es the INT3                 |               |              |                 |               |              |         |

|                      |                         | les the INT3                |               | •            |                 |               |              |         |

| bit 4                |                         | T2 External                 | •             |              |                 |               |              |         |

|                      |                         | es the INT2<br>les the INT2 |               |              |                 |               |              |         |

| bit 3                |                         | T1 External                 |               | •            |                 |               |              |         |

| Sit O                |                         | es the INT1                 | •             |              |                 |               |              |         |

|                      |                         | les the INT1                |               | •            |                 |               |              |         |

| bit 2                | INT3IF: IN              | T3 External                 | Interrupt Fla | ag bit       |                 |               |              |         |

|                      |                         |                             |               | curred (mus  | t be cleared    | l in software | )            |         |

|                      |                         | NT3 external                | •             |              |                 |               |              |         |

| bit 1                |                         | T2 External                 | •             | •            | 4 h a ala ana d |               | <b>`</b>     |         |

|                      |                         | NT2 external                | •             | curred (mus  | st be cleared   | i in software | )            |         |

| bit 0                |                         | T1 External                 | •             |              |                 |               |              |         |

|                      |                         |                             | -             | curred (mus  | t be cleared    | l in software | )            |         |

|                      |                         | NT1 external                |               |              |                 |               | ,            |         |

|                      |                         |                             |               |              |                 |               |              |         |

|                      | Legend:                 |                             |               |              |                 |               |              |         |

|                      | R = Reada               | ble bit                     |               | Vritable bit |                 | •             | bit, read as | '0'     |

|                      | - n = Value             | at POR                      | '1' = E       | Bit is set   | '0' = Bit       | is cleared    | x = Bit is u | unknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| REGISTER 9-6: | PIR3: PER |                                                                                                                                                                 | INTERRU         | PT REQUE                      | EST (FLAG      | ) REGISTI     | ER 3          |        |  |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|---------------|---------------|--------|--|

|               | U-0       | U-0                                                                                                                                                             | R-0             | R-0                           | R/W-0          | R/W-0         | R/W-0         | R/W-0  |  |

|               |           |                                                                                                                                                                 | RC2IF           | TX2IF                         | TMR4IF         | CCP5IF        | CCP4IF        | CCP3IF |  |

|               | bit 7     |                                                                                                                                                                 |                 |                               |                |               |               | bit 0  |  |

| bit 7- 6      | Unimplem  | ented: Rea                                                                                                                                                      | <b>d as</b> '0' |                               |                |               |               |        |  |

| bit 5         | RC2IF: US | ART2 Rece                                                                                                                                                       | ive Interrup    | t Flag bit                    |                |               |               |        |  |

|               |           | SART2 rece<br>SART2 rece                                                                                                                                        |                 | RCREG, is fu<br>empty         | III (cleared w | when RCRE     | G is read)    |        |  |

| bit 4         | TX2IF: US | ART2 Trans                                                                                                                                                      | mit Interrup    | t Flag bit                    |                |               |               |        |  |

|               |           | SART2 tran<br>SART2 tran                                                                                                                                        |                 |                               | mpty (cleare   | ed when TX    | REG is writte | en)    |  |

| bit 3         | TMR4IF: T | MR3 Overfl                                                                                                                                                      | ow Interrupt    | Flag bit                      |                |               |               |        |  |

|               |           | register over<br>register did                                                                                                                                   |                 | ust be cleare<br>w            | ed in softwar  | e)            |               |        |  |

| bit 2-0       | CCPxIF: C | CPx Interru                                                                                                                                                     | pt Flag bit (   | CCP Module                    | s 3, 4 and 5   | 5)            |               |        |  |

|               |           | R1 or TMR3                                                                                                                                                      | •               | oture occurre<br>apture occur |                | cleared in so | oftware)      |        |  |

|               | 1 = A TMF | <u>Compare mode:</u><br>1 = A TMR1 or TMR3 register compare match occurred (must be cleared in software)<br>0 = No TMR1 or TMR3 register compare match occurred |                 |                               |                |               |               |        |  |

|               |           | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                        |                 |                               |                |               |               |        |  |

|               | Legend:   |                                                                                                                                                                 |                 |                               |                |               |               |        |  |

|               | R = Reada | ble bit                                                                                                                                                         | W = WI          | ritable bit                   | U = Unir       | nplemented    | bit, read as  | '0'    |  |

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|--------------------|------------------|----------------------|--------------------|

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority Registers (IPR1, IPR2 and IPR3). The operation of the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

| ER 9-10: | IPR1: PER                                          | IPHERAL                                                                                                                                         | INTERRU        | PT PRIOR       | ITY REGIS       | TER 1  |        |        |

|----------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----------------|--------|--------|--------|

|          | R/W-1                                              | R/W-1                                                                                                                                           | R/W-1          | R/W-1          | R/W-1           | R/W-1  | R/W-1  | R/W-1  |

|          | PSPIP <sup>(1)</sup>                               | ADIP                                                                                                                                            | RC1IP          | TX1IP          | SSPIP           | CCP1IP | TMR2IP | TMR1IP |

|          | bit 7                                              |                                                                                                                                                 |                |                |                 |        |        | bit 0  |

| bit 7    | <b>PSPIP:</b> Par<br>1 = High pri<br>0 = Low prio  | ority                                                                                                                                           | Port Read/V    | Vrite Interrup | ot Priority bit | (1)    |        |        |

| bit 6    | <b>ADIP:</b> A/D (<br>1 = High pri<br>0 = Low prio | ority                                                                                                                                           | nterrupt Pric  | rity bit       |                 |        |        |        |

| bit 5    | <b>RC1IP:</b> US/<br>1 = High pri<br>0 = Low prio  | ority                                                                                                                                           | vive Interrupt | Priority bit   |                 |        |        |        |

| bit 4    | <b>TX1IP:</b> USA<br>1 = High pri<br>0 = Low prio  | ority                                                                                                                                           | mit Interrup   | t Priority bit |                 |        |        |        |

| bit 3    | SSPIP: Mas<br>1 = High pri<br>0 = Low prio         | ority                                                                                                                                           | onous Seria    | l Port Interru | ıpt Priority b  | it     |        |        |

| bit 2    | <b>CCP1IP:</b> Co<br>1 = High pri<br>0 = Low prio  | ority                                                                                                                                           | pt Priority bi | t              |                 |        |        |        |

| bit 1    | 1 = High pri                                       | <b>TMR2IP:</b> TMR2 to PR2 Match Interrupt Priority bit 1 = High priority 0 = Low priority                                                      |                |                |                 |        |        |        |

| bit 0    | 1 = High pri                                       | <ul> <li>0 = Low priority</li> <li>TMR1IP: TMR1 Overflow Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                |                |                 |        |        |        |

|          | P                                                  | <b>J</b>                                                                                                                                        |                |                |                 |        |        |        |

# REGISTER 9-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

Note 1: Enabled only in Microcontroller mode for PIC18F8X20 devices.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name         | Bit#  | Buffer Type           | Function                                                                    |

|--------------|-------|-----------------------|-----------------------------------------------------------------------------|

| RD0/PSP0/AD0 | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 0 or address/data bus bit 0. |

| RD1/PSP1/AD1 | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 1 or address/data bus bit 1. |

| RD2/PSP2/AD2 | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 2 or address/data bus bit 2. |

| RD3/PSP3/AD3 | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 3 or address/data bus bit 3. |

| RD4/PSP4/AD4 | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 4 or address/data bus bit 4. |

| RD5/PSP5/AD5 | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 5 or address/data bus bit 5. |

| RD6/PSP6/AD6 | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 6 or address/data bus bit 6. |

| RD7/PSP7/AD7 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin, Parallel Slave Port bit 7 or address/data bus bit 7. |

#### TABLE 10-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

WAIT1

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in System Bus or Parallel Slave Port mode.

| Name   | Bit 7                                       | Bit 6               | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------------------|---------------------|-------|---------|-------|-------|-------|-----------|----------------------|---------------------------------|

| PORTD  | RD7                                         | RD6                 | RD5   | RD4     | RD3   | RD2   | RD1   | RD0       | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Da                                     | ata Output Register |       |         |       |       |       |           | xxxx xxxx            | uuuu uuuu                       |

| TRISD  | PORTD Data Direction Register 1111 1111 111 |                     |       |         |       |       |       | 1111 1111 |                      |                                 |

| PSPCON | IBF                                         | OBF                 | IBOV  | PSPMODE | _     | _     | _     | _         | 0000                 | 0000                            |

TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

WAIT0

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

WM1

WM0

0-00 --00

0-00 --00

MEMCON EBDIS

| TABLE 10-9: F | ORIEF | UNCTIONS              |                                                                                                                                                                                                                   |

|---------------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name          | Bit#  | Buffer Type           | Function                                                                                                                                                                                                          |

| RE0/RD/AD8    | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, read control for Parallel Slave Port or<br>address/data bit 8<br>For RD (PSP Control mode):<br>1 = Not a read operation<br>0 = Read operation, reads PORTD register (if chip selected)     |

| RE1/WR/AD9    | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, write control for Parallel Slave Port or<br>address/data bit 9<br>For WR (PSP Control mode):<br>1 = Not a write operation<br>0 = Write operation, writes PORTD register (if chip selected) |

| RE2/CS/AD10   | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, chip select control for Parallel Slave Port or<br>address/data bit 10<br>For CS (PSP Control mode):<br>1 = Device is not selected<br>0 = Device is selected                                |

| RE3/AD11      | bit 3 | ST/TTL <sup>(1)</sup> | Input/output port pin or address/data bit 11.                                                                                                                                                                     |

| RE4/AD12      | bit 4 | ST/TTL <sup>(1)</sup> | Input/output port pin or address/data bit 12.                                                                                                                                                                     |

| RE5/AD13      | bit 5 | ST/TTL <sup>(1)</sup> | Input/output port pin or address/data bit 13.                                                                                                                                                                     |

| RE6/AD14      | bit 6 | ST/TTL <sup>(1)</sup> | Input/output port pin or address/data bit 14.                                                                                                                                                                     |

| RE7/CCP2/AD15 | bit 7 | ST/TTL <sup>(1)</sup> | Input/output port pin, Capture2 input/Compare2 output/PWM output (PIC18F8X20 devices in Microcontroller mode only) or address/data bit 15.                                                                        |

### TABLE 10-9: PORTE FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O or CCP mode and TTL buffers when in System Bus or PSP Control mode.

| TABLE 10-10: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name   | Bit 7   | Bit 6   | Bit 5      | Bit 4           | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|---------|------------|-----------------|---------|-------|-------|-------|----------------------|---------------------------------|

| TRISE  | PORTE   | Data Di | rection Co | ontrol Register |         |       |       |       | 1111 1111            | 1111 1111                       |

| PORTE  | Read PC | ORTE pi | n/Write P  | ORTE Data La    | tch     |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| LATE   | Read PC | ORTE D  | ata Latch/ | Write PORTE     | Data La | atch  |       |       | xxxx xxxx            | uuuu uuuu                       |

| MEMCON | EBDIS   | _       | WAIT1      | WAIT0           |         | _     | WM1   | WM0   | 0-0000               | 000000                          |

| PSPCON | IBF     | OBF     | IBOV       | PSPMODE         |         | _     |       | _     | 0000                 | 0000                            |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTE.

| Name           | Bit#  | Buffer Type | Function                                                                             |

|----------------|-------|-------------|--------------------------------------------------------------------------------------|

| RF0/AN5        | bit 0 | ST          | Input/output port pin or analog input.                                               |

| RF1/AN6/C2OUT  | bit 1 | ST          | Input/output port pin, analog input or comparator 2 output.                          |

| RF2/AN7/C1OUT  | bit 2 | ST          | Input/output port pin, analog input or comparator 1 output.                          |

| RF3/AN8        | bit 3 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF4/AN9        | bit 4 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF5/AN10/CVREF | bit 5 | ST          | Input/output port pin, analog input/comparator input or comparator reference output. |

| RF6/AN11       | bit 6 | ST          | Input/output port pin or analog input/comparator input.                              |

| RF7/SS         | bit 7 | ST/TTL      | Input/output port pin or slave select pin for synchronous serial port.               |

#### TABLE 10-11: PORTF FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

#### TABLE 10-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Name   | Bit 7   | Bit 6      | Bit 5     | Bit 4       | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------|------------|-----------|-------------|-----------|-------|-------|-------|----------------------|---------------------------------|

| TRISF  | PORTF I | Data Direc | tion Con  | trol Regist | ter       |       |       |       | 1111 1111            | 1111 1111                       |

| PORTF  | Read PC | ORTF pin/  | Nrite PO  | RTF Data    | Latch     |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| LATF   | Read PC | ORTF Data  | a Latch/W | /rite POR   | FF Data L | atch. |       |       | 0000 0000            | uuuu uuuu                       |

| ADCON1 |         | _          | VCFG1     | VCFG0       | PCFG3     | PCFG2 | PCFG1 | PCFG0 | 00 0000              | 00 0000                         |

| CMCON  | C2OUT   | C1OUT      | C2INV     | C1INV       | CIS       | CM2   | CM1   | CM0   | 0000 0000            | 0000 0000                       |

| CVRCON | CVREN   | CVROE      | CVRR      | CVRSS       | CVR3      | CVR2  | CVR1  | CVR0  | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTF.

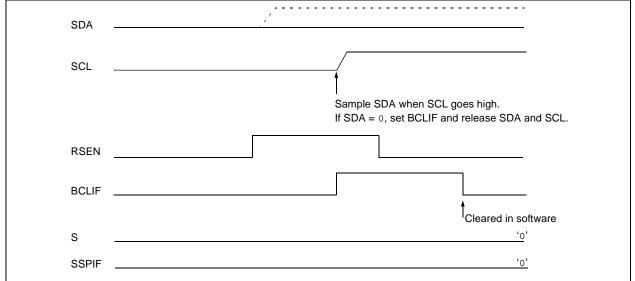

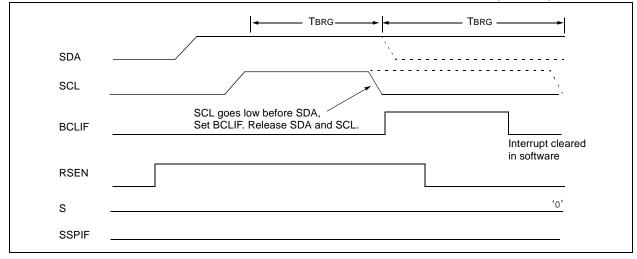

# 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, Figure 17-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 17-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

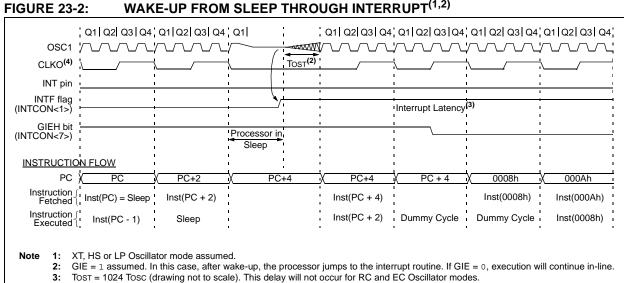

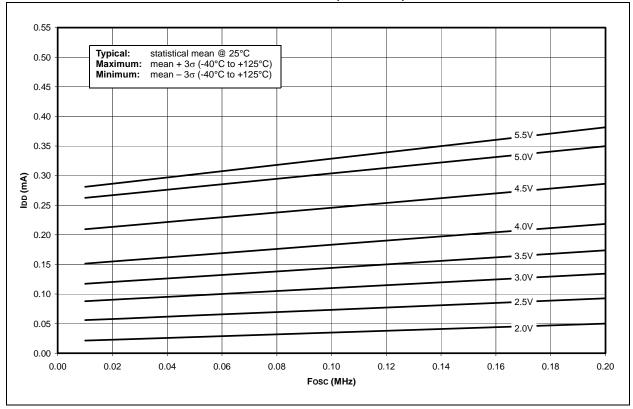

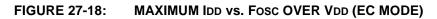

### 23.3 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared, but keeps running, the  $\overline{\text{PD}}$  bit (RCON<3>) is cleared, the  $\overline{\text{TO}}$  (RCON<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 23.3.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a peripheral interrupt.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt.

- 5. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 6. MSSP (Start/Stop) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/l<sup>2</sup>C).

- 8. USART RX or TX (Synchronous Slave mode).

- 9. A/D conversion (when A/D clock source is RC).

- 10. EEPROM write operation complete.

- 11. LVD interrupt.

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 23.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

4: CLKO is not available in these oscillator modes, but shown here for timing reference

### 23.4 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $PIC^{\textcircled{B}}$  devices. The user program memory is divided on binary boundaries into individual blocks, each of which has three separate code protection bits associated with it:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

The code protection bits are located in Configuration Registers 5L through 7H. Their locations within the registers are summarized in Table 23-3.

In the PIC18FXX20 family, the block size varies with the size of the user program memory. For PIC18FX520 devices, program memory is divided into four blocks of 8 Kbytes each. The first block is further divided into a boot block of 2 Kbytes and a second block (Block 0) of 6 Kbytes, for a total of five blocks. The organization of the blocks and their associated code protection bits are shown in Figure 23-3.

For PIC18FX620 and PIC18FX720 devices, program memory is divided into blocks of 16 Kbytes. The first block is further divided into a boot block of 512 bytes and a second block (Block 0) of 15.5 Kbytes, for a total of nine blocks. This produces five blocks for 64-Kbyte devices and nine for 128-Kbyte devices. The organization of the blocks and their associated code protection bits are shown in Figure 23-4.

| File    | Name     | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|----------------------|----------------------|----------------------|----------------------|-------|-------|-------|-------|

| 300008h | CONFIG5L | CP7 <sup>(1)</sup>   | CP6 <sup>(1)</sup>   | CP5 <sup>(1)</sup>   | CP4 <sup>(1)</sup>   | CP3   | CP2   | CP1   | CP0   |

| 300009h | CONFIG5H | CPD                  | CPB                  | _                    | —                    | _     |       | _     | _     |

| 30000Ah | CONFIG6L | WRT7 <sup>(1)</sup>  | WRT6 <sup>(1)</sup>  | WRT5 <sup>(1)</sup>  | WRT4 <sup>(1)</sup>  | WRT3  | WRT2  | WRT1  | WRT0  |

| 30000Bh | CONFIG6H | WRTD                 | WRTB                 | WRTC                 | —                    |       | _     | _     | _     |

| 30000Ch | CONFIG7L | EBTR7 <sup>(1)</sup> | EBTR6 <sup>(1)</sup> | EBTR5 <sup>(1)</sup> | EBTR4 <sup>(1)</sup> | EBTR3 | EBTR2 | EBTR1 | EBTR0 |

| 30000Dh | CONFIG7H | _                    | EBTRB                | _                    | _                    |       |       | _     | _     |

TABLE 23-3: SUMMARY OF CODE PROTECTION REGISTERS

**Legend:** Shaded cells are unimplemented.

Note 1: Unimplemented in PIC18FX520 and PIC18FX620 devices.

#### 23.4.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 23.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write-protected. The WRTC bit controls protection of the configuration registers. In user mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 23.5 ID Locations

Eight memory locations (200000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

### 23.6 In-Circuit Serial Programming

PIC18FX520/X620/X720 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

| Note: | When     | performing           | In-Circuit            | Serial   |

|-------|----------|----------------------|-----------------------|----------|

|       | Progran  | nming, verify        | that power            | is con-  |

|       | nected   | to <b>all</b> VDD ar | nd AVDD pins          | s of the |

|       | microco  | ntroller and th      | nat <b>all</b> Vss an | d AVss   |

|       | pins are | grounded.            |                       |          |

## 23.7 In-Circuit Debugger

When the DEBUG bit in the CONFIG4L Configuration register is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 23-4 shows which features are consumed by the background debugger.

#### TABLE 23-4: DEBUGGER RESOURCES

| I/O pins       | RB6, RB7       |

|----------------|----------------|

| Stack          | 2 levels       |

| Program Memory | Last 576 bytes |

| Data Memory    | Last 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## 23.8 Low-Voltage ICSP Programming

The LVP bit in the CONFIG4L Configuration register enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM pin, provided the LVP bit is set. The LVP bit defaults to a '1' from the factory.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin and should be held low during normal operation.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 5 in the TRISB register must be cleared to disable the pull-up on RB5 and ensure the proper operation of the device.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only High-Voltage Programming mode can be used to program the device.

When using Low-Voltage ICSP Programming, the part must be supplied 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the codeprotect bits from an on state to an off state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs or user code can be reprogrammed or added.

| Mnem     | onic,  | Description                    | Qualas | 16-  | Bit Instr | uction W | Vord | Status    | Natas |

|----------|--------|--------------------------------|--------|------|-----------|----------|------|-----------|-------|

| Operands |        | Description                    | Cycles | MSb  |           |          | LSb  | Affected  | Notes |

| CONTROL  | OPERAT | IONS                           |        |      |           |          |      |           |       |

| BC       | n      | Branch if Carry                | 1 (2)  | 1110 | 0010      | nnnn     | nnnn | None      |       |

| BN       | n      | Branch if Negative             | 1 (2)  | 1110 | 0110      | nnnn     | nnnn | None      |       |

| BNC      | n      | Branch if Not Carry            | 1 (2)  | 1110 | 0011      | nnnn     | nnnn | None      |       |

| BNN      | n      | Branch if Not Negative         | 1 (2)  | 1110 | 0111      | nnnn     | nnnn | None      |       |

| BNOV     | n      | Branch if Not Overflow         | 1 (2)  | 1110 | 0101      | nnnn     | nnnn | None      |       |

| BNZ      | n      | Branch if Not Zero             | 1 (2)  | 1110 | 0001      | nnnn     | nnnn | None      |       |

| BOV      | n      | Branch if Overflow             | 1 (2)  | 1110 | 0100      | nnnn     | nnnn | None      |       |

| BRA      | n      | Branch Unconditionally         | 2      | 1101 | 0nnn      | nnnn     | nnnn | None      |       |

| BZ       | n      | Branch if Zero                 | 1 (2)  | 1110 | 0000      | nnnn     | nnnn | None      |       |

| CALL     | n, s   | Call subroutine 1st word       | 2      | 1110 | 110s      | kkkk     | kkkk | None      |       |

|          |        | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| CLRWDT   | —      | Clear Watchdog Timer           | 1      | 0000 | 0000      | 0000     | 0100 | TO, PD    |       |

| DAW      | —      | Decimal Adjust WREG            | 1      | 0000 | 0000      | 0000     | 0111 | С         |       |

| GOTO     | n      | Go to address 1st word         | 2      | 1110 | 1111      | kkkk     | kkkk | None      |       |

|          |        | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| NOP      | —      | No Operation                   | 1      | 0000 | 0000      | 0000     | 0000 | None      |       |

| NOP      | _      | No Operation                   | 1      | 1111 | xxxx      | xxxx     | xxxx | None      | 4     |

| POP      | —      | Pop top of return stack (TOS)  | 1      | 0000 | 0000      | 0000     | 0110 | None      |       |

| PUSH     | —      | Push top of return stack (TOS) | 1      | 0000 | 0000      | 0000     | 0101 | None      |       |

| RCALL    | n      | Relative Call                  | 2      | 1101 | 1nnn      | nnnn     | nnnn | None      |       |

| RESET    |        | Software device Reset          | 1      | 0000 | 0000      | 1111     | 1111 | All       |       |

| RETFIE   | S      | Return from interrupt enable   | 2      | 0000 | 0000      | 0001     | 000s | GIE/GIEH, |       |

|          |        |                                |        |      |           |          |      | PEIE/GIEL |       |

| RETLW    | k      | Return with literal in WREG    | 2      | 0000 | 1100      | kkkk     | kkkk | None      |       |

| RETURN   | S      | Return from Subroutine         | 2      | 0000 | 0000      | 0001     | 001s | None      |       |

| SLEEP    | _      | Go into Standby mode           | 1      | 0000 | 0000      | 0000     | 0011 | TO, PD    |       |

#### TABLE 24-1: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note** 1: When a Port register is modified as a function of itself (e.g., MOVF PORTE, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| ΒZ                                                                                                                                                                                                                                                                                 |                                      | Branch if                 | Zero                 |       |                                            |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|----------------------|-------|--------------------------------------------|--|--|--|--|

| Synt                                                                                                                                                                                                                                                                               | ax:                                  | [ <i>label</i> ] B        | Zn                   |       |                                            |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                | rands:                               | -128 ≤ n ≤                | $-128 \le n \le 127$ |       |                                            |  |  |  |  |

| Ope                                                                                                                                                                                                                                                                                | ration:                              | if Zero bit<br>(PC) + 2 + | is '1'<br>· 2n → PC  |       |                                            |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                              | us Affected:                         | None                      |                      |       |                                            |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                               | oding:                               | 1110                      | 0000 r               | nnn   | nnnn                                       |  |  |  |  |

| Description: If the Zero bit is '1', then the<br>program will branch.<br>The 2's complement number '2n<br>added to the PC. Since the PC '<br>have incremented to fetch the ne<br>instruction, the new address will<br>PC+2+2n. This instruction is the<br>a two-cycle instruction. |                                      |                           |                      |       | r '2n' is<br>PC will<br>ne next<br>will be |  |  |  |  |

| Word                                                                                                                                                                                                                                                                               | ds:                                  | 1                         |                      |       |                                            |  |  |  |  |

| Cycl                                                                                                                                                                                                                                                                               | es:                                  | 1(2)                      |                      |       |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | ycle Activity:                       |                           |                      |       |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | Q1                                   | Q2                        | Q3                   |       | Q4                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | Decode                               | Read literal<br>'n'       | Process<br>Data      | Write | e to PC                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | No                                   | No                        | No                   |       | No                                         |  |  |  |  |

| IF NL                                                                                                                                                                                                                                                                              | operation                            | operation                 | operation            | n ope | eration                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | o Jump:<br>Q1                        | Q2                        | Q3                   |       | Q4                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | Decode                               | Read literal              | Process              |       | No                                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                    |                                      | 'n'                       | Data                 | оре   | eration                                    |  |  |  |  |

| <u>Exar</u>                                                                                                                                                                                                                                                                        | <u>nple</u> :<br>Before Instru<br>PC |                           | BZ Jur<br>dress (HEF | -     |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | After Instruct                       |                           | uless (ner           | (6)   |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | If Zero                              | = 1;                      |                      |       |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | PC<br>If Zero                        | = 0;                      | dress (Jun           | -     |                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | PC                                   | = ad                      | dress (HEF           | RE+2) |                                            |  |  |  |  |