Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

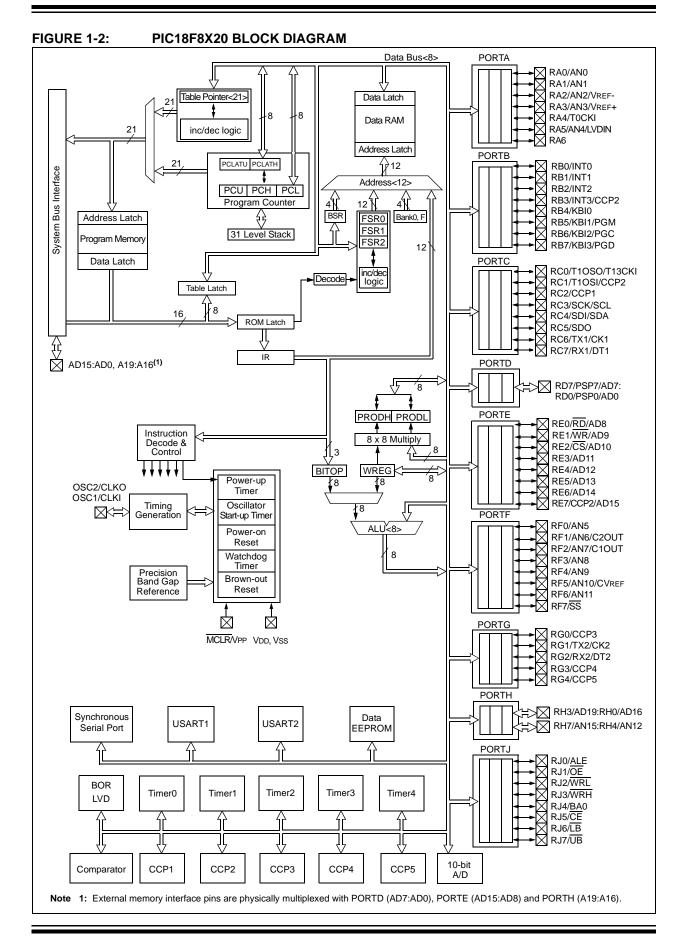

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 68                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.75K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8720-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name      | Pin N             | umber        | Pin     | Buffer | Description                         |

|---------------|-------------------|--------------|---------|--------|-------------------------------------|

| Pin Name      | PIC18F6X20        | PIC18F8X20   | Туре    | Туре   | Description                         |

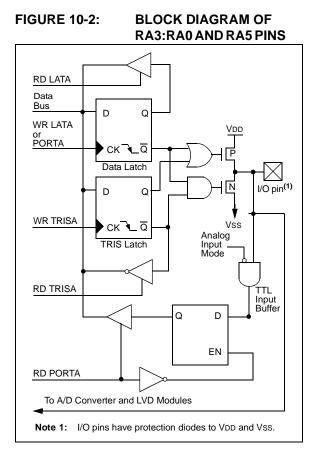

|               |                   |              |         |        | PORTA is a bidirectional I/O port.  |

| RA0/AN0       | 24                | 30           |         |        |                                     |

| RA0           |                   |              | I/O     | TTL    | Digital I/O.                        |

| AN0           |                   |              | I       | Analog | Analog input 0.                     |

| RA1/AN1       | 23                | 29           |         |        |                                     |

| RA1           |                   |              | I/O     | TTL    | Digital I/O.                        |

| AN1           |                   |              | I       | Analog | Analog input 1.                     |

| RA2/AN2/VREF- | 22                | 28           |         | -      | -                                   |

| RA2           |                   |              | I/O     | TTL    | Digital I/O.                        |

| AN2           |                   |              | I       | Analog | Analog input 2.                     |

| Vref-         |                   |              | I       | Analog | A/D reference voltage (Low) input.  |

| RA3/AN3/VREF+ | 21                | 27           |         | Ū      |                                     |

| RA3           |                   |              | I/O     | TTL    | Digital I/O.                        |

| AN3           |                   |              | ., C    | Analog | Analog input 3.                     |

| VREF+         |                   |              | I       | Analog | A/D reference voltage (High) input. |

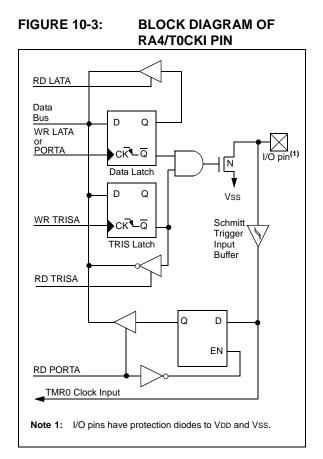

| RA4/T0CKI     | 28                | 34           |         | Ū      |                                     |

| RA4           | 20                | 01           | I/O     | ST/OD  | Digital I/O – Open-drain when       |

|               |                   |              | ., C    | 0.702  | configured as output.               |

| TOCKI         |                   |              | 1       | ST     | Timer0 external clock input.        |

| RA5/AN4/LVDIN | 27                | 33           |         |        |                                     |

| RA5           | 21                | 00           | I/O     | TTL    | Digital I/O.                        |

| AN4           |                   |              |         | Analog | Analog input 4.                     |

| LVDIN         |                   |              | i       | Analog | Low-Voltage Detect input.           |

| RA6           |                   |              |         |        | See the OSC2/CLKO/RA6 pin.          |

| -             | compatible inp    | l            |         | CMOS - | CMOS compatible input or output     |

|               | nitt Trigger inpu |              | evels   |        | Analog input                        |

| I = Inpu      |                   |              |         | •      |                                     |

| P = Pow       |                   |              |         | -      | Open-Drain (no P diode to VDD)      |

|               | •••               | CP2 when CCF | P2MX is |        | ed (all operating modes except      |

| Microcontro   | -                 |              | 2101/13 |        | a (an operating modes except        |

#### TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

**6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

| TABLE 3-3.             |                    |            |                                    |                                                               |                                 |  |

|------------------------|--------------------|------------|------------------------------------|---------------------------------------------------------------|---------------------------------|--|

| Register               | Applicable Devices |            | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| PORTJ                  | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |

| PORTH                  | PIC18F6X20         | PIC18F8X20 | 0000 xxxx                          | 0000 uuuu                                                     | uuuu uuuu                       |  |

| PORTG                  | PIC18F6X20         | PIC18F8X20 | x xxxx                             | uuuu uuuu                                                     | u uuuu                          |  |

| PORTF                  | PIC18F6X20         | PIC18F8X20 | x000 0000                          | u000 0000                                                     | u000 0000                       |  |

| PORTE                  | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| PORTD                  | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| PORTC                  | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| PORTB                  | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| PORTA <sup>(5,6)</sup> | PIC18F6X20         | PIC18F8X20 | -x0x 0000 <b>(5)</b>               | -u0u 0000 <b>(5)</b>                                          | -uuu uuuu <sup>(5)</sup>        |  |

| TMR4                   | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |

| PR4                    | PIC18F6X20         | PIC18F8X20 | 1111 1111                          | 1111 1111                                                     | սսսս սսսս                       |  |

| T4CON                  | PIC18F6X20         | PIC18F8X20 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |

| CCPR4H                 | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| CCPR4L                 | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                                     | սսսս սսսս                       |  |

| CCP4CON                | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |

| CCPR5H                 | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | սսսս սսսս                                                     | սսսս սսսս                       |  |

| CCPR5L                 | PIC18F6X20         | PIC18F8X20 | XXXX XXXX                          | uuuu uuuu                                                     | սսսս սսսս                       |  |

| CCP5CON                | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| SPBRG2                 | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |

| RCREG2                 | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |

| TXREG2                 | PIC18F6X20         | PIC18F8X20 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |

| TXSTA2                 | PIC18F6X20         | PIC18F8X20 | 0000 -010                          | 0000 -010                                                     | uuuu -uuu                       |  |

| RCSTA2                 | PIC18F6X20         | PIC18F8X20 | 0000 000x                          | x000 0000x                                                    | սսսս սսսս                       |  |

#### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for Reset value for specific condition.

5: Bit 6 of PORTA, LATA and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

#### TABLE 4-2: SPECIAL FUNCTION REGISTER MAP (CONTINUED)

| Address | Name    | Address | Name | Address | Name | Address | Name |

|---------|---------|---------|------|---------|------|---------|------|

| F7Fh    | (1)     | F5Fh    | (1)  | F3Fh    | (1)  | F1Fh    | (1)  |

| F7Eh    | (1)     | F5Eh    | (1)  | F3Eh    | (1)  | F1Eh    | (1)  |

| F7Dh    | (1)     | F5Dh    | (1)  | F3Dh    | (1)  | F1Dh    | (1)  |

| F7Ch    | (1)     | F5Ch    | (1)  | F3Ch    | _(1) | F1Ch    | (1)  |

| F7Bh    | (1)     | F5Bh    | (1)  | F3Bh    | (1)  | F1Bh    | (1)  |

| F7Ah    | (1)     | F5Ah    | (1)  | F3Ah    | (1)  | F1Ah    | (1)  |

| F79h    | (1)     | F59h    | (1)  | F39h    | (1)  | F19h    | (1)  |

| F78h    | TMR4    | F58h    | (1)  | F38h    | (1)  | F18h    | (1)  |

| F77h    | PR4     | F57h    | (1)  | F37h    | (1)  | F17h    | (1)  |

| F76h    | T4CON   | F56h    | (1)  | F36h    | _(1) | F16h    | (1)  |

| F75h    | CCPR4H  | F55h    | (1)  | F35h    | (1)  | F15h    | (1)  |

| F74h    | CCPR4L  | F54h    | (1)  | F34h    | _(1) | F14h    | (1)  |

| F73h    | CCP4CON | F53h    | (1)  | F33h    | _(1) | F13h    | (1)  |

| F72h    | CCPR5H  | F52h    | (1)  | F32h    | _(1) | F12h    | (1)  |

| F71h    | CCPR5L  | F51h    | (1)  | F31h    | _(1) | F11h    | (1)  |

| F70h    | CCP5CON | F50h    | (1)  | F30h    | _(1) | F10h    | (1)  |

| F6Fh    | SPBRG2  | F4Fh    | (1)  | F2Fh    | (1)  | F0Fh    | (1)  |

| F6Eh    | RCREG2  | F4Eh    | (1)  | F2Eh    | _(1) | F0Eh    | (1)  |

| F6Dh    | TXREG2  | F4Dh    | (1)  | F2Dh    | _(1) | F0Dh    | _(1) |

| F6Ch    | TXSTA2  | F4Ch    | (1)  | F2Ch    | _(1) | F0Ch    | (1)  |

| F6Bh    | RCSTA2  | F4Bh    | (1)  | F2Bh    | _(1) | F0Bh    | (1)  |

| F6Ah    | (1)     | F4Ah    | (1)  | F2Ah    | _(1) | F0Ah    | _(1) |

| F69h    | (1)     | F49h    | (1)  | F29h    | (1)  | F09h    | (1)  |

| F68h    | (1)     | F48h    | (1)  | F28h    | (1)  | F08h    | (1)  |

| F67h    | (1)     | F47h    | (1)  | F27h    | _(1) | F07h    | (1)  |

| F66h    | (1)     | F46h    | (1)  | F26h    | (1)  | F06h    | (1)  |

| F65h    | (1)     | F45h    | (1)  | F25h    | _(1) | F05h    | (1)  |

| F64h    | (1)     | F44h    | (1)  | F24h    | _(1) | F04h    | _(1) |

| F63h    | (1)     | F43h    | (1)  | F23h    | (1)  | F03h    | (1)  |

| F62h    | _(1)    | F42h    | (1)  | F22h    | _(1) | F02h    | (1)  |

| F61h    | (1)     | F41h    | (1)  | F21h    | (1)  | F01h    | (1)  |

| F60h    | (1)     | F40h    | (1)  | F20h    | (1)  | F00h    | (1)  |

Note 1: Unimplemented registers are read as '0'.

2: This register is not available on PIC18F6X20 devices.

3: This is not a physical register.

#### 4.10 Access Bank

The Access Bank is an architectural enhancement, which is very useful for C compiler code optimization. The techniques used by the C compiler may also be useful for programs written in assembly.

This data memory region can be used for:

- Intermediate computational values

- · Local variables of subroutines

- · Faster context saving/switching of variables

- · Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 160 bytes in Bank 15 (SFRs) and the lower 96 bytes in Bank 0. These two sections will be referred to as Access RAM High and Access RAM Low, respectively. Figure 4-7 indicates the Access RAM areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank. This bit is denoted by the 'a' bit (for access bit).

When forced in the Access Bank (a = 0), the last address in Access RAM Low is followed by the first address in Access RAM High. Access RAM High maps the Special Function Registers, so that these registers can be accessed without any software overhead. This is useful for testing status flags and modifying control bits.

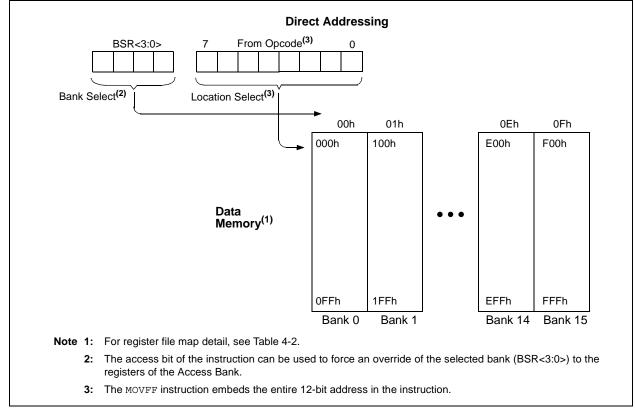

#### 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The Status register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR, since the 12-bit addresses are embedded into the instruction word.

Section 4.12 "Indirect Addressing, INDF and FSR Registers" provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### FIGURE 4-8: DIRECT ADDRESSING

| REGISTER 5-1: | EECON1 F                                                                                                                                                                                                                                                                                                            | REGISTER                                                                                                                                                                       | (ADDRE                     | SS FA6h)                    |                                  |              |               |            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|----------------------------------|--------------|---------------|------------|

|               | R/W-x                                                                                                                                                                                                                                                                                                               | R/W-x                                                                                                                                                                          | U-0                        | R/W-0                       | R/W-x                            | R/W-0        | R/S-0         | R/S-0      |

|               | EEPGD                                                                                                                                                                                                                                                                                                               | CFGS                                                                                                                                                                           | _                          | FREE                        | WRERR                            | WREN         | WR            | RD         |

|               | bit 7                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                |                            |                             |                                  |              |               | bit 0      |

| bit 7         | EEPGD: F                                                                                                                                                                                                                                                                                                            | lash Prograr                                                                                                                                                                   | n or Data E                |                             | mory Select b                    | it           |               |            |

|               | 1 = Acces                                                                                                                                                                                                                                                                                                           | <ul> <li>1 = Access Flash program memory</li> <li>0 = Access data EEPROM memory</li> </ul>                                                                                     |                            |                             |                                  |              |               |            |

| bit 6         |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                |                            | -                           | figuration Sele                  | ct bit       |               |            |

|               |                                                                                                                                                                                                                                                                                                                     | s configurati<br>s Flash prog                                                                                                                                                  | -                          | s<br>a EEPROM               | memory                           |              |               |            |

| bit 5         | Unimplem                                                                                                                                                                                                                                                                                                            | ented: Read                                                                                                                                                                    | <b>d as</b> '0'            |                             |                                  |              |               |            |

| bit 4         | FREE: Flas                                                                                                                                                                                                                                                                                                          | sh Row Eras                                                                                                                                                                    | se Enable b                | oit                         |                                  |              |               |            |

|               | (cleare                                                                                                                                                                                                                                                                                                             | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul> |                            |                             |                                  |              |               |            |

| bit 3         | WRERR: F                                                                                                                                                                                                                                                                                                            | lash Progra                                                                                                                                                                    | m/Data EE                  | PROM Error                  | <sup>·</sup> Flag bit            |              |               |            |

|               | (any R<br>0 = The w                                                                                                                                                                                                                                                                                                 | leset during rite operatio                                                                                                                                                     | self-timed  <br>n complete | d                           | g in normal ope                  | ,            |               |            |

|               | Note:                                                                                                                                                                                                                                                                                                               | When a Wi<br>tracing of th                                                                                                                                                     |                            |                             | GD and CFGS                      | bits are not | t cleared. T  | his allows |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                           | ash Program                                                                                                                                                                    | /Data EEP                  | ROM Write I                 | Enable bit                       |              |               |            |

|               |                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                              | •                          | rogram/data<br>program/data |                                  |              |               |            |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                           | Control bit                                                                                                                                                                    |                            |                             |                                  |              |               |            |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle. (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                                                                                                                                                                |                            |                             |                                  |              |               |            |

| bit 0         | RD: Read                                                                                                                                                                                                                                                                                                            | •                                                                                                                                                                              |                            | bompiete                    |                                  |              |               |            |

| bit 0         | 1 = Initiate<br>can or                                                                                                                                                                                                                                                                                              | s an EEPR                                                                                                                                                                      | ot cleared)                | in software.                | ne cycle. RD is<br>RD bit cannot |              |               |            |

|               | Legend:                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                |                            |                             |                                  |              |               | ]          |

|               | R = Reada                                                                                                                                                                                                                                                                                                           | ble bit                                                                                                                                                                        | W = V                      | Vritable bit                | U = Unimp                        | lemented bi  | it. read as ' | 0'         |

|               |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                |                            |                             | -                                |              |               |            |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

#### 6.0 EXTERNAL MEMORY **INTERFACE**

| Note: | The            | External | Me | mory | Interface | is   | not   |

|-------|----------------|----------|----|------|-----------|------|-------|

|       | imple<br>devic |          | on | PIC1 | 8F6X20    | (64- | ·pin) |

The External Memory Interface is a feature of the PIC18F8X20 devices that allows the controller to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory.

The physical implementation of the interface uses 27 pins. These pins are reserved for external address/data bus functions; they are multiplexed with I/O port pins on four ports. Three I/O ports are multiplexed with the address/data bus, while the fourth port is multiplexed with the bus control signals. The I/O port functions are enabled when the EBDIS bit in the MEMCON register is set (see Register 6-1). A list of the multiplexed pins and their functions is provided in Table 6-1.

As implemented in the PIC18F8X20 devices, the interface operates in a similar manner to the external memory interface introduced on PIC18C601/801 microcontrollers. The most notable difference is that the interface on PIC18F8X20 devices only operates in 16-bit modes. The 8-bit mode is not supported.

For a more complete discussion of the operating modes that use the external memory interface, refer to Section 4.1.1 "PIC18F8X20 Program Memory Modes".

R/W-0

U-0

R/W-0

#### 6.1 **Program Memory Modes and the External Memory Interface**

As previously noted, PIC18F8X20 controllers are capable of operating in any one of four program memory modes, using combinations of on-chip and external program memory. The functions of the multiplexed port pins depend on the program memory mode selected, as well as the setting of the EBDIS bit.

In Microprocessor Mode, the external bus is always active and the port pins have only the external bus function.

In Microcontroller Mode, the bus is not active and the pins have their port functions only. Writes to the MEMCOM register are not permitted.

In Microprocessor with Boot Block or Extended Microcontroller Mode, the external program memory bus shares I/O port functions on the pins. When the device is fetching or doing table read/table write operations on the external program memory space, the pins will have the external bus function. If the device is fetching and accessing internal program memory locations only, the EBDIS control bit will change the pins from external memory to I/O port functions. When EBDIS = 0, the pins function as the external bus. When EBDIS = 1, the pins function as I/O ports.

Note: Maximum Fosc for the PIC18FX520 is limited to 25 MHz when using the external memory interface.

R/W-0

R/W-0

U-0

|         | EBDIS                                  | —                                                                                                                                                                                                                                                                                                                                                                                                         | WAIT1           | WAIT0        | —           | —          | WM1          | WM0           |  |

|---------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|------------|--------------|---------------|--|

|         | bit7                                   | L                                                                                                                                                                                                                                                                                                                                                                                                         | I               | 1            |             | I          |              | bit0          |  |

|         |                                        |                                                                                                                                                                                                                                                                                                                                                                                                           |                 |              |             |            |              |               |  |

| bit 7   | EBDIS: Ex                              | ternal Bus D                                                                                                                                                                                                                                                                                                                                                                                              | isable bit      |              |             |            |              |               |  |

|         |                                        | al system bu<br>al system bu                                                                                                                                                                                                                                                                                                                                                                              |                 |              |             |            | as I/O ports |               |  |

| bit 6   | Unimplem                               | Inimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |                 |              |             |            |              |               |  |

| bit 5-4 | 11 = Table<br>10 = Table<br>01 = Table | <b>NAIT&lt;1:0&gt;:</b> Table Reads and Writes Bus Cycle Wait Count bits<br>1 = Table reads and writes will wait 0 Tcy<br>0 = Table reads and writes will wait 1 Tcy<br>1 = Table reads and writes will wait 2 Tcy<br>0 = Table reads and writes will wait 3 Tcy                                                                                                                                          |                 |              |             |            |              |               |  |

| bit 3-2 | Unimplem                               | ented: Read                                                                                                                                                                                                                                                                                                                                                                                               | <b>d as</b> '0' |              |             |            |              |               |  |

| bit 1-0 | -                                      |                                                                                                                                                                                                                                                                                                                                                                                                           |                 | 16-bit Bus b | oits        |            |              |               |  |

|         | TABL<br>01 = Byte \$<br>will ac        | <ul> <li>WM&lt;1:0&gt;: TBLWRT Operation with 16-bit Bus bits</li> <li>1x = Word Write mode: TABLAT&lt;0&gt; and TABLAT&lt;1&gt; word output, WRH active when TABLAT&lt;1&gt; written</li> <li>01 = Byte Select mode: TABLAT data copied on both MSB and LSB, WRH and (UB or LB) will activate</li> <li>00 = Byte Write mode: TABLAT data copied on both MSB and LSB, WRH or WRL will activate</li> </ul> |                 |              |             |            |              |               |  |

|         | 00 = Byte V                            | write mode:                                                                                                                                                                                                                                                                                                                                                                                               | TABLAT DAT      | a copied on  | DOTU MOR S  | and LSB, W |              | will activate |  |

|         | Legend:                                |                                                                                                                                                                                                                                                                                                                                                                                                           |                 |              |             |            |              |               |  |

|         | R = Reada                              | ble bit                                                                                                                                                                                                                                                                                                                                                                                                   | W = W           | /ritable bit | U = Unim    | nplemented | bit, read as | '0'           |  |

|         | - n = Value                            | at POR                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = B         | it is set    | '0' = Bit i | s cleared  | x = Bit is u | nknown        |  |

R/W-0

U-0

#### **REGISTER 6-1:** MEMCON REGISTER

| LIN 3-11. | IF NZ. FLN                                       | IFILINAL   |                 |                | I I KLOIS     |           |              |        |

|-----------|--------------------------------------------------|------------|-----------------|----------------|---------------|-----------|--------------|--------|

|           | U-0                                              | R/W-1      | U-0             | R/W-1          | R/W-1         | R/W-1     | R/W-1        | R/W-1  |

|           | —                                                | CMIP       | _               | EEIP           | BCLIP         | LVDIP     | TMR3IP       | CCP2IP |

|           | bit 7                                            |            |                 |                |               |           |              | bit 0  |

| bit 7     | Unimpleme                                        | ented: Rea | <b>d as</b> '0' |                |               |           |              |        |

| bit 6     | <b>CMIP:</b> Com<br>1 = High pri<br>0 = Low pri  | iority     | errupt Priorit  | y bit          |               |           |              |        |

| bit 5     | Unimpleme                                        | ented: Rea | <b>d as</b> '0' |                |               |           |              |        |

| bit 4     | <b>EEIP:</b> Data<br>1 = High pri<br>0 = Low pri | iority     | Flash Write     | Operation In   | terrupt Prior | ity bit   |              |        |

| bit 3     | <b>BCLIP:</b> Bus<br>1 = High pri<br>0 = Low pri | iority     | nterrupt Prio   | rity bit       |               |           |              |        |

| bit 2     | <b>LVDIP:</b> Low<br>1 = High pri<br>0 = Low pri | iority     | etect Interru   | pt Priority bi | t             |           |              |        |

| bit 1     | <b>TMR3IP:</b> T<br>1 = High pr<br>0 = Low pri   | iority     | ow Interrupt    | Priority bit   |               |           |              |        |

| bit 0     | <b>CCP2IP:</b> C<br>1 = High pr<br>0 = Low pri   | iority     | pt Priority bi  | t              |               |           |              |        |

|           | Legend:                                          |            |                 |                |               |           |              |        |

|           | R = Readal                                       | ole bit    | W = W           | ritable bit    | U = Unin      | plemented | bit, read as | '0'    |

|           | 1                                                |            |                 |                |               |           |              |        |

'1' = Bit is set

'0' = Bit is cleared

### REGISTER 9-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

- n = Value at POR

x = Bit is unknown

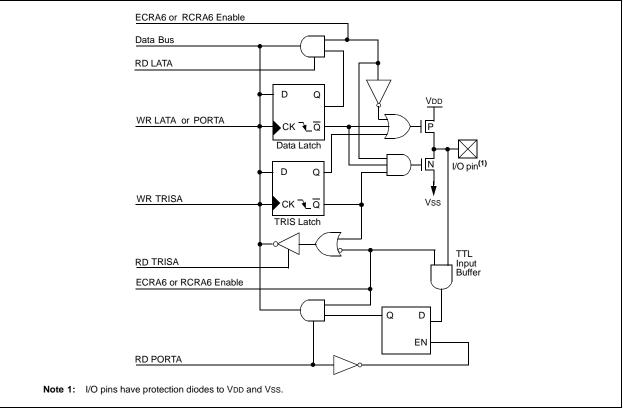

### FIGURE 10-4: BLOCK DIAGRAM OF RA6 PIN (WHEN ENABLED AS I/O)

### 13.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 13-1. Timer2 can be shut-off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption. Figure 13-1 is a simplified block diagram of the Timer2 module. Register 13-1 shows the Timer2 Control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

#### 13.1 Timer2 Operation

Timer2 can be used as the PWM time base for the PWM mode of the CCP module. The TMR2 register is readable and writable and is cleared on any device Reset. The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit, TMR2IF (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |  |

|-------|----------|----------|----------|----------|--------|---------|---------|--|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |  |

| bit 7 |          |          |          |          |        |         | bit 0   |  |

#### bit 7 Unimplemented: Read as '0'

bit 6-3 T2OUTPS3:T2OUTPS0: Timer2 Output Postscale Select bits

|   |  | Postscale<br>Postscale |  |

|---|--|------------------------|--|

| • |  |                        |  |

| • |  |                        |  |

| • |  |                        |  |

1111 = 1:16 Postscale

- bit 2 TMR2ON: Timer2 On bit

- 1 = Timer2 is on

- 0 = Timer2 is off

#### bit 1-0 T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits

- 00 =Prescaler is 1

- 01 =Prescaler is 4

- 1x = Prescaler is 16

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 19.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2 Tosc

- 4 Tosc

- 8 Tosc

- 16 Tosc

- 32 Tosc

- 64 Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 19-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

### 19.3 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert as an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume current out of the device's specification limits.

#### TABLE 19-1: TAD VS. DEVICE OPERATING FREQUENCIES

| AD Clock S | ource (TAD) | Maximum Device Frequency |             |  |  |

|------------|-------------|--------------------------|-------------|--|--|

| Operation  | ADCS2:ADCS0 | PIC18FXX20               | PIC18LFXX20 |  |  |

| 2 Tosc     | 000         | 1.25 MHz                 | 666 kHz     |  |  |

| 4 Tosc     | 100         | 2.50 MHz                 | 1.33 MHz    |  |  |

| 8 Tosc     | 001         | 5.00 MHz                 | 2.67 MHz    |  |  |

| 16 Tosc    | 101         | 10.0 MHz                 | 5.33 MHz    |  |  |

| 32 Tosc    | 010         | 20.0 MHz                 | 10.67 MHz   |  |  |

| 64 Tosc    | 110         | 40.0 MHz                 | 21.33 MHz   |  |  |

| RC         | x11         | _                        | —           |  |  |

| REGISTER 23-7: | CONFIG5                                                                                                                  | L: CONFIC                | JURATION                         | REGISTE                       | R 5 LOW (E | BYTE ADD    | RESS 3000     | 08h)       |

|----------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|-------------------------------|------------|-------------|---------------|------------|

|                | R/P-1                                                                                                                    | R/P-1                    | R/P-1                            | R/P-1                         | R/P-1      | R/P-1       | R/P-1         | R/P-1      |

|                | CP7 <sup>(1)</sup>                                                                                                       | CP6 <sup>(1)</sup>       | CP5 <sup>(1)</sup>               | CP4 <sup>(1)</sup>            | CP3        | CP2         | CP1           | CP0        |

|                | bit 7                                                                                                                    |                          |                                  |                               |            |             |               | bit 0      |

| h:4 7          |                                                                                                                          | Protection               | ь:µ(1)                           |                               |            |             |               |            |

| bit 7          |                                                                                                                          |                          |                                  | landa proto                   | otod       |             |               |            |

|                |                                                                                                                          |                          |                                  | t code-proted<br>de-protected |            |             |               |            |

| bit 6          |                                                                                                                          | Protection               |                                  |                               |            |             |               |            |

|                | 1 = Block 6                                                                                                              | 5 (018000-0 <sup>-</sup> | 1BFFFh) not                      | code-protec                   | cted       |             |               |            |

|                |                                                                                                                          |                          |                                  | de-protected                  |            |             |               |            |

| bit 5          |                                                                                                                          | Protection               |                                  |                               |            |             |               |            |

|                |                                                                                                                          |                          |                                  | code-protec                   | ted        |             |               |            |

| bit 4          |                                                                                                                          | Protection               | 17FFFh) coc<br>հit <b>(1)</b>    | le-protected                  |            |             |               |            |

| Dit 4          |                                                                                                                          |                          |                                  | code-protec                   | tod        |             |               |            |

|                |                                                                                                                          | •                        | 13FFFh) coc                      | •                             | leu        |             |               |            |

| bit 3          |                                                                                                                          | Protection               | -                                | ·                             |            |             |               |            |

|                | For PIC18F                                                                                                               | X520 devic               | es:                              |                               |            |             |               |            |

|                | 1 = Block 3 (006000-007FFFh) not code-protected                                                                          |                          |                                  |                               |            |             |               |            |

|                | 0 = Block 3 (006000-007FFh) code-protected                                                                               |                          |                                  |                               |            |             |               |            |

|                | For PIC18FX620 and PIC18FX720 devices:<br>1 = Block 3 (00C000-00FFFFh) not code-protected                                |                          |                                  |                               |            |             |               |            |

|                |                                                                                                                          |                          |                                  | de-protected                  |            |             |               |            |

| bit 2          |                                                                                                                          | Protection               |                                  | •                             |            |             |               |            |

|                | For PIC18F                                                                                                               | X520 devic               | es:                              |                               |            |             |               |            |

|                | 1 = Block 2 (004000-005FFFh) not code-protected                                                                          |                          |                                  |                               |            |             |               |            |

|                | 0 = Block 2 (004000-005FFFh) code-protected                                                                              |                          |                                  |                               |            |             |               |            |

|                | For PIC18FX620 and PIC18FX720 devices:<br>1 = Block 2 (008000-00BFFFh) not code-protected                                |                          |                                  |                               |            |             |               |            |

|                |                                                                                                                          | •                        |                                  | de-protected                  | lou        |             |               |            |

| bit 1          | CP1: Code                                                                                                                | Protection               | bit                              |                               |            |             |               |            |

|                |                                                                                                                          | X520 devic               |                                  |                               |            |             |               |            |

|                |                                                                                                                          |                          |                                  | code-protec                   | ted        |             |               |            |

|                |                                                                                                                          | -                        | 03FFFh) coc<br><u>PIC18FX720</u> | -                             |            |             |               |            |

|                |                                                                                                                          |                          |                                  | code-protec                   | ted        |             |               |            |

|                |                                                                                                                          |                          | )<br>7FFFh) coc                  |                               |            |             |               |            |

| bit 0          | CP0: Code                                                                                                                | Protection               | bit                              |                               |            |             |               |            |

|                | For PIC18FX520 devices:                                                                                                  |                          |                                  |                               |            |             |               |            |

|                | <ul> <li>1 = Block 0 (000800-001FFFh) not code-protected</li> <li>0 = Block 0 (000800-001FFFh) code-protected</li> </ul> |                          |                                  |                               |            |             |               |            |

|                |                                                                                                                          | -                        | PIC18FX720                       | -                             |            |             |               |            |

|                |                                                                                                                          |                          |                                  | code-protec                   | ted        |             |               |            |

|                |                                                                                                                          |                          | 03FFFh) coc                      |                               |            |             |               |            |

|                | Note 1:                                                                                                                  | Unimpleme                | ented in PIC                     | 18FX520 and                   | d PIC18FX6 | 20 devices; | maintain this | s bit set. |

|                | Legend:                                                                                                                  |                          |                                  |                               |            |             |               | ]          |

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

|         | R/C-1<br>CPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/C-1       | U-0                            | U-0      | U-0      | U-0        | U-0             | U-0   |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|----------|----------|------------|-----------------|-------|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                | 00       | 0-0      | 0-0        | 0-0             | 0-0   |

|         | GFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CPB         | _                              | —        | —        |            | —               | —     |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                |          |          |            |                 | bit 0 |

| bit 7   | 1 = Data El                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EPROM not   | Code Protect<br>code-protected | cted     |          |            |                 |       |

| bit 6   | <ul> <li>0 = Data EEPROM code-protected</li> <li>CPB: Boot Block Code Protection bit</li> <li>For PIC18FX520 devices:</li> <li>1 = Boot Block (000000-0007FFh) not code-protected</li> <li>0 = Boot Block (000000-0007FFh) code-protected</li> <li>For PIC18FX620 and PIC18FX720 devices:</li> <li>1 = Boot Block (000000-0001FFh) not code-protected</li> <li>0 = Boot Block (000000-0001FFh) not code-protected</li> <li>0 = Boot Block (000000-0001FFh) code-protected</li> </ul> |             |                                |          |          |            |                 |       |

| bit 5-0 | Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ented: Read | <b>d as</b> '0'                |          |          |            |                 |       |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                |          |          |            |                 |       |

|         | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ble bit     | C = Clear                      | able bit | U = Unin | nplemented | bit, read as 'C | )'    |

u = Unchanged from programmed state

- n = Value when device is unprogrammed

REGISTER 23-8:

|       | R/P-1                                                                                                           | R/P-1                    | R/P-1                                     | R/P-1                        | R/P-1 | R/P-1 | R/P-1 | R/P-1 |

|-------|-----------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|------------------------------|-------|-------|-------|-------|

|       | WRT7 <sup>(1)</sup>                                                                                             | WRT6 <sup>(1)</sup>      | WRT5 <sup>(1)</sup>                       | WRT4 <sup>(1)</sup>          | WRT3  | WRT2  | WRT1  | WRT0  |

|       | bit 7                                                                                                           |                          |                                           |                              |       |       |       | bit C |

| bit 7 | WR7: Write                                                                                                      | Protection               | bit <sup>(1)</sup>                        |                              |       |       |       |       |

|       |                                                                                                                 | •                        | ,                                         | write-protected              | ted   |       |       |       |

| bit 6 |                                                                                                                 | Protection               |                                           | •                            |       |       |       |       |

|       |                                                                                                                 |                          | ,                                         | write-protec<br>te-protected | ted   |       |       |       |

| bit 5 | WR5: Write                                                                                                      | Protection               | bit <sup>(1)</sup>                        |                              |       |       |       |       |

|       |                                                                                                                 |                          | 17FFFh) not<br>17FFFh) writ               | write-protected              | ted   |       |       |       |

| bit 4 | WR4: Write                                                                                                      | Protection               | bit <sup>(1)</sup>                        |                              |       |       |       |       |

|       |                                                                                                                 |                          | 13FFFh) not<br>13FFFh) writ               | write-protect<br>e-protected | ted   |       |       |       |

| bit 3 | WR3: Write                                                                                                      | Protection               | bit                                       |                              |       |       |       |       |

|       | 1 = Block 3                                                                                                     | •                        |                                           | write-protect                | ted   |       |       |       |

|       | 1 = Block 3                                                                                                     | (00C000-0                |                                           | write-protec                 | ted   |       |       |       |

| bit 2 |                                                                                                                 | •                        |                                           | te-protected                 |       |       |       |       |

| Dit 2 | WR2: Write Protection bit<br><u>For PIC18FX520 devices:</u><br>1 = Block 2 (004000-005FFFh) not write-protected |                          |                                           |                              |       |       |       |       |

|       | For PIC18F<br>1 = Block 2                                                                                       | X620 and F<br>(008000-00 | -                                         | •                            | ted   |       |       |       |

| bit 1 |                                                                                                                 | Protection               | •                                         |                              |       |       |       |       |

|       | For PIC18F<br>1 = Block 1                                                                                       | X520 devic<br>(002000-00 | <u>es:</u>                                | write-protected              | ted   |       |       |       |

|       | For PIC18F<br>1 = Block 1                                                                                       | X620 and F<br>(004000-00 | PIC18FX720                                | devices:<br>write-protect    | ted   |       |       |       |

| bit 0 |                                                                                                                 | Protection               |                                           | •                            |       |       |       |       |

|       | 1 = Block 0                                                                                                     | •                        |                                           | write-protected              | ted   |       |       |       |

|       | 1 = Block 0                                                                                                     | (000200-00               | PIC18FX720<br>03FFFh) not<br>03FFFh) writ | write-protect                | ted   |       |       |       |

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|