Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6520-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

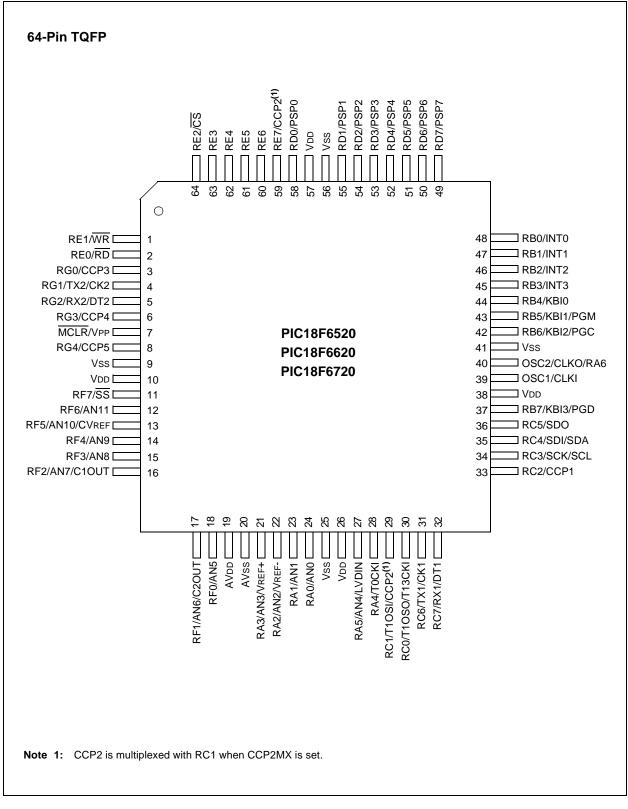

### **Pin Diagrams**

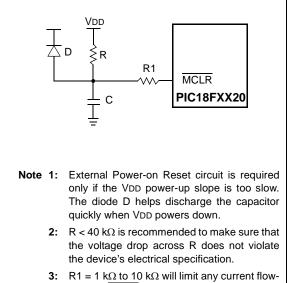

## 3.1 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, tie the  $\overline{\text{MCLR}}$  pin through a 1 k $\Omega$  to 10 k $\Omega$  resistor to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 3-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 3-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

ing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

## 3.2 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33) only on power-up from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/ disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter #33 for details.

## 3.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset, or wake-up from Sleep.

## 3.4 PLL Lock Time-out

With the PLL enabled, the time-out sequence following a Power-on Reset is different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

## 3.5 Brown-out Reset (BOR)

A configuration bit, BOREN, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below parameter D005 for greater than parameter #35, the brown-out situation will reset the chip. A Reset may not occur if VDD falls below parameter D005 for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. If the Power-up Timer is enabled, it will be invoked after VDD rises above BVDD; it then will keep the chip in Reset for an additional time delay (parameter #33). If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute the additional time delay.

## 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired. Then, OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figures 3-3 through 3-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, the time-outs will expire if MCLR is kept low long enough. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes, or to synchronize more than one PIC18FXX20 device operating in parallel.

Table 3-2 shows the Reset conditions for some Special Function Registers, while Table 3-3 shows the Reset conditions for all of the registers.

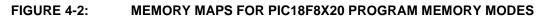

#### **REGISTER 4-1: CONFIG3L CONFIGURATION BYTE** R/P-1 U-0 U-0 U-0 U-0 U-0 R/P-1 R/P-1 WAIT PM1 PM0 bit 7 bit 0 bit 7 WAIT: External Bus Data Wait Enable bit 1 = Wait selections unavailable, device will not wait 0 = Wait programmed by WAIT1 and WAIT0 bits of MEMCOM register (MEMCOM<5:4>) Unimplemented: Read as '0' bit 6-2 bit 1-0 PM1:PM0: Processor Data Memory Mode Select bits 11 = Microcontroller mode 10 = Microprocessor mode 01 = Microcontroller with Boot Block mode 00 = Extended Microcontroller mode Legend: P = Programmable bit U = Unimplemented bit, read as '0' R = Readable bit - n = Value after erase '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

|                         | Microprocessor<br>Mode (MP) |                               |                       |                          | Microproces<br>with Boot Bl<br>Mode (MPB | ock                          | Microco<br>Mode                   | Extended<br>Microcontroller<br>Mode (EMC)     |                                 |                                     |                              |

|-------------------------|-----------------------------|-------------------------------|-----------------------|--------------------------|------------------------------------------|------------------------------|-----------------------------------|-----------------------------------------------|---------------------------------|-------------------------------------|------------------------------|

| Program Space Execution | 000000h                     | External<br>Program<br>Memory | 1                     | 000000<br>Boot<br>Boot+1 | External<br>Program<br>Memory            | On-Chip<br>Program<br>Memory | 000000h<br>Boundary<br>Boundary+1 | On-Chip<br>Program<br>Memory<br>Reads<br>'0's | 000000h<br>Boundary<br>Boundary | +1<br>External<br>Program<br>Memory | On-Chip<br>Program<br>Memory |

|                         |                             | External<br>Memory            | J<br>On-Chip<br>Flash | 1FFFF                    | -n<br>External<br>Memory                 | On-Chip<br>Flash             | 1FFFFFh                           | On-Chip<br>Flash                              | 1FFFFh                          | External<br>Memory                  | On-Chip<br>Flash             |

| Bour                    | ndary Valu                  | es for Mi                     | croprocessor          | with Bo                  | ot Block, Mic                            | rocontrolle                  | r and Extended M                  | licrocontroller ı                             | nodes <sup>(1)</sup>            |                                     |                              |

|                         | Device                      |                               | Boot                  |                          | Boot+                                    | ·1                           | Boundary                          | Bound                                         | lary+1                          | Avail<br>Memory                     |                              |

|                         | PIC18F65                    | 20                            | 0007FF                | h                        | 000800                                   | Dh                           | 007FFFh                           | 0080                                          | 000h                            | M                                   | С                            |

|                         | PIC18F66                    | 20                            | 0001FF                | h                        | 00020                                    | Dh                           | 00FFFFh                           | 0100                                          | 000h                            | M                                   | С                            |

|                         | PIC18F6720 0001FFt          |                               | h                     | 000200h                  |                                          | 01FFFFh                      | 0200                              | 020000h                                       |                                 | MC                                  |                              |

PIC18F8720

0001FFh

000200h

01FFFFh

020000h

MP, MPBB, MC, EMC

Note 1:

PIC18F6X20 devices are included here for completeness, to show the boundaries of their Boot Blocks and program memory spaces.

007FFFh

00FFFFh

008000h

010000h

000800h

000200h

0007FFh

0001FFh

PIC18F8520

PIC18F8620

MP, MPBB, MC, EMC

MP, MPBB, MC, EMC

## 9.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

### **REGISTER 9-1: INTCON REGISTER**

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0         | R/W-x |

|----------|-----------|--------|--------|-------|--------|---------------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF  |

| bit 7    |           |        |        |       |        |               | bit 0 |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit                                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>When IPEN (RCON&lt;7&gt;) = 0</u> :                                                                                                          |

|       | 1 = Enables all unmasked interrupts                                                                                                             |

|       | 0 = Disables all interrupts<br>When IPEN (RCON<7>) = 1:                                                                                         |

|       | 1 = Enables all high priority interrupts                                                                                                        |

|       | 0 = Disables all interrupts                                                                                                                     |

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                      |

|       | When IPEN (RCON<7>) = $0$ :                                                                                                                     |

|       | 1 = Enables all unmasked peripheral interrupts                                                                                                  |

|       | 0 = Disables all peripheral interrupts                                                                                                          |

|       | <u>When IPEN (RCON&lt;7&gt;) = 1</u> :<br>1 = Enables all low priority peripheral interrupts                                                    |

|       | 0 = Disables all low priority peripheral interrupts                                                                                             |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                      |

|       | 1 = Enables the TMR0 overflow interrupt                                                                                                         |

|       | 0 = Disables the TMR0 overflow interrupt                                                                                                        |

| bit 4 | INTOIE: INTO External Interrupt Enable bit                                                                                                      |

|       | 1 = Enables the INTO external interrupt                                                                                                         |

|       | 0 = Disables the INT0 external interrupt                                                                                                        |

| bit 3 | RBIE: RB Port Change Interrupt Enable bit                                                                                                       |

|       | <ol> <li>Enables the RB port change interrupt</li> <li>Disables the RB port change interrupt</li> </ol>                                         |

| bit 2 | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                        |

|       | 1 = TMR0 register has overflowed (must be cleared in software)                                                                                  |

|       | 0 = TMR0 register did not overflow                                                                                                              |

| bit 1 | INTOIF: INTO External Interrupt Flag bit                                                                                                        |

|       | 1 = The INT0 external interrupt occurred (must be cleared in software)                                                                          |

|       | 0 = The INT0 external interrupt did not occur                                                                                                   |

| bit 0 | RBIF: RB Port Change Interrupt Flag bit                                                                                                         |

|       | 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)                                                                |

|       | 0 = None of the RB7:RB4 pins have changed state                                                                                                 |

|       | <b>Note:</b> A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared. |

|       |                                                                                                                                                 |

|       | Lewey de                                                                                                                                        |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 10.5 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

PORTE is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. PORTE is multiplexed with the CCP module (Table 10-9).

On PIC18F8X20 devices, PORTE is also multiplexed with the system bus as the external memory interface; the I/O bus is available only when the system bus is disabled, by setting the EBDIS bit in the MEMCON register (MEMCON<7>). If the device is configured in Microprocessor or Extended Microcontroller mode, then the PORTE<7:0> becomes the high byte of the address/data bus for the external program memory interface. In Microcontroller mode, the PORTE<2:0> pins become the control inputs for the Parallel Slave Port when bit PSPMODE (PSPCON<4>) is set. (Refer to Section 4.1.1 "PIC18F8X20 Program Memory Modes" for more information on program memory modes.) When the Parallel Slave Port is active, three PORTE pins (RE0/RD/AD8, RE1/WR/AD9 and RE2/CS/AD10) function as its control inputs. This automatically occurs when the PSPMODE bit (PSPCON<4>) is set. Users must also make certain that bits TRISE<2:0> are set to configure the pins as digital inputs and the ADCON1 register is configured for digital I/O. The PORTE PSP control functions are summarized in Table 10-9.

Pin RE7 can be configured as the alternate peripheral pin for CCP module 2 when the device is operating in Microcontroller mode. This is done by clearing the configuration bit, CCP2MX, in configuration register, CONFIG3H (CONFIG3H<0>).

| Note: | For PIC18F8X20 (80-pin) devices operat- |

|-------|-----------------------------------------|

|       | ing in Extended Microcontroller mode,   |

|       | PORTE defaults to the system bus on     |

|       | Power-on Reset.                         |

### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE | ; Initialize PORTE by<br>; clearing output                     |

|-------|-------|----------------------------------------------------------------|

| CLRF  | LATE  | ; data latches<br>; Alternate method                           |

|       |       | ; to clear output<br>; data latches                            |

| MOVLW | 0x03  | ; Value used to<br>: initialize data                           |

| MOVWF | TRISE | ; direction<br>; Set RE1:RE0 as inputs<br>; RE7:RE2 as outputs |

|       |       |                                                                |

| Name        | Bit#  | Buffer Type | Function                                                                                                 |  |  |  |  |  |

|-------------|-------|-------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RG0/CCP3    | bit 0 | ST          | Input/output port pin or Capture3 input/Compare3 output/PWM3 output.                                     |  |  |  |  |  |

| RG1/TX2/CK2 | bit 1 | ST          | Input/output port pin, addressable USART2 asynchronous transmit or addressable USART2 synchronous clock. |  |  |  |  |  |

| RG2/RX2/DT2 | bit 2 | ST          | Input/output port pin, addressable USART2 asynchronous receive or addressable USART2 synchronous data.   |  |  |  |  |  |

| RG3/CCP4    | bit 3 | ST          | Input/output port pin or Capture4 input/Compare4 output/PWM4 output.                                     |  |  |  |  |  |

| RG4/CCP5    | bit 4 | ST          | Input/output port pin or Capture5 input/Compare5 output/PWM5 output.                                     |  |  |  |  |  |

### TABLE 10-13: PORTG FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 10-14: SUMMARY OF REGISTERS ASSOCIATED WITH PORTG

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3                                     | Bit 2    | Bit 1    | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-------|-------|-------|-----------|-------------------------------------------|----------|----------|-------|----------------------|---------------------------------|

| PORTG | _     | _     |       | Read PC   | RTF pin/\                                 | Write PO | RTF Data | Latch | x xxxx               | u uuuu                          |

| LATG  | —     | _     |       | LATG Da   | LATG Data Output Register                 |          |          |       |                      | u uuuu                          |

| TRISG | _     | _     | _     | Data Dire | Data Direction Control Register for PORTG |          |          |       |                      | 1 1111                          |

**Legend:** x = unknown, u = unchanged

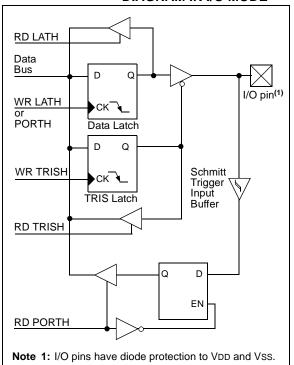

## 10.8 PORTH, LATH and TRISH Registers

| Note: | PORTH is available only on PIC18F8X20 |

|-------|---------------------------------------|

|       | devices.                              |

PORTH is an 8-bit wide, bidirectional I/O port. The corresponding data direction register is TRISH. Setting a TRISH bit (= 1) will make the corresponding PORTH pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISH bit (= 0) will make the corresponding PORTH pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATH register, read and write the latched output value for PORTH.

Pins RH7:RH4 are multiplexed with analog inputs AN15:AN12. Pins RH3:RH0 are multiplexed with the system bus as the external memory interface; they are the high-order address bits, A19:A16. By default, pins RH7:RH4 are enabled as A/D inputs and pins RH3:RH0 are enabled as the system address bus. Register ADCON1 configures RH7:RH4 as I/O or A/D inputs. Register MEMCON configures RH3:RH0 as I/O or system bus pins.

- Note 1: On Power-on Reset, PORTH pins RH7:RH4 default to A/D inputs and read as '0'.

- 2: On Power-on Reset, PORTH pins RH3:RH0 default to system bus signals.

#### EXAMPLE 10-8: INITIALIZING PORTH

| CLRF  | PORTH  | ; Initialize PORTH by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | ; data latches                             |

| CLRF  | LATH   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0Fh    | ;                                          |

| MOVWF | ADCON1 | ;                                          |

| MOVLW | 0CFh   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISH  | ; Set RH3:RH0 as inputs                    |

|       |        | ; RH5:RH4 as outputs                       |

|       |        | ; RH7:RH6 as inputs                        |

| 1     |        |                                            |

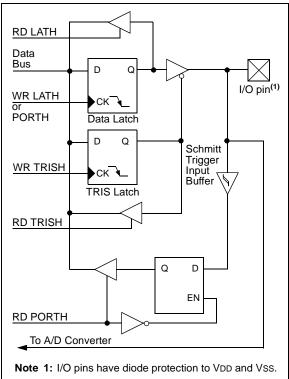

### FIGURE 10-17: RH3:RH0 PINS BLOCK DIAGRAM IN I/O MODE

## FIGURE 10-18: R

#### RH7:RH4 PINS BLOCK DIAGRAM IN I/O MODE

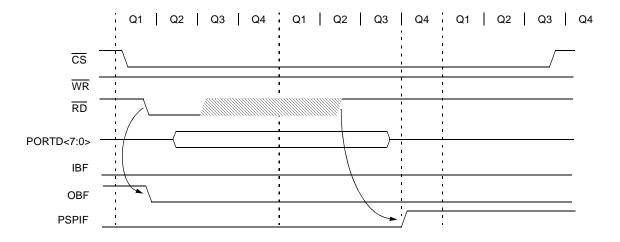

## FIGURE 10-25: PARALLEL SLAVE PORT READ WAVEFORMS

### TABLE 10-19: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Name   | Bit 7                | Bit 6         | Bit 5        | Bit 4          | Bit 3     | Bit 2                 | Bit 1                   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------|---------------|--------------|----------------|-----------|-----------------------|-------------------------|--------|----------------------|---------------------------------|

| PORTD  | Port Data            | Latch whe     | n written; F | Port pins when | read      |                       |                         |        | xxxx xxxx            | uuuu uuuu                       |

| LATD   | LATD Data            | a Output b    |              | xxxx xxxx      | uuuu uuuu |                       |                         |        |                      |                                 |

| TRISD  | PORTD D              | ata Directi   | on bits      |                |           |                       |                         |        | 1111 1111            | 1111 1111                       |

| PORTE  | -                    | —             | -            | —              | —         | Read POR<br>Write POR | RTE pin/<br>RTE Data La | itch   | 0000 0000            | 0000 0000                       |

| LATE   | —                    | —             | _            | _              | —         | LATE Data             | a Output bits           | 3      | xxxx xxxx            | uuuu uuuu                       |

| TRISE  | _                    | _             | _            | _              | —         | PORTE Da              | ata Directio            | n bits | 1111 1111            | 1111 1111                       |

| PSPCON | IBF                  | OBF           | IBOV         | PSPMODE        | —         | —                     | —                       | —      | 0000                 | 0000                            |

| INTCON | GIE/<br>GIEH         | PEIE/<br>GIEL | TMR0IF       | INTOIE         | RBIE      | TMR0IF                | INTOIF                  | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1   | PSPIF <sup>(1)</sup> | ADIF          | RCIF         | TXIF           | SSPIF     | CCP1IF                | TMR2IF                  | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup> | ADIE          | RCIE         | TXIE           | SSPIE     | CCP1IE                | TMR2IE                  | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup> | ADIP          | RCIP         | TXIP           | SSPIP     | CCP1IP                | TMR2IP                  | TMR1IP | 0111 1111            | 0111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port.

**Note 1:** Enabled only in Microcontroller mode for PIC18F8X20 devices.

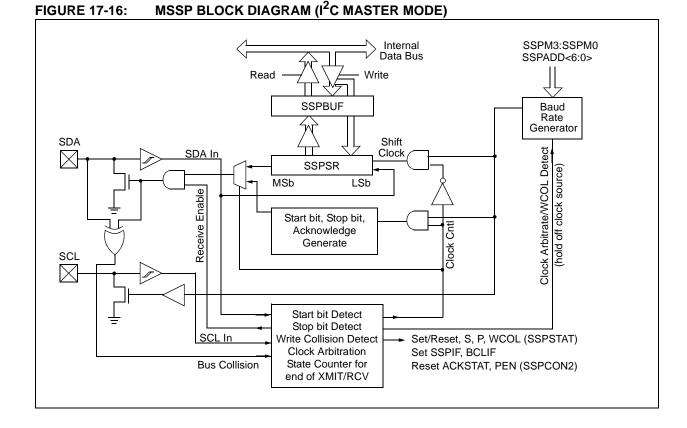

## 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt if enabled):

- Start Condition

- Stop Condition

- Data Transfer Byte Transmitted/received

- Acknowledge Transmit

- Repeated Start

© 2003-2013 Microchip Technology Inc.

## 18.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTAx<4>). In addition, enable bit SPEN (RCSTAx<7>) is set in order to configure the appropriate I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTAx<7>).

### 18.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 18-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREGx register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREGx (if available). Once the TXREGx register transfers the data to the TSR register (occurs in one TCYCLE), the TXREGx is empty and interrupt bit TXxIF (PIR1<4> for USART1, PIR3<4> for USART1, PIE3<4> for USART2). Flag bit TXxIF will be

set, regardless of the state of enable bit TXxIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register. While flag bit TXxIF indicates the status of the TXREGx register, another bit TRMT (TXSTAx<1>) shows the status of the TSR register. TRMT is a read-only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 18.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXxIE in the appropriate PIE register.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREGx register.

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG. The flag bit becomes valid in the second instruction cycle following the load instruction.

| Name                  | Bit 7        | Bit 6         | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|--------------|---------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE     | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                  | PSPIF        | ADIF          | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                  | PSPIE        | ADIE          | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                  | PSPIP        | ADIP          | RCIP       | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR3                  | _            | _             | RC2IF      | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 00 0000              | 00 0000                         |

| PIE3                  | _            | _             | RC2IE      | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 00 0000              | 00 0000                         |

| IPR3                  | _            | _             | RC2IP      | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup> | SPEN         | RX9           | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TXREGx <sup>(1)</sup> | USART Tra    | ansmit Re     | gister     |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup> | CSRC         | TX9           | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> | Baud Rate    | Generato      | r Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| 1                     |              |               |            |        |        |        |        |        |                      |                                 |

### TABLE 18-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

**Note 1:** Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

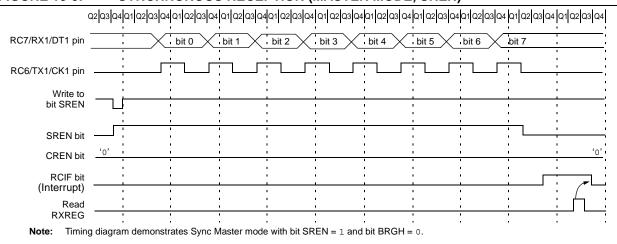

### 18.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTAx<5>) or enable bit CREN (RCSTAx<4>). Data is sampled on the RXx pin (RC7/RX1/DT1 or RG2/RX2/ DT2) on the falling edge of the clock. If enable bit SREN is set, only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGx register for the appropriate baud rate (Section 18.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCxIE in the appropriate PIE register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- 7. Interrupt flag bit RCxIF will be set when reception is complete and an interrupt will be generated if the enable bit RCxIE was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name                  | Bit 7     | Bit 6         | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------|---------------|---------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                | GIE/GIEH  | PEIE/GIEL     | TMR0IE  | INT0IE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                  | PSPIF     | ADIF          | RC1IF   | TX1IF  | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                  | PSPIE     | ADIE          | RC1IE   | TX1IE  | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                  | PSPIP     | ADIP          | RC1IP   | TX1IP  | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR3                  | _         | _             | RC2IF   | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 00 0000              | 00 0000                         |

| PIE3                  | —         | —             | RC2IE   | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 00 0000              | 00 0000                         |

| IPR3                  | _         | _             | RC2IP   | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup> | SPEN      | RX9           | SREN    | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| RCREGx <sup>(1)</sup> | USART Re  | ceive Registe | er      |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup> | CSRC      | TX9           | TXEN    | SYNC   |        | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> | Baud Rate | Generator R   | egister |        | •      |        |        |        | 0000 0000            | 0000 0000                       |

| Lawawala              |           |               |         |        | 01     | II     |        |        |                      |                                 |

### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

**Legend:** x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.**Note 1:**Register names generically refer to both of the identically named registers for the two USART modules, where 'x'

indicates the particular module. Bit names and Reset values are identical between modules.

## FIGURE 18-8: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

## 19.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has 12 inputs for the PIC18F6X20 devices and 16 for the PIC18F8X20 devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 19-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 19-2, configures the functions of the port pins. The ADCON2 register, shown in Register 19-3, configures the A/D clock source and justification.

## REGISTER 19-1: ADCON0 REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |  |

|-------|-----|-------|-------|-------|-------|---------|-------|--|

| _     | _   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |  |

| bit 7 |     |       |       |       |       |         | bit 0 |  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-2 CHS3:CHS0: Analog Channel Select bits

- 0000 = Channel 0 (AN0)

- 0001 = Channel 1 (AN1)

- 0010 = Channel 2 (AN2)

- 0011 = Channel 3 (AN3)

- 0100 = Channel 4 (AN4) 0101 = Channel 5 (AN5)

- 0101 = Channel 6 (AN6)

- 0111 = Channel 7 (AN7)

- 1000 =Channel 8 (AN8)

- 1001 = Channel 9 (AN9)

- 1010 = Channel 10 (AN10)

- 1011 = Channel 11 (AN11)

- 1100 = Channel 12 (AN12)<sup>(1)</sup>

- 1101 =Channel 13 (AN13)<sup>(1)</sup>

- $1110 = Channel 14 (AN14)^{(1)}$

- $1111 = Channel 15 (AN15)^{(1)}$

Note 1: These channels are not available on the PIC18F6X20 (64-pin) devices.

bit 1 GO/DONE: A/D Conversion Status bit

When ADON = 1:

1 = A/D conversion in progress (setting this bit starts the A/D conversion, which is automatically cleared by hardware when the A/D conversion is complete)

0 = A/D conversion not in progress

bit 0 ADON: A/D On bit

- 1 = A/D converter module is enabled

- 0 = A/D converter module is disabled

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 19-3: | ADCON2                                           | REGISTER                                            | 1                            |              |          |           |                |       |

|----------------|--------------------------------------------------|-----------------------------------------------------|------------------------------|--------------|----------|-----------|----------------|-------|

|                | R/W-0                                            | U-0                                                 | U-0                          | U-0          | U-0      | R/W-0     | R/W-0          | R/W-0 |

|                | ADFM                                             | _                                                   | _                            | _            | _        | ADCS2     | ADCS1          | ADCS0 |

|                | bit 7                                            |                                                     |                              |              |          |           |                | bit 0 |

| bit 7          | <b>ADFM:</b> A/D<br>1 = Right ju<br>0 = Left jus | ustified                                            | mat Select b                 | bit          |          |           |                |       |

| bit 6-3        | Unimplem                                         | ented: Read                                         | <b>d as</b> '0'              |              |          |           |                |       |

| bit 2-0        | ADCS1:AD                                         | DCS0: A/D C                                         | Conversion C                 | Clock Select | bits     |           |                |       |

|                | 100 = Foso<br>101 = Foso<br>110 = Foso           | c/8<br>c/32<br>(clock derive<br>c/4<br>c/16<br>c/64 | ed from an F<br>ed from an F |              |          |           |                |       |

|                | Legend:                                          |                                                     |                              |              |          |           |                |       |

|                | R = Reada                                        | ble bit                                             | W = W                        | ritable bit  | U = Unim | plemented | bit, read as ' | 0'    |

'1' = Bit is set

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ pin and RA2/AN2/VREF- pin.

- n = Value at POR

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion is aborted. Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference), or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared and A/D interrupt flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 19-1.

x = Bit is unknown

'0' = Bit is cleared

## 23.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The  $\overline{TO}$  bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT.

The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

## 23.2.1 CONTROL REGISTER

Register 23-15 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

## **REGISTER 23-15: WDTCON REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| _     | —   | —   | —   | —   | —   | —   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

### bit 7-1 Unimplemented: Read as '0'

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

1 = Watchdog Timer is on

0 = Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = 0

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| RLN         | CF                    | Rotate Lo                                                                                                           | eft f (no d                                                                                        | carry)                                                                                     |                                                                        |

|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Synt        | ax:                   | [ label ]                                                                                                           | RLNCF                                                                                              | f [,d [,a                                                                                  | a]                                                                     |

| Ope         | rands:                | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                | 5                                                                                                  |                                                                                            |                                                                        |

| Ope         | ration:               | $(f) \rightarrow$<br>$(f<7>) \rightarrow$                                                                           |                                                                                                    | 1>,                                                                                        |                                                                        |

| Statu       | us Affected:          | N, Z                                                                                                                |                                                                                                    |                                                                                            |                                                                        |

| Enco        | oding:                | 0100                                                                                                                | 01da                                                                                               | ffff                                                                                       | ffff                                                                   |

|             | cription:             | The conte<br>rotated or<br>the result<br>the result<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will<br>BSR valu | he bit to the<br>is placed<br>is stored<br>t). If 'a' is<br>be select<br>value. If 'a<br>be select | he left. If<br>I in W. If<br>I back in<br>'0', the<br>ted, over<br>a' is '1',<br>'ed as pe | 'd' is '0',<br>'d' is '1',<br>register<br>Access<br>riding<br>then the |

|             |                       | -                                                                                                                   | regis                                                                                              | ster f                                                                                     | ┫                                                                      |

| Wor         | ds:                   | 1                                                                                                                   |                                                                                                    |                                                                                            |                                                                        |

| Cycl        | es:                   | 1                                                                                                                   |                                                                                                    |                                                                                            |                                                                        |

| QC          | cycle Activity:       |                                                                                                                     |                                                                                                    |                                                                                            |                                                                        |

|             | Q1                    | Q2                                                                                                                  | Q3                                                                                                 |                                                                                            | Q4                                                                     |

|             | Decode                | Read<br>register 'f'                                                                                                | Process<br>Data                                                                                    |                                                                                            | rite to<br>ination                                                     |

| <u>Exar</u> | <u>nple</u> :         | RLNCF                                                                                                               | REG,                                                                                               | 1, 0                                                                                       |                                                                        |

|             | Before Instru<br>REG  | iction<br>= 1010 1                                                                                                  | 011                                                                                                |                                                                                            |                                                                        |

|             | After Instruct<br>REG | tion<br>= 0101 0                                                                                                    | 111                                                                                                |                                                                                            |                                                                        |

| RRCF              | Rotate Right f through Carry                                                                       |                                                                                                         |                                                       |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Syntax:           | [label]                                                                                            | RRCF f[,d                                                                                               | l [,a]                                                |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                | 5                                                                                                       |                                                       |  |  |  |

| Operation:        | $(f < n >) \rightarrow c$<br>$(f < 0 >) \rightarrow c$<br>$(C) \rightarrow des$                    | С,                                                                                                      |                                                       |  |  |  |

| Status Affected:  | C, N, Z                                                                                            |                                                                                                         |                                                       |  |  |  |

| Encoding:         | 0011                                                                                               | 00da ff                                                                                                 | ff ffff                                               |  |  |  |

|                   | is placed i<br>is placed b<br>(default). I<br>Bank will b<br>the BSR v<br>bank will b<br>BSR value | n W. If 'd' is<br>back in regis<br>f 'a' is '0', th<br>be selected,<br>alue. If 'a' is<br>be selected a | e Access<br>overriding<br>'1', then the<br>as per the |  |  |  |

| Words:            | 1                                                                                                  |                                                                                                         |                                                       |  |  |  |

| Cycles:           | 1                                                                                                  |                                                                                                         |                                                       |  |  |  |

| Q Cycle Activity: |                                                                                                    |                                                                                                         |                                                       |  |  |  |

| Q1                | Q2                                                                                                 | Q3                                                                                                      | Q4                                                    |  |  |  |

| Decode            | Read<br>register 'f'                                                                               | Process<br>Data                                                                                         | Write to destination                                  |  |  |  |

| Example:          | RRCF                                                                                               | REG, 0,                                                                                                 | 0                                                     |  |  |  |

| Refore Instru     | uction                                                                                             |                                                                                                         |                                                       |  |  |  |

| Before Instru | uction | 1    |      |  |

|---------------|--------|------|------|--|

| REG           | =      | 1110 | 0110 |  |

| С             | =      | 0    |      |  |

| After Instruc | tion   |      |      |  |

| REG           | =      | 1110 | 0110 |  |

| W             | =      | 0111 | 0011 |  |

| С             | =      | 0    |      |  |

|               |        |      |      |  |

| SUBWFB                                      | Subtract                                                                                     | W from f with                                                                                                                                                                                    | n Borrow                                                                                           |

|---------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Syntax:                                     | [ label ]                                                                                    | SUBWFB f[,                                                                                                                                                                                       | d [,a]                                                                                             |

| Operands:                                   | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                         | 5                                                                                                                                                                                                |                                                                                                    |

| Operation:                                  | (f) – (W) ·                                                                                  | $-(\overline{C}) \rightarrow dest$                                                                                                                                                               |                                                                                                    |

| Status Affected:                            | N, OV, C                                                                                     | , DC, Z                                                                                                                                                                                          |                                                                                                    |

| Encoding:                                   | 0101                                                                                         | 10da fff                                                                                                                                                                                         | f ffff                                                                                             |

| Description:                                | (borrow) f<br>plement r<br>result is s<br>result is s<br>(default).<br>Bank will<br>BSR valu | W and the Car<br>from register 'f'<br>nethod). If 'd' is<br>tored in W. If 'd<br>tored back in r<br>If 'a' is '0', the<br>be selected, ov<br>e. If 'a' is '1', th<br>lected as per th<br>fault). | (2's com-<br>s '0', the<br>d' is '1', the<br>egister 'f'<br>Access<br>verriding the<br>en the bank |

| Words:                                      | 1                                                                                            |                                                                                                                                                                                                  |                                                                                                    |

| Cycles:                                     | 1                                                                                            |                                                                                                                                                                                                  |                                                                                                    |

| Q Cycle Activity:                           |                                                                                              |                                                                                                                                                                                                  |                                                                                                    |

| Q1                                          | Q2                                                                                           | Q3                                                                                                                                                                                               | Q4                                                                                                 |

| Decode                                      | Read<br>register 'f'                                                                         | Process<br>Data                                                                                                                                                                                  | Write to destination                                                                               |

| Example 1:                                  | SUBWFB                                                                                       | REG, 1, 0                                                                                                                                                                                        |                                                                                                    |

| Before Instru<br>REG<br>C<br>After Instruct | = 0x19<br>= 0x0D<br>= 1<br>tion                                                              | (0001 100<br>(0000 110                                                                                                                                                                           | )))                                                                                                |

| REG<br>W<br>C<br>Z                          | = 0x0C<br>= 0x0D<br>= 1<br>= 0                                                               | (0000 101<br>(0000 110                                                                                                                                                                           |                                                                                                    |

| Z<br>N                                      | = 0                                                                                          | ; result is po                                                                                                                                                                                   | ositive                                                                                            |

| Example 2:                                  | SUBWFB                                                                                       | REG, 0, 0                                                                                                                                                                                        |                                                                                                    |

| Before Instru<br>REG<br>W<br>C              | = 0x1B<br>= 0x1A<br>= 0                                                                      | (0001 101<br>(0001 101                                                                                                                                                                           |                                                                                                    |

| After Instruct<br>REG<br>W<br>C             | tion<br>= 0x1B<br>= 0x00<br>= 1                                                              | (0001 101                                                                                                                                                                                        | 1)                                                                                                 |

| C<br>Z<br>N                                 | = 1<br>= 0                                                                                   | ; result is ze                                                                                                                                                                                   | ro                                                                                                 |

| Example 3:                                  | SUBWFB                                                                                       | REG, 1, 0                                                                                                                                                                                        |                                                                                                    |

| Before Instru<br>REG<br>W<br>C              | uction<br>= 0x03<br>= 0x0E<br>= 1                                                            | (0000 001<br>(0000 110                                                                                                                                                                           |                                                                                                    |

| After Instruct                              |                                                                                              | (                                                                                                                                                                                                |                                                                                                    |

| REG<br>W<br>C                               | = 0xF5<br>= 0x0E<br>= 0                                                                      | (1111 010<br>; <b>[2's comp]</b><br>(0000 110                                                                                                                                                    |                                                                                                    |

| Z<br>N                                      | = 0<br>= 0<br>= 1                                                                            | ; result is ne                                                                                                                                                                                   | egative                                                                                            |

| SWAPF                                            | Swap f                                                                                   |                                                                                          |                                                                                                |

|--------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Syntax:                                          | [label] S                                                                                | SWAPF f[,d                                                                               | l [,a]                                                                                         |

| Operands:                                        | $0 \le f \le 255$                                                                        | 5                                                                                        |                                                                                                |

|                                                  | d ∈ [0,1]<br>a ∈ [0,1]                                                                   |                                                                                          |                                                                                                |

| Operation:                                       |                                                                                          | • dest<7:4>,<br>• dest<3:0>                                                              |                                                                                                |

| Status Affected:                                 | None                                                                                     |                                                                                          |                                                                                                |

| Encoding:                                        | 0011                                                                                     | 10da ffi                                                                                 | ff ffff                                                                                        |

| Description:                                     | register 'f'<br>'0', the res<br>'1', the res<br>(default). I<br>Bank will t<br>the BSR v | ult is placed<br>f 'a' is '0', the<br>pe selected, o<br>alue. If 'a' is<br>pe selected a | ed. If 'd' is<br>in W. If 'd' is<br>in register 'f'<br>e Access<br>overriding<br>'1', then the |

| Words:                                           | 1                                                                                        |                                                                                          |                                                                                                |

| Cycles:                                          | 1                                                                                        |                                                                                          |                                                                                                |

| O Ousla Astivit                                  |                                                                                          |                                                                                          |                                                                                                |

| Q Cycle Activity:                                |                                                                                          |                                                                                          |                                                                                                |

| Q Cycle Activity:<br>Q1                          | Q2                                                                                       | Q3                                                                                       | Q4                                                                                             |

|                                                  |                                                                                          | Q3<br>Process<br>Data                                                                    | Q4<br>Write to<br>destination                                                                  |

| Q1<br>Decode<br>Example:<br>Before Instru<br>REG | Q2<br>Read<br>register 'f'<br>SWAPF R<br>Inction<br>= 0x53                               | Process                                                                                  | Write to                                                                                       |