Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

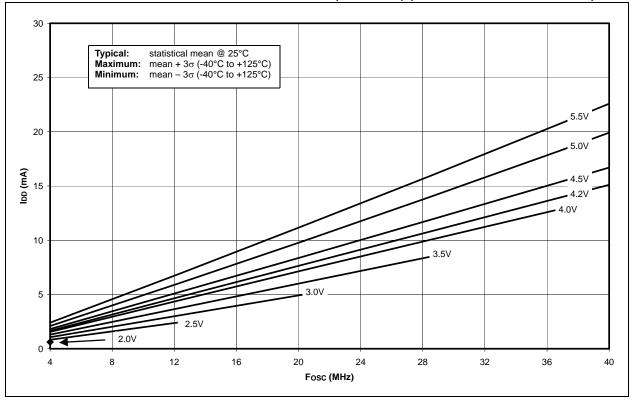

| Speed                      | 40MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 52                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

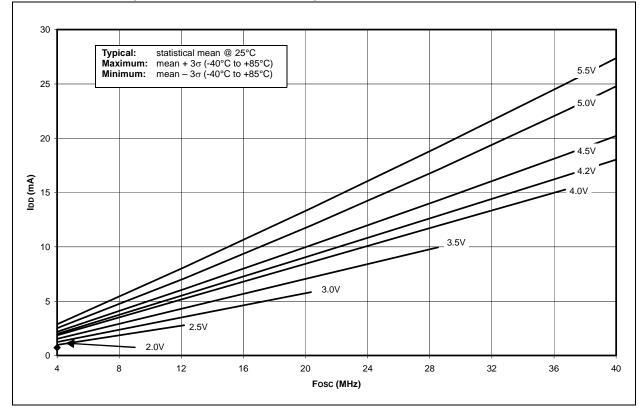

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | A/D 12x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-TQFP                                                                      |

| Supplier Device Package    | 64-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6520t-i-ptg |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

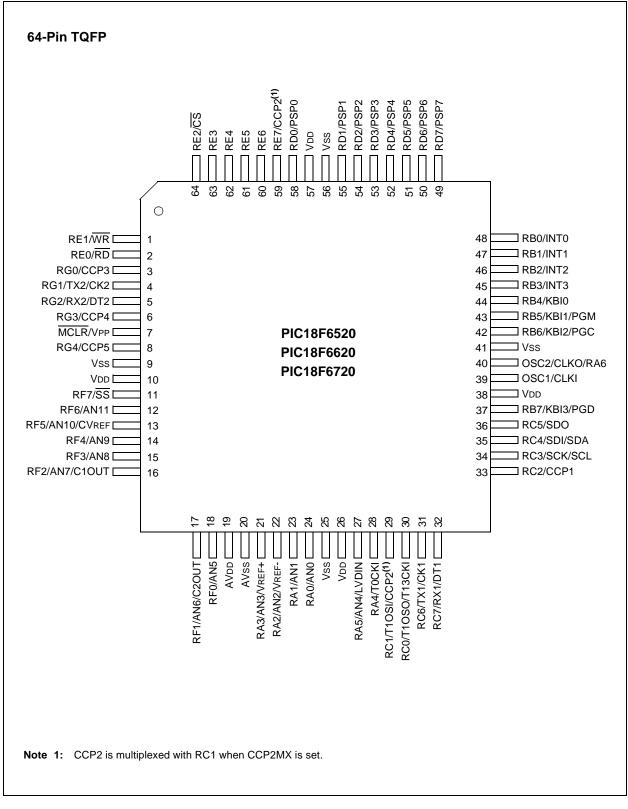

### **Pin Diagrams**

| Pin Name      | Pin N             | umber        | Pin     | Buffer | Description                         |  |  |

|---------------|-------------------|--------------|---------|--------|-------------------------------------|--|--|

| Pin Name      | PIC18F6X20        | PIC18F8X20   | Туре    | Туре   | Description                         |  |  |

|               |                   |              |         |        | PORTA is a bidirectional I/O port.  |  |  |

| RA0/AN0       | 24                | 30           |         |        |                                     |  |  |

| RA0           |                   |              | I/O     | TTL    | Digital I/O.                        |  |  |

| AN0           |                   |              | I       | Analog | Analog input 0.                     |  |  |

| RA1/AN1       | 23                | 29           |         |        |                                     |  |  |

| RA1           |                   |              | I/O     | TTL    | Digital I/O.                        |  |  |

| AN1           |                   |              | I       | Analog | Analog input 1.                     |  |  |

| RA2/AN2/VREF- | 22                | 28           |         | -      | -                                   |  |  |

| RA2           |                   |              | I/O     | TTL    | Digital I/O.                        |  |  |

| AN2           |                   |              | I       | Analog | Analog input 2.                     |  |  |

| Vref-         |                   |              | I       | Analog | A/D reference voltage (Low) input.  |  |  |

| RA3/AN3/VREF+ | 21                | 27           |         | Ū      |                                     |  |  |

| RA3           |                   |              | I/O     | TTL    | Digital I/O.                        |  |  |

| AN3           |                   |              | ., C    | Analog | Analog input 3.                     |  |  |

| VREF+         |                   |              | I       | Analog | A/D reference voltage (High) input. |  |  |

| RA4/T0CKI     | 28                | 34           |         | Ū      |                                     |  |  |

| RA4           | 20                | 01           | I/O     | ST/OD  | Digital I/O – Open-drain when       |  |  |

|               |                   |              | ., C    | 0.702  | configured as output.               |  |  |

| TOCKI         |                   |              | 1       | ST     | Timer0 external clock input.        |  |  |

| RA5/AN4/LVDIN | 27                | 33           |         |        |                                     |  |  |

| RA5           | 21                | 00           | I/O     | TTL    | Digital I/O.                        |  |  |

| AN4           |                   |              |         | Analog | Analog input 4.                     |  |  |

| LVDIN         |                   |              | i       | Analog | Low-Voltage Detect input.           |  |  |

| RA6           |                   |              |         |        | See the OSC2/CLKO/RA6 pin.          |  |  |

| -             | compatible inp    | l            |         | CMOS - | CMOS compatible input or output     |  |  |

|               | nitt Trigger inpu |              | evels   |        | Analog input                        |  |  |

| I = Inpu      |                   |              |         | •      |                                     |  |  |

| P = Pow       |                   |              |         | -      | Open-Drain (no P diode to VDD)      |  |  |

|               | •••               | CP2 when CCF | P2MX is |        | ed (all operating modes except      |  |  |

| Microcontro   | -                 |              | 2101/13 |        | a (an operating modes except        |  |  |

## TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

**6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

## 4.14 RCON Register

The Reset Control (RCON) register contains flag bits that allow differentiation between the sources of a device Reset. These flags include the TO, PD, POR, BOR and RI bits. This register is readable and writable.

- Note 1: If the BOREN configuration bit is set (Brown-out Reset enabled), the BOR bit is '1' on a Power-on Reset. After a Brownout Reset has occurred, the BOR bit will be cleared and must be set by firmware to indicate the occurrence of the next Brown-out Reset.

- 2: It is recommended that the POR bit be set after a Power-on Reset has been detected, so that subsequent Power-on Resets may be detected.

## REGISTER 4-4: RCON REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| IPEN  | _   | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |     |     |       |       |       |       | bit 0 |

bit 7 IPEN: Interrupt Priority Enable bit

- 1 = Enable priority levels on interrupts

- 0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)

## bit 6-5 Unimplemented: Read as '0'

- bit 4 RI: RESET Instruction Flag bit

- 1 = The RESET instruction was not executed

- 0 = The RESET instruction was executed causing a device Reset (must be set in software after a Brown-out Reset occurs)

- bit 3 **TO:** Watchdog Time-out Flag bit

- 1 = After power-up, CLRWDT instruction, or SLEEP instruction

- 0 = A WDT time-out occurred

- bit 2 PD: Power-down Detection Flag bit

- 1 = After power-up or by the CLRWDT instruction

- 0 = By execution of the SLEEP instruction

- bit 1 **POR:** Power-on Reset Status bit

- 1 = A Power-on Reset has not occurred

- 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

- bit 0 BOR: Brown-out Reset Status bit

- 1 = A Brown-out Reset has not occurred

- 0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 5.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch is used to hold 8-bit data during data transfers between program memory and data RAM.

### 5.2.3 TBLPTR – TABLE POINTER REGISTER

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the Device ID, the User ID and the configuration bits.

The Table Pointer, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways, based on the table operation. These operations are shown in Table 5-1. These operations on the TBLPTR only affect the low-order 21 bits.

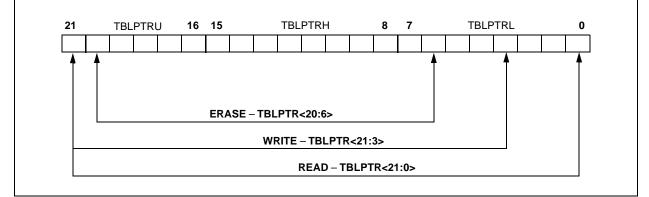

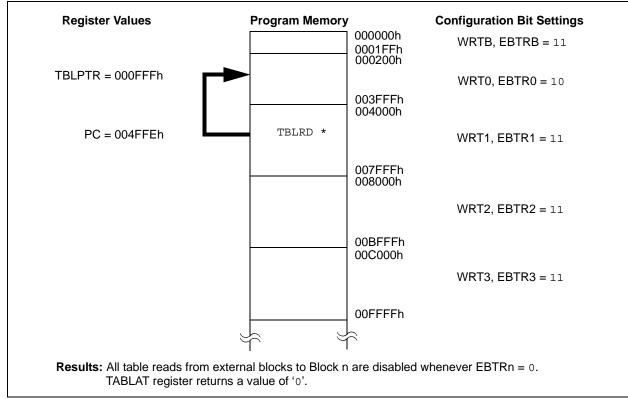

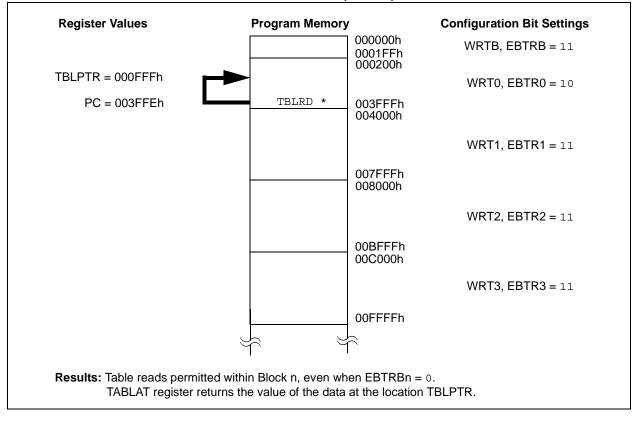

## 5.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer, TBLPTR (TBLPTR<21:3>), will determine which program memory block of 8 bytes is written to. For more detail, see Section 5.5 "Writing to Flash Program Memory".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

Figure 5-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| Example            | Operation on Table Pointer                  |

|--------------------|---------------------------------------------|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |

### FIGURE 5-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

NOTES:

NOTES:

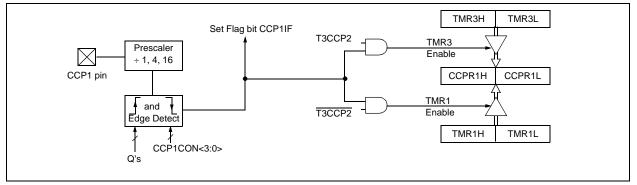

## 16.2 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

### 16.2.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-                |

|-------|---------------------------------------------------------|

|       | put, a write to the port can cause a capture condition. |

### 16.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode, or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 16.1.1 "CCP Modules and Timer Resources").

## 16.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

### 16.2.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON, F  | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP1CON     | ; | Load CCP1CON with   |

|       |             | ; | this value          |

### FIGURE 16-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

| IER 17-2: |                                                                                                                                                                                                                                                                                                                                                                                                 | . 11001 0                                                                                                                                                                                                               |                            | EGISTER'                                      |                 | JL)          |               |             |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------|-----------------|--------------|---------------|-------------|--|--|--|

|           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                   | R/W-0                      | R/W-0                                         | R/W-0           | R/W-0        | R/W-0         | R/W-0       |  |  |  |

|           | WCOL                                                                                                                                                                                                                                                                                                                                                                                            | SSPOV                                                                                                                                                                                                                   | SSPEN                      | СКР                                           | SSPM3           | SSPM2        | SSPM1         | SSPM0       |  |  |  |

|           | bit 7                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                         |                            |                                               |                 |              |               | bit 0       |  |  |  |

| bit 7     | WCOL: Wr                                                                                                                                                                                                                                                                                                                                                                                        | ite Collision                                                                                                                                                                                                           | Detect bit (1              | ransmit mod                                   | de only)        |              |               |             |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                 | be cleared in                                                                                                                                                                                                           |                            | n while it is s                               | till transmitti | ing the prev | ious word     |             |  |  |  |

| bit 6     | SSPOV: Re                                                                                                                                                                                                                                                                                                                                                                                       | eceive Overl                                                                                                                                                                                                            | flow Indicato              | or bit                                        |                 |              |               |             |  |  |  |

|           | <u>SPI Slave r</u>                                                                                                                                                                                                                                                                                                                                                                              | <u>node:</u>                                                                                                                                                                                                            |                            |                                               |                 |              |               |             |  |  |  |

|           | of over<br>must re                                                                                                                                                                                                                                                                                                                                                                              | flow, the da<br>ead the SSF<br>be cleared ir                                                                                                                                                                            | ta in SSPSF<br>BUF, even i | e SSPBUF r<br>R is lost. Ove<br>f only transn | erflow can o    | nly occur in | Slave mod     | e. The user |  |  |  |

|           | Note:                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                         |                            | overflow bit<br>d by writing t                |                 |              |               | eption (and |  |  |  |

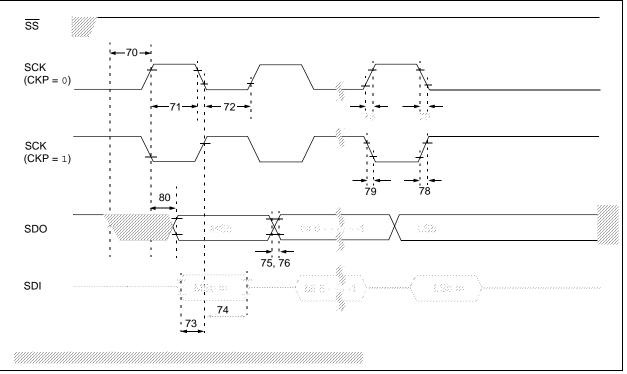

| bit 5     | 1 = Enable                                                                                                                                                                                                                                                                                                                                                                                      | <b>SSPEN:</b> Synchronous Serial Port Enable bit<br>1 = Enables serial port and configures SCK, SDO, SDI and $\overline{SS}$ as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins |                            |                                               |                 |              |               |             |  |  |  |

|           | <b>Note:</b> When enabled, these pins must be properly configured as input or output.                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                         |                            |                                               |                 |              |               |             |  |  |  |

| bit 4     | CKP: Clock                                                                                                                                                                                                                                                                                                                                                                                      | CKP: Clock Polarity Select bit                                                                                                                                                                                          |                            |                                               |                 |              |               |             |  |  |  |

|           | <ul> <li>1 = Idle state for clock is a high level</li> <li>0 = Idle state for clock is a low level</li> </ul>                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                         |                            |                                               |                 |              |               |             |  |  |  |

| bit 3-0   | SSPM3:SS                                                                                                                                                                                                                                                                                                                                                                                        | PM0: Synch                                                                                                                                                                                                              | nronous Seri               | ial Port Mode                                 | e Select bits   |              |               |             |  |  |  |

|           | <ul> <li>0101 = SPI Slave mode, clock = SCK pin, SS pin control disabled, SS can be used as I/O pin</li> <li>0100 = SPI Slave mode, clock = SCK pin, SS pin control enabled</li> <li>0011 = SPI Master mode, clock = TMR2 output/2</li> <li>0010 = SPI Master mode, clock = Fosc/64</li> <li>0001 = SPI Master mode, clock = Fosc/16</li> <li>0000 = SPI Master mode, clock = Fosc/4</li> </ul> |                                                                                                                                                                                                                         |                            |                                               |                 |              |               |             |  |  |  |

|           | Note:                                                                                                                                                                                                                                                                                                                                                                                           | Bit combina<br>I <sup>2</sup> C mode o                                                                                                                                                                                  |                            | ecifically list                               | ed here are     | either reser | ved, or impl  | lemented in |  |  |  |

|           | Legend:                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                         |                            |                                               |                 |              |               |             |  |  |  |

|           | R = Readal                                                                                                                                                                                                                                                                                                                                                                                      | ble bit                                                                                                                                                                                                                 | W = Writab                 | le bit                                        | U = Unimp       | lemented bi  | t, read as '0 | ,           |  |  |  |

|           | - n = Value                                                                                                                                                                                                                                                                                                                                                                                     | at POR                                                                                                                                                                                                                  | '1' = Bit is s             | set                                           | '0' = Bit is o  | cleared      | x = Bit is u  | nknown      |  |  |  |

#### REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER1 (SPI MODE)

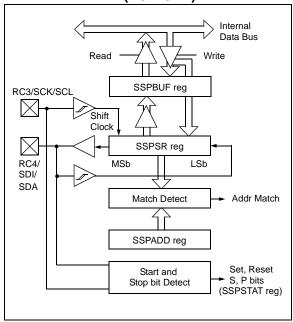

## 17.4 I<sup>2</sup>C Mode

The MSSP module in  $I^2C$  mode fully implements all master and slave functions (including general call support) and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial clock (SCL) RC3/SCK/SCL

- Serial data (SDA) RC4/SDI/SDA

The user must configure these pins as inputs or outputs through the TRISC<4:3> bits.

#### FIGURE 17-7: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

## 17.4.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 2 (SSPCON2)

- MSSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

- MSSP Address Register (SSPADD)

SSPCON, SSPCON2 and SSPSTAT are the control and status registers in  $I^2C$  mode operation. The SSPCON and SSPCON2 registers are readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

SSPADD register holds the slave device address when the SSP is configured in  $I^2C$  Slave mode. When the SSP is configured in Master mode, the lower seven bits of SSPADD act as the Baud Rate Generator reload value.

In receive operations, SSPSR and SSPBUF together, create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not doublebuffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

| TXSTAx:                               | TRANSMIT                                                     | STATUS        | AND CON      | TROL REG    | SISTER     |              |        |

|---------------------------------------|--------------------------------------------------------------|---------------|--------------|-------------|------------|--------------|--------|

| R/W-0                                 | R/W-0                                                        | R/W-0         | R/W-0        | U-0         | R/W-0      | R-1          | R/W-0  |

| CSRC                                  | TX9                                                          | TXEN          | SYNC         | —           | BRGH       | TRMT         | TX9D   |

| bit 7                                 |                                                              |               |              |             |            |              | bit    |

| CSRC: Clo                             | ock Source S                                                 | elect bit     |              |             |            |              |        |

| Asynchron<br>Don't care               |                                                              |               |              |             |            |              |        |

|                                       | <u>us mode:</u><br><sup>.</sup> mode (clock<br>mode (clock f |               |              | om BRG)     |            |              |        |

| <b>TX9</b> : 9-bit                    | Transmit Ena                                                 | ble bit       |              |             |            |              |        |

|                                       | s 9-bit transm<br>s 8-bit transm                             |               |              |             |            |              |        |

| 1 = Transn                            | nsmit Enable<br>nit enabled<br>nit disabled                  | bit           |              |             |            |              |        |

| Note:                                 | SREN/CRE                                                     | N overrides   | TXEN in Sy   | /nc mode.   |            |              |        |

| SYNC: US                              | ART Mode S                                                   | elect bit     |              |             |            |              |        |

|                                       | onous mode                                                   |               |              |             |            |              |        |

| Unimplem                              | ented: Read                                                  | <b>as</b> '0' |              |             |            |              |        |

| BRGH: Hig                             | gh Baud Rate                                                 | e Select bit  |              |             |            |              |        |

| Asynchron<br>1 = High s<br>0 = Low sp | peed                                                         |               |              |             |            |              |        |

| <u>Synchrono</u><br>Unused in         |                                                              |               |              |             |            |              |        |

| TRMT: Tra                             | nsmit Shift R                                                | egister Stat  | us bit       |             |            |              |        |

| 1 = TSR e<br>0 = TSR fu               |                                                              |               |              |             |            |              |        |

|                                       | bit of Transm<br>dress/data bit                              |               | bit.         |             |            |              |        |

| Legend:                               |                                                              |               |              |             |            |              |        |

| R = Reada                             | ble bit                                                      | W = W         | /ritable bit | U = Unin    | nplemented | bit, read as | '0'    |

| - n = Value                           | at POR                                                       | '1' = B       | it is set    | '0' = Bit i | s cleared  | x = Bit is u | nknown |

## REGISTER 18-1: TXSTAX: TRANSMIT STATUS AND CONTROL REGISTER

NOTES:

## FIGURE 23-6: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED

## FIGURE 23-7: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED

NOTES:

## 24.1 Instruction Set

| ADD         | DLW            | ADD literal to W                           |                          |      |          |  |  |  |  |

|-------------|----------------|--------------------------------------------|--------------------------|------|----------|--|--|--|--|

| Synt        | ax:            | [ <i>label</i> ] A                         | [ <i>label</i> ] ADDLW k |      |          |  |  |  |  |

| Ope         | rands:         | $0 \le k \le 25$                           | $0 \le k \le 255$        |      |          |  |  |  |  |

| Ope         | ration:        | (W) + k $\rightarrow$                      |                          |      |          |  |  |  |  |

| Statu       | us Affected:   | N, OV, C,                                  | DC, Z                    |      |          |  |  |  |  |

| Enco        | oding:         | 0000                                       | 1111                     | kkkk | kkkk     |  |  |  |  |

| Desc        | cription:      | The conter<br>8-bit literal<br>placed in \ | 'k' and t                |      |          |  |  |  |  |

| Wor         | ds:            | 1                                          |                          |      |          |  |  |  |  |

| Cycl        | es:            | 1                                          | 1                        |      |          |  |  |  |  |

| QC          | ycle Activity: |                                            |                          |      |          |  |  |  |  |

|             | Q1             | Q2                                         | Q3                       |      | Q4       |  |  |  |  |

|             | Decode         | Read<br>literal 'k'                        | Proces<br>Data           | s Wr | ite to W |  |  |  |  |

| <u>Exar</u> | <u>mple</u> :  | ADDLW 0                                    | x15                      |      |          |  |  |  |  |

|             | Before Instru  | iction                                     |                          |      |          |  |  |  |  |

|             | W =            | 0x10                                       |                          |      |          |  |  |  |  |

|             | After Instruct | tion                                       |                          |      |          |  |  |  |  |

|             | W =            | 0x25                                       |                          |      |          |  |  |  |  |

| ADDWF            | ADD W to                                              | o f                                                                                                                                                                                                                                  |      |   |                       |  |  |  |

|------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|-----------------------|--|--|--|

| Syntax:          | [ label ] A                                           | [ label ] ADDWF f [,d [,a] f [,d                                                                                                                                                                                                     |      |   |                       |  |  |  |

| Operands:        | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$    |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| Operation:       | (W) + (f) -                                           | $\rightarrow$ dest                                                                                                                                                                                                                   |      |   |                       |  |  |  |

| Status Affected: | N, OV, C,                                             | DC, Z                                                                                                                                                                                                                                |      |   |                       |  |  |  |

| Encoding:        | 0010                                                  | 01da                                                                                                                                                                                                                                 | fff  | f | ffff                  |  |  |  |

| Description:     | result is s<br>result is s<br>(default).<br>Bank will | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected. If 'a' is '1',<br>the BSR is used. |      |   |                       |  |  |  |

| Words:           | 1                                                     |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| Cycles:          | 1                                                     |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| Q Cycle Activity | :                                                     |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| Q1               | Q2                                                    | Q3                                                                                                                                                                                                                                   | 3    |   | Q4                    |  |  |  |

| Decode           | Read<br>register 'f'                                  | Proce<br>Data                                                                                                                                                                                                                        |      |   | /rite to<br>stination |  |  |  |

| Example:         | ADDWF                                                 | REG,                                                                                                                                                                                                                                 | 0, 0 |   |                       |  |  |  |

| Before Instru    | uction                                                |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| W<br>REG         | = 0x17<br>= 0xC2                                      |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| After Instruc    | tion                                                  |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

|                  |                                                       |                                                                                                                                                                                                                                      |      |   |                       |  |  |  |

| COMF                       | Complement f                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                    | [ <i>label</i> ] COMF f [,d [,a]                                                                                                                                                                                                                                                                                                             |

| Operands:                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                        |

| Operation:                 | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                            |

| Status Affected:           | N, Z                                                                                                                                                                                                                                                                                                                                         |

| Encoding:                  | 0001 11da ffff ffff                                                                                                                                                                                                                                                                                                                          |

| Description:               | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |

| Words:                     | 1                                                                                                                                                                                                                                                                                                                                            |

| Cycles:                    | 1                                                                                                                                                                                                                                                                                                                                            |

| Q Cycle Activity:          |                                                                                                                                                                                                                                                                                                                                              |

| Q1                         | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                     |

| Decode                     | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                               |

| Example:                   | COMF REG, 0, 0                                                                                                                                                                                                                                                                                                                               |

| Before Instru<br>REG       | uction<br>= 0x13                                                                                                                                                                                                                                                                                                                             |

| After Instruct<br>REG<br>W | tion<br>= 0x13<br>= 0xEC                                                                                                                                                                                                                                                                                                                     |

| CPF                   | SEQ                   | Compare                                                                                                                                | f with W,                                                                                                                                                                                                                                                                                                                                                                                      | skip if | f = W     |  |  |  |  |

|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|--|--|--|--|

| Synt                  | tax:                  | [ label ]                                                                                                                              | CPFSEQ                                                                                                                                                                                                                                                                                                                                                                                         | f [,a]  |           |  |  |  |  |

| Ope                   | rands:                | 0 ≤ f ≤ 25<br>a ∈ [0,1]                                                                                                                | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

| Ope                   | ration:               | (f) – (W),<br>skip if (f) = (W)<br>(unsigned comparison)                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

| Status Affected: None |                       |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

| Enco                  | oding:                | 0110                                                                                                                                   | 0110 001a ffff                                                                                                                                                                                                                                                                                                                                                                                 |         |           |  |  |  |  |

| Des                   | cription:             | memory l<br>of W by p<br>subtraction<br>If 'f' = W,<br>instruction<br>is executed<br>two-cycle<br>Access B<br>overriding<br>then the b | Compares the contents of data<br>memory location 'f' to the contents<br>of W by performing an unsigned<br>subtraction.<br>If 'f' = W, then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is '0', the<br>Access Bank will be selected,<br>overriding the BSR value. If 'a' = 1,<br>then the bank will be selected as |         |           |  |  |  |  |

| Mar                   | do                    | •                                                                                                                                      | SR value (c                                                                                                                                                                                                                                                                                                                                                                                    | ierauit | ).        |  |  |  |  |

| Wor                   |                       | 1                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

| Cycl                  |                       | by                                                                                                                                     | cycles if sk<br>/ a 2-word i                                                                                                                                                                                                                                                                                                                                                                   | -       |           |  |  |  |  |

| QC                    | Cycle Activity:<br>Q1 | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                             |         | Q4        |  |  |  |  |

|                       | Decode                | Read                                                                                                                                   | Process                                                                                                                                                                                                                                                                                                                                                                                        |         | No        |  |  |  |  |

|                       | Dooddo                | register 'f'                                                                                                                           | Data                                                                                                                                                                                                                                                                                                                                                                                           | ор      | eration   |  |  |  |  |

| lf sl                 | kip:                  |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

|                       | Q1                    | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                             |         | Q4        |  |  |  |  |

|                       | No                    | No                                                                                                                                     | No                                                                                                                                                                                                                                                                                                                                                                                             |         | No        |  |  |  |  |

| lf al                 | operation             | operation                                                                                                                              | operation                                                                                                                                                                                                                                                                                                                                                                                      | · · ·   | operation |  |  |  |  |

| II SP                 | kip and follow<br>Q1  | Q2                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                             | n.      | Q4        |  |  |  |  |

|                       | No                    | No                                                                                                                                     | No                                                                                                                                                                                                                                                                                                                                                                                             |         | No<br>No  |  |  |  |  |

|                       | operation             | operation                                                                                                                              | operation                                                                                                                                                                                                                                                                                                                                                                                      | op      | peration  |  |  |  |  |

|                       | No                    | No                                                                                                                                     | No                                                                                                                                                                                                                                                                                                                                                                                             |         | No        |  |  |  |  |

|                       | operation             | operation                                                                                                                              | operation                                                                                                                                                                                                                                                                                                                                                                                      | ор      | peration  |  |  |  |  |

| <u>Exa</u>            | <u>mple</u> :         | HERE<br>NEQUAL<br>EQUAL                                                                                                                | CPFSEQ R<br>:<br>:                                                                                                                                                                                                                                                                                                                                                                             | EG, O   |           |  |  |  |  |

|                       | Before Instru         |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

|                       | PC Addre              |                                                                                                                                        | ERE                                                                                                                                                                                                                                                                                                                                                                                            |         |           |  |  |  |  |

|                       | W<br>REG              | = ?<br>= ?                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

|                       | After Instruct        | -                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                |         |           |  |  |  |  |

|                       | If REG                | = W                                                                                                                                    | :                                                                                                                                                                                                                                                                                                                                                                                              |         |           |  |  |  |  |

|                       | PC                    |                                                                                                                                        | ,<br>ddress (EQU                                                                                                                                                                                                                                                                                                                                                                               | JAL)    |           |  |  |  |  |

|                       | lf REG<br>PC          | ≠ W                                                                                                                                    | ·                                                                                                                                                                                                                                                                                                                                                                                              | \       |           |  |  |  |  |

|                       | FU                    | = A0                                                                                                                                   | ddress (NEG                                                                                                                                                                                                                                                                                                                                                                                    | ĮUAL)   |           |  |  |  |  |

| XORWF Exclusive OR W with f |                                                                                        |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:                     | [label] )                                                                              | KORWF f                                                                                                                                                                                                                                                                                                                                          | [,d [,a]             |  |  |  |  |

| Operands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                    |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Operation:                  | (W) .XOR                                                                               | . (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                         |                      |  |  |  |  |

| Status Affected:            | N, Z                                                                                   |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Encoding:                   | 0001                                                                                   | 10da ff                                                                                                                                                                                                                                                                                                                                          | ff ffff              |  |  |  |  |

| Description:                | with regist<br>is stored in<br>is stored b<br>(default). I<br>Bank will b<br>the BSR v | Exclusive OR the contents of W<br>with register 'f'. If 'd' is '0', the result<br>is stored in W. If 'd' is '1', the result<br>is stored back in register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is '1', then the<br>bank will be selected as per the<br>BSR value. (default) |                      |  |  |  |  |

| Words:                      | 1                                                                                      |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Cycles:                     | 1                                                                                      |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Q Cycle Activity:           |                                                                                        |                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Q1                          | Q2                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                               | Q4                   |  |  |  |  |

| Decode                      | Read<br>register 'f'                                                                   | Process<br>Data                                                                                                                                                                                                                                                                                                                                  | Write to destination |  |  |  |  |