Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 68                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8520t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.6.2 OSCILLATOR TRANSITIONS

PIC18FXX20 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

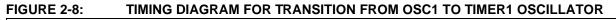

A timing diagram indicating the transition from the main oscillator to the Timer1 oscillator is shown in Figure 2-8. The Timer1 oscillator is assumed to be running all the time. After the SCS bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

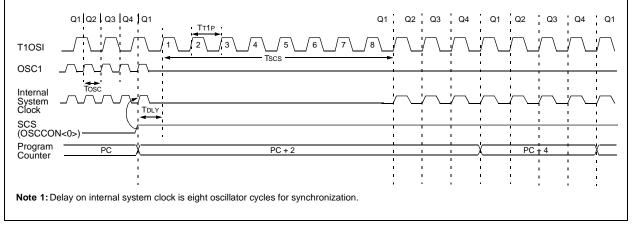

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place. If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes, is shown in Figure 2-9.

### 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The data memory map is in turn divided into 16 banks of 256 bytes each. The lower 4 bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits of the BSR are not implemented.

The data memory space contains both Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (0FFFh) and extend downwards. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

PIC18FX520 devices have 2048 bytes of data RAM, extending from Bank 0 to Bank 7 (000h through 7FFh). PIC18FX620 and PIC18FX720 devices have 3840 bytes of data RAM, extending from Bank 0 to Bank 14 (000h through EFFh). The organization of the data memory space for these devices is shown in Figure 4-6 and Figure 4-7.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the data memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 4.10** "Access Bank" provides a detailed description of the Access RAM.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates using a File Select Register and corresponding Indirect File Operand. The operation of indirect addressing is shown in Section 4.12 "Indirect Addressing, INDF and FSR Registers".

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as General Purpose Registers by all instructions. The top section of Bank 15 (F60h to FFFh) contains SFRs. All other banks of data memory contain GPR registers, starting with Bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2 and Table 4-3.

The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature. The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations are unimplemented and read as '0's. The addresses for the SFRs are listed in Table 4-2.

| REGISTER 5-1: | EECON1 F                                                                                                                                                                                                                                                                                                            | REGISTER                                                                                                                                                                                                                                                                   | (ADDRE          | SS FA6h)                    |                       |              |               |            |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|-----------------------|--------------|---------------|------------|--|--|

|               | R/W-x                                                                                                                                                                                                                                                                                                               | R/W-x                                                                                                                                                                                                                                                                      | U-0             | R/W-0                       | R/W-x                 | R/W-0        | R/S-0         | R/S-0      |  |  |

|               | EEPGD                                                                                                                                                                                                                                                                                                               | CFGS                                                                                                                                                                                                                                                                       | _               | FREE                        | WRERR                 | WREN         | WR            | RD         |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                            |                 |                             |                       |              |               | bit 0      |  |  |

| bit 7         | EEPGD: F                                                                                                                                                                                                                                                                                                            | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                                                                                      |                 |                             |                       |              |               |            |  |  |

|               | 1 = Acces                                                                                                                                                                                                                                                                                                           | 1 = Access Flash program memory                                                                                                                                                                                                                                            |                 |                             |                       |              |               |            |  |  |

| bit 6         |                                                                                                                                                                                                                                                                                                                     | <ul> <li>0 = Access data EEPROM memory</li> <li>CFGS: Flash Program/Data EEPROM or Configuration Select bit</li> </ul>                                                                                                                                                     |                 |                             |                       |              |               |            |  |  |

|               |                                                                                                                                                                                                                                                                                                                     | <ul> <li>1 = Access configuration registers</li> <li>0 = Access Flash program or data EEPROM memory</li> </ul>                                                                                                                                                             |                 |                             |                       |              |               |            |  |  |

| bit 5         | Unimplem                                                                                                                                                                                                                                                                                                            | ented: Read                                                                                                                                                                                                                                                                | <b>d as</b> '0' |                             |                       |              |               |            |  |  |

| bit 4         | FREE: Flas                                                                                                                                                                                                                                                                                                          | sh Row Eras                                                                                                                                                                                                                                                                | se Enable b     | oit                         |                       |              |               |            |  |  |

|               | (cleare                                                                                                                                                                                                                                                                                                             | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul>                                                                                             |                 |                             |                       |              |               |            |  |  |

| bit 3         | WRERR: F                                                                                                                                                                                                                                                                                                            | lash Progra                                                                                                                                                                                                                                                                | m/Data EE       | PROM Error                  | <sup>·</sup> Flag bit |              |               |            |  |  |

|               | <ul> <li>1 = A write operation is prematurely terminated<br/>(any Reset during self-timed programming in normal operation)</li> <li>0 = The write operation completed</li> </ul>                                                                                                                                    |                                                                                                                                                                                                                                                                            |                 |                             |                       |              |               |            |  |  |

|               | Note:                                                                                                                                                                                                                                                                                                               | When a Wi<br>tracing of th                                                                                                                                                                                                                                                 |                 |                             | GD and CFGS           | bits are not | t cleared. T  | his allows |  |  |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                           | ash Program                                                                                                                                                                                                                                                                | /Data EEP       | ROM Write I                 | Enable bit            |              |               |            |  |  |

|               |                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                          | •               | rogram/data<br>program/data |                       |              |               |            |  |  |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                           | Control bit                                                                                                                                                                                                                                                                |                 |                             |                       |              |               |            |  |  |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle. (The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                                                                                                                                                                                                                                                            |                 |                             |                       |              |               |            |  |  |

| bit 0         |                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                                                                                                                                          |                 | bompiete                    |                       |              |               |            |  |  |

| bit 0         | 1 = Initiate<br>can or                                                                                                                                                                                                                                                                                              | <ul> <li>RD: Read Control bit</li> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bic can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)</li> <li>0 = Does not initiate an EEPROM read</li> </ul> |                 |                             |                       |              |               |            |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                            |                 |                             |                       |              |               | ]          |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                           | ble bit                                                                                                                                                                                                                                                                    | W = V           | Vritable bit                | U = Unimp             | lemented b   | it. read as ' | 0'         |  |  |

|               |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                            |                 |                             | -                     |              |               |            |  |  |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

#### EXAMPLE 5-3: WRITING TO FLASH PROGRAM MEMORY

| EXAMPLE 5-3:   | WRI             | TING TO FLASH PROC            |                                                                      |

|----------------|-----------------|-------------------------------|----------------------------------------------------------------------|

|                | MOVLW           | D'64                          | ; number of bytes in erase block                                     |

|                | MOVWF           | COUNTER                       |                                                                      |

|                | MOVLW           | BUFFER_ADDR_HIGH              | ; point to buffer                                                    |

|                | MOVWF<br>MOVLW  | FSR0H<br>BUFFER ADDR LOW      |                                                                      |

|                | MOVWF           | FSROL                         |                                                                      |

|                | MOVLW           | CODE_ADDR_UPPER               | ; Load TBLPTR with the base                                          |

|                | MOVWF           | TBLPTRU                       | ; address of the memory block                                        |

|                | MOVLW           | CODE_ADDR_HIGH                |                                                                      |

|                | MOVWF<br>MOVLW  | TBLPTRH<br>CODE ADDR LOW      |                                                                      |

|                | MOVHW           | CODE_ADDR_LOW<br>TBLPTRL      |                                                                      |

| READ_BLOCK     |                 |                               |                                                                      |

|                | TBLRD*+         | ÷                             | ; read into TABLAT, and inc                                          |

|                | MOVF            | TABLAT, W                     | ; get data                                                           |

|                | MOVWF           | POSTINCO<br>COUNTER           | ; store data<br>; done?                                              |

|                | BRA             | READ BLOCK                    | ; repeat                                                             |

| MODIFY_WORD    |                 |                               |                                                                      |

| _              | MOVLW           | DATA_ADDR_HIGH                | ; point to buffer                                                    |

|                | MOVWF           | FSROH                         |                                                                      |

|                | MOVLW<br>MOVWF  | DATA_ADDR_LOW<br>FSR0L        |                                                                      |

|                | MOVWF<br>MOVLW  | NEW DATA LOW                  | ; update buffer word                                                 |

|                | MOVWF           | POSTINC0                      | , apaaoo barror nora                                                 |

|                | MOVLW           | NEW_DATA_HIGH                 |                                                                      |

|                | MOVWF           | INDF0                         |                                                                      |

| ERASE_BLOCK    | MOLITIN         |                               |                                                                      |

|                | MOVLW<br>MOVWF  | CODE_ADDR_UPPER<br>TBLPTRU    | ; load TBLPTR with the base<br>; address of the memory block         |

|                | MOVLW           | CODE ADDR HIGH                | , address of the memory brock                                        |

|                | MOVWF           | TBLPTRH                       |                                                                      |

|                | MOVLW           | CODE_ADDR_LOW                 |                                                                      |

|                | MOVWF           | TBLPTRL                       |                                                                      |

|                | BSF<br>BCF      | EECON1, EEPGD<br>EECON1, CFGS | ; point to Flash program memory<br>; access Flash program memory     |

|                | BSF             | EECON1, WREN                  | ; enable write to memory                                             |

|                | BSF             | EECON1, FREE                  | ; enable Row Erase operation                                         |

|                | BCF             | INTCON, GIE                   | ; disable interrupts                                                 |

|                | MOVLW           | 55h                           |                                                                      |

| Required       | MOVWF<br>MOVLW  | EECON2<br>AAh                 | ; write 55H                                                          |

| Sequence       | MOVWF           | EECON2                        | ; write AAH                                                          |

| -              | BSF             | EECON1, WR                    | ; start erase (CPU stall)                                            |

|                | NOP             |                               |                                                                      |

|                | BSF<br>TDIDD+   | INTCON, GIE                   | ; re-enable interrupts<br>; dummy read decrement                     |

| WRITE BUFFER B | TBLRD*-<br>BACK | -                             | ; dummy read decrement                                               |

|                | MOVLW           | 8                             | ; number of write buffer groups of 8 bytes                           |

|                | MOVWF           | COUNTER_HI                    |                                                                      |

|                | MOVLW           | BUFFER_ADDR_HIGH              | ; point to buffer                                                    |

|                | MOVWF           | FSROH                         |                                                                      |

|                | MOVLW<br>MOVWF  | BUFFER_ADDR_LOW<br>FSR0L      |                                                                      |

| PROGRAM LOOP   | 110 V W1        | IDROL                         |                                                                      |

|                | MOVLW           | 8                             | ; number of bytes in holding register                                |

|                | MOVWF           | COUNTER                       |                                                                      |

| WRITE_WORD_TO_ | -               |                               |                                                                      |

|                | MOVFF           | POSTINCO, WREG                | ; get low byte of buffer data<br>; present data to table latch       |

|                | TBLWT+*         | •                             | ; present data to table latch<br>; write data, perform a short write |

|                |                 |                               | ; to internal TBLWT holding register.                                |

|                | DECFSZ          | COUNTER                       | ; loop until buffers are full                                        |

|                | BRA             | WRITE_WORD_TO_HREGS           |                                                                      |

| r              |                 |                               |                                                                      |

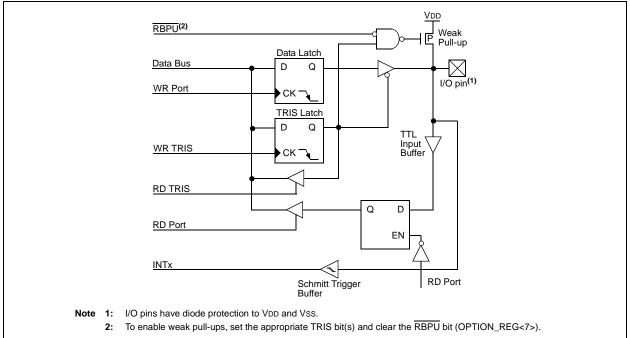

#### FIGURE 10-6: BLOCK DIAGRAM OF RB2:RB0 PINS

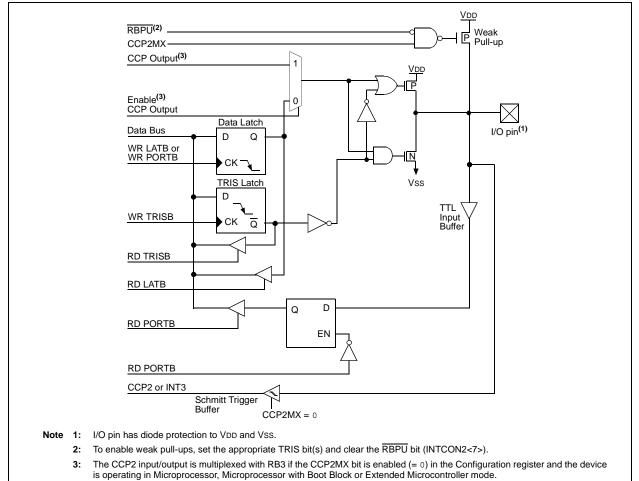

#### FIGURE 10-7: BLOCK DIAGRAM OF RB3 PIN

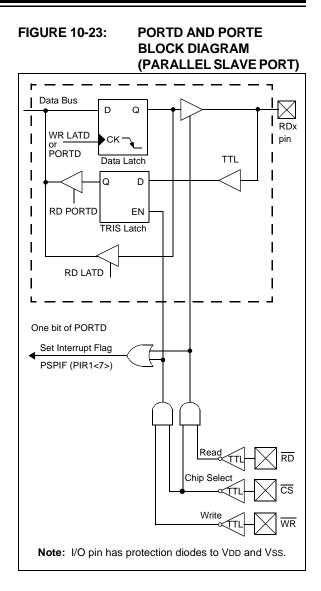

### 10.10 Parallel Slave Port

PORTD also operates as an 8-bit wide Parallel Slave Port, or microprocessor port, when control bit PSPMODE (PSPCON<4>) is set. It is asynchronously readable and writable by the external world through the RD control input pin, RE0/RD/AD8 and the WR control input pin, RE1/WR/AD9.

| Note: | For PIC18F8X20 devices, th | devices, the Paralle |    |  |  |

|-------|----------------------------|----------------------|----|--|--|

|       | Slave Port is available    | only                 | in |  |  |

|       | Microcontroller mode.      |                      |    |  |  |

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AD8 to be the RD input, RE1/WR/AD9 to be the WR input and RE2/ CS/AD10 to be the CS (Chip Select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits, PCFG2:PCFG0 (ADCON1<2:0>), must be set which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (PSPCON<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs) and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

| REGISTER 17-5:                                                                                                                                                                                                                                                                   | SSPCON                                           | 2: MSSP CO                                                                                                                                       | NTROL R                                 | EGISTER 2     | (I <sup>2</sup> C MOD | E)           |              |             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------|-----------------------|--------------|--------------|-------------|--|--|--|

|                                                                                                                                                                                                                                                                                  | R/W-0                                            | R/W-0                                                                                                                                            | R/W-0                                   | R/W-0         | R/W-0                 | R/W-0        | R/W-0        | R/W-0       |  |  |  |

|                                                                                                                                                                                                                                                                                  | GCEN                                             | ACKSTAT                                                                                                                                          | ACKDT                                   | ACKEN         | RCEN                  | PEN          | RSEN         | SEN         |  |  |  |

|                                                                                                                                                                                                                                                                                  | bit 7                                            |                                                                                                                                                  |                                         |               |                       |              |              | bit 0       |  |  |  |

| bit 7                                                                                                                                                                                                                                                                            | GCEN: G                                          | eneral Call En                                                                                                                                   | able bit (Sla                           | ve mode onl   | y)                    |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  | <ul> <li>1 = Enable interrupt when a general call address (0000h) is received in the SSPSR</li> <li>0 = General call address disabled</li> </ul> |                                         |               |                       |              |              |             |  |  |  |

| bit 6                                                                                                                                                                                                                                                                            | ACKSTAT                                          | F: Acknowledg                                                                                                                                    | e Status bit                            | (Master Tran  | smit mode c           | only)        |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  | <ul><li>1 = Acknowledge was not received from slave</li><li>0 = Acknowledge was received from slave</li></ul>                                    |                                         |               |                       |              |              |             |  |  |  |

| bit 5                                                                                                                                                                                                                                                                            | ACKDT: A                                         | Acknowledge [                                                                                                                                    | Data bit (Ma                            | ster Receive  | mode only)            |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  | 1 = Not Acknowledge<br>0 = Acknowledge                                                                                                           |                                         |               |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  | Note:                                            | Value that w the end of a                                                                                                                        |                                         | itted when th | e user initiat        | tes an Ackı  | nowledge s   | equence at  |  |  |  |

| bit 4                                                                                                                                                                                                                                                                            | ACKEN:                                           | Acknowledge                                                                                                                                      | Sequence E                              | nable bit (Ma | aster Receiv          | e mode on    | ly)          |             |  |  |  |

|                                                                                                                                                                                                                                                                                  | Autor                                            | te Acknowledg<br>matically clear<br>owledge seque                                                                                                | ed by hardw                             |               | SCL pins a            | nd transmi   | t ACKDT da   | ata bit.    |  |  |  |

| bit 3                                                                                                                                                                                                                                                                            | RCEN: R                                          | eceive Enable                                                                                                                                    | bit (Master                             | mode only)    |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  | 1 = Enabl<br>0 = Recei                           | es Receive mo<br>ve Idle                                                                                                                         | ode for I <sup>2</sup> C                |               |                       |              |              |             |  |  |  |

| bit 2                                                                                                                                                                                                                                                                            | -                                                | p Condition En                                                                                                                                   |                                         |               |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  | e Stop conditio<br>condition Idle                                                                                                                | on on SDA a                             | ind SCL pins  | . Automatica          | ally cleared | by hardwa    | re.         |  |  |  |

| bit 1                                                                                                                                                                                                                                                                            |                                                  | epeated Start (                                                                                                                                  |                                         | -             |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  | e Repeated St<br>ated Start con                                                                                                                  |                                         | on SDA and    | SCL pins. A           | utomaticall  | y cleared by | hardware.   |  |  |  |

| bit 0                                                                                                                                                                                                                                                                            | SEN: Start Condition Enabled/Stretch Enabled bit |                                                                                                                                                  |                                         |               |                       |              |              |             |  |  |  |

| In Master mode:<br>1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware<br>0 = Start condition Idle<br>In Slave mode:<br>1 = Clock stretching is enabled for both Slave Transmit and Slave Receive (stretch e<br>0 = Clock stretching is disabled |                                                  |                                                                                                                                                  |                                         |               |                       |              |              | re.         |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                  |                                                                                                                                                  |                                         |               |                       |              |              | n enabled)  |  |  |  |

| <b>Note:</b> For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I <sup>2</sup> C module is not in the Idle this bit may not be set (no spooling) and the SSPBUF may not be written (or to the SSPBUF are disabled).                                                                    |                                                  |                                                                                                                                                  |                                         |               |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  | Logondi                                          |                                                                                                                                                  |                                         |               |                       |              |              |             |  |  |  |

|                                                                                                                                                                                                                                                                                  | Legend:                                          | ahla hit                                                                                                                                         | $\lambda \lambda I = \lambda \lambda I$ | ritable hit   | II – Unimr            | lamented     | hit read as  | ' <b>O'</b> |  |  |  |

| Legend:            |                  |                                        |

|--------------------|------------------|----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'     |

| - n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown |

#### 17.4.3.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON1<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 17.4.4** "**Clock Stretching**" for more detail.

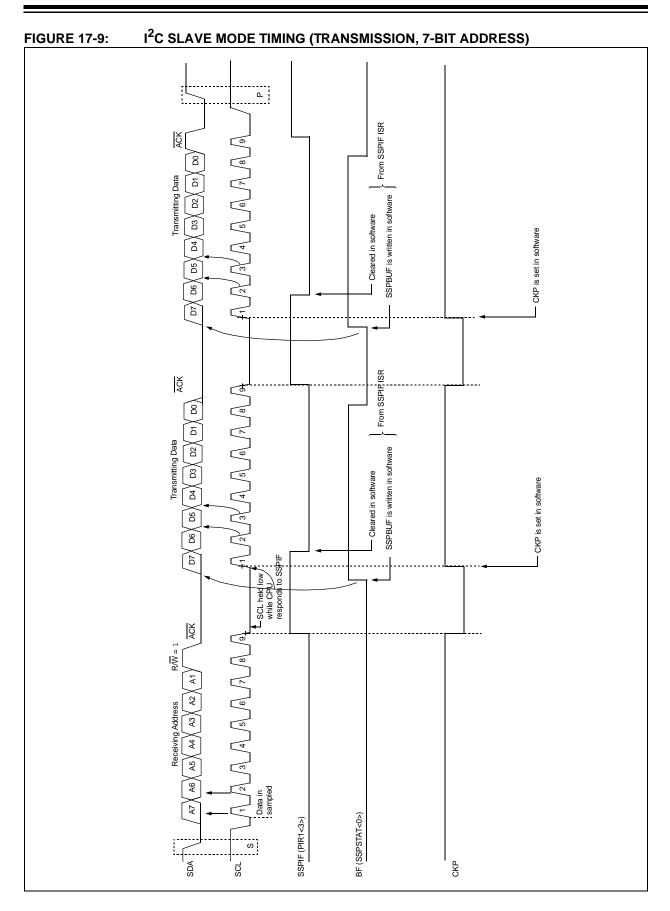

#### 17.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low, regardless of SEN (see Section 17.4.4 "Clock Stretching", for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-9).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

### 17.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 17.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 17-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence, in order to prevent an overflow condition.

#### 17.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence, as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 17.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs, regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 17-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software, regardless of the state of the BF bit.

#### 17.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled as in 7-bit Slave Transmit mode (see Figure 17-11).

### 18.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the TXx pin (RC6/TX1/CK1 or RG1/TX2/CK2), instead of being supplied internally in Master mode. TRISC<6> must be set for this mode. This allows the device to transfer or receive data while in Sleep mode. Slave mode is entered by clearing bit CSRC (TXSTAx<7>).

#### 18.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXxIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit TXxIF will now be set.

- e) If enable bit TXxIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXxIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name                                               | Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------------------------------------|--------------|---------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON                                             | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 0000            | 0000 0000                       |

| PIR1                                               | PSPIF        | ADIF          | RC1IF  | TX1IF  | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1                                               | PSPIE        | ADIE          | RC1IE  | TX1IE  | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1                                               | PSPIP        | ADIP          | RC1IP  | TX1IP  | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 0111 1111            | 0111 1111                       |

| PIR3                                               | _            | _             | RC2IF  | TX2IF  | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 00 0000              | 00 0000                         |

| PIE3                                               | _            |               | RC2IE  | TX2IE  | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 00 0000              | 00 0000                         |

| IPR3                                               | _            | _             | RC2IP  | TX2IP  | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 11 1111              | 11 1111                         |

| RCSTAx <sup>(1)</sup>                              | SPEN         | RX9           | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TXREGx <sup>(1)</sup> USART Transmit Register      |              |               |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTAx <sup>(1)</sup>                              | CSRC         | TX9           | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRGx <sup>(1)</sup> Baud Rate Generator Register |              |               |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

#### TABLE 18-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

| BTG               | Bit Toggle                                   | e f                                |                                                                              | BOV                          | Branch if                                                         | Overflow                                                 |                                                                                 |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

| Syntax:           | [label] B                                    | TG f,b[,a]                         |                                                                              | Syntax:                      | [ <i>label</i> ] B                                                | [ <i>label</i> ] BOV n                                   |                                                                                 |  |  |  |

| Operands:         | $0 \le f \le 255$                            | 5                                  |                                                                              | Operands:                    | -128 ≤ n ≤                                                        | -128 ≤ n ≤ 127                                           |                                                                                 |  |  |  |

|                   | 0 ≤ b < 7<br>a ∈ [0,1]                       |                                    |                                                                              | Operation:                   |                                                                   | if Overflow bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                                                 |  |  |  |

| Operation:        | $(f < b >) \rightarrow f$                    | <b></b>                            |                                                                              | Status Affected:             | None                                                              |                                                          |                                                                                 |  |  |  |

| Status Affected:  | None                                         |                                    |                                                                              | Encoding:                    | 1110                                                              | 0100 nn                                                  | nn nnnn                                                                         |  |  |  |

| Encoding:         | 0111                                         | bbba f                             | fff ffff                                                                     | Description:                 | If the Ove                                                        | rflow bit is '1                                          | ' then the                                                                      |  |  |  |

| Description:      | inverted. If<br>will be sele<br>value. If 'a | f 'a' is '0', the<br>ected, overri | location 'f' is<br>Access Bank<br>ding the BSR<br>le bank will be<br>R value |                              | The 2's co<br>added to t<br>have incre<br>instruction<br>PC+2+2n. | he PC. Sind<br>emented to f<br>, the new ac              | umber '2n' is<br>the PC will<br>etch the next<br>dress will be<br>ction is then |  |  |  |

| Words:            | 1                                            |                                    |                                                                              | Words:                       | 1                                                                 |                                                          | •                                                                               |  |  |  |

| Cycles:           | 1                                            |                                    |                                                                              |                              |                                                                   |                                                          |                                                                                 |  |  |  |

| Q Cycle Activity: |                                              |                                    |                                                                              | Cycles:                      | 1(2)                                                              |                                                          |                                                                                 |  |  |  |

| Q1                | Q2                                           | Q3                                 | Q4                                                                           | Q Cycle Activity<br>If Jump: |                                                                   |                                                          |                                                                                 |  |  |  |

| Decode            | Read<br>register 'f'                         | Process<br>Data                    | Write<br>register 'f'                                                        | Q1                           | Q2                                                                | Q3                                                       | Q4                                                                              |  |  |  |

| Example:          | BTG F                                        | PORTC, 4,                          | 0                                                                            | Decode                       | Read literal<br>'n'                                               | Process<br>Data                                          | Write to PC                                                                     |  |  |  |

| Before Instru     |                                              |                                    |                                                                              | No                           | No                                                                | No                                                       | No                                                                              |  |  |  |

| PORTC             |                                              | 101 <b>[0x75]</b>                  |                                                                              | operation                    | operation                                                         | operation                                                | operation                                                                       |  |  |  |

| After Instruct    | ion:                                         |                                    |                                                                              | If No Jump:<br>Q1            | Q2                                                                | Q3                                                       | Q4                                                                              |  |  |  |

| PORTC             | = 0110 0                                     | 101 <b>[0x65]</b>                  |                                                                              | Decode                       | Read literal                                                      | Process                                                  | No                                                                              |  |  |  |

|                   |                                              |                                    |                                                                              | Decode                       | 'n'                                                               | Data                                                     | operation                                                                       |  |  |  |

|                   |                                              |                                    |                                                                              | Example:                     | HERE                                                              | BOV Jump                                                 | )                                                                               |  |  |  |

|                   |                                              |                                    |                                                                              | Before Instru                | uction                                                            |                                                          |                                                                                 |  |  |  |

PC

After Instruction

If Overflow = PC = If Overflow = PC =

=

1;

address (HERE)

address (Jump) 0; address (HERE+2)

| © 2003-2013 Microchip | Technology Inc. |

|-----------------------|-----------------|

|-----------------------|-----------------|

| COMF                       | Complement f                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                    | [ <i>label</i> ] COMF f [,d [,a]                                                                                                                                                                                                                                                                                                             |

| Operands:                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                        |

| Operation:                 | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                            |

| Status Affected:           | N, Z                                                                                                                                                                                                                                                                                                                                         |

| Encoding:                  | 0001 11da ffff ffff                                                                                                                                                                                                                                                                                                                          |

| Description:               | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |

| Words:                     | 1                                                                                                                                                                                                                                                                                                                                            |

| Cycles:                    | 1                                                                                                                                                                                                                                                                                                                                            |

| Q Cycle Activity:          |                                                                                                                                                                                                                                                                                                                                              |

| Q1                         | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                     |

| Decode                     | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                               |

| Example:                   | COMF REG, 0, 0                                                                                                                                                                                                                                                                                                                               |

| Before Instru<br>REG       | uction<br>= 0x13                                                                                                                                                                                                                                                                                                                             |

| After Instruct<br>REG<br>W | tion<br>= 0x13<br>= 0xEC                                                                                                                                                                                                                                                                                                                     |