Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.75K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

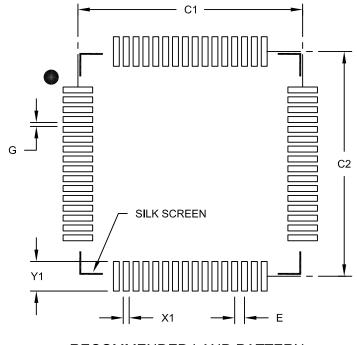

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8620-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Din Nome                                      | Pin Nu         | umber           | Pin   | Buffer   | Description                                                                          |  |  |  |  |  |  |

|-----------------------------------------------|----------------|-----------------|-------|----------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name                                      | PIC18F6X20     | PIC18F8X20      | Туре  | Туре     | Description                                                                          |  |  |  |  |  |  |

|                                               |                |                 |       |          | PORTE is a bidirectional I/O port.                                                   |  |  |  |  |  |  |

| RE0/RD/AD8                                    | 2              | 4               |       |          |                                                                                      |  |  |  |  |  |  |

| RE0                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| RD                                            |                |                 | I     | TTL      | Read control for Parallel Slave Port (see $\overline{WR}$ and $\overline{CS}$ pins). |  |  |  |  |  |  |

| AD8 <sup>(3)</sup>                            |                |                 | I/O   | TTL      | External memory address/data 8.                                                      |  |  |  |  |  |  |

| RE1/WR/AD9                                    | 1              | 3               |       |          |                                                                                      |  |  |  |  |  |  |

| RE1                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| WR                                            |                |                 | I     | TTL      | Write control for Parallel Slave Port                                                |  |  |  |  |  |  |

| (2)                                           |                |                 |       |          | (see $\overline{CS}$ and $\overline{RD}$ pins).                                      |  |  |  |  |  |  |

| AD9 <sup>(3)</sup>                            |                |                 | I/O   | TTL      | External memory address/data 9.                                                      |  |  |  |  |  |  |

| RE2/CS/AD10                                   | 64             | 78              |       |          |                                                                                      |  |  |  |  |  |  |

| RE2                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| CS                                            |                |                 | I     | TTL      | Chip select control for Parallel Slave                                               |  |  |  |  |  |  |

| (2)                                           |                |                 |       |          | Port (see $\overline{RD}$ and $\overline{WR}$ ).                                     |  |  |  |  |  |  |

| AD10 <sup>(3)</sup>                           |                |                 | I/O   | TTL      | External memory address/data 10.                                                     |  |  |  |  |  |  |

| RE3/AD11                                      | 63             | 77              |       |          |                                                                                      |  |  |  |  |  |  |

| RE3                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| AD11 <sup>(3)</sup>                           |                |                 | I/O   | TTL      | External memory address/data 11.                                                     |  |  |  |  |  |  |

| RE4/AD12                                      | 62             | 76              |       |          |                                                                                      |  |  |  |  |  |  |

| RE4                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| AD12                                          |                |                 | I/O   | TTL      | External memory address/data 12.                                                     |  |  |  |  |  |  |

| RE5/AD13                                      | 61             | 75              |       |          |                                                                                      |  |  |  |  |  |  |

| RE5                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| AD13 <sup>(3)</sup>                           |                |                 | I/O   | TTL      | External memory address/data 13.                                                     |  |  |  |  |  |  |

| RE6/AD14                                      | 60             | 74              |       |          |                                                                                      |  |  |  |  |  |  |

| RE6                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| AD14 <sup>(3)</sup>                           |                |                 | I/O   | TTL      | External memory address/data 14.                                                     |  |  |  |  |  |  |

| RE7/CCP2/AD15                                 | 59             | 73              |       |          |                                                                                      |  |  |  |  |  |  |

| RE7                                           |                |                 | I/O   | ST       | Digital I/O.                                                                         |  |  |  |  |  |  |

| CCP2 <sup>(1,4)</sup>                         |                |                 | I/O   | ST       | Capture2 input/Compare2 output/                                                      |  |  |  |  |  |  |

|                                               |                |                 |       |          | PWM2 output.                                                                         |  |  |  |  |  |  |

| AD15 <sup>(3)</sup>                           |                |                 | I/O   | TTL      | External memory address/data 15.                                                     |  |  |  |  |  |  |

| _egend: TTL = TTL o                           | compatible inp | ut              |       | CMOS =   | CMOS compatible input or output                                                      |  |  |  |  |  |  |

|                                               |                | ut with CMOS le | evels | Analog = | Analog input                                                                         |  |  |  |  |  |  |

| I = Input                                     |                |                 |       |          | Output                                                                               |  |  |  |  |  |  |

| P = Power OD = Open-Drain (no P diode to VDD) |                |                 |       |          |                                                                                      |  |  |  |  |  |  |

#### PIC18EXX20 PINOLIT I/O DESCRIPTIONS (CONTINUED) TARI E 1-2.

Microcontroller).

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X20 devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

6: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

## 4.7.1 TWO-WORD INSTRUCTIONS

The PIC18FXX20 devices have four two-word instructions: MOVFF, CALL, GOTO and LFSR. The second word of these instructions has the 4 MSBs set to '1's and is a special kind of NOP instruction. The lower 12 bits of the second word contain data to be used by the instruction. If the first word of the instruction is executed, the data in the second word is accessed. If the second word of the instruction is executed by itself (first word was skipped), it will execute as a NOP. This action is necessary when the two-word instruction is preceded by a conditional instruction that changes the PC. A program example that demonstrates this concept is shown in Example 4-3. Refer to **Section 24.0 "Instruction Set Summary"** for further details of the instruction set.

| EXAMPLE 4-3: | TWO-WORD INSTRUCTIONS |

|--------------|-----------------------|

|              |                       |

| CASE   | 1:   |      |      |           |            |                                     |

|--------|------|------|------|-----------|------------|-------------------------------------|

| Object | Code |      |      | Source Co | de         |                                     |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ    | REG1       | ; is RAM location 0?                |

| 1100   | 0001 | 0010 | 0011 | MOVFF     | REG1, REG2 | ; No, execute 2-word instruction    |

| 1111   | 0100 | 0101 | 0110 |           |            | ; 2nd operand holds address of REG2 |

| 0010   | 0100 | 0000 | 0000 | ADDWF     | REG3       | ; continue code                     |

| CASE   | 2:   |      |      |           |            |                                     |

| Object | Code |      |      | Source Co | de         |                                     |

| 0110   | 0110 | 0000 | 0000 | TSTFSZ    | REG1       | ; is RAM location 0?                |

| 1100   | 0001 | 0010 | 0011 | MOVFF     | REG1, REG2 | ; Yes                               |

| 1111   | 0100 | 0101 | 0110 |           |            | ; 2nd operand becomes NOP           |

| 0010   | 0100 | 0000 | 0000 | ADDWF     | REG3       | ; continue code                     |

## 4.8 Look-up Tables

Look-up tables are implemented two ways. These are:

- Computed GOTO

- Table Reads

## 4.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL).

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to the calling function.

The offset value (value in WREG) specifies the number of bytes that the program counter should advance.

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

## 4.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows 2 bytes of data to be stored in each instruction location.

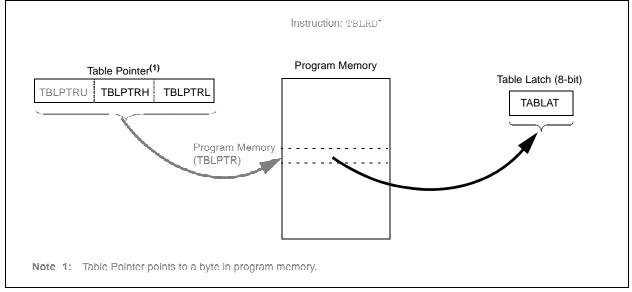

Look-up table data may be stored 2 bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from, or written to program memory. Data is transferred to/from program memory, one byte at a time.

A description of the table read/table write operation is shown in **Section 5.0 "Flash Program Memory"**.

## 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable, during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

## 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

## FIGURE 5-1: TABLE READ OPERATION

NOTES:

| REGISTER 9-8: | PIE2: PER                                                                                                         | IPHERAL                       | INTERRU         | PT ENABL      | E REGIST     | ER 2      |                |        |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|---------------|--------------|-----------|----------------|--------|--|--|--|--|--|

|               | U-0                                                                                                               | R/W-0                         | U-0             | R/W-0         | R/W-0        | R/W-0     | R/W-0          | R/W-0  |  |  |  |  |  |

|               |                                                                                                                   | CMIE                          | _               | EEIE          | BCLIE        | LVDIE     | TMR3IE         | CCP2IE |  |  |  |  |  |

|               | bit 7                                                                                                             |                               |                 |               |              |           |                | bit 0  |  |  |  |  |  |

| bit 7         | Unimplem                                                                                                          | ented: Read                   | <b>d as</b> '0' |               |              |           |                |        |  |  |  |  |  |

| bit 6         | CMIE: Comparator Interrupt Enable bit                                                                             |                               |                 |               |              |           |                |        |  |  |  |  |  |

|               | <ul> <li>1 = Enables the comparator interrupt</li> <li>0 = Disables the comparator interrupt</li> </ul>           |                               |                 |               |              |           |                |        |  |  |  |  |  |

| bit 5         | Unimplem                                                                                                          | Unimplemented: Read as '0'    |                 |               |              |           |                |        |  |  |  |  |  |

| bit 4         | EEIE: Data EEPROM/Flash Write Operation Interrupt Enable bit                                                      |                               |                 |               |              |           |                |        |  |  |  |  |  |

|               | <ul> <li>1 = Enables the write operation interrupt</li> <li>0 = Disables the write operation interrupt</li> </ul> |                               |                 |               |              |           |                |        |  |  |  |  |  |

| bit 3         | BCLIE: Bu                                                                                                         | s Collision Ir                | nterrupt Ena    | ble bit       |              |           |                |        |  |  |  |  |  |

|               |                                                                                                                   | s the bus co<br>as the bus co |                 | •             |              |           |                |        |  |  |  |  |  |

| bit 2         | LVDIE: Lov                                                                                                        | w-Voltage De                  | etect Interru   | pt Enable bit | t            |           |                |        |  |  |  |  |  |

|               |                                                                                                                   | s the Low-Ves the Low-Ves     |                 |               |              |           |                |        |  |  |  |  |  |

| bit 1         | TMR3IE: T                                                                                                         | MR3 Overflo                   | ow Interrupt    | Enable bit    |              |           |                |        |  |  |  |  |  |

|               |                                                                                                                   | s the TMR3<br>es the TMR3     |                 |               |              |           |                |        |  |  |  |  |  |

| bit 0         | <b>CCP2IE:</b> CCP2 Interrupt Enable bit<br>1 = Enables the CCP2 interrupt<br>0 = Disables the CCP2 interrupt     |                               |                 |               |              |           |                |        |  |  |  |  |  |

|               | Legend:                                                                                                           |                               |                 |               |              |           |                |        |  |  |  |  |  |

|               | R = Reada                                                                                                         | ble bit                       | W = W           | ritable bit   | U = Unim     | plemented | bit, read as ' | 0'     |  |  |  |  |  |

|               | - n = Value                                                                                                       | at POR                        | '1' = Bi        | it is set     | '0' = Bit is | s cleared | x = Bit is u   | nknown |  |  |  |  |  |

| TABLE 10-3. PU               |       |                       | i                                                                                                                                                                                                                                              |

|------------------------------|-------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                         | Bit#  | Buffer                | Function                                                                                                                                                                                                                                       |

| RB0/INT0                     | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 0.<br>Internal software programmable weak pull-up.                                                                                                                                                |

| RB1/INT1                     | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 1.<br>Internal software programmable weak pull-up.                                                                                                                                                |

| RB2/INT2                     | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                                                                                                |

| RB3/INT3/CCP2 <sup>(3)</sup> | bit 3 | TTL/ST <sup>(4)</sup> | Input/output pin or external interrupt input 3. Capture2 input/Compare2 output/PWM output (when CCP2MX configuration bit is enabled, all PIC18F8X20 operating modes except Microcontroller mode). Internal software programmable weak pull-up. |

| RB4/KBI0                     | bit 4 | TTL                   | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                                                                                                                   |

| RB5/KBI1/PGM                 | bit 5 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Low-voltage ICSP enable pin.                                                                                                                   |

| RB6/KBI2/PGC                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming clock.                                                                                                                      |

| RB7/KBI3/PGD                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Serial programming data.                                                                                                                       |

#### TABLE 10-3 PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: RC1 is the alternate assignment for CCP2 when CCP2MX is not set (all operating modes except Microcontroller mode).

- 4: This buffer is a Schmitt Trigger input when configured as the CCP2 input.

INT2IE

| TADLL   | 0-4. 30      |               |            |           | 1000CIA   |        | FOR    | D     |                      |                                 |

|---------|--------------|---------------|------------|-----------|-----------|--------|--------|-------|----------------------|---------------------------------|

| Name    | Bit 7        | Bit 6         | Bit 5      | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| PORTB   | RB7          | RB6           | RB5        | RB4       | RB3       | RB2    | RB1    | RB0   | xxxx xxxx            | uuuu uuuu                       |

| LATB    | LATB Data    | a Output Re   |            | xxxx xxxx | uuuu uuuu |        |        |       |                      |                                 |

| TRISB   | PORTB D      | ata Directior | n Register |           |           |        |        |       | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE     | INTOIE    | RBIE      | TMR0IF | INTOIF | RBIF  | 0000 0000            | 0000 0000                       |

| INTCON2 | RBPU         | INTEDG0       | INTEDG1    | INTEDG2   | INTEDG3   | TMR0IP | INT3IP | RBIP  | 1111 1111            | 1111 1111                       |

INT1IE

INT3IF

INT2IF

INT1IF

#### TARI E 10-1. SUMMARY OF REGISTERS ASSOCIATED WITH PORTR

INT3IE x = unknown, u = unchanged. Shaded cells are not used by PORTB. Legend:

INTCON3

INT2IP

INT1IP

1100 0000

1100 0000

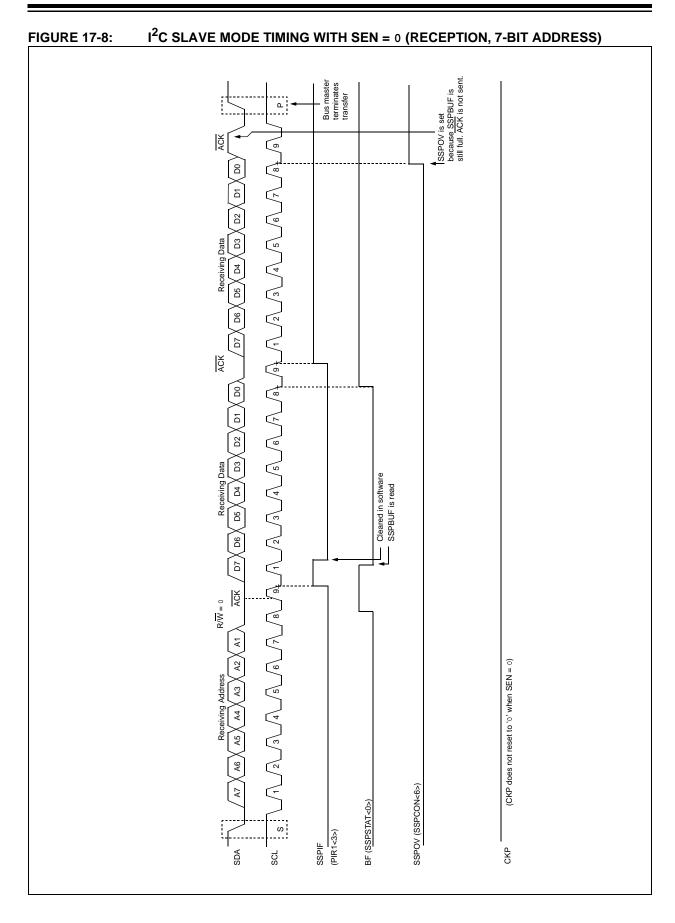

## **REGISTER 17-4:** SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C MODE)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7 WCOL: Write Collision Detect bit

In Master Transmit mode:

- 1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software)

- 0 = No collision

#### In Slave Transmit mode:

- 1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

- 0 = No collision

- In Receive mode (Master or Slave modes):

This is a "don't care" bit.

#### bit 6 **SSPOV:** Receive Overflow Indicator bit

- In Receive mode:

- 1 = A byte is received while the SSPBUF register is still holding the previous byte (must be cleared in software)

- 0 = No overflow

In Transmit mode:

This is a "don't care" bit in Transmit mode.

- bit 5 SSPEN: Synchronous Serial Port Enable bit

- 1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

Note: When enabled, the SDA and SCL pins must be properly configured as input or output.

- bit 4 **CKP:** SCK Release Control bit

- In Slave mode:

- 1 = Release clock

- 0 = Holds clock low (clock stretch), used to ensure data setup time

- In Master mode:

Unused in this mode.

#### bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 1111 =  $I^2C$  Slave mode, 10-bit address with Start and Stop bit interrupts enabled

- $1110 = I^2C$  Slave mode, 7-bit address with Start and Stop bit interrupts enabled

- $1011 = I^2C$  Firmware Controlled Master mode (Slave Idle)

- $1000 = I_{C}^{2}$  Master mode, clock = Fosc/(4 \* (SSPADD + 1))

- 0111 =  $I^2C$  Slave mode, 10-bit address

- $0110 = I^2C$  Slave mode, 7-bit address

- **Note:** Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

### Legend:

| - J                |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

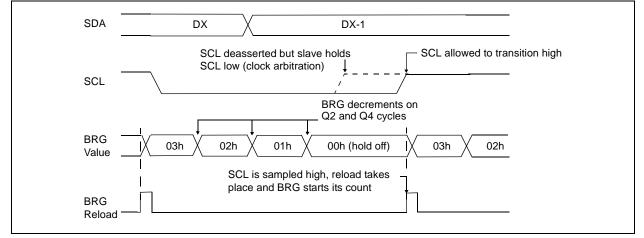

## 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 15-18).

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to '0'. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, Figure 17-30.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

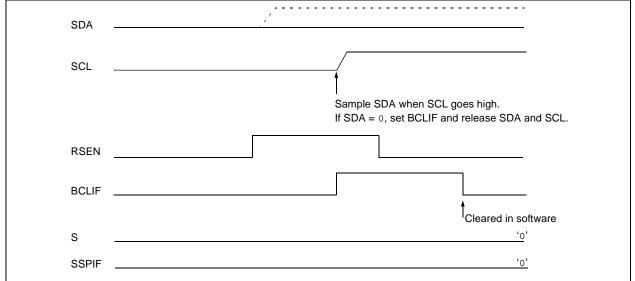

## FIGURE 17-29: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

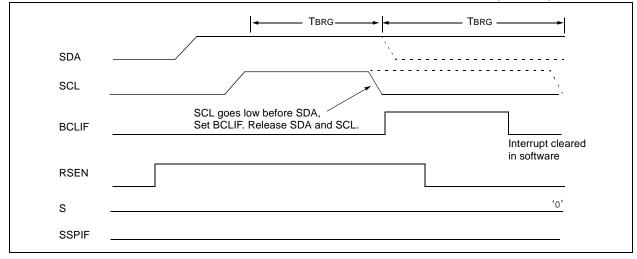

#### FIGURE 17-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

### 17.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to '0'. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 17-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 17-32).

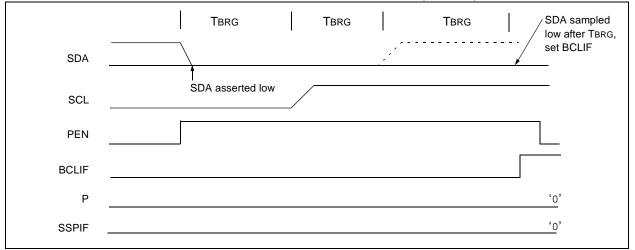

### FIGURE 17-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

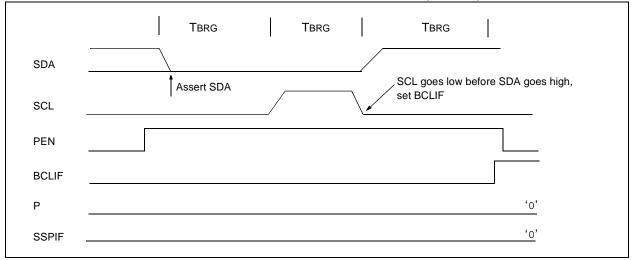

#### FIGURE 17-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| DAUD                   | Fosc = 40 MHz |            |                             |        | 33 MHz     |                             |        | 25 MHz     |                             |        | 20 MHz     |                             |

|------------------------|---------------|------------|-----------------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|

| BAUD<br>RATE<br>(Kbps) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                    | NA            | -          | -                           | NA     | -          | -                           | NA     | -          | -                           | NA     | -          | -                           |

| 1.2                    | NA            | -          | -                           | NA     | -          | -                           | NA     | -          | -                           | NA     | -          | -                           |

| 2.4                    | NA            | -          | -                           | NA     | -          | -                           | NA     | -          | -                           | NA     | -          | -                           |

| 9.6                    | NA            | -          | -                           | NA     | -          | -                           | NA     | -          | -                           | NA     | -          | -                           |

| 19.2                   | NA            | -          | -                           | NA     | -          | -                           | NA     | -          | -                           | NA     | -          | -                           |

| 76.8                   | 76.92         | +0.16      | 129                         | 77.10  | +0.39      | 106                         | 77.16  | +0.47      | 80                          | 76.92  | +0.16      | 64                          |

| 96                     | 96.15         | +0.16      | 103                         | 95.93  | -0.07      | 85                          | 96.15  | +0.16      | 64                          | 96.15  | +0.16      | 51                          |

| 300                    | 303.03        | +1.01      | 32                          | 294.64 | -1.79      | 27                          | 297.62 | -0.79      | 20                          | 294.12 | -1.96      | 16                          |

| 500                    | 500           | 0          | 19                          | 485.30 | -2.94      | 16                          | 480.77 | -3.85      | 12                          | 500    | 0          | 9                           |

| HIGH                   | 10000         | -          | 0                           | 8250   | -          | 0                           | 6250   | -          | 0                           | 5000   | -          | 0                           |

| LOW                    | 39.06         | -          | 255                         | 32.23  | -          | 255                         | 24.41  | -          | 255                         | 19.53  | -          | 255                         |

#### TABLE 18-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD           | Fosc = 16 MHz |            |                             | 10 MHz |            |                             |         | 7.15909 M⊦ | Iz                          | 5.0688 MHz |            |                             |

|----------------|---------------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|------------|------------|-----------------------------|

| RATE<br>(Kbps) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3            | NA            | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA         | -          | -                           |

| 1.2            | NA            | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA         | -          | -                           |

| 2.4            | NA            | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA         | -          | -                           |

| 9.6            | NA            | -          | -                           | NA     | -          | -                           | 9.62    | +0.23      | 185                         | 9.60       | 0          | 131                         |

| 19.2           | 19.23         | +0.16      | 207                         | 19.23  | +0.16      | 129                         | 19.24   | +0.23      | 92                          | 19.20      | 0          | 65                          |

| 76.8           | 76.92         | +0.16      | 51                          | 75.76  | -1.36      | 32                          | 77.82   | +1.32      | 22                          | 74.54      | -2.94      | 16                          |

| 96             | 95.24         | -0.79      | 41                          | 96.15  | +0.16      | 25                          | 94.20   | -1.88      | 18                          | 97.48      | +1.54      | 12                          |

| 300            | 307.70        | +2.56      | 12                          | 312.50 | +4.17      | 7                           | 298.35  | -0.57      | 5                           | 316.80     | +5.60      | 3                           |

| 500            | 500           | 0          | 7                           | 500    | 0          | 4                           | 447.44  | -10.51     | 3                           | 422.40     | -15.52     | 2                           |

| HIGH           | 4000          | -          | 0                           | 2500   | -          | 0                           | 1789.80 | -          | 0                           | 1267.20    | -          | 0                           |

| LOW            | 15.63         | -          | 255                         | 9.77   | -          | 255                         | 6.99    | -          | 255                         | 4.95       | -          | 255                         |

| BAUD           | Fosc = 4 MHz |            |                             | 3.579545 MHz |            |                             |       | 1 MHz      |                             |       | 32.768 kHz |                             |  |

|----------------|--------------|------------|-----------------------------|--------------|------------|-----------------------------|-------|------------|-----------------------------|-------|------------|-----------------------------|--|

| RATE<br>(Kbps) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3            | NA           | -          | -                           | NA           | -          | -                           | NA    | -          | -                           | 0.30  | +1.14      | 26                          |  |

| 1.2            | NA           | -          | -                           | NA           | -          | -                           | 1.20  | +0.16      | 207                         | 1.17  | -2.48      | 6                           |  |

| 2.4            | NA           | -          | -                           | NA           | -          | -                           | 2.40  | +0.16      | 103                         | 2.73  | +13.78     | 2                           |  |

| 9.6            | 9.62         | +0.16      | 103                         | 9.62         | +0.23      | 92                          | 9.62  | +0.16      | 25                          | 8.20  | -14.67     | 0                           |  |

| 19.2           | 19.23        | +0.16      | 51                          | 19.04        | -0.83      | 46                          | 19.23 | +0.16      | 12                          | NA    | -          | -                           |  |

| 76.8           | 76.92        | +0.16      | 12                          | 74.57        | -2.90      | 11                          | 83.33 | +8.51      | 2                           | NA    | -          | -                           |  |

| 96             | 1000         | +4.17      | 9                           | 99.43        | +3.57      | 8                           | 83.33 | -13.19     | 2                           | NA    | -          | -                           |  |

| 300            | 333.33       | +11.11     | 2                           | 298.30       | -0.57      | 2                           | 250   | -16.67     | 0                           | NA    | -          | -                           |  |

| 500            | 500          | 0          | 1                           | 447.44       | -10.51     | 1                           | NA    | -          | -                           | NA    | -          | -                           |  |

| HIGH           | 1000         | -          | 0                           | 894.89       | -          | 0                           | 250   | -          | 0                           | 8.20  | -          | 0                           |  |

| LOW            | 3.91         | -          | 255                         | 3.50         | -          | 255                         | 0.98  | -          | 255                         | 0.03  | -          | 255                         |  |

| Name   | Bit 7        | Bit 6         | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>all other<br>Resets |

|--------|--------------|---------------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| CMCON  | C2OUT        | C1OUT         | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000       | 0000 0000                       |

| CVRCON | CVREN        | CVROE         | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   | 0000 0000       | 0000 0000                       |

| INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 0000       | 0000 0000                       |

| PIR2   |              | CMIF          | —      | _      | BCLIF  | LVDIF  | TMR3IF | CCP2IF | -0 0000         | -0 0000                         |

| PIE2   |              | CMIE          | —      | _      | BCLIE  | LVDIE  | TMR3IE | CCP2IE | -0 0000         | -0 0000                         |

| IPR2   |              | CMIP          | —      | _      | BCLIP  | LVDIP  | TMR3IP | CCP2IP | -1 1111         | -1 1111                         |

| PORTF  | RF7          | RF6           | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | x000 0000       | u000 0000                       |

| LATF   | LATF7        | LATF6         | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx xxxx       | uuuu uuuu                       |

| TRISF  | TRISF7       | TRISF6        | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 1111 1111       | 1111 1111                       |

## TABLE 20-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'.

Shaded cells are unused by the comparator module.

## 23.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The  $\overline{TO}$  bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/ disables the operation of the WDT.

The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

- **Note 1:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- 2: When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared, but the postscaler assignment is not changed.

## 23.2.1 CONTROL REGISTER

Register 23-15 shows the WDTCON register. This is a readable and writable register, which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

## **REGISTER 23-15: WDTCON REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | —   | —   | —   | —   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

#### bit 7-1 Unimplemented: Read as '0'

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

1 = Watchdog Timer is on

0 = Watchdog Timer is turned off if the WDTEN configuration bit in the configuration register = 0

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Mnem      | onic,                   | Description                      | Cycles | 16-Bit Instruction Word |      |      |      | Status          |       |

|-----------|-------------------------|----------------------------------|--------|-------------------------|------|------|------|-----------------|-------|

| Operands  |                         | Description                      | Cycles | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL O | PERATIC                 | DNS                              |        |                         |      |      |      |                 |       |

| ADDLW     | k                       | Add literal and WREG             | 1      | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k                       | AND literal with WREG            | 1      | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW     | k                       | Inclusive OR literal with WREG   | 1      | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR      | f, k                    | Move literal (12-bit) 2nd word   | 2      | 1110                    | 1110 | 00ff | kkkk | None            |       |

|           |                         | to FSRx 1st word                 |        | 1111                    | 0000 | kkkk | kkkk |                 |       |

| MOVLB     | k                       | Move literal to BSR<3:0>         | 1      | 0000                    | 0001 | 0000 | kkkk | None            |       |

| MOVLW     | k                       | Move literal to WREG             | 1      | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW     | k                       | Multiply literal with WREG       | 1      | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW     | k                       | Return with literal in WREG      | 2      | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW     | k                       | Subtract WREG from literal       | 1      | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k                       | Exclusive OR literal with WREG   | 1      | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEM  | $ORY \leftrightarrow F$ | <b>PROGRAM MEMORY OPERATIONS</b> | 5      |                         |      |      |      |                 |       |

| TBLRD*    |                         | Table Read                       | 2      | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+   |                         | Table Read with post-increment   |        | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-   |                         | Table Read with post-decrement   |        | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*   |                         | Table Read with pre-increment    |        | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*    |                         | Table Write                      | 2 (5)  | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+   |                         | Table Write with post-increment  |        | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-   |                         | Table Write with post-decrement  |        | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*   |                         | Table Write with pre-increment   |        | 0000                    | 0000 | 0000 | 1111 | None            |       |

### TABLE 24-1: PIC18FXXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| Syntax:[ label ] CLRF f [,a]Syntax:[ label ] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Operands: $0 \le f \le 255$ Operands:None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| $a \in [0,1]$ Operation: 000h $\rightarrow$ WDT,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Operation: $000h \rightarrow f$ $000h \rightarrow WDT$ postsc $1 \rightarrow Z$ $1 \rightarrow TO$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | aler,          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Status Affected: Z<br>Encoding: 0110 1010 5555 5555 Status Affected: TO, PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 000 0100       |

| Description:         Clears the contents of the specified<br>register. If 'a' is '0', the Access         Encoding.         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000 </td <td></td> |                |

| Bank will be selected, overriding Watchdog Timer. It a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| the BSR value. If 'a' = 1, then the postscaler of the WD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T. Status bits |

| bank will be selected as per the TO and PD are set.<br>BSR value (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Worde: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| Cycles: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>.</b>       |

| Q Cycle Activity:         Q1         Q2         Q3           Q1         Q2         Q3         Q4         Decode         No         Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q4<br>No       |

| Decode Read Process Write Decode No Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | operation      |