Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 25MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 68                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 3.75K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8620t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

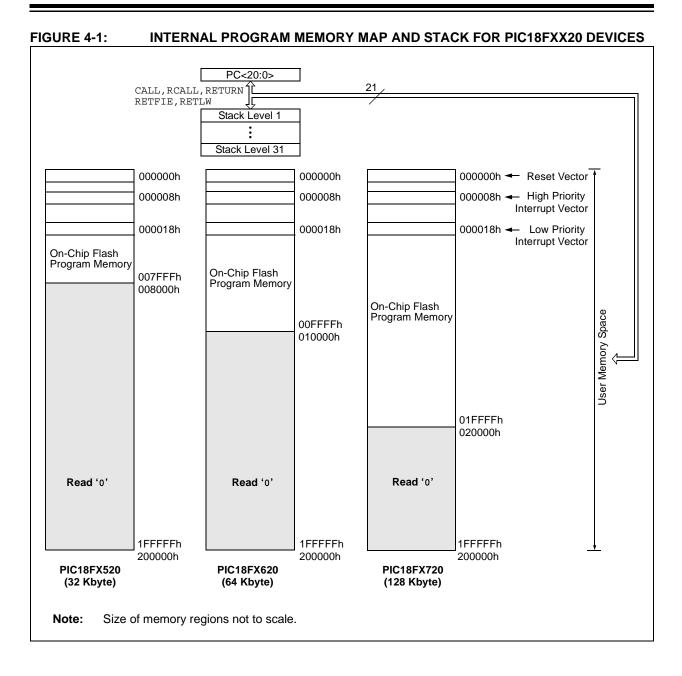

|                                   | Inte              | rnal Program Men   | nory           | External Program Memory |                    |                |  |  |

|-----------------------------------|-------------------|--------------------|----------------|-------------------------|--------------------|----------------|--|--|

| Operating Mode                    | Execution<br>From | Table Read<br>From | Table Write To | Execution<br>From       | Table Read<br>From | Table Write To |  |  |

| Microprocessor                    | No Access         | No Access          | No Access      | Yes                     | Yes                | Yes            |  |  |

| Microprocessor<br>with Boot Block | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes            |  |  |

| Microcontroller                   | Yes               | Yes                | Yes            | No Access               | No Access          | No Access      |  |  |

| Extended<br>Microcontroller       | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes            |  |  |

#### **REGISTER 4-1: CONFIG3L CONFIGURATION BYTE** R/P-1 U-0 U-0 U-0 U-0 U-0 R/P-1 R/P-1 WAIT PM1 PM0 bit 7 bit 0 bit 7 WAIT: External Bus Data Wait Enable bit 1 = Wait selections unavailable, device will not wait 0 = Wait programmed by WAIT1 and WAIT0 bits of MEMCOM register (MEMCOM<5:4>) Unimplemented: Read as '0' bit 6-2 bit 1-0 PM1:PM0: Processor Data Memory Mode Select bits 11 = Microcontroller mode 10 = Microprocessor mode 01 = Microcontroller with Boot Block mode 00 = Extended Microcontroller mode Legend: P = Programmable bit U = Unimplemented bit, read as '0' R = Readable bit - n = Value after erase '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

|                         | Microprocessor<br>Mode (MP) |                               |                       |                          | Microproces<br>with Boot Bl<br>Mode (MPB | ock                          | Microco<br>Mode                   | Extended<br>Microcontroller<br>Mode (EMC)     |                                 |                                     |                              |

|-------------------------|-----------------------------|-------------------------------|-----------------------|--------------------------|------------------------------------------|------------------------------|-----------------------------------|-----------------------------------------------|---------------------------------|-------------------------------------|------------------------------|

| Program Space Execution | 000000h                     | External<br>Program<br>Memory | 1                     | 000000<br>Boot<br>Boot+1 | External<br>Program<br>Memory            | On-Chip<br>Program<br>Memory | 000000h<br>Boundary<br>Boundary+1 | On-Chip<br>Program<br>Memory<br>Reads<br>'0's | 000000h<br>Boundary<br>Boundary | +1<br>External<br>Program<br>Memory | On-Chip<br>Program<br>Memory |

|                         |                             | External<br>Memory            | J<br>On-Chip<br>Flash | 1FFFF                    | -n<br>External<br>Memory                 | On-Chip<br>Flash             | 1FFFFFh                           | On-Chip<br>Flash                              | 1FFFFh                          | External<br>Memory                  | On-Chip<br>Flash             |

| Bour                    | ndary Valu                  | es for Mi                     | croprocessor          | with Bo                  | ot Block, Mic                            | rocontrolle                  | r and Extended M                  | licrocontroller ı                             | nodes <sup>(1)</sup>            |                                     |                              |

|                         | Device                      |                               | Boot                  |                          | Boot+                                    | ·1                           | Boundary                          | Bound                                         | lary+1                          | Avail<br>Memory                     |                              |

|                         | PIC18F65                    | 20                            | 0007FF                | h                        | 000800                                   | Dh                           | 007FFFh                           | 0080                                          | 000h                            | M                                   | С                            |

|                         | PIC18F66                    | 20                            | 0001FF                | h                        | 00020                                    | Dh                           | 00FFFFh                           | 0100                                          | 000h                            | M                                   | С                            |

|                         | PIC18F67                    | 20                            | 0001FF                | h                        | 00020                                    | 0h                           | 01FFFFh                           | 0200                                          | 000h                            | Μ                                   | С                            |

PIC18F8720

0001FFh

000200h

01FFFFh

020000h

MP, MPBB, MC, EMC

Note 1:

PIC18F6X20 devices are included here for completeness, to show the boundaries of their Boot Blocks and program memory spaces.

007FFFh

00FFFFh

008000h

010000h

000800h

000200h

0007FFh

0001FFh

PIC18F8520

PIC18F8620

MP, MPBB, MC, EMC

MP, MPBB, MC, EMC

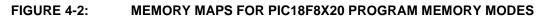

### 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined, such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

### 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). Figure 4-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4 "PCL, PCLATH and PCLATU").

The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on

word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-5 shows how the instruction "GOTO 00006h" is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. **Section 24.0 "Instruction Set Summary"** provides further details of the instruction set.

### FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

|                |           |                     | <b>LSB</b> = 1 | <b>LSB</b> = 0 | Word Address $\downarrow$ |

|----------------|-----------|---------------------|----------------|----------------|---------------------------|

|                | Program I |                     |                |                | 000000h                   |

|                | Byte Loca | tions $\rightarrow$ |                |                | 000002h                   |

|                |           |                     |                |                | 000004h                   |

|                |           |                     |                |                | 000006h                   |

| Instruction 1: |           | 055h                | 0Fh            | 55h            | 000008h                   |

| Instruction 2: | GOTO      | 000006h             | EFh            | 03h            | 00000Ah                   |

|                |           |                     | F0h            | 00h            | 00000Ch                   |

| Instruction 3: | MOVFF     | 123h, 456h          | Clh            | 23h            | 00000Eh                   |

|                |           |                     | F4h            | 56h            | 000010h                   |

|                |           |                     |                |                | 000012h                   |

|                |           |                     |                |                | 000014h                   |

| File Name | Bit 7                                                                                                  | Bit 6                                                                                                   | Bit 5                 | Bit 4          | Bit 3                       | Bit 2          | Bit 1            | Bit 0     | Value on<br>POR, BOR | Details on page: |

|-----------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|----------------|-----------------------------|----------------|------------------|-----------|----------------------|------------------|

| TOSU      | _                                                                                                      | _                                                                                                       | _                     | Top-of-Stack   | Upper Byte (T               | OS<20:16>)     |                  | •         | 0 0000               | 32, 42           |

| TOSH      | Top-of-Stack                                                                                           | High Byte (TO                                                                                           | DS<15:8>)             |                |                             |                |                  |           | 0000 0000            | 32, 42           |

| TOSL      | Top-of-Stack                                                                                           | Top-of-Stack Low Byte (TOS<7:0>)                                                                        |                       |                |                             |                |                  |           |                      |                  |

| STKPTR    | STKFUL                                                                                                 | STKUNF                                                                                                  | —                     | Return Stack   | Pointer                     |                |                  |           | 00-0 0000            | 32, 43           |

| PCLATU    | —                                                                                                      |                                                                                                         | bit 21                | Holding Regi   | ster for PC<20              | ):16>          |                  |           | 10 0000              | 32, 44           |

| PCLATH    | Holding Reg                                                                                            | Holding Register for PC<15:8>                                                                           |                       |                |                             |                |                  |           |                      |                  |

| PCL       | PC Low Byte (PC<7:0>)                                                                                  |                                                                                                         |                       |                |                             |                |                  |           |                      | 32, 44           |

| TBLPTRU   | —                                                                                                      | _                                                                                                       | bit 21 <sup>(2)</sup> | Program Mer    | nory Table Poi              | nter Upper By  | te (TBLPTR<2     | 0:16>)    | 00 0000              | 32, 64           |

| TBLPTRH   | Program Me                                                                                             | mory Table Po                                                                                           | ointer High By        | te (TBLPTR<    | 15:8>)                      |                |                  |           | 0000 0000            | 32, 64           |

| TBLPTRL   | Program Me                                                                                             | mory Table Po                                                                                           | ointer Low Byt        | e (TBLPTR<7    | ':0>)                       |                |                  |           | 0000 0000            | 32, 64           |

| TABLAT    | Program Me                                                                                             | mory Table La                                                                                           | itch                  |                |                             |                |                  |           | 0000 0000            | 32, 64           |

| PRODH     | Product Reg                                                                                            | ister High Byte                                                                                         | Э                     |                |                             |                |                  |           | xxxx xxxx            | 32, 85           |

| PRODL     | Product Reg                                                                                            | ister Low Byte                                                                                          | )                     |                |                             |                |                  |           | xxxx xxxx            | 32, 85           |

| INTCON    | GIE/GIEH                                                                                               | PEIE/GIEL                                                                                               | TMR0IE                | INT0IE         | RBIE                        | TMR0IF         | <b>INT0IF</b>    | RBIF      | 0000 0000            | 32, 89           |

| INTCON2   | RBPU                                                                                                   | INTEDG0                                                                                                 | INTEDG1               | INTEDG2        | INTEDG3                     | TMR0IP         | INT3IP           | RBIP      | 1111 1111            | 32, 90           |

| INTCON3   | INT2IP                                                                                                 | INT1IP                                                                                                  | INT3IE                | INT2IE         | INT1IE                      | INT3IF         | INT2IF           | INT1IF    | 1100 0000            | 32, 91           |

| INDF0     | Uses conten                                                                                            | ts of FSR0 to a                                                                                         | iddress data n        | nemory – value | e of FSR0 not o             | changed (not a | physical regis   | ter)      | n/a                  | 57               |

| POSTINC0  |                                                                                                        | Uses contents of FSR0 to address data memory – value of FSR0 post-incremented (not a physical register) |                       |                |                             |                |                  |           |                      | 57               |

| POSTDEC0  |                                                                                                        |                                                                                                         |                       |                |                             |                |                  |           | n/a                  | 57               |

| PREINC0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) |                                                                                                         |                       |                |                             |                |                  |           | n/a                  | 57               |

| PLUSW0    | Uses conten                                                                                            |                                                                                                         | address data          | memory – val   | ue of FSR0 pr               |                |                  | <u> </u>  | n/a                  | 57               |

| FSR0H     | —                                                                                                      | _                                                                                                       | _                     | _              |                             | Memory Addr    | ess Pointer 0    | High Byte | 0000                 | 32, 57           |

| FSR0L     | Indirect Data                                                                                          | Memory Add                                                                                              | ress Pointer (        | Low Byte       |                             | ,              |                  | <u> </u>  | xxxx xxxx            | 32, 57           |

| WREG      | Working Reg                                                                                            | gister                                                                                                  |                       |                |                             |                |                  |           | xxxx xxxx            | 32               |

| INDF1     |                                                                                                        | -                                                                                                       | address data          | memory – val   | ue of FSR1 no               | t changed (no  | t a physical re  | gister)   | n/a                  | 57               |

| POSTINC1  |                                                                                                        | ts of FSR1 to                                                                                           |                       | -              | ue of FSR1 po               |                |                  | <u> </u>  | n/a                  | 57               |

| POSTDEC1  |                                                                                                        | ts of FSR1 to                                                                                           | address data          | memory – val   | ue of FSR1 po               | st-decrement   | ed               |           | n/a                  | 57               |

| PREINC1   | Uses conten<br>(not a physic                                                                           |                                                                                                         | address data          | memory – val   | ue of FSR1 pr               | e-incremented  | 1                |           | n/a                  | 57               |

| PLUSW1    |                                                                                                        | ts of FSR1 to<br>al register) – v                                                                       |                       |                | ue of FSR1 pr<br>ie in WREG | e-incremented  | 1                |           | n/a                  | 57               |

| FSR1H     | —                                                                                                      | —                                                                                                       | —                     | —              |                             | Memory Addr    | ess Pointer 1    | High Byte | 0000                 | 33, 57           |

| FSR1L     | Indirect Data                                                                                          | Memory Add                                                                                              | ress Pointer 1        | Low Byte       |                             |                |                  |           | xxxx xxxx            | 33, 57           |

| BSR       |                                                                                                        | —                                                                                                       | —                     | —              | Bank Select I               | Register       |                  |           | 0000                 | 33, 56           |

| INDF2     | Uses conten                                                                                            | ts of FSR2 to                                                                                           | address data          | memory – val   | ue of FSR2 no               | t changed (no  | ot a physical re | egister)  | n/a                  | 57               |

| POSTINC2  | Uses conten<br>(not a physic                                                                           |                                                                                                         | address data          | memory – val   | ue of FSR2 po               | st-incremente  | ed               |           | n/a                  | 57               |

| POSTDEC2  |                                                                                                        | ts of FSR2 to                                                                                           | address data          | memory – val   | ue of FSR2 po               | st-decrement   | ed               |           | n/a                  | 57               |

### TABLE 4-3: REGISTER FILE SUMMARY

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator modes only and read '0' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers are unused on PIC18F6X20 devices; always maintain these clear.

### 4.13 Status Register

bit 7-5 bit 4

bit 3

bit 2

The Status register, shown in Register 4-3, contains the arithmetic status of the ALU. The Status register can be the destination for any instruction, as with any other register. If the Status register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the Status register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the Status register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the Status register, because these instructions do not affect the Z, C, DC, OV or N bits from the Status register. For other instructions not affecting any status bits, see Table 24-1.

| Note: | The C and DC bits operate as a borrow | 2 |  |  |  |  |  |  |  |

|-------|---------------------------------------|---|--|--|--|--|--|--|--|

|       | and digit borrow bit respectively, in |   |  |  |  |  |  |  |  |

|       | subtraction.                          |   |  |  |  |  |  |  |  |

### REGISTER 4-3: STATUS REGISTER

| U-0           | U-0             | U-0           | R/W-x               | R/W-x         | R/W-x         | R/W-x          | R/W-x   |

|---------------|-----------------|---------------|---------------------|---------------|---------------|----------------|---------|

| _             | _               | _             | Ν                   | OV            | Z             | DC             | С       |

| bit 7         |                 |               |                     |               |               |                | bit C   |

| Unimplem      | ented: Read     | <b>as</b> '0' |                     |               |               |                |         |

| N: Negativ    |                 |               |                     |               |               |                |         |

| 0             |                 | ed arithmeti  | c (2's comp         | ement). It ir | dicates whe   | ther the resi  | ult was |

|               | LU MSB = 1      |               | - (= - <b>o</b> omp |               |               |                |         |

| •             | was negative    | ,             |                     |               |               |                |         |

|               | was positive    |               |                     |               |               |                |         |

| OV: Overflo   | •               |               |                     |               |               |                |         |

|               |                 | ed arithmeti  | c (2's comp         | ement). It ir | ndicates an o | overflow of th | ne      |

|               | itude, which    |               | · ·                 | ,             |               |                |         |

| 1 = Overfloor | w occurred      | for signed a  | rithmetic (in       | this arithme  | tic operation | l)             |         |

|               | rflow occurre   | 0             | (                   |               |               | 7              |         |

| Z: Zero bit   |                 |               |                     |               |               |                |         |

| 1 = The rest  | sult of an arit | hmetic or lo  | aic operatio        | n is zero     |               |                |         |

|               | sult of an arit |               | • .                 |               | 0             |                |         |

|               | arrv/borrow     |               |                     |               |               |                |         |

### bit 1 **DC:** Digit carry/borrow bit

- For ADDWF, ADDLW, SUBLW and SUBWF instructions:

- 1 = A carry-out from the 4th low-order bit of the result occurred

- 0 = No carry-out from the 4th low-order bit of the result

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the 2's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either bit 4 or bit 3 of the source register.

### bit 0 C: Carry/borrow bit

For ADDWF, ADDLW, SUBLW and SUBWF instructions:

- 1 = A carry-out from the Most Significant bit of the result occurred

- 0 = No carry-out from the Most Significant bit of the result occurred

- **Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the 2's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low-order bit of the source register.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

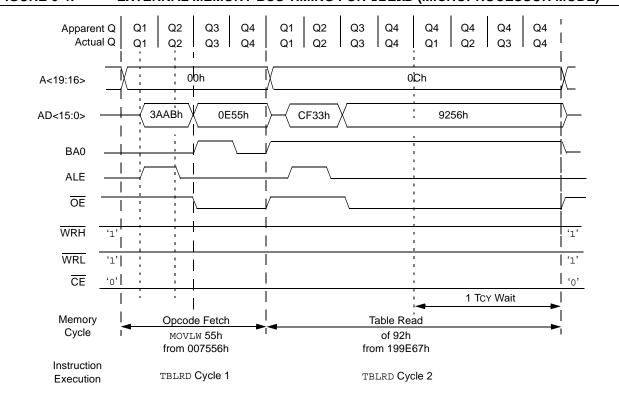

### 6.2.4 16-BIT MODE TIMING

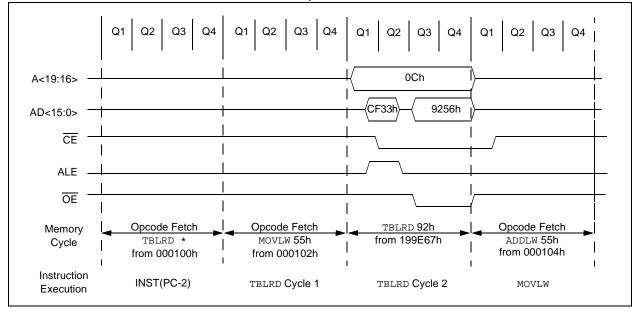

The presentation of control signals on the external memory bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 6-4 through Figure 6-6.

### FIGURE 6-4: EXTERNAL MEMORY BUS TIMING FOR TBLRD (MICROPROCESSOR MODE)

### FIGURE 6-5: EXTERNAL MEMORY BUS TIMING FOR TBLRD (EXTENDED MICROCONTROLLER MODE)

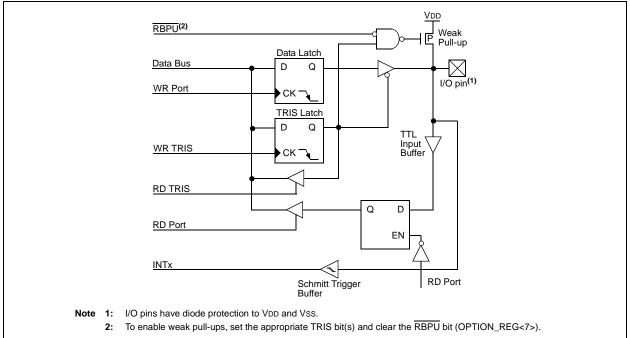

### FIGURE 10-6: BLOCK DIAGRAM OF RB2:RB0 PINS

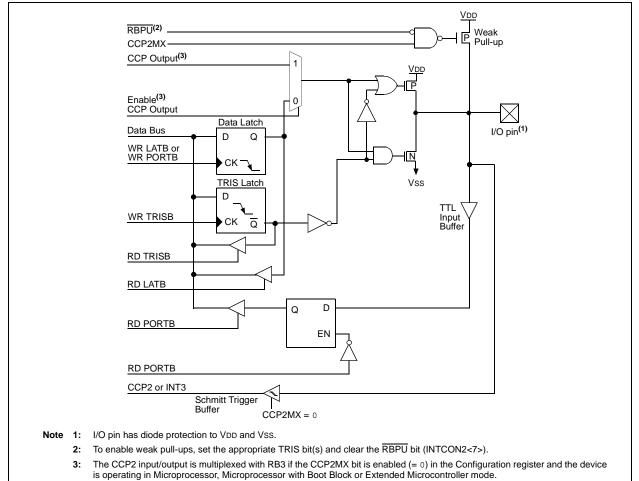

### FIGURE 10-7: BLOCK DIAGRAM OF RB3 PIN

| EXAMPLE | 12-1:  | IMPLEMENTIN  | IG A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE |

|---------|--------|--------------|-------------------------------------------------------|

| RTCinit |        |              |                                                       |

|         | MOVLW  | 0x80         | ; Preload TMR1 register pair                          |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                               |

|         | CLRF   | TMR1L        |                                                       |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                       |

|         | MOVWF  | T10SC        | ; Asynchronous operation, external oscillator         |

|         | CLRF   | secs         | ; Initialize timekeeping registers                    |

|         | CLRF   | mins         | ;                                                     |

|         | MOVLW  | .12          |                                                       |

|         | MOVWF  | hours        |                                                       |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                             |

|         | RETURN |              |                                                       |

| RTCisr  |        |              |                                                       |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                          |

|         | BCF    | PIR1, TMR1IF |                                                       |

|         | INCF   | secs, F      | ; Increment seconds                                   |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | secs         | ; Clear seconds                                       |

|         | INCF   | mins, F      | ; Increment minutes                                   |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                 |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | CLRF   | mins         | ; clear minutes                                       |

|         | INCF   | hours, F     | ; Increment hours                                     |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                   |

|         | CPFSGT |              |                                                       |

|         | RETURN |              | ; No, done                                            |

|         | MOVLW  | .01          | ; Reset hours to 1                                    |

|         | MOVWF  | hours        |                                                       |

|         | RETURN |              | ; Done                                                |

| J       |        |              |                                                       |

### EXAMPLE 12-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

### TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Name   | Bit 7       | Bit 6          | Bit 5       | Bit 4         | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Value on<br>POR, BOR |      | Value on<br>all other<br>Resets |      |

|--------|-------------|----------------|-------------|---------------|----------------|-----------|--------|--------|----------------------|------|---------------------------------|------|

| INTCON | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE        | RBIE           | TMR0IF    | INT0IF | RBIF   | 0000                 | 0000 | 0000                            | 0000 |

| PIR1   | PSPIF       | ADIF           | RCIF        | TXIF          | SSPIF          | CCP1IF    | TMR2IF | TMR1IF | 0000                 | 0000 | 0000                            | 0000 |

| PIE1   | PSPIE       | ADIE           | RCIE        | TXIE          | SSPIE          | CCP1IE    | TMR2IE | TMR1IE | 0000                 | 0000 | 0000                            | 0000 |

| IPR1   | PSPIP       | ADIP           | RCIP        | TXIP          | SSPIP          | CCP1IP    | TMR2IP | TMR1IP | 0111                 | 1111 | 0111                            | 1111 |

| TMR1L  | Holding Reg | gister for the | Least Signi | ficant Byte o | of the 16-bit  | TMR1 Regi | ster   |        | xxxx                 | xxxx | uuuu                            | uuuu |

| TMR1H  | Holding Reg | gister for the | Most Signif | icant Byte o  | f the 16-bit T | MR1 Regis | ster   |        | xxxx                 | xxxx | uuuu                            | uuuu |

| T1CON  | RD16        | —              | T1CKPS1     | T1CKPS0       | T1OSCEN        | T1SYNC    | TMR1CS | TMR10N | 0-00                 | 0000 | u-uu                            | uuuu |

$\label{eq:logend: Legend: Legend: u = unchanged, -= unimplemented, read as `0`. Shaded cells are not used by the Timer1 module.$

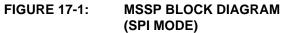

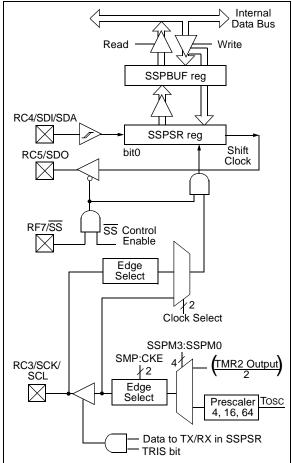

### 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The I<sup>2</sup>C interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode

### 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly, depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

### 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS) – RF7/SS

Figure 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

### 18.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USARTs. It is a dedicated 8-bit Baud Rate Generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTAx<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGx register can be calculated using the formula in Table 18-1. From this, the error in baud rate can be determined. Example 18-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the equation in Example 18-1 can reduce the baud rate error in some cases.

Writing a new value to the SPBRGx register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

### 18.1.1 SAMPLING

The data on the RXx pin (either RC7/RX1/DT1 or RG2/ RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the pin.

| Desired Baud Rate    | = Fosc/(64 (X + 1))                                               |

|----------------------|-------------------------------------------------------------------|

| Solving for X:       |                                                                   |

| Х                    | = $((FOSC/Desired Baud Rate)/64) - 1$                             |

| Х                    | = ((16000000/9600)/64) - 1                                        |

| Х                    | = [25.042] $=$ 25                                                 |

| Calculated Baud Rate | = 1600000/(64 (25 + 1)) = 9615                                    |

| Error                | = (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate |

|                      | = (9615 - 9600)/9600                                              |

|                      | = 0.16%                                                           |

### TABLE 18-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                        | BRGH = 1 (High Speed)        |

|------|---------------------------------------------|------------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X + 1)) | Baud Rate = Fosc/(16(X + 1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X + 1))   | N/A                          |

**Legend:** X = value in SPBRGx (0 to 255)

### TABLE 18-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name   | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|-------|-------|-------|-------|-------|-------|-----------|----------------------|---------------------------------|

| TXSTAx | CSRC                         | TX9   | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D      | 0000 -010            | 0000 -010                       |

| RCSTAx | SPEN                         | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D      | 0000 000x            | 0000 000x                       |

| SPBRGx | Baud Rate Generator Register |       |       |       |       |       |       | 0000 0000 | 0000 0000            |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

**Note 1:** Register names generically refer to both of the identically named registers for the two USART modules, where 'x' indicates the particular module. Bit names and Reset values are identical between modules.

NOTES:

| 23-10:  | CONFIG6    | H: CONFIG      | URATION             | REGISTE                       | R 6 HIGH (E | STIEADD    | RE223000 | JUBN) |

|---------|------------|----------------|---------------------|-------------------------------|-------------|------------|----------|-------|

|         | R/P-1      | R/P-1          | R-1                 | U-0                           | U-0         | U-0        | U-0      | U-0   |

|         | WRTD       | WRTB           | WRTC <sup>(1)</sup> | —                             |             |            |          | —     |

|         | bit 7      |                |                     |                               |             |            |          | bit 0 |

|         |            |                |                     |                               |             |            |          |       |

| bit 7   | WRTD: Da   | ta EEPRON      | Write Prote         | ection bit                    |             |            |          |       |

|         | 1 = Data E | EPROM not      | write-protect       | cted                          |             |            |          |       |

|         | 0 = Data E | EPROM writ     | e-protected         |                               |             |            |          |       |

| bit 6   | WRTB: Bo   | ot Block Wri   | te Protection       | n bit                         |             |            |          |       |

|         |            | X520 devic     |                     |                               |             |            |          |       |

|         |            | <b>`</b>       | ,                   | not write-pro                 |             |            |          |       |

|         |            | •              |                     | write-protec                  | ted         |            |          |       |

|         |            | FX620 and F    |                     |                               | te ete el   |            |          |       |

|         |            | •              | ,                   | not write-pro<br>write-protec |             |            |          |       |

| bit 5   |            |                | -                   | te Protection                 |             |            |          |       |

| C IIC   |            | 0              | 0                   |                               |             |            |          |       |

|         | •          | •              | •                   | 0-3000FFh)<br>0-3000FFh)      |             |            |          |       |

|         | •          | •              | ,                   |                               | •           |            |          |       |

|         | Note 1:    | i his dit is r | ead-only and        | d cannot be                   | changed in  | user mode. |          |       |

| bit 4-0 | Unimplem   | ented: Read    | <b>as</b> '0'       |                               |             |            |          |       |

|         |            |                |                     |                               |             |            |          |       |

### REGISTER 23-10: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

### 23.3 Power-down Mode (Sleep)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared, but keeps running, the  $\overline{\text{PD}}$  bit (RCON<3>) is cleared, the  $\overline{\text{TO}}$  (RCON<4>) bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

### 23.3.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a peripheral interrupt.

The following peripheral interrupts can wake the device from Sleep:

- 1. PSP read or write.

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. TMR3 interrupt. Timer3 must be operating as an asynchronous counter.

- 4. CCP Capture mode interrupt.

- 5. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 6. MSSP (Start/Stop) bit detect interrupt.

- MSSP transmit or receive in Slave mode (SPI/l<sup>2</sup>C).

- 8. USART RX or TX (Synchronous Slave mode).

- 9. A/D conversion (when A/D clock source is RC).

- 10. EEPROM write operation complete.

- 11. LVD interrupt.

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and will cause a "wake-up". The TO and PD bits in the RCON register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 2) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 23.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If an interrupt condition (interrupt flag bit and interrupt enable bits are set) occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt condition occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| RET   | URN             | Return from Subroutine                                                                                                                                       |                                                                                                                            |                                                                               |                                                            |  |  |  |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| Synt  | ax:             | [ label ]                                                                                                                                                    | RETURN                                                                                                                     | [s]                                                                           |                                                            |  |  |  |

| Ope   | rands:          | $s \in [0,1]$                                                                                                                                                | s ∈ [0,1]                                                                                                                  |                                                                               |                                                            |  |  |  |

| Ope   | ration:         | $(TOS) \rightarrow PC,$<br>if s = 1<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |                                                                                                                            |                                                                               |                                                            |  |  |  |

| Statu | us Affected:    | None                                                                                                                                                         |                                                                                                                            |                                                                               |                                                            |  |  |  |

| Enco  | oding:          | 0000                                                                                                                                                         | 0000                                                                                                                       | 0001                                                                          | 001s                                                       |  |  |  |

| Desc  | cription:       | is popped<br>(TOS) is le<br>counter. If<br>the shado<br>STATUSS<br>into their o<br>W, Status                                                                 | and subrout<br>and the to<br>baded into<br>a 's' = 1, th<br>w registers<br>and BSR<br>correspond<br>and BSR.<br>these regi | op of th<br>the pro-<br>e conte<br>s, WS,<br>S, are l<br>ding req<br>If 's' = | e stack<br>ogram<br>ents of<br>loaded<br>gisters,<br>0, no |  |  |  |

| Wor   | ds:             | 1                                                                                                                                                            |                                                                                                                            |                                                                               |                                                            |  |  |  |

| Cycl  | es:             | 2                                                                                                                                                            |                                                                                                                            |                                                                               |                                                            |  |  |  |

| QC    | cycle Activity: |                                                                                                                                                              |                                                                                                                            |                                                                               |                                                            |  |  |  |

|       | Q1              | Q2                                                                                                                                                           | Q3                                                                                                                         |                                                                               | Q4                                                         |  |  |  |

|       | Decode          | No                                                                                                                                                           | Process                                                                                                                    |                                                                               | op PC                                                      |  |  |  |

|       |                 | operation                                                                                                                                                    | Data                                                                                                                       | fro                                                                           | m stack                                                    |  |  |  |

|       | No              | No                                                                                                                                                           | No                                                                                                                         |                                                                               | No                                                         |  |  |  |

|       | operation       | operation                                                                                                                                                    | operation                                                                                                                  | n op                                                                          | peration                                                   |  |  |  |

| Example: | RETURN |

|----------|--------|

After Interrupt PC = TOS

| Syntax:                            | [ label ]                                                                  | RLCF f                                                                             | [,d [,a]                                   |                    |

|------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------|--------------------|

| Operands:                          | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                         | 5                                                                                  |                                            |                    |

| Operation:                         | $(f < n >) \rightarrow$<br>$(f < 7 >) \rightarrow$<br>$(C) \rightarrow de$ |                                                                                    | ',                                         |                    |

| Status Affected:                   | C, N, Z                                                                    |                                                                                    |                                            |                    |

| Encoding:                          | 0011                                                                       | 01da :                                                                             | Efff                                       | ffff               |

|                                    | the Carry<br>is placed<br>is stored<br>(default).                          | he bit to the<br>flag. If 'd' i<br>in W. If 'd' i<br>back in reg<br>If 'a' is '0', | s '0', t<br>s '1', t<br>ister 'f<br>the Ac | he resu<br>he resu |

|                                    | the BSR<br>bank will                                                       | be selecte<br>value. If 'a'<br>be selected<br>e (default).<br>registe              | = 1, tł<br>d as pe                         | nen the            |

| Words:                             | the BSR<br>bank will<br>BSR valu                                           | value. If 'a'<br>be selected<br>e (default).                                       | = 1, tł<br>d as pe                         | nen the            |

| Words:<br>Cycles:                  | the BSR<br>bank will<br>BSR valu                                           | value. If 'a'<br>be selected<br>e (default).                                       | = 1, tł<br>d as pe                         | nen the            |

|                                    | the BSR<br>bank will<br>BSR valu                                           | value. If 'a'<br>be selected<br>e (default).                                       | = 1, tł<br>d as pe                         | nen the            |

| Cycles:                            | the BSR<br>bank will<br>BSR valu                                           | value. If 'a'<br>be selected<br>e (default).                                       | = 1, tł<br>d as pe                         | nen the            |

| Cycles:<br>Q Cycle Activity:       | the BSR<br>bank will<br>BSR valu<br>C<br>1<br>1                            | value. If 'a'<br>be selected<br>e (default).<br>registe                            | = 1, th<br>d as pe<br>er f                 | hen the<br>er the  |

| Cycles:<br>Q Cycle Activity:<br>Q1 | the BSR<br>bank will<br>BSR valu<br>C<br>1<br>1<br>1<br>2<br>2<br>Read     | value. If 'a'<br>be selected<br>e (default).<br>registe<br>Q3<br>Process           | = 1, th<br>d as per<br>er f<br>W<br>des    | Q4<br>Vrite to     |

A

| After Instru |   |      |      |

|--------------|---|------|------|

| REG          | = | 1110 | 0110 |

| W            | = | 1100 | 1100 |

| С            | = | 1    |      |

### 26.1 DC Characteristics: Supply Voltage PIC18F6520/8520/6620/8620/6720/8720 (Industrial, Extended) PIC18LF6520/8520/6620/8620/6720/8720 (Industrial)

| PIC18LF6520/8520/6620/8620/6720/8720<br>(Industrial) |                                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le T_A \le +85^{\circ}C$ for industrial |           |                                                                                                                                                                                       |           |      |                                           |  |

|------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------------------------------------------|--|

|                                                      | PIC18F6520/8520/6620/8620/6720/8720<br>(Industrial, Extended) |                                                                                                                                     |           | tandard Operating Conditions (unless otherwise stated)perating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |           |      |                                           |  |

| Param<br>No.                                         | Symbol                                                        | Characteristic                                                                                                                      | Min       | Nin Typ Max Units Conditions                                                                                                                                                          |           |      |                                           |  |

| D001                                                 | Vdd                                                           | Supply Voltage                                                                                                                      |           |                                                                                                                                                                                       |           |      |                                           |  |

|                                                      |                                                               | PIC18LFXX20                                                                                                                         | 2.0       | _                                                                                                                                                                                     | 5.5       | V    | HS, XT, RC and LP Oscillator mode         |  |

|                                                      |                                                               | PIC18FXX20                                                                                                                          | 4.2       | _                                                                                                                                                                                     | 5.5       | V    |                                           |  |

| D001A                                                | AVdd                                                          | Analog Supply Voltage                                                                                                               | Vdd - 0.3 | _                                                                                                                                                                                     | VDD + 0.3 | V    |                                           |  |

| D002                                                 | Vdr                                                           | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                                        | 1.5       | —                                                                                                                                                                                     | -         | V    |                                           |  |

| D003                                                 | VPOR                                                          | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal                                                                    | _         | —                                                                                                                                                                                     | 0.7       | V    | See section on Power-on Reset for details |  |

| D004                                                 | Svdd                                                          | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal                                                                 | 0.05      | —                                                                                                                                                                                     | _         | V/ms | See section on Power-on Reset for details |  |

| D005                                                 | VBOR                                                          | Brown-out Reset Voltage                                                                                                             | _         |                                                                                                                                                                                       |           |      |                                           |  |

|                                                      |                                                               | BORV1:BORV0 = 11                                                                                                                    | N/A       |                                                                                                                                                                                       | N/A       | V    | Reserved                                  |  |

|                                                      |                                                               | BORV1:BORV0 = 10                                                                                                                    | 2.64      | _                                                                                                                                                                                     | 2.92      | V    |                                           |  |

|                                                      |                                                               | BORV1:BORV0 = 01                                                                                                                    | 4.11      | _                                                                                                                                                                                     | 4.55      | V    |                                           |  |

|                                                      |                                                               | BORV1:BORV0 = 00                                                                                                                    | 4.41      |                                                                                                                                                                                       | 4.87      | V    |                                           |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

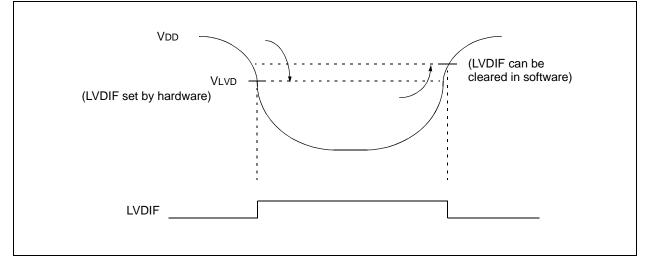

### FIGURE 26-5: LOW-VOLTAGE DETECT CHARACTERISTICS

### TABLE 26-3: LOW-VOLTAGE DETECT CHARACTERISTICS

### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $~-40^\circ C \le TA \le +85^\circ C$  for industrial  $-40^\circ C ~\le TA \le +125^\circ C$  for extended

| Param<br>No. | Symbol | Characteristic         |              | Min  | Тур† | Max  | Units | Conditions |

|--------------|--------|------------------------|--------------|------|------|------|-------|------------|

| D420         |        | LVD Voltage on VDD     | LVV = 0001   | 1.96 | 2.06 | 2.16 | V     |            |

|              |        | Transition high-to-low | LVV = 0010   | 2.16 | 2.27 | 2.38 | V     |            |

|              |        |                        | LVV = 0011   | 2.35 | 2.47 | 2.59 | V     |            |

|              |        |                        | LVV = 0100   | 2.45 | 2.58 | 2.71 | V     |            |

|              |        |                        | LVV = 0101   | 2.64 | 2.78 | 2.92 | V     |            |

|              |        |                        | LVV = 0110   | 2.75 | 2.89 | 3.03 | V     |            |

|              |        |                        | LVV = 0111   | 2.95 | 3.1  | 3.26 | V     |            |

|              |        |                        | LVV = 1000   | 3.24 | 3.41 | 3.58 | V     |            |

|              |        |                        | LVV = 1001   | 3.43 | 3.61 | 3.79 | V     |            |

|              |        |                        | LVV = 1010   | 3.53 | 3.72 | 3.91 | V     |            |

|              |        |                        | LVV = 1011   | 3.72 | 3.92 | 4.12 | V     |            |

|              |        |                        | LVV = 1100   | 3.92 | 4.13 | 4.34 | V     |            |

|              |        |                        | LVV = 1101   | 4.11 | 4.33 | 4.55 | V     |            |

|              |        |                        | LVV = 1110   | 4.41 | 4.64 | 4.87 | V     |            |

| D423         | Vbg    | Band Gap Reference V   | oltage Value |      | 1.22 | —    | V     |            |

† Production tested at TAMB = 25°C. Specifications over temperature limits ensured by characterization.

### APPENDIX E: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN726, "PIC17CXXX to PIC18CXXX Migration*". This Application Note is available as Literature Number DS00726.

### Q

| <b>u</b>                                          |

|---------------------------------------------------|

| Q Clock                                           |

| R                                                 |

| RAM. See Data Memory                              |

|                                                   |

| RC Oscillator                                     |

| RCALL                                             |

| RCON Registers 101                                |

| RCSTA Register                                    |

| SPEN Bit 197                                      |

| Reader Response                                   |

| Register File                                     |

| Registers                                         |

| ADCON0 (A/D Control 0)                            |

| ADCON1 (A/D Control 1)                            |

| ADCON2 (A/D Control 2)                            |

|                                                   |

| CCPxCON (Capture/Compare/PWM Control)             |

| CMCON (Comparator Control)                        |

| CONFIG1H (Configuration 1 High)240                |

| CONFIG2H (Configuration 2 High)241                |

| CONFIG2L (Configuration 2 Low) 241                |

| CONFIG3H (Configuration 3 High)242                |

| CONFIG3L (Configuration 3 Low)                    |

| CONFIG3L (Configuration Byte)                     |

| CONFIG4L (Configuration 4 Low)                    |

| CONFIG5H (Configuration 5 High)                   |

|                                                   |

| CONFIG5L (Configuration 5 Low)                    |

| CONFIG6H (Configuration 6 High)247                |

| CONFIG6L (Configuration 6 Low) 246                |

| CONFIG7H (Configuration 7 High)249                |

| CONFIG7L (Configuration 7 Low)248                 |

| CVRCON (Comparator Voltage Reference Control) 229 |

| Device ID 1                                       |

| Device ID 2                                       |

| EECON1 (Data EEPROM Control 1)                    |

| INTCON (Interrupt Control)                        |

|                                                   |

| INTCON2 (Interrupt Control 2)                     |

| INTCON3 (Interrupt Control 3)                     |

| IPR1 (Peripheral Interrupt Priority 1)            |

| IPR2 (Peripheral Interrupt Priority 2)            |

| IPR3 (Peripheral Interrupt Priority 3)100         |

| LVDCON (Low-Voltage Detect Control)               |

| MEMCON (Memory Control)71                         |

| OSCCON                                            |

| PIE1 (Peripheral Interrupt Enable 1)              |

| PIE2 (Peripheral Interrupt Enable 2)              |

| PIE2 (Peripheral Interrupt Enable 3)              |

|                                                   |

| PIR1 (Peripheral Interrupt Request 1)             |

| PIR2 (Peripheral Interrupt Request 2)             |

| PIR3 (Peripheral Interrupt Request 3)             |

| PSPCON (Parallel Slave Port Control) Register 129 |

| RCON                                              |