Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFl

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | CPU32                                                                        |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 66MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, EIA-232, Ethernet, GPIO, HDLC, I <sup>2</sup> C, SMBus, SPI |

| Peripherals                | DMA, POR, WDT                                                                |

| Number of I/O              | 72                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | RREM                                                                         |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 24К х 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.25V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 208-TFBGA                                                                    |

| Supplier Device Package    | 208-BGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/fido1100bga208ir1        |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| List o | of Fig | ures                                               | 5  |

|--------|--------|----------------------------------------------------|----|

| List o | of Tab | bles                                               | 6  |

| 1.     | Over   | view                                               | 7  |

| 2.     | Featu  | ures                                               | 9  |

|        | 2.1    | Core CPU                                           | 10 |

|        | 2.2    | JTAG                                               | 10 |

|        | 2.3    | Internal Memory and Memory Management              | 11 |

|        | 2.4    | External Bus Interface                             | 12 |

|        | 2.5    | PMU/UIC/CPU DMA                                    | 12 |

|        | 2.6    | Internal Peripherals                               |    |

|        |        | 2.6.1 Timer Counter Units (TCU)                    |    |

|        |        | 2.6.2 Analog-to-Digital Converter (ADC)            | 14 |

|        |        | 2.6.3 Timers                                       |    |

|        | 2.7    | Power Control                                      | 14 |

| 3.     | Libra  | aries and Support Tools                            | 15 |

| 4.     | Pack   | aging, Pin Descriptions, and Physical Dimensions   | 16 |

|        | 4.1    | PQFP Package                                       | 17 |

|        |        | 4.1.1 PQFP Pinout                                  | 17 |

|        |        | 4.1.2 PQFP Physical Dimensions                     |    |

|        | 4.2    | BGA 10- by 10-mm Package                           | 25 |

|        |        | 4.2.1 BGA 10- by 10-mm Pinout                      |    |

|        |        | 4.2.2 BGA 10- by 10-mm Physical Package Dimensions | 33 |

|        | 4.3    | BGA 15- by 15-mm Package                           | 34 |

|        |        | 4.3.1 BGA 15- by 15-mm Pinout                      | 34 |

|        |        | 4.3.2 BGA 15- by 15-mm Physical Package Dimensions | 42 |

|        |        | 4.3.3 BGA 15- by 15-mm Signal Routing              | 43 |

|        | 4.4    | Power and Ground Signals                           | 45 |

| 5.     | Elect  | trical Characteristics                             | 47 |

| 6.     | Ther   | mal Characteristics                                | 49 |

| 7.     | Rese   | t                                                  | 52 |

|        | 7.1    | Overview                                           | 52 |

|        | 7.2    | Signal Considerations and Reset Timing             | 52 |

|        | 7.3    | Clock Signals                                      | 54 |

|        | 7.4    | Typical Clock Source Implementations               | 54 |

|        |        | 7.4.1 Normal or Driven Clock Source                | 54 |

|        |        | 7.4.2 Using an External Crystal                    | 54 |

|        | 7.5    | Off-Chip Component Value                           |    |

| 8.     | Signa  | als                                                |    |

|        | 8.1    | External Bus Operation                             | 57 |

|        |        | 8.1.1 Overview                                     | 57 |

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 3 of 83

|     | 8.2   | Genera      | al Setup and Hold Timing                                          | 57 |

|-----|-------|-------------|-------------------------------------------------------------------|----|

|     | 8.3   | Extern      | al Bus Timing                                                     | 58 |

| 9.  | Setu  | p and H     | old Timing                                                        | 59 |

|     | -     | 9.1.1       | External Bus Timing for a 32-Bit Transfer (without RDY_N)         | 61 |

|     |       | 9.1.2       | External Bus Timing for a 32-Bit Transfer (with RDY_N)            | 62 |

|     |       | 9.1.3       | External Bus Timing for 8-Bit/16-Bit Transfer (without RDY_N)     | 64 |

|     |       | 9.1.4       | External Bus Timing for 8-Bit/16-Bit Transfer (with RDY_N)        | 65 |

|     | 9.2   | <b>SDRA</b> | M Timing                                                          | 66 |

|     |       | 9.2.1       | SDRAM CAS Timing                                                  |    |

|     |       | 9.2.2       | SDRAM Row Activation Timing                                       | 67 |

|     |       | 9.2.3       | SDRAM Read Operation Timing                                       | 69 |

|     |       | 9.2.4       | SDRAM Read Burst Timing                                           | 69 |

|     |       | 9.2.5       | SDRAM Write Operation, Write Burst, Write-to-Write, and Write-to- |    |

|     |       |             | Precharge Timing                                                  | 70 |

| 10. | JTA   | G           |                                                                   | 74 |

|     | 10.1  | JTAG        | Scan Chain Debug Functionality                                    | 75 |

| 11. | Orde  | ering Inf   | formation                                                         | 77 |

| 12. | Errat | ta          |                                                                   | 78 |

|     | 12.1  | Summ        | ary                                                               | 78 |

|     |       |             | · · ·                                                             |    |

| 13. | Revi  | sion His    | story                                                             | 82 |

| 14. | For A | Additior    | al Information                                                    | 83 |

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 4 of 83

# 2. Features

The fido1100 communication controller's features include:

- 32-bit Core CPU

- CISC architecture optimized for real time

- CPU32+ (Motorola® 68000) instruction-set compatible

- Five hardware contexts, each with its own register set and interrupt vector table

- An 8- or 16-bit external bus interface with programmable chip selects

- 24 Kbytes of high-speed internal user SRAM

- 32 Kbytes of high-speed internal user-mappable Relocatable Rapid Execution Memory (RREM)

- A Memory Protection Unit (MPU)

- An SDRAM controller

- Flat, contiguous memory space

- Non-aligned memory access support

- Dedicated Peripheral Management Unit (PMU)

- Four Universal I/O Controllers (UICs) capable of supporting the following protocols:

- GPIO

- 10/100 Ethernet with flexible MAC Address Filtering schemes

- EIA-232

- CAN

- SPI

- I<sup>2</sup>C<sup>TM</sup> Bus

- SMBus

- HDLC

- Two channels of full-featured direct memory access (DMA) with deterministic arbitration

- Two Timer/Counter Units (TCU)

- A Watchdog timer, system timer, and context timers

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 9 of 83

- JTAG emulation and debug interface

- Available in a 208-pin PQFP, BGA 10- by 10-mm package, and BGA 15- by 15-mm package

- 3.3V operation with 5V-tolerant I/O

- Industrial temperature grade

- Software development supported by libraries and tools including UIC firmware for various interface protocols and formats, as well as a customized GNU tool set.

#### 2.1 Core CPU

The fido1100 core is based on the CPU32 architecture, and is compatible with the CPU32 instruction set. The fido1100 incorporates five independent hardware contexts. While all contexts share the same Execution Unit, each of the five hardware contexts in the fido1100 has its own register set, execution priority and exception vector table. From an application's view, this unique feature of the fido1100 allows it to operate as five independent machines in one:

- 32-bit address and data paths on-chip

- 66-MHz operation

- Instruction execution from external memory or fast internal memory.

- Each hardware context has its own copy of:

- Eight 32-bit User Data Registers (D0-D7)

- Seven 32-bit Address Registers (A0-A6)

- Two 32-bit Stack Pointers (A7 and A7')

- One 32-bit Program Counter

- One 16-bit Status Register (SR)

- One 32-bit Vector Base Register (VBR)

### 2.2 JTAG

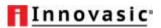

The fido1100 is fully compliant with the IEEE 1149.1 Test Access Port and Boundary-Scan architecture (see Table 2). The fido1100 architecture is equipped with the TAP (Test Access Port) interface, TAP controller, instruction register, instruction decoder, boundary-scan register, and by-pass register.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 10 of 83

# 3. Libraries and Support Tools

- Full library support

- UIC libraries

- Embedded communication stacks

- TCP/IP

- GPIO sample programs

- Customized GNU tool set

- Eclipse IDE

- Sourcery G++ from Code Sourcery

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 15 of 83

# 4. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions for the fido1100 communication controller PQFP, BGA 10- by 10-mm package, and BGA 15- by 15-mm package is provided individually. Refer to sections, figures, and tables for information on the device of interest.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 16 of 83

| Pin | Signal Name | Туре          | Description                                        |

|-----|-------------|---------------|----------------------------------------------------|

| 36  | D12         | Bidirectional | External Bus Interface data Bit [12]               |

| 37  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| 38  | D13         | Bidirectional | External Bus Interface data Bit [13]               |

| 39  | D14         | Bidirectional | External Bus Interface data Bit [14]               |

| 40  | D15         | Bidirectional | External Bus Interface data Bit [15]               |

| 41  | RDY_N       | Input         | External Bus Interface External Ready Indication   |

| 42  | GND         | Ground        | Digital ground                                     |

| 43  | MEMCLK      | Output        | Memory clock used by external memory               |

| 44  | GND         | Ground        | Digital ground                                     |

| 45  | BE0_N       | Output        | Byte enable 0, active low                          |

| 46  | BE1_N       | Output        | Byte enable 1, active low                          |

| 47  | OE_N        | Output        | Output enable, active low                          |

| 48  | VDDC        | Power         | Digital core supply voltage (+2.5VDC)              |

| 49  | RW_N        | Output        | Read or write control (active low write)           |

| 50  | BA_0        | Output        | Bank Enable 0                                      |

| 51  | BA_1        | Output        | Bank Enable 1                                      |

| 52  | CAS_N       | Output        | Column activate signal, active low                 |

| 53  | GND         | Ground        | Digital Ground                                     |

| 54  | RAS_N       | Output        | Row activate signal, active low                    |

| 55  | CKE         | Output        | Clock enable to be used in conjunction with MEMCLK |

| 56  | HOLDREQ_N   | Input         | External Bus hold request, active low              |

| 57  | HOLDGNT_N   | Output        | External Bus grant request, active low             |

| 58  | RESET_N     | Input         | Reset input                                        |

| 59  | RESET_OUT_N | Output        | Reset output                                       |

| 60  | GND         | Ground        | Digital ground                                     |

| 61  | A0          | Output        | External Bus Interface address Bit [0]             |

| 62  | A1          | Output        | External Bus Interface address Bit [1]             |

| 63  | A2          | Output        | External Bus Interface address Bit [2]             |

| 64  | A3          | Output        | External Bus Interface address Bit [3]             |

| 65  | VDDIO       | Power         | Digital I/O supply voltage (+3.3VDC)               |

| 66  | A4          | Output        | External Bus Interface address Bit [4]             |

| 67  | A5          | Output        | External Bus Interface address Bit [5]             |

| 68  | A6          | Output        | External Bus Interface address Bit [6]             |

| 69  | A7          | Output        | External Bus Interface address Bit [7]             |

| 70  | GND         | Ground        | Digital ground                                     |

| 71  | A8          | Output        | External Bus Interface address Bit [8]             |

| 72  | A9          | Output        | External Bus Interface address Bit [9]             |

| 73  | A10         | Output        | External Bus Interface address Bit [10]            |

| 74  | A11         | Output        | External Bus Interface address Bit [11]            |

# Table 3. PQFP Pin Listing (Continued)

### 4.2 BGA 10- by 10-mm Package

#### 4.2.1 BGA 10- by 10-mm Pinout

The pinout for the fido1100<sup>™</sup> communication controller BGA 10- by 10-mm package is as shown in Figure 4. The corresponding pinout is provided in Table 4.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 25 of 83 http://www.innovasic.com Customer Support: 1-888-824-4184

| Pin | Signal Name | Туре          | Description                                                         |

|-----|-------------|---------------|---------------------------------------------------------------------|

| B10 | UIC3_6      | Bidirectional | Universal I/O Controller 3 pin 6                                    |

| C9  | UIC3_7      | Bidirectional | Universal I/O Controller 3 pin 7                                    |

| A10 | UIC3_8      | Bidirectional | Universal I/O Controller 3 pin 8                                    |

| C8  | UIC3_9      | Bidirectional | Universal I/O Controller 3 pin 9                                    |

| B9  | UIC3_10     | Bidirectional | Universal I/O Controller 3 pin 10                                   |

| A9  | UIC3_11     | Bidirectional | Universal I/O Controller 3 pin 11                                   |

| C7  | UIC3_12     | Bidirectional | Universal I/O Controller 3 pin 12                                   |

| B8  | UIC3_13     | Bidirectional | Universal I/O Controller 3 pin 13                                   |

| A8  | GND         | Ground        | Digital Ground                                                      |

| C6  | UIC3_14     | Bidirectional | Universal I/O Controller 3 pin 14                                   |

| B7  | UIC3_15     | Bidirectional | Universal I/O Controller 3 pin 15                                   |

| A7  | UIC3_16     | Bidirectional | Universal I/O Controller 3 pin 16                                   |

| B6  | UIC3_17     | Bidirectional | Universal I/O Controller 3 pin 17                                   |

| A6  | T0IC0_T0OC0 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 0 or output compare 0 |

| C5  | T0IC1_T0OC1 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 1 or output compare 1 |

| B5  | T0IC2_T0OC2 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 2 or output compare 2 |

| A5  | T0IC3_T0OC3 | Bidirectional | Muxed pin, Timer Counter Unit 0 input capture 3 or output compare 3 |

| M8  | GND         | Ground        | Digital ground                                                      |

| C4  | T1IC0_T1OC0 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 0 or output compare 0 |

| B4  | T1IC1_T1OC1 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 1 or output compare 1 |

| A4  | T1IC2_T1OC2 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 2 or output compare 2 |

| B3  | T1IC3_T1OC3 | Bidirectional | Muxed pin, Timer Counter Unit 1 input capture 3 or output compare 3 |

| L7  | VDDC        | Power         | Digital core supply voltage (+2.5VDC)                               |

| A3  | TOIN        | Input         | Timer Counter Unit 0 external clock source                          |

| A2  | T1IN        | Input         | Timer Counter Unit 1 external clock source                          |

| M9  | GND         | Ground        | Digital Ground                                                      |

| J7  | VDDC        | Power         | Digital core supply voltage (+2.5VDC)                               |

## Table 4. BGA 10- by 10-mm Pin Listing (Continued)

### 4.3 BGA 15- by 15-mm Package

#### 4.3.1 BGA 15- by 15-mm Pinout

The pinout for the fido1100<sup>™</sup> communication controller BGA 15- by 15-mm package is as shown in Figure 6. The corresponding pinout is provided in Table 5.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 34 of 83 http://www.innovasic.com Customer Support: 1-888-824-4184

| Pin | Signal Name | Туре     | Description                                                                                     |

|-----|-------------|----------|-------------------------------------------------------------------------------------------------|

| Т8  | A11         | Output   | External Bus Interface address Bit [11]                                                         |

| D9  | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                           |

| U8  | A12         | Output   | External Bus Interface address Bit [12]                                                         |

| U9  | A13         | Output   | External Bus Interface address Bit [13]                                                         |

| Т9  | A14         | Output   | External Bus Interface address Bit [14]                                                         |

| R9  | A15         | Output   | External Bus Interface address Bit [15]                                                         |

| H4  | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                           |

| U10 | A16         | Output   | External Bus Interface address Bit [16]                                                         |

| T10 | A17         | Output   | External Bus Interface address Bit [17]                                                         |

| R10 | A18         | Output   | External Bus Interface address Bit [18]                                                         |

| U11 | A19         | Output   | External Bus Interface address Bit [19]                                                         |

| G14 | VDDIO       | Power    | Digital I/O supply voltage (+3.3VDC)                                                            |

| T11 | A20         | Output   | External Bus Interface address Bit [20]                                                         |

| P11 | A21         | Output   | External Bus Interface address Bit [21]                                                         |

| R11 | A22         | Output   | External Bus Interface address Bit [22]                                                         |

| U12 | A23         | Output   | External Bus Interface address Bit [23]                                                         |

| E4  | GND         | Ground   | Digital ground                                                                                  |

| T12 | A24         | Output   | External Bus Interface address Bit [24]                                                         |

| U13 | A_25_RESET_ | Internal | Muxed pin, External Bus Interface address Bit [25] or POR                                       |

|     | DELAY       | Pull-up  | counter bypass                                                                                  |

| P12 | A_26_SIZE   | Internal | Muxed pin, External Bus Interface address Bit [26] or data bus                                  |

|     |             | Pull-up  | size select (0 = 8-Bit, 1= 16=Bit)                                                              |

| R12 | A27_CS7_N   | Output   | Muxed pin, External Bus Interface address Bit [27] or Chip select 7 (chip select active low)    |

| T13 | A28_CS6_N   | Output   | Muxed pin, External Bus Interface address Bit [28] or Chip select 6 (chip select active low)    |

| R13 | A29_CS5_N   | Output   | Muxed pin, External Bus Interface address Bit [29] or Chip                                      |

| U14 | A30_CS4_N   | Output   | select 5 (chip select active low)<br>Muxed pin, External Bus Interface address Bit [30] or Chip |

| 014 | A30_C34_N   | Output   | select 4 (chip select active low)                                                               |

| T14 | CS0_N       | Output   | Chip select 0 (chip select active low)                                                          |

| T15 | CS1_N       | Output   | Chip select 1 (chip select active low)                                                          |

| R15 | CS2_N       | Output   | Chip select 2 (chip select active low)                                                          |

| R14 | CS3_N       | Output   | Chip select 3 (chip select active low)                                                          |

| U15 | TDI         | Input    | JTAG data input                                                                                 |

| U16 | TDO         | Output   | JTAG data output                                                                                |

| T16 | TCK         | Input    | JTAG clock input                                                                                |

| U17 | TMS         | Input    | JTAG control signal                                                                             |

| K14 | VDDC        | Power    | Digital core supply voltage (+2.5VDC)                                                           |

# Table 5. BGA 15- by 15-mm Package Pin Listing (Continued)

## 4.3.3 BGA 15- by 15-mm Signal Routing

The 15- by15-mm BGA can be easily routed using economical and readily available PCB fabrication design rules. In order to route all signals from the fido1100 BGA, 2 layers in addition to power and ground are required, using 0.1mm trace/space technology. Since 0.1mm = 3.937mil, most PCB fabricators will consider this 4mil trace/space.

The PCB land pattern for the BGA should use 0.3mm round pads. Since the BGA pitch is 0.8mm, this leaves 0.5mm of space between pads. Using 0.1mm trace/space, 2 signals may be routed between each pair of pads (2 traces + 3spaces = 0.5mm). Figure 8 shows how this is accomplished.

Referring to Figure 8, signal layer 1 is shown in black, signal layer 2 is shown in red, and the vias are shown in blue. Signal layer 1 is the top side with the BGA pads, while signal layer 2 may be any other layer, but is typically the bottom side. All vias with no trace routed out from the BGA are power or ground.

Note that the innermost row of pads is all power and ground, except for 9 pads which are signals. Three of these signals are easily routed on signal layer 1, but 6 of them require the use of vias and signal layer 2. If all of the signals are not required for a given design, it may be possible to route all of the used signals on signal layer 1.

It may be beneficial to place more vias and to route more signals on layers other than signal layer 1. This could produce a better PCB layout, but care should be exercised to not include an excessive number of vias. The use of too many vias can lead to inadequate copper on the power/ground plane layers surrounding the center area of the BGA, resulting in relative isolation of the BGA power/ground via connections.

Note the open space between pads M17 and N17 (A1 is upper left corner). These signals are XTAL1 and XTAL0. It is best not to route other signals between these pads, especially if a crystal is used for the clock source.

The power connections to the inner ring of pads have 4 vias for +3.3V and 4 vias for +2.5V. The use of a single bypass capacitor for each via, and alternating 0.1uF and 0.01uF values on each supply, provide reasonable bypass capacitance for the fido1100. Using 8 capacitors in this manner allows the use of capacitors in the 0603 package for economical PCB assembly.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 43 of 83

# 5. Electrical Characteristics

Tables 11, 12, 13, 14, and 15 show the absolute maximum ratings, ESD and latch-up characteristics, recommended operating conditions, DC characteristics, and input impedance, respectively.

### Table 11. Absolute Maximum Ratings

| Symbol            | Parameter Name                              | Conditions | Min  | Тур | Max  | Units |

|-------------------|---------------------------------------------|------------|------|-----|------|-------|

| V <sub>DDC</sub>  | Digital core supply voltage                 | -          | -0.3 | _   | 3.05 | V     |

| V <sub>DDIO</sub> | Digital I/O supply voltage                  | -          | -0.3 | -   | 5.5  | V     |

| V <sub>AIN</sub>  | Analog input voltage with respect to ground | -          | -0.3 | _   | 3.9  | V     |

| T <sub>A</sub>    | Ambient temperature                         | _          | -40  | -   | +85  | °C    |

| Τ <sub>s</sub>    | Storage temperature                         | -          | -55  | _   | +150 | °C    |

Note: Operation of the fido1100 outside of maximum operating ratings may result in failure of the device.

#### Table 12. ESD and Latch-Up Characteristics

| Symbol            | Parameter Name            | Conditions | Min  | Тур | Max | Units |

|-------------------|---------------------------|------------|------|-----|-----|-------|

| V <sub>HBM</sub>  | Human body model          | -          | 2000 | -   | _   | V     |

| V <sub>MM</sub>   | Machine model             | -          | 200  | -   | _   | V     |

| I <sub>LATP</sub> | Positive latch-up current | _          | -    | -   | 50  | μA    |

| I <sub>LATN</sub> | Negative latch-up current | _          | _    | _   | -50 | μA    |

### Table 13. Recommended Operating Conditions

| Symbol            | Parameter Name                  | Conditions | Min  | Тур | Max  | Units |

|-------------------|---------------------------------|------------|------|-----|------|-------|

| $V_{DDC}$         | Digital core supply voltage     | —          | 2.25 | 2.5 | 2.75 | V     |

| V <sub>DDIO</sub> | Digital I/O supply voltage      | —          | 3.0  | 3.3 | 3.6  | V     |

| f <sub>XTAL</sub> | Crystal frequency               | -          | -    | -   | 66   | MHz   |

| T <sub>A</sub>    | Ambient temperature             | -          | -40  | -   | +85  | О°    |

| $V_{DDA}$         | Analog supply voltage           | -          | 3.0  | 3.3 | 3.6  | V     |

| V <sub>RH</sub>   | ADC reference voltage—high      | -          | -    | 3.0 | _    | V     |

| V <sub>RL</sub>   | ADC reference voltage—low       | —          | -    | 0   | -    | V     |

| CL                | Digital output load capacitance | See note   | -    | 3.1 | -    | pF    |

Note: This parameter is guaranteed by design and not tested in production.

The following multiplexed signals are tri-stated during reset and should be pulled high if being used as chip selects or pulled low if being used as address lines (the fido1100 boots at address 0x00000000). If not being used, they can be pulled either high or low.

- A27\_CS7\_N

- A28\_CS6\_N

- A29\_CS5\_N

- A30\_CS4\_N

At Reset, the CS0\_N signal defaults to low for external memory access, supporting the boot sequence from address 0x00000000.

# 7.3 Clock Signals

## 7.4 Typical Clock Source Implementations

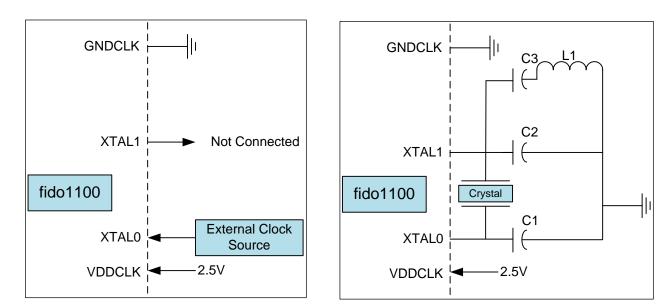

The fido1100 can operate in one of two modes: (1) Normal or driven clock source input or (2) using an external crystal to set the operating frequency of the internal oscillator.

*Note:* VDDCLK and GNDCLK must be connected even when not using an external crystal.

### 7.4.1 Normal or Driven Clock Source

System configuration—Drive external clock source into XTAL0 (see Figure 11). XTAL1 is left unconnected. XTAL0 is effectively a Schmitt trigger input. Target frequency should have a duty cycle of approximately 40% to 60%.

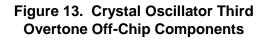

# 7.4.2 Using an External Crystal

- System Configuration (third overtone)—Crystal across XTAL0/XTAL1 (see Figure 12), 36 pF load caps to ground, 0.1-μF cap, and 0.33-μH inductor in series from XTAL1 to ground.

- System Configuration (fundamental tone)—Crystal across XTAL0/XTAL1 (see Figure 13) and 20-pF load caps to ground.

*Note:* Load capacitor and inductor values may be different based on crystal used. Please consult with your crystal supplier for more information.

Third overtone configuration is recommended for 24- to 66-MHz operation and fundamental tone configuration is recommended for 1- to 24-MHz operation.

## Figure 12. Driven Clock Source

#### Figure 14. Crystal Oscillator Fundamental Overtone Off-Chip Components

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 55 of 83 http://www.innovasic.com Customer Support: 1-888-824-4184

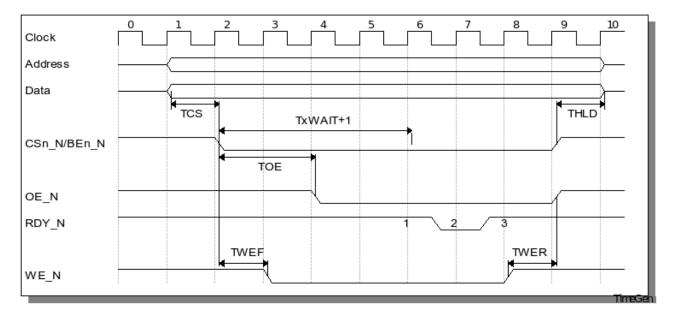

#### 8.3 External Bus Timing

Signals listed on the External Bus Timing diagrams are described below.

- TwWAIT

- If RDY\_ENABLE=0, specifies the width of the chip select active period for the nonburst-mode write cycle. The allowed range is 0–31, resulting in a wait time of 1–32 clocks.

- If RDY\_ENABLE=1, specifies the wait time before the RDY\_N line is first sampled for the write cycle. This provides a max wait time of 484 nS at 66 MHz. Anything greater than this will require the external RDY\_N line and external logic.

- TrWAIT

- If RDY\_ENABLE=0, specifies the width of the chip select active period for the nonburst-mode read cycle. The allowed range is 0–31, resulting in a wait time of 1–32 clocks.

- If RDY\_ENABLE=1, specifies the wait time before the RDY\_N line is first sampled for the read cycle. This provides a max wait time of 484 nS at 66 MHz. Anything greater than this will require the external RDY\_N line and external logic.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 58 of 83

- The output-enable signal (OE\_N) goes active (low) 0–3 clocks (TOE) after the chip select.

- The output-enable signal (OE\_N) goes inactive (hi) coincident with the chip select. This is also when the read data is sampled.

- The write-enable signal (WE\_N) goes active (low) 0–3 clocks (TWEF) after the chip select.

- The write-enable signal (WE\_N) goes inactive (hi) 0–3 clocks (TWER) before the end of the cycle (CSn\_N is removed).

# 9.1.4 External Bus Timing for 8-Bit/16-Bit Transfer (with RDY\_N)

This timing is programmable via the External Bus Chip Select Control Register (see Figure 23).

- The write-cycle timing is controlled by TwWAIT setting (shown as TxWAIT in the diagram), 1–16 clocks.

- The read-cycle timing is controlled by TrWAIT setting (shown as TxWAIT in the diagram), 1–16 clocks.

- The TxWAIT setting determines when first to start sampling the low active RDY\_N line (labeled with an arrow marked "1" in the diagram).

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 65 of 83

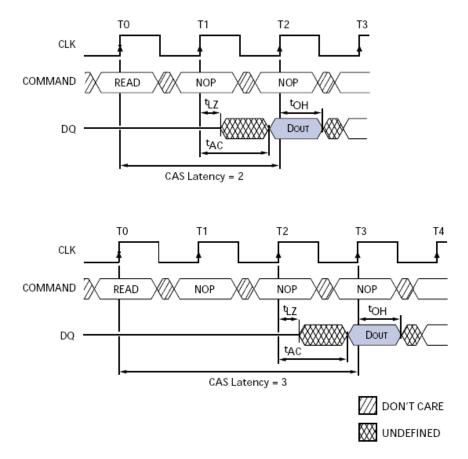

Figure 25. SDRAM CAS Timing

# 9.2.2 SDRAM Row Activation Timing

Before any READ or WRITE commands can be issued to a bank within the SDRAM, a row in that bank must be "opened." This is accomplished via the ACTIVE command, which selects both the bank and the row to be activated (see Figure 25). After opening a row (issuing an ACTIVE command), a READ or WRITE command may be issued to that row, subject to the tRCD specification. The tRCD (MIN) should be divided by the clock period and rounded up to the next whole number to determine the earliest clock edge after the ACTIVE command on which a READ or WRITE command can be entered. For example, a tRCD specification of 20ns with a 125-MHz clock (8-ns period) results in 2.5 clocks, rounded to 3. This is reflected in Figure 26, which covers any case where 2 < tRCD (MIN)/tCK  $\leq 3$ . (The same procedure is used to convert other specification limits from time units to clock cycles.)

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 67 of 83 http://www.innovasic.com Customer Support: 1-888-824-4184

# Figure 35. JTAG Port Register Interface

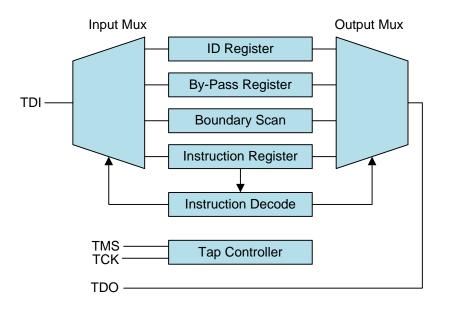

The timing of the JTAG signals is shown in Figure 35. The TDO pin remains in the high impedance state except during a shift-DR or shift-IR controller state. In the shift-DR and shift-IR controller states, TDO is updated on the falling edge of TCK. TMS and TDI are sampled on the rising edge of TCK.

Figure 36. Timing of JTAG Signals

# 10.1 JTAG Scan Chain Debug Functionality

The JTAG port contains an 8-bit-wide instruction register. Instructions are transferred to this register during the shift-IR state of the TAP state machine and are decoded by entering the Update-IR state of the TAP. The JTAG controller executes the last decoded instruction until another new one is entered and decoded. The instructions and data are entered serially through the TDI pin, LSB first.

The JTAG Test Access Port (TAP) instruction shift register will support the debug scan chain commands shown in Table 23.

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 75 of 83

| JTAG        | Coop Chain Function                                                                                              | Scan<br>Chain        | Scan Chain<br>Reference | Public or |

|-------------|------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|-----------|

| Instruction | Scan Chain Function                                                                                              | Length               | Number                  | Private   |

| 00010000    | READWRITEADDRCMD (Read/Write<br>Memory/Registers Address and Command)                                            | 37 bits              | 1                       | Private   |

| 00010001    | READDATA (Read Memory/Registers Data)                                                                            | 32 bits              | 2                       | Private   |

| 00010010    | WRITEDATA (Write Memory/Registers Data)                                                                          | 32 bits              | 7                       | Private   |

| 00010011    | READPC_ANDCONTEXT (Read Program<br>Counter and Active context)                                                   | 37 bits              | 4                       | Private   |

| 00010100    | READWRITEDRBUGREG (Read/Write Debug<br>Control Register)                                                         | 15 bits              | 5                       | Private   |

| 11111110    | IDCODE (Read Device ID Register)                                                                                 | 32 bits              | 3                       | Public    |

| 11111000    | EXTEST (IO Boundary Scan)                                                                                        | n bits<br>(I/O Pins) | 6                       | Public    |

| 11111010    | SAMPLE/PRELOAD (Sample Boundary Scan chain on "Capture-DR" state, Load Boundary Scan chain on 'Update-DR' state) | N bits<br>(I/O Pins) | 6                       | Public    |

| 11111111    | BYPASS (Use TDI/TDO Bypass Register)                                                                             | 1 bit                | 9                       | Public    |

| 00000111    | RUNBIST (Run Built in Self Test)                                                                                 | 16 bits              | 8                       | Public    |

| 00001111    | ENABLEATPG (Enable ATPG Mode for<br>Manufacturing Test)                                                          | N/A                  | N/A                     | Private   |

#### Table 23. Debug Scan Chain Commands Supported by the JTAG TAP

Notes:

- 1. The boundary-scan scan chain is selected via the EXETEST, SAMPLE, and PRELOAD instructions.

- The SAMPLE and PRELOAD instructions have the SAME binary code. (They are identified as separate instructions in the JTAG Spec, but are allowed to have the same binary code for backwards compatibility with previous version of spec.)

- 3. Any undefined bit pattern that is shifted into the Instruction Register will perform the same function as the BYPASS instruction.

- 4. On Power-on Reset, or when the JTAG state machine enters the "Test Logic Reset" the instruction register will reset its value to operate as the IDCODE Instruction (per JTAG Spec).

IA211080807-08 UNCONTROLLED WHEN PRINTED OR COPIED Page 76 of 83