Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26j53-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                 | Pin Nu                     | ımber             |             |                        |                                                                                  |  |  |

|---------------------------------|----------------------------|-------------------|-------------|------------------------|----------------------------------------------------------------------------------|--|--|

| Pin Name                        | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN            | Pin<br>Type | Buffer<br>Type         | Description                                                                      |  |  |

|                                 |                            |                   |             |                        | PORTB (continued)                                                                |  |  |

| RB4/CCP4/KBI0/SCK1/SCL1/        | 25 <sup>(2)</sup>          | 22 <sup>(2)</sup> |             |                        |                                                                                  |  |  |

| RP7                             |                            |                   |             |                        | Disting 1/0                                                                      |  |  |

| RB4<br>CCP4                     |                            |                   | 1/O<br>1/O  | TTL/DIG<br>ST/DIG      | Digital I/O.<br>Capture/Compare/PWM input/output.                                |  |  |

| KBIO                            |                            |                   | 1           | TTL                    | Interrupt-on-change pin.                                                         |  |  |

| SCK1                            |                            |                   | I/O         | ST/DIG                 | Synchronous serial clock input/output.                                           |  |  |

| SCL1                            |                            |                   | I/O         | I <sup>2</sup> C       | I <sup>2</sup> C clock input/output.                                             |  |  |

| RP7                             |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 7 input/output.                                        |  |  |

| RB5/CCP5/KBI1/SDI1/SDA1/<br>RP8 | 26 <sup>(2)</sup>          | 23 <sup>(2)</sup> |             |                        |                                                                                  |  |  |

| RB5                             |                            |                   | I/O         | TTL/DIG                | Digital I/O.                                                                     |  |  |

| CCP5                            |                            |                   | I/O         | ST/DIG                 | Capture/Compare/PWM input/output.                                                |  |  |

| KBI1                            |                            |                   | I           | TTL                    | Interrupt-on-change pin.                                                         |  |  |

| SDI1<br>SDA1                    |                            |                   | I<br>I/O    | ST<br>I <sup>2</sup> C | SPI data input.                                                                  |  |  |

| RP8                             |                            |                   | 1/O         | ST/DIG                 | l <sup>2</sup> C data input/output.<br>Remappable Peripheral Pin 8 input/output. |  |  |

| RB6/CCP6/KBI2/PGC/RP9           | 27 <b>(2)</b>              | 24 <b>(2)</b>     | "0          | 01/210                 |                                                                                  |  |  |

| RB6                             | 2/( )                      | 2417              | I/O         | TTL/DIG                | Digital I/O.                                                                     |  |  |

| CCP6                            |                            |                   | 1/O         | ST/DIG                 | Capture/Compare/PWM input/output.                                                |  |  |

| KBI2                            |                            |                   | Ι           | TTL                    | Interrupt-on-change pin.                                                         |  |  |

| PGC                             |                            |                   |             | ST                     | ICSP™ clock input.                                                               |  |  |

| RP9                             |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 9 input/output.                                        |  |  |

| RB7/CCP7/KBI3/PGD/RP10          | 28 <sup>(2)</sup>          | 25 <sup>(2)</sup> |             |                        |                                                                                  |  |  |

| RB7<br>CCP7                     |                            |                   | 1/O<br>1/O  | TTL/DIG<br>ST/DIG      | Digital I/O.<br>Capture/Compare/PWM input/output.                                |  |  |

| KBI3                            |                            |                   | 1/0         | TTL                    | Interrupt-on-change pin.                                                         |  |  |

| PGD                             |                            |                   | 1/O         | ST/DIG                 | In-Circuit Debugger and ICSP programming                                         |  |  |

|                                 |                            |                   |             |                        | data pin.                                                                        |  |  |

| RP10                            |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 10 input/output.                                       |  |  |

| Legend: TTL = TTL compat        |                            |                   | lovala      |                        | MOS = CMOS compatible input or output                                            |  |  |

| ST = Schmitt Trig<br>I = Input  | ger input wi               |                   | ieveis      | Ar<br>O                | nalog = Analog input<br>= Output                                                 |  |  |

| P = Power                       |                            |                   |             | Ō                      | D = Open-Drain (no P diode to VDD)                                               |  |  |

| DIG = Digital output            | ıt                         |                   |             | 1 <sup>2</sup> (       | $C = Open-Drain, I^2C specific$                                                  |  |  |

#### TABLE 1-3: PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV<2:0>) | Clock Mode<br>(FOSC<2:0>) | MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|-------------------------------|-------------------------------|---------------------------|------------------------------------|------------------------------------|

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | N1/A                          | 50                        | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | N/A                           | EC                        | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (000)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | ÷12 (000)                     | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (001)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 40 MHz                        | ÷10(001)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (00.0)                      | FORM                      | ÷2 (10)                            | 24 MHz                             |

| 24 MHz                        | ÷6(010)                       | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               | N/A                           |                           | None (11)                          | 24 MHz                             |

|                               |                               | EC <sup>(1)</sup>         | ÷2 (10)                            | 12 MHz                             |

| 24 MHz                        |                               |                           | ÷3 (01)                            | 8 MHz                              |

|                               |                               |                           | ÷6 (00)                            | 4 MHz                              |

|                               | ÷5 (011)                      |                           | None (11)                          | 48 MHz                             |

|                               |                               | 50511                     | ÷2 (10)                            | 24 MHz                             |

| 20 MHz                        |                               | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 16 MHz                        | ÷4 (100)                      | HSPLL, ECPLL              | ÷3 (01)                            | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (2.22.)                     |                           | ÷2 (10)                            | 24 MHz                             |

| 12 MHz                        | ÷3(101)                       | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 0.1411-                       | 0 (5 5 5)                     | HSPLL, ECPLL,             | ÷2 (10)                            | 24 MHz                             |

| 8 MHz                         | ÷2 (110)                      | INTOSCPLL/<br>INTOSCPLLO  | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 4.8411                        | 4 ()                          |                           | ÷2 (10)                            | 24 MHz                             |

| 4 MHz                         | ÷ <b>1</b> (111)              | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| <b>TABLE 3-5:</b> | OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION |

|-------------------|----------------------------------------------------|

|                   |                                                    |

Note 1: The 24 MHz EC mode (without PLL) is only compatible with low-speed USB. Full-speed USB requires a 48 MHz system clock.

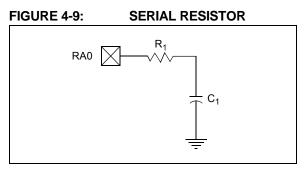

A series resistor between RA0 and the external capacitor provides overcurrent protection for the RA0/AN0/C1INA/ULPWU/RP0 pin and can allow for software calibration of the time-out (see Figure 4-9).

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The ULPWU peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

| Note: | For more information, refer to AN879, |

|-------|---------------------------------------|

|       | Using the Microchip Ultra Low-Power   |

|       | Wake-up Module application note       |

|       | (DS00879).                            |

#### 4.8 Peripheral Module Disable

All peripheral modules (except for I/O ports) also have a second control bit that can disable their functionality. These bits, known as the Peripheral Module Disable (PMDISx) bits, are generically named "xxxMD" (using "xxx" as the mnemonic version of the module's name).

These bits are located in the PMDISx Special Function Registers. In contrast to the module enable bits (generically named "xxxEN" and located in bit position seven of the control registers), the PMDISx bits must be set (= 1) to disable the modules.

While the PMD and module enable bits both disable a peripheral's functionality, the PMD bit completely shuts down the peripheral, effectively powering down all circuits and removing all clock sources. This has the additional effect of making any of the module's control and buffer registers, mapped in the SFR space, unavailable for operations. Essentially, the peripheral ceases to exist until the PMD bit is cleared.

This differs from using the module enable bit, which allows the peripheral to be reconfigured and buffer registers preloaded, even when the peripheral's operations are disabled.

The PMDISx bits are most useful in highly power-sensitive applications. In these cases, the bits can be set before the main body of the application to remove peripherals that will not be needed at all.

| Register | Bit 7                | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR |

|----------|----------------------|---------|---------|---------|---------|--------|--------|--------|----------------------|

| PMDIS3   | CCP10MD              | CCP9MD  | CCP8MD  | CCP7MD  | CCP6MD  | CCP5MD | CCP4MD | _      | 0000 000-            |

| PMDIS2   | —                    | TMR8MD  | _       | TMR6MD  | TMR5MD  | CMP3MD | CMP2MD | CMP1MD | -0-0 0000            |

| PMDIS1   | PSPMD <sup>(1)</sup> | CTMUMD  | RTCCMD  | TMR4MD  | TMR3MD  | TMR2MD | TMR1MD | _      | 0000 000-            |

| PMDIS0   | ECCP3MD              | ECCP2MD | ECCP1MD | UART2MD | UART1MD | SPI2MD | SPI1MD | ADCMD  | 0000 0000            |

#### TABLE 4-2: LOW-POWER MODE REGISTERS

Note 1: Not implemented on 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF27J53).

### 9.0 INTERRUPTS

Devices of the PIC18F47J53 family have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are 19 registers, which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4, PIR5

- PIE1, PIE2, PIE3, PIE4, PIE5

- IPR1, IPR2, IPR3, IPR4, IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address, 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

#### 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from Idle or Sleep mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-19: RCON: RESET CONTROL REGISTER (ACCESS FD0h)

| R/W-0 | U-0 | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-----|-------|-------|

| IPEN  | —   | CM    | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |       |       |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | <ul> <li>IPEN: Interrupt Priority Enable bit</li> <li>1 = Enable priority levels on interrupts</li> <li>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5 | CM: Configuration Mismatch Flag bit                                                                                                                                                         |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                                                              |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 3 | TO: Watchdog Timer Time-out Flag bit                                                                                                                                                        |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                                                                           |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 1 | POR: Power-on Reset Status bit                                                                                                                                                              |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                                                             |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

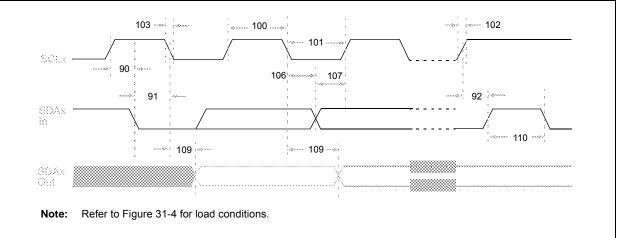

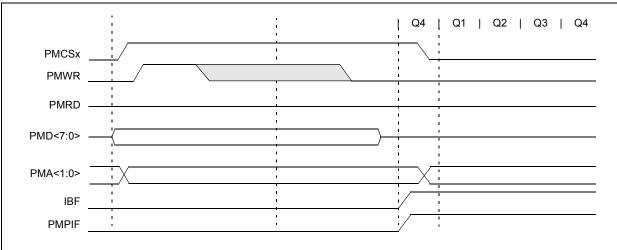

#### 11.2.5.2 WRITE TO SLAVE PORT

When chip select is active and a write strobe occurs (PMCSx = 1 and PMWR = 1), the data from PMD<7:0> is captured into one of the four input buffer bytes. Which byte is written depends on the 2-bit address placed on ADDRL<1:0>.

Table 11-1 provides the corresponding input registers and their associated address.

When an input buffer is written, the corresponding IBxF bit is set. The IBF flag bit is set when all the buffers are written. If any buffer is already written (IBxF = 1), the next write strobe to that buffer will generate an OBUF event and the byte will be discarded.

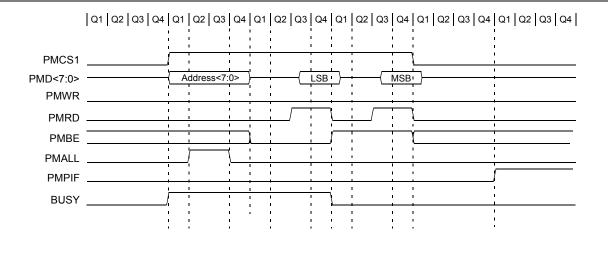

#### FIGURE 11-8: PARALLEL SLAVE PORT WRITE WAVEFORMS

# PIC18F47J53

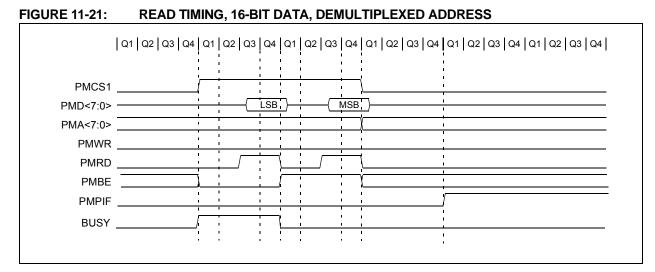

#### FIGURE 11-22: WRITE TIMING, 16-BIT DATA, DEMULTIPLEXED ADDRESS

|          | Q1 Q2 Q3 Q4 | Q1       | Q2 Q3       | Q4       | Q1          | Q2 Q3       | Q4 | Q1 Q2 Q3 Q4 | Q1   Q2   Q3   Q4   Q1   Q2   Q3   Q4 |

|----------|-------------|----------|-------------|----------|-------------|-------------|----|-------------|---------------------------------------|

|          |             | i<br>i   | 1           | 1<br>1   |             | 1<br>1      | 1  | 1<br>1      | 1<br>1                                |

| PMCS1    |             | <u></u>  | !<br>!      |          | 1           | :           |    | <u> </u>    | 1<br>1<br>1                           |

| PMD<7:0> |             |          | LSB         |          | (           | MSB         |    | <u>;</u>    |                                       |

| PMA<7:0> |             | 1        | 1           | 1        |             | r<br>1      |    | X           | r                                     |

| PMWR     |             | 1        |             | <u> </u> |             |             |    | 1           | 1<br>1<br>1                           |

| PMRD     |             | 1        |             |          | 1<br>1<br>1 |             |    |             |                                       |

| PMBE     |             | 7        | 1<br>1      |          | [           | r<br>1      |    | Υ           | I                                     |

| PMPIF    |             | 1<br>1   | 1<br>1<br>1 | 1<br>1   | 1<br>1      | 1<br>1      |    | 1<br>1      |                                       |

| BUSY     |             | <u> </u> |             |          | !<br>!      | ,<br>,<br>, |    | 1<br>1      |                                       |

|          |             |          | 1<br>1      |          |             | 1<br>1      |    | <br>        | ,<br>,<br>,                           |

#### FIGURE 11-23: READ TIMING, 16-BIT MULTIPLEXED DATA, PARTIALLY MULTIPLEXED ADDRESS

#### 13.2 Timer1 Operation

The Timer1 module is an 8-bit or 16-bit incrementing counter, which is accessed through the TMR1H:TMR1L register pair.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively.

When Timer1 is enabled, the RC1/CCP8/T1OSI/UOE/ RP12 and RC0/T1OSO/T1CKI/RP11 pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

#### 13.3 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Register 13-1 displays the clock source selections.

#### 13.3.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

#### 13.3.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input, T1CKI, or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR Reset

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0)

when T1CKI is high, then Timer1 is enabled (TMR1ON = 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                          |  |  |  |  |

|---------|---------|---------|---------------------------------------|--|--|--|--|

| 0       | 1       | х       | Clock Source (Fosc)                   |  |  |  |  |

| 0       | 0       | x       | Instruction Clock (Fosc/4)            |  |  |  |  |

| 1       | 0       | 0       | External Clock on T1CKI Pin           |  |  |  |  |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pin |  |  |  |  |

#### TABLE 13-1: TIMER1 CLOCK SOURCE SELECTION

| Name     | Bit 7                     | Bit 6          | Bit 5   | Bit 4    | Bit 3            | Bit 2   | Bit 1   | Bit 0   |  |  |

|----------|---------------------------|----------------|---------|----------|------------------|---------|---------|---------|--|--|

| INTCON   | GIE/GIEH                  | PEIE/GIEL      | TMR0IE  | INT0IE   | RBIE             | TMR0IF  | INT0IF  | RBIF    |  |  |

| PIR5     | _                         | _              | CM3IF   | TMR8IF   | TMR6IF           | TMR5IF  | TMR5GIF | TMR1GIF |  |  |

| PIE5     | _                         | _              | CM3IE   | TMR8IE   | TMR6IE           | TMR5IE  | TMR5GIE | TMR1GIE |  |  |

| PIR2     | OSCFIF                    | CM2IF          | CM1IF   | USBIF    | BCL1IF           | HLVDIF  | TMR3IF  | CCP2IF  |  |  |

| PIE2     | OSCFIE                    | CM2IE          | CM1IE   | USBIE    | BCL1IE           | HLVDIE  | TMR3IE  | CCP2IE  |  |  |

| TMR3H    | Timer3 Register High Byte |                |         |          |                  |         |         |         |  |  |

| TMR3L    | Timer3 Regi               | ster Low Byte  | ;       |          |                  |         |         |         |  |  |

| T3GCON   | TMR3GE                    | T3GPOL         | T3GTM   | T3GSPM   | T3GGO/<br>T3DONE | T3GVAL  | T3GSS1  | T3GSS0  |  |  |

| T3CON    | TMR3CS1                   | TMR3CS0        | T3CKPS1 | T3CKPS0  | T3OSCEN          | T3SYNC  | RD16    | TMR3ON  |  |  |

| TMR5H    | Timer5 Regi               | ster High Byte | e       |          |                  |         |         |         |  |  |

| TMR5L    | Timer5 Regi               | ster Low Byte  | 9       |          |                  |         |         |         |  |  |

| T5GCON   | TMR5GE                    | T5GPOL         | T5GTM   | T5GSPM   | T5GGO/<br>T5DONE | T5GVAL  | T5GSS1  | T5GSS0  |  |  |

| T5CON    | TMR5CS1                   | TMR5CS0        | T5CKPS1 | T5CKPS0  | T5OSCEN          | T5SYNC  | RD16    | TMR5ON  |  |  |

| OSCCON2  | _                         | SOSCRUN        |         | SOSCDRV  | SOSCGO           | PRISD   | _       |         |  |  |

| CCPTMRS0 | C3TSEL1                   | C3TSEL0        | C2TSEL2 | C2TSEL1  | C2TSEL0          | C1TSEL2 | C1TSEL1 | C1TSEL0 |  |  |

| CCPTMRS1 | C7TSEL1                   | C7TSEL0        | _       | C6TSEL0  | _                | C5TSEL0 | C4TSEL1 | C4TSEL0 |  |  |

| CCPTMRS1 | _                         | _              | _       | C10TSEL0 |                  | C9TSEL0 | C8TSEL1 | C8TSEL0 |  |  |

| CCPTMRS2 | _                         | _              | _       | C10TSEL0 | _                | C9TSEL0 | C8TSEL1 | C8TSEL0 |  |  |

|          |                           |                |         |          |                  |         |         |         |  |  |

#### TABLE 15-5: REGISTERS ASSOCIATED WITH TIMER3/5 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

#### 18.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP4IE bit (PIE4<1>) clear to avoid false interrupts and should clear the flag bit, CCP4IF, following any such change in operating mode.

#### 18.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCP4M<3:0>). Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Doing that also will not clear the prescaler counter – meaning the first capture may be from a non-zero prescaler.

Example 18-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 18-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       |             |   | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP4CON     | ; | Load CCP4CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

#### 18.3 Compare Mode

In Compare mode, the 16-bit CCPR4 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP4 pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP4M<3:0>). At the same time, the interrupt flag bit, CCP4IF, is set.

Figure 18-2 gives the Compare mode block diagram

#### 18.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP4CON register will force    |

|-------|---------------------------------------------|

|       | the RB4 compare output latch (depending     |

|       | on device configuration) to the default low |

|       | level. This is not the PORTB I/O data       |

|       | latch.                                      |

#### 18.3.2 TIMER1/3/5 MODE SELECTION

If the CCP module is using the compare feature in conjunction with any of the Timer1/3/5 timers, the timers must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the compare operation may not work.

```

Note: Details of the timer assignments for the CCP modules are given in Table 18-2 and Table 18-3.

```

#### 18.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP4M<3:0> = 1010), the CCP4 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP4IE bit is set.

#### 18.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP4M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable period register for either timer.

The Special Event Trigger for CCP4 cannot start an A/D conversion.

Note: The Special Event Trigger of ECCP1 can start an A/D conversion, but the A/D Converter must be enabled. For more information, see Section 19.0 "Enhanced Capture/Compare/PWM (ECCP) Module".

#### 18.4 PWM Mode

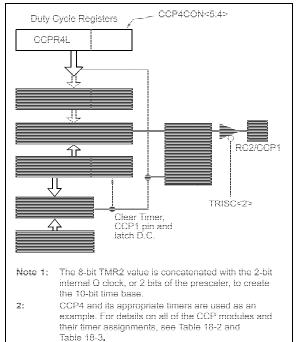

In Pulse-Width Modulation (PWM) mode, the CCP4 pin produces up to a 10-bit resolution PWM output. Since the CCP4 pin is multiplexed with a PORTB data latch, the appropriate TRIS bit must be cleared to make the CCP4 pin an output.

Figure 18-3 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 18.4.3** "Setup for PWM Operation".

FIGURE 18-3: SIMPLIFIED PWM BLOCK DIAGRAM

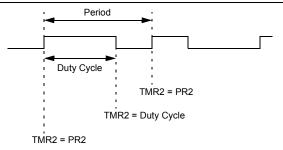

A PWM output (Figure 18-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 18-4: PWM OUTPUT

#### 18.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### **EQUATION 18-1:**

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP4 pin is set

(An exception: If the PWM duty cycle = 0%, the CCP4 pin will not be set)

The PWM duty cycle is latched from CCPR4L into CCPR4H

| Note: | The     | Timer2      | postscalers          | (see     |

|-------|---------|-------------|----------------------|----------|

|       | Sectio  | n 14.0 "Tin | ner2 Module") a      | are not  |

|       | used in | the determ  | ination of the PV    | /M fre-  |

|       | quency  | . The posts | caler could be u     | sed to   |

|       | have a  | servo upda  | te rate at a differe | ent fre- |

|       | quency  | than the P  | WM output.           |          |

#### 24.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode when enabled. Each operational comparator will consume additional current. To minimize power consumption while in Sleep mode, turn off the comparators (CON = 0) before entering Sleep. If the device wakes up from Sleep, the contents of the CMxCON register are not affected.

#### 24.8 Effects of a Reset

A device Reset forces the CMxCON registers to their Reset state. This forces both comparators and the voltage reference to the OFF state.

| Name   | Bit 7                          | Bit 6                           | Bit 5                          | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   |

|--------|--------------------------------|---------------------------------|--------------------------------|--------|--------|--------|---------|---------|

| INTCON | GIE/GIEH                       | PEIE/GIEL                       | TMR0IE                         | INT0IE | RBIE   | TMR0IF | INT0IF  | RBIF    |

| PIR2   | OSCFIF                         | CM2IF                           | CM1IF                          | USBIF  | BCL1IF | HLVDIF | TMR3IF  | CCP2IF  |

| PIR5   | —                              | —                               | CM3IF                          | TMR8IF | TMR6IF | TMR5IF | TMR5GIF | TMR1GIF |

| PIE2   | OSCFIE                         | CM2IE                           | CM1IE                          | USBIE  | BCL1IE | HLVDIE | TMR3IE  | CCP2IE  |

| PIE5   | —                              | —                               | CM3IE                          | TMR8IE | TMR6IE | TMR5IE | TMR5GIE | TMR1GIE |

| IPR2   | OSCFIP                         | CM2IP                           | CM1IP                          | USBIP  | BCL1IP | HLVDIP | TMR3IP  | CCP2IP  |

| IPR5   | —                              | _                               | CM3IP                          | TMR8IP | TMR6IP | TMR5IP | TMR5GIP | TMR1GIP |

| CMxCON | CON                            | COE                             | CPOL                           | EVPOL1 | EVPOL0 | CREF   | CCH1    | CCH0    |

| CVRCON | CVREN                          | CVROE                           | CVRR                           | CVRSS  | CVR3   | CVR2   | CVR1    | CVR0    |

| CMSTAT | —                              | _                               | _                              | _      | _      | COUT3  | COUT2   | COUT1   |

| ANCON0 | PCFG7 <sup>(Leg</sup><br>end:) | PCFG6 <sup>(Leg-</sup><br>end:) | PCFG5 <sup>(Le</sup><br>gend:) | PCFG4  | PCFG3  | PCFG2  | PCFG1   | PCFG0   |

| ANCON1 | VBGEN                          | _                               |                                | PCFG12 | PCFG11 | PCFG10 | PCFG9   | PCFG8   |

| TRISA  | TRISA7                         | TRISA6                          | TRISA5                         | _      | TRISA3 | TRISA2 | TRISA1  | TRISA0  |

TABLE 24-3: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are not related to comparator operation.

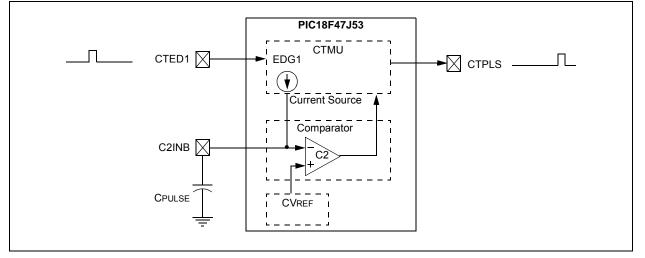

# 27.6 Creating a Delay with the CTMU Module

A unique feature on board the CTMU module is its ability to generate system clock, independent output pulses based on an external capacitor value. This is accomplished using the internal comparator voltage reference module, Comparator 2 input pin and an external capacitor. The pulse is output onto the CTPLS pin. To enable this mode, set the TGEN bit.

See Figure 27-4 for an example circuit. *C*PULSE is chosen by the user to determine the output pulse width on CTPLS. The pulse width is calculated by T = (CPULSE/I)\*V, where *I* is known from the current source measurement step (Section 27.3.1 "Current Source Calibration") and *V* is the internal reference voltage (CVREF).

An example use of this feature is for interfacing with variable capacitive-based sensors, such as a humidity sensor. As the humidity varies, the pulse width output on CTPLS will vary. The CTPLS output pin can be connected to an input capture pin and the varying pulse width is measured to determine the humidity in the application.

Follow these steps to use this feature:

- 1. Set the CPOL bit (CMxCON<5>).

- 2. Initialize the comparator voltage reference.

- 3. Initialize the CTMU and enable time delay generation by setting the TGEN bit.

- 4. Set EDG1STAT.

- 5. When CPULSE charges to the value of the voltage reference trip point, an output pulse is generated on CTPLS.

## FIGURE 27-4: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE DELAY GENERATION

#### 27.7 Operation During Sleep/Idle Modes

## 27.7.1 SLEEP MODE AND DEEP SLEEP MODES

When the device enters any Sleep mode, the CTMU module current source is always disabled. If the CTMU is performing an operation that depends on the current source when Sleep mode is invoked, the operation may not terminate correctly. Capacitance and time measurements may return erroneous values.

#### 27.7.2 IDLE MODE

The behavior of the CTMU in Idle mode is determined by the CTMUSIDL bit (CTMUCONH<5>). If CTMUSIDL is cleared, the module will continue to operate in Idle mode. If CTMUSIDL is set, the module's current source is disabled when the device enters Idle mode. In this case, if the module is performing an operation when Idle mode is invoked, the results will be similar to those with Sleep mode.

### 27.8 Effects of a Reset on CTMU

Upon Reset, all registers of the CTMU are cleared. This leaves the CTMU module disabled; its current source is turned off and all configuration options return to their default settings. The module needs to be re-initialized following any Reset.

If the CTMU is in the process of taking a measurement at the time of Reset, the measurement will be lost. A partial charge may exist on the circuit that was being measured, and should be properly discharged before the CTMU makes subsequent attempts to make a measurement. The circuit is discharged by setting and then clearing the IDISSEN bit (CTMUCONH<1>) while the A/D Converter is connected to the appropriate channel.

<sup>© 2009-2016</sup> Microchip Technology Inc.

# 28.0 SPECIAL FEATURES OF THE CPU

PIC18F47J53 family devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- · Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

- Two-Speed Start-up

- Code Protection

- In-Circuit Serial Programming (ICSP)

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet. In addition to their Power-up and Oscillator Start-up Timers provided for Resets, the PIC18F47J53 family of devices has a configurable Watchdog Timer (WDT), which is controlled in software.

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

#### 28.1 Configuration Bits

The Configuration bits can be programmed to select various device configurations. The configuration data is stored in the last four words of Flash program memory; Figure 6-1 depicts this. The configuration data gets loaded into the volatile Configuration registers, CON-FIG1L through CONFIG4H, which are readable and mapped to program memory, starting at location 300000h.

Table 28-2 provides a complete list. A detailed explanation of the various bit functions is provided in Register 28-1 through Register 28-6.

#### 28.1.1 CONSIDERATIONS FOR CONFIGURING THE PIC18F47J53 FAMILY DEVICES

Unlike some previous PIC18 microcontrollers, devices of the PIC18F47J53 family do not use persistent memory registers to store configuration information. The Configuration registers, CONFIG1L through CON-FIG4H, are implemented as volatile memory.

Immediately after power-up, or after a device Reset, the microcontroller hardware automatically loads the CONFIG1L through CONFIG4L registers with configuration data stored in nonvolatile Flash program memory. The last four words of Flash program memory, known as the Flash Configuration Words (FCW), are used to store the configuration data.

Table 28-1 provides the Flash program memory, which will be loaded into the corresponding Configuration register.

When creating applications for these devices, users should always specifically allocate the location of the FCW for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The four Most Significant bits (MSb) of the FCW, corresponding to CONFIG1H, CONFIG2H, CONFIG3H and CONFIG4H, should always be programmed to '1111'. This makes these FCWs appear to be NOP instructions in the remote event that their locations are ever executed by accident.

The four MSbs of the CONFIG1H, CONFIG2H, CON-FIG3H and CONFIG4H registers are not implemented, so writing '1's to their corresponding FCW has no effect on device operation.

To prevent inadvertent configuration changes during code execution, the Configuration registers, CON-FIG1L through CONFIG4L, are loaded only once per power-up or Reset cycle. User's firmware can still change the configuration by using self-reprogramming to modify the contents of the FCW.

Modifying the FCW will not change the active contents being used in the CONFIG1L through CONFIG4H registers until after the device is reset.

#### REGISTER 28-8: CONFIG4H: CONFIGURATION REGISTER 4 HIGH (BYTE ADDRESS 300007h)

| U-1   | U-1 | U-1 | U-1 | R/WO-1  | U-0 | R/WO-1 | R/WO-1 |

|-------|-----|-----|-----|---------|-----|--------|--------|

| —     | —   | —   | —   | LS48MHZ |     | WPEND  | WPDIS  |

| bit 7 |     |     |     |         |     |        | bit 0  |

| Legend:           |                     |                             |                    |

|-------------------|---------------------|-----------------------------|--------------------|

| R = Readable bit  | WO = Write-Once bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Program the corresponding Flash Configuration bit to '1'                                                                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | LS48MHZ: Low-Speed USB Clock Selection                                                                                                                                                                                                    |

|         | 1 = 48-MHz system clock is expected; divide-by-8 generates low-speed USB clock                                                                                                                                                            |

|         | 0 = 24-MHz system clock is expected; divide-by-4 generates low-speed USB clock                                                                                                                                                            |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                                |

| bit 1   | WPEND: Write-Protect Disable bit                                                                                                                                                                                                          |

|         | <ul> <li>1 = Flash pages, WPFP&lt;6:0&gt; to (Configuration Words page), are write/erase protected</li> <li>0 = Flash pages 0 to WPFP&lt;6:0&gt; are write/erase-protected</li> </ul>                                                     |

| bit 0   | WPDIS: Write-Protect Disable bit                                                                                                                                                                                                          |

|         | <ul> <li>1 = WPFP&lt;5:0&gt;, WPEND and WPCFG bits are ignored; all Flash memory may be erased or written</li> <li>0 = WPFP&lt;5:0&gt;, WPEND and WPCFG bits enabled; erase/write-protect is active for the selected region(s)</li> </ul> |

## REGISTER 28-9: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F47J53 FAMILY DEVICES (BYTE ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-5 DEV<2:0>: Device ID bits

These bits are used with DEV<10:3> bits in Device ID Register 2 to identify the part number. See Register 28-10.

bit 4-0 **REV<4:0>:** Revision ID bits These bits are used to indicate the device revision.

# PIC18F47J53

| DEC          | FSZ                  | Decrement                                                               | f, Skip if 0                                                                                                                                                                                                                                                                         |                                    |  |  |  |  |

|--------------|----------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| Synta        | ax:                  | DECFSZ f                                                                | {,d {,a}}                                                                                                                                                                                                                                                                            |                                    |  |  |  |  |

| Oper         | ands:                | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                     | $d \in [0,1]$                                                                                                                                                                                                                                                                        |                                    |  |  |  |  |

| Oper         | ation:               | .,                                                                      | $(f) - 1 \rightarrow dest,$<br>skip if result = 0                                                                                                                                                                                                                                    |                                    |  |  |  |  |

| Statu        | s Affected:          | None                                                                    | None                                                                                                                                                                                                                                                                                 |                                    |  |  |  |  |

| Enco         | ding:                | 0010                                                                    | 0010 11da ffff ffff                                                                                                                                                                                                                                                                  |                                    |  |  |  |  |

| Description: |                      | decremente<br>placed in W                                               | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).                                                                                                                 |                                    |  |  |  |  |

|              |                      | which is alre                                                           |                                                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

|              |                      |                                                                         | ne BSR is use                                                                                                                                                                                                                                                                        | nk is selected.<br>d to select the |  |  |  |  |

|              |                      | set is enable<br>in Indexed I<br>mode when<br>Section 29<br>Bit-Oriente | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 29.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                    |  |  |  |  |

| Word         | ls:                  | 1                                                                       | 1                                                                                                                                                                                                                                                                                    |                                    |  |  |  |  |

| Cycle        | es:                  | •                                                                       | cles if skip an<br>2-word instru                                                                                                                                                                                                                                                     |                                    |  |  |  |  |

| QC           | ycle Activity:       |                                                                         |                                                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

|              | Q1                   | Q2                                                                      | Q3                                                                                                                                                                                                                                                                                   | Q4                                 |  |  |  |  |

|              | Decode               | Read                                                                    | Process                                                                                                                                                                                                                                                                              | Write to                           |  |  |  |  |

| lf ok        | in:                  | register 'f'                                                            | Data                                                                                                                                                                                                                                                                                 | destination                        |  |  |  |  |

| lf sk        | ip.<br>Q1            | Q2                                                                      | Q3                                                                                                                                                                                                                                                                                   | Q4                                 |  |  |  |  |

|              | No                   | No                                                                      | No                                                                                                                                                                                                                                                                                   | No                                 |  |  |  |  |

|              | operation            | operation                                                               | operation                                                                                                                                                                                                                                                                            | operation                          |  |  |  |  |

| lf sk        | ip and followe       | d by 2-word ins                                                         | struction:                                                                                                                                                                                                                                                                           |                                    |  |  |  |  |

| i            | Q1                   | Q2                                                                      | Q3                                                                                                                                                                                                                                                                                   | Q4                                 |  |  |  |  |

|              | No                   | No                                                                      | No                                                                                                                                                                                                                                                                                   | No                                 |  |  |  |  |

|              | operation            | operation<br>No                                                         | operation                                                                                                                                                                                                                                                                            | operation                          |  |  |  |  |

|              | No<br>operation      | operation                                                               | No<br>operation                                                                                                                                                                                                                                                                      | No<br>operation                    |  |  |  |  |

| I            |                      |                                                                         |                                                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

| <u>Exan</u>  | nple:                | HERE                                                                    | DECFSZ<br>GOTO                                                                                                                                                                                                                                                                       | CNT, 1, 1<br>LOOP                  |  |  |  |  |

|              | Doforo Instruc       | CONTINUE                                                                |                                                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

|              | Before Instruc<br>PC | = Address                                                               | (HERE)                                                                                                                                                                                                                                                                               |                                    |  |  |  |  |

|              | After Instruction    |                                                                         | . (                                                                                                                                                                                                                                                                                  |                                    |  |  |  |  |

|              |                      | = CNT – 1                                                               | l                                                                                                                                                                                                                                                                                    |                                    |  |  |  |  |

|              | If CNT<br>PC         | = 0;<br>= Address                                                       | G (CONTINUE                                                                                                                                                                                                                                                                          | :)                                 |  |  |  |  |

|              | If CNT<br>PC         | <ul><li>≠ 0;</li><li>= Address</li></ul>                                |                                                                                                                                                                                                                                                                                      |                                    |  |  |  |  |

|              | 10                   | 7001635                                                                 | , TITITI - Z                                                                                                                                                                                                                                                                         | • /                                |  |  |  |  |

| DCFSNZ                                     | Decrement                                                                                                          | Decrement f, Skip if Not 0                                                             |                              |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------|--|--|--|

| Syntax:                                    | DCFSNZ                                                                                                             | DCFSNZ f {,d {,a}}                                                                     |                              |  |  |  |

| Operands:                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                 | d ∈ [0,1]                                                                              |                              |  |  |  |

| Operation:                                 | .,                                                                                                                 | (f) $-1 \rightarrow \text{dest}$ ,<br>skip if result $\neq 0$                          |                              |  |  |  |

| Status Affected:                           | None                                                                                                               |                                                                                        |                              |  |  |  |

| Encoding:                                  | 0100                                                                                                               | 11da fff                                                                               | f ffff                       |  |  |  |

| Description:                               | decremente<br>placed in W                                                                                          | ts of register 'f<br>ed. If 'd' is '0', f<br>/. If 'd' is '1', th<br>< in register 'f' | the result is<br>e result is |  |  |  |

|                                            | instruction v<br>discarded a                                                                                       | is not '0', the<br>which is alread<br>nd a NOP is ex<br>king it a 2-cyc                | ly fetched is<br>kecuted     |  |  |  |

|                                            |                                                                                                                    | ne Access Bar<br>ne BSR is useo<br>(default).                                          |                              |  |  |  |

|                                            | ed instruction<br>ction operates<br>Addressing<br>Fh). See<br><b>iented and</b><br><b>s in Indexed</b><br>details. |                                                                                        |                              |  |  |  |

| Words:                                     | 1                                                                                                                  |                                                                                        |                              |  |  |  |

| Cycles:                                    |                                                                                                                    | ycles if skip ar<br>a 2-word instru                                                    |                              |  |  |  |

| Q Cycle Activity:                          | Q2                                                                                                                 | 02                                                                                     | 04                           |  |  |  |

| Q1<br>Decode                               | Read                                                                                                               | Q3<br>Process                                                                          | Q4<br>Write to               |  |  |  |

| 200000                                     | register 'f'                                                                                                       | Data                                                                                   | destination                  |  |  |  |

| lf skip:                                   |                                                                                                                    |                                                                                        |                              |  |  |  |

| Q1                                         | Q2                                                                                                                 | Q3                                                                                     | Q4                           |  |  |  |

| No<br>operation                            | No<br>operation                                                                                                    | No<br>operation                                                                        | No<br>operation              |  |  |  |