Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

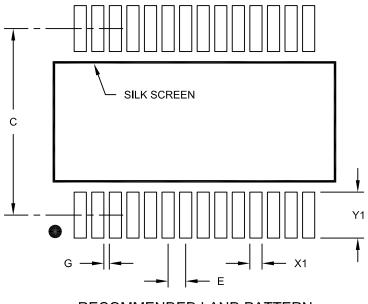

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j53-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                           | Pin N             | Pin Number        |             |                  |                                            |  |

|-------------------------------------------------------------------------------------------|-------------------|-------------------|-------------|------------------|--------------------------------------------|--|

| Pin Name                                                                                  | 44-<br>QFN        | 44-<br>TQFP       | Pin<br>Type | Buffer<br>Type   | Description                                |  |

|                                                                                           |                   |                   |             |                  | PORTD is a bidirectional I/O port.         |  |

| RD0/PMD0/SCL2                                                                             | 38 <sup>(3)</sup> | 38(3)             |             |                  |                                            |  |

| RD0                                                                                       |                   |                   | I/O         | ST/DIG           | Digital I/O.                               |  |

| PMD0                                                                                      |                   |                   | I/O         | ST/TTL/          | Parallel Master Port data.                 |  |

|                                                                                           |                   |                   |             | DIG              | 20.000                                     |  |

| SCL2                                                                                      | (2)               | (2)               | I/O         | l <sup>2</sup> C | l <sup>2</sup> C data input/output.        |  |

| RD1/PMD1/SDA2                                                                             | 39 <b>(3)</b>     | 39 <b>(3)</b>     |             |                  |                                            |  |

| RD1                                                                                       |                   |                   | I/O         | ST/DIG           |                                            |  |

| PMD1                                                                                      |                   |                   | I/O         | ST/TTL/<br>DIG   | Parallel Master Port data.                 |  |

| SDA2                                                                                      |                   |                   | I/O         | I <sup>2</sup> C | l <sup>2</sup> C data input/output.        |  |

| -                                                                                         | 40(3)             | 40 <sup>(3)</sup> | ., O        |                  |                                            |  |

| RD2/PMD2/RP19<br>RD2                                                                      | 40(3)             | 40(3)             | I/O         | ST/DIG           | Digital I/O.                               |  |

| PMD2                                                                                      |                   |                   | 1/O         | ST/TTL/          | •                                          |  |

|                                                                                           |                   |                   |             | DIG              |                                            |  |

| RP19                                                                                      |                   |                   | I/O         | ST/DIG           | Remappable Peripheral Pin 19 input/output. |  |

| RD3/PMD3/RP20                                                                             | 41 <sup>(3)</sup> | 41 <sup>(3)</sup> |             |                  |                                            |  |

| RD3                                                                                       |                   |                   | I/O         | ST/DIG           | Digital I/O.                               |  |

| PMD3                                                                                      |                   |                   | I/O         | ST/TTL/          |                                            |  |

|                                                                                           |                   |                   |             | DIG              |                                            |  |

| RP20                                                                                      |                   |                   | I/O         | ST/DIG           | Remappable Peripheral Pin 20 input/output. |  |

| RD4/PMD4/RP21                                                                             | 2 <sup>(3)</sup>  | 2 <sup>(3)</sup>  |             |                  |                                            |  |

| RD4                                                                                       |                   |                   | I/O         | ST/DIG           | Digital I/O.                               |  |

| PMD4                                                                                      |                   |                   | I/O         | ST/TTL/          | Parallel Master Port data.                 |  |

| 8804                                                                                      |                   |                   |             | DIG              | Demonschle Devichenst Die 04 immet/endent  |  |

| RP21                                                                                      | (0)               | (0)               | I/O         | ST/DIG           | Remappable Peripheral Pin 21 input/output. |  |

| RD5/PMD5/RP22                                                                             | 3 <b>(3)</b>      | ვ <b>(3)</b>      |             | 07/010           |                                            |  |

| RD5                                                                                       |                   |                   | 1/O         | ST/DIG           | Digital I/O.<br>Parallel Master Port data. |  |

| PMD5                                                                                      |                   |                   | I/O         | ST/TTL/<br>DIG   | Parallel Master Port data.                 |  |

| RP22                                                                                      |                   |                   | I/O         | ST/DIG           | Remappable Peripheral Pin 22 input/output. |  |

| RD6/PMD6/RP23                                                                             | 4 <sup>(3)</sup>  | 4(3)              |             |                  |                                            |  |

| RD6/PMD6/RP23                                                                             | 4,                | 4."/              | I/O         | ST/DIG           | Digital I/O.                               |  |

| PMD6                                                                                      |                   |                   | 1/O         | ST/TTL/          |                                            |  |

|                                                                                           |                   |                   | -           | DIG              |                                            |  |

| RP23                                                                                      |                   |                   | I/O         | ST/DIG           | Remappable Peripheral Pin 23 input/output. |  |

| RD7/PMD7/RP24                                                                             | 5 <b>(3)</b>      | 5 <b>(3)</b>      |             |                  |                                            |  |

| RD7                                                                                       |                   |                   | I/O         | ST/DIG           |                                            |  |

| PMD7                                                                                      |                   |                   | I/O         | ST/TTL/          | Parallel Master Port data.                 |  |

|                                                                                           |                   |                   |             | DIG              |                                            |  |

| RP24                                                                                      |                   |                   | I/O         | ST/DIG           |                                            |  |

| Legend: TTL = TTL compatib                                                                |                   |                   | 0 1         |                  | CMOS = CMOS compatible input or output     |  |

| ST = Schmitt Trigger input with CMOS levels Analog = Analog input<br>I = Input O = Output |                   |                   |             |                  |                                            |  |

| I = Input<br>P = Power                                                                    |                   |                   |             |                  | OD = Open-Drain (no P diode to VDD)        |  |

| DIG = Digital output                                                                      |                   |                   |             |                  | $I^2C$ = Open-Drain, $I^2C$ specific       |  |

|                                                                                           | disabled if       | OSC1              | and O       | SC2 are          | used for the clock function.               |  |

PIC18F4XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

2: Available only on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

3: 5.5V tolerant.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Low-Power Modes".

- Note 1: The Timer1 crystal driver is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select the Timer1 clock source will be ignored, unless the CONFIG2L register's T1DIG bit is set.

- 2: If Timer1 is driving a crystal, it is recommended that the Timer1 oscillator be operating and stable prior to switching to it as the clock source; otherwise, a very long delay may occur while the Timer1 oscillator starts.

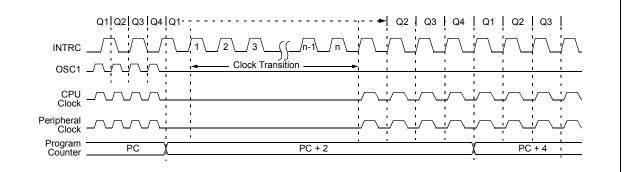

#### 3.5.2 OSCILLATOR TRANSITIONS

PIC18F47J53 family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in more detail in **Section 4.1.2 "Entering Power-Managed Modes**".

| R/W-0 | R/W-1 | R/W-1 | R/W-0 | R-1 <sup>(1)</sup> | R-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------------------|------|-------|-------|

| IDLEN | IRCF2 | IRCF1 | IRCF0 | OSTS               | FLTS | SCS1  | SCS0  |

| bit 7 |       |       |       |                    |      |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as `0′             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | IDLEN: Idle Enable bit                                                                  |

|---------|-----------------------------------------------------------------------------------------|

|         | 1 = Device enters Idle mode on SLEEP instruction                                        |

|         | 0 = Device enters Sleep mode on SLEEP instruction                                       |

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits                                    |

|         | 111 = 8 MHz (INTOSC drives clock directly)                                              |

|         | 110 = 4 $MHz^{(2)}$                                                                     |

|         | 101 <b>= 2 MHz</b>                                                                      |

|         | 100 <b>= 1 MHz</b>                                                                      |

|         | 011 = 500 kHz                                                                           |

|         | 010 = 250 kHz                                                                           |

|         | 001 = 125 kHz<br>000 = 31 kHz (from either INTOSC/256 or INTRC directly) <sup>(3)</sup> |

|         |                                                                                         |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup>                     |

|         | 1 = Oscillator Start-up Timer time-out has expired; primary oscillator is running       |

|         | 0 = Oscillator Start-up Timer time-out is running; primary oscillator is not ready      |

| bit 2   | FLTS: Frequency Lock Tuning Status bit                                                  |

|         | 1 = INTOSC is stable                                                                    |

|         | 0 = INTOSC is not stable                                                                |

| bit 1-0 | SCS<1:0>: System Clock Select bits                                                      |

|         | 11 = Postscaled internal clock (INTRC/INTOSC derived)                                   |

|         | 10 = Reserved                                                                           |

|         | 01 = Timer1 oscillator                                                                  |

|         | 00 = Primary clock source (INTOSC postscaler output when FOSC<2:0> = 001 or 000)        |

|         | 00 = Primary clock source (CPU divider output for other values of FOSC<2:0>)            |

| Note 1: | Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.              |

| 2:      | Default output frequency of INTOSC on Reset (4 MHz).                                    |

Default output frequency of INTOSC on Reset (4 MH2).

Source selected by the INTSRC bit (OSCTUNE<7>).

## 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. This mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications, which are not highly timing-sensitive or do not require high-speed clocks at all times.

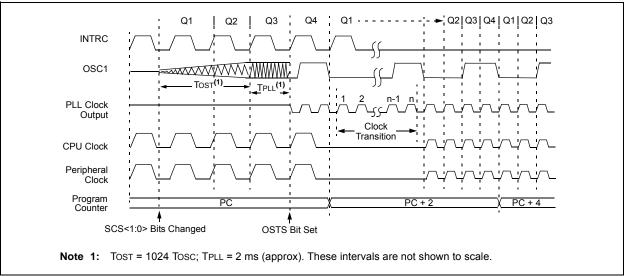

This mode is entered by setting the SCS<1:0> bits (OSCCON<1:0>) to '11'. When the clock source is switched to the internal oscillator block (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared.

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC block while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC clock source will continue to run if either the WDT or the FSCM is enabled.

#### REGISTER 4-3: DSGPR0: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 0 (BANKED F4Eh)

| -                 | -                |                              |                    |       |

|-------------------|------------------|------------------------------|--------------------|-------|

|                   |                  | R/W-xxxx <sup>(1)</sup>      |                    |       |

|                   | Deep Sleep Per   | sistent General Purpose bits |                    |       |

| bit 7             |                  |                              |                    | bit 0 |

|                   |                  |                              |                    |       |

| Legend:           |                  |                              |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit,       | read as '0'        |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared         | x = Bit is unknown |       |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

#### REGISTER 4-4: DSGPR1: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 1 (BANKED F4Fh)

| R/W-xxxx <sup>(1)</sup>       |              |

|-------------------------------|--------------|

| Deep Sleep Persistent General | Purpose bits |

| bit 7                         | bit 0        |

|                               |              |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 Deep Sleep Persistent General Purpose bits

Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

## REGISTER 4-5: DSWAKEH: DEEP SLEEP WAKE HIGH BYTE REGISTER (BANKED F4Bh)

| U-0             | U-0 | U-0              | U-0 | U-0                                | U-0              | U-0      | R/W-0  |

|-----------------|-----|------------------|-----|------------------------------------|------------------|----------|--------|

| —               | —   | —                | —   | —                                  | —                | —        | DSINT0 |

| bit 7           | •   |                  |     |                                    |                  |          | bit 0  |

|                 |     |                  |     |                                    |                  |          |        |

| Legend:         |     |                  |     |                                    |                  |          |        |

| R = Readable I  | bit | W = Writable     | bit | U = Unimpler                       | mented bit, read | l as '0' |        |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is un |                  | nown     |        |

bit 7-1 Unimplemented: Read as '0'

DSINT0: Interrupt-on-Change bit

1 = Interrupt-on-change was asserted during Deep Sleep

0 = Interrupt-on-change was not asserted during Deep Sleep

bit 0

<sup>© 2009-2016</sup> Microchip Technology Inc.

# PIC18F47J53

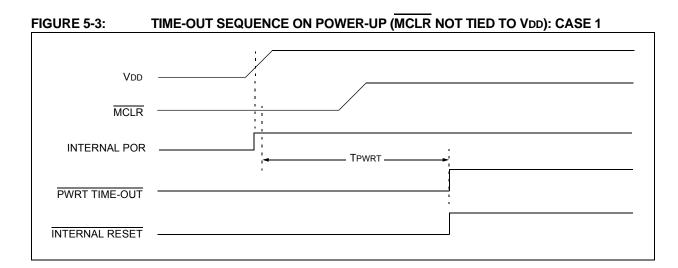

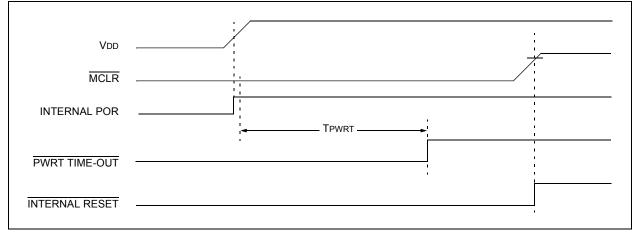

## FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

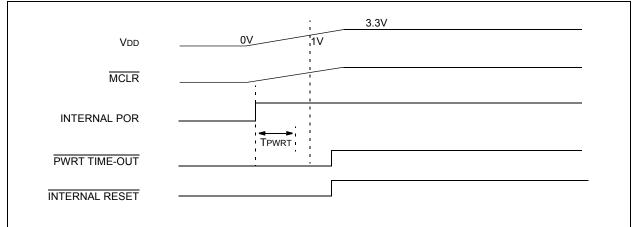

## FIGURE 5-5: SLOW RISE TIME (MCLR TIED TO VDD, VDD RISE > TPWRT)

## 9.0 INTERRUPTS

Devices of the PIC18F47J53 family have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are 19 registers, which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4, PIR5

- PIE1, PIE2, PIE3, PIE4, PIE5

- IPR1, IPR2, IPR3, IPR4, IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address, 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

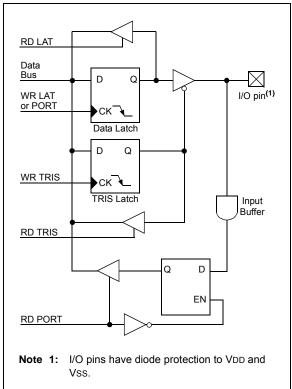

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

Figure 10-1 displays a simplified model of a generic I/O port, without the interfaces to other peripherals.

FIGURE 10-1: GENERIC I/O PORT OPERATION

## 10.1 I/O Port Pin Capabilities

When developing an application, the capabilities of the port pins must be considered. Outputs on some pins have higher output drive strength than others. Similarly, some pins can tolerate higher than VDD input levels.

## 10.1.1 PIN OUTPUT DRIVE

The output pin drive strengths vary for groups of pins intended to meet the needs for a variety of applications. PORTB and PORTC are designed to drive higher loads, such as LEDs. All other ports are designed for small loads, typically indication only. Table 10-1 summarizes the output capabilities. Refer to **Section 31.0 "Electrical Characteristics"** for more details.

| TABLE 10-1: OUTPUT DRIVE LEVEL |

|--------------------------------|

|--------------------------------|

| Port  | Drive   | Description                   |  |  |

|-------|---------|-------------------------------|--|--|

| PORTA |         |                               |  |  |

| PORTD | Minimum | Intended for indication.      |  |  |

| PORTE |         |                               |  |  |

| PORTB | High    | Suitable for direct LED drive |  |  |

| PORTC | High    | levels.                       |  |  |

## 10.1.2 INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages up to 5.5V; a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should be avoided. Table 10-2 summarizes the input capabilities. Refer to **Section 31.0 "Electrical Characteristics"** for more details.

TABLE 10-2: INPUT VOLTAGE LEVELS

| Port or Pin | Tolerated<br>Input | Description                      |

|-------------|--------------------|----------------------------------|

| PORTA<7:0>  |                    |                                  |

| PORTB<3:0>  | Voo                | Only VDD input levels            |

| PORTC<2:0>  | VDD                | tolerated.                       |

| PORTE<2:0>  |                    |                                  |

| PORTB<7:4>  |                    | Tolerates input levels           |

| PORTC<7:6>  | 5.5V               | above VDD, useful for            |

| PORTD<7:0>  |                    | most standard logic.             |

| PORTC<5:4>  | (USB)              | Designed for USB specifications. |

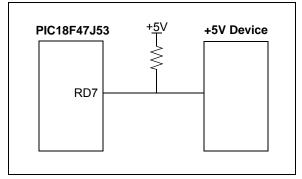

### 10.1.3 INTERFACING TO A 5V SYSTEM

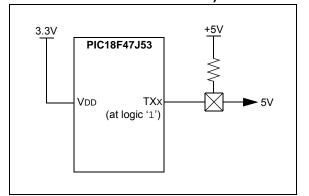

Though the VDDMAX of the PIC18F47J53 family is 3.6V, these devices are still capable of interfacing with 5V systems, even if the VIH of the target system is above 3.6V. This is accomplished by adding a pull-up resistor to the port pin (Figure 10-2), clearing the LAT bit for that pin and manipulating the corresponding TRIS bit (Figure 10-1) to either allow the line to be pulled high or to drive the pin low. Only port pins that are tolerant of voltages up to 5.5V can be used for this type of interface (refer to Section 10.1.2 "Input Pins and Voltage Considerations").

FIGURE 10-2: +5V SYSTEM HARDWARE INTERFACE

#### EXAMPLE 10-1: COMMUNICATING WITH THE +5V SYSTEM

| BCF LATD, 7  | ; set up LAT register so<br>; changing TRIS bit will<br>; drive line low |

|--------------|--------------------------------------------------------------------------|

|              | ; send a 0 to the 5V system                                              |

| BCF TRISD, 7 | ; send a 1 to the 5V system                                              |

#### 10.1.4 OPEN-DRAIN OUTPUTS

The output pins for several peripherals are also equipped with a configurable open-drain output option. This allows the peripherals to communicate with external digital logic operating at a higher voltage level, without the use of level translators.

The open-drain option is implemented on port pins specifically associated with the data and clock outputs of the EUSARTs, the MSSP modules (in SPI mode) and

the ECCP modules. It is selectively enabled by setting the open-drain control bit for the corresponding module in the ODCON registers (Register 10-1, Register 10-2 and Register 10-3). Their configuration is discussed in more detail with the individual port where these peripherals are multiplexed. Output functions that are routed through the PPS module may also use the open-drain option. The open-drain functionality will follow the I/O pin assignment in the PPS module.

When the open-drain option is required, the output pin must also be tied through an external pull-up resistor provided by the user to a higher voltage level, up to 5.5V (Figure 10-3). When a digital logic high signal is output, it is pulled up to the higher voltage level.

# FIGURE 10-3:

#### USING THE OPEN-DRAIN OUTPUT (USART SHOWN AS EXAMPLE)

## 10.1.5 TTL INPUT BUFFER OPTION

Many of the digital I/O ports use Schmitt Trigger (ST) input buffers. While this form of buffering works well with many types of input, some applications may require TTL level signals to interface with external logic devices. This is particularly true for the Parallel Master Port (PMP), which is likely to be interfaced to TTL level logic or memory devices.

The inputs for the PMP can be optionally configured for TTL buffers with the PMPTTL bit in the PADCFG1 register (Register 10-4). Setting this bit configures all data and control input pins for the PMP to use TTL buffers. By default, these PMP inputs use the port's ST buffers.

| TABLE 10-11: | PORIEI   | 0 2010110       | IART |             |                                                                      |

|--------------|----------|-----------------|------|-------------|----------------------------------------------------------------------|

| Pin          | Function | TRIS<br>Setting | I/O  | I/O<br>Type | Description                                                          |

| RE0/AN5/     | RE0      | 1               | Ι    | ST          | PORTE<0> data input; disabled when analog input is enabled.          |

| PMRD         |          | 0               | 0    | DIG         | LATE<0> data output; not affected by analog input.                   |

|              | AN5      | 1               | Ι    | ANA         | A/D Input Channel 5; default input configuration on POR.             |

|              | PMRD     | 1               | Ι    | ST/TTL      | Parallel Master Port (io_rd_in).                                     |

|              |          | 0               | 0    | DIG         | Parallel Master Port read strobe.                                    |

| RE1/AN6/     | RE1      | 1               | Ι    | ST          | PORTE<1> data input; disabled when analog input is enabled.          |

| PMWR         |          | 0               | 0    | DIG         | LATE<1> data output; not affected by analog input.                   |

|              | AN6      | 1               | Ι    | ANA         | A/D Input Channel 6; default input configuration on POR.             |

|              | PMWR     | 1               | Ι    | ST/TTL      | Parallel Master Port (io_wr_in).                                     |

|              |          | 0               | 0    | DIG         | Parallel Master Port write strobe.                                   |

| RE2/AN7/     | RE2      | 1               | Ι    | ST          | PORTE<2> data input; disabled when analog input is enabled.          |

| PMCS         |          | 0               | 0    | DIG         | LATE<2> data output; not affected by an analog input.                |

|              | AN7      | 1               | Ι    | ANA         | A/D Input Channel 7; default input configuration on POR.             |

|              | PMCS     | 0               | 0    | DIG         | Parallel Master Port byte enable.                                    |

| Vss1<br>Vss2 |          | _               | Ρ    | _           | Ground reference for logic and I/O pins.                             |

| AVss1        | —        | —               | Р    | _           | Ground reference for analog modules.                                 |

| Vdd1         |          |                 | 6    |             | Desitive surgely for a sink and disited to sign and UO since         |

| VDD2         |          | _               | Р    | _           | Positive supply for peripheral digital logic and I/O pins.           |

| VDDCORE/VCAP | VDDCORE  |                 | Р    | _           | Positive supply for microcontroller core logic (regulator disabled). |

|              | VCAP     |                 | Р    | _           | External filter capacitor connection (regulator enabled).            |

| AVDD1        |          |                 | Р    |             | Positive supply for appleg modules                                   |

| AVDD2        |          |                 | _    |             | Positive supply for analog modules.                                  |

| VUSB         |          |                 | Р    | _           | USB voltage input pin.                                               |

#### TABLE 10-11: PORTE I/O SUMMARY

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level I = Input; O = Output; P = Power

#### TABLE 10-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                 | Bit 7                | Bit 6                | Bit 5                | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|----------------------|----------------------|----------------------|----------------------|-------|-------|--------|--------|--------|

| PORTE <sup>(1)</sup> | —                    | —                    | _                    | _     | _     | RE2    | RE1    | RE0    |

| LATE <sup>(1)</sup>  | _                    | _                    | _                    | _     |       | LATE2  | LATE1  | LATE0  |

| TRISE <sup>(1)</sup> | RDPU                 | REPU                 | _                    | —     | —     | TRISE2 | TRISE1 | TRISE0 |

| ANCON0               | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4 | PCFG3 | PCFG2  | PCFG1  | PCFG0  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTE.

**Note 1:** These registers and/or bits are not available in 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF26J53).

| Note: | bit 7 | RDPU: PORTD Pull-up Enable bit               |

|-------|-------|----------------------------------------------|

|       | 0 =   | All PORTD pull-ups are disabled              |

|       | 1 =   | PORTD pull-ups are enabled for any input pad |

|       | bit 6 | REPU: PORTE Pull-up Enable bit               |

|       |       |                                              |

- 0 = All PORTE pull-ups are disabled

- 1 = PORTE pull-ups are enabled for any input pad

# PIC18F47J53

## REGISTER 18-4: CCPRxL: CCP4-10 PERIOD LOW BYTE REGISTER (4, BANKED F13h; 5, F10h; 6, F0Dh; 7, F0Ah; 8, F07h; 9, F04h; 10, F01h)

| R/W-x       | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxL7     | CCPRxL6 | CCPRxL5 | CCPRxL4 | CCPRxL3 | CCPRxL2 | CCPRxL1 | CCPRxL0 |

| bit 7 bit 0 |         |         |         |         |         |         |         |

|             |         |         |         |         |         |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 CCPRxL<7:0>: CCPx Period Register Low Byte bits Capture Mode: Capture register low byte Compare Mode: Compare register low byte PWM Mode: PWM Period register low byte

## REGISTER 18-5: CCPRxH: CCP4-10 PERIOD HIGH BYTE REGISTER (4, BANKED F14h; 5, F11h; 6, F0Eh; 7, F0Bh; 8, F08h; 9, F05h; 10, F02h)

| R/W-x     | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxH7   | CCPRxH6 | CCPRxH5 | CCPRxH4 | CCPRxH3 | CCPRxH2 | CCPRxH1 | CCPRxH0 |

| bit 7 bit |         |         |         |         |         |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **CCPRxH<7:0>:** CCPx Period Register High Byte bits Capture Mode: Capture register high byte Compare Mode: Compare register high byte PWM Mode: PWM Period register high byte

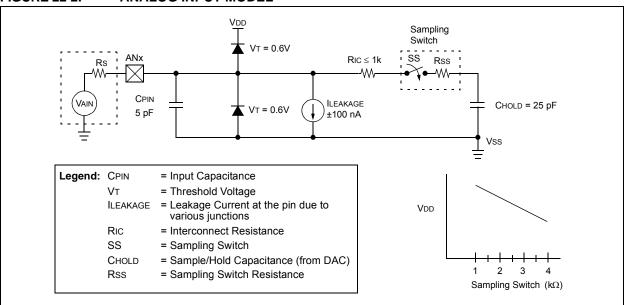

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs. To determine acquisition time, see **Section 22.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to do an A/D conversion:

- 1. Configure the A/D module:

- Configure the required ADC pins as analog pins using ANCON0, ANCON1

- Set voltage reference using ADCON0

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON1)

- Select A/D conversion clock (ADCON1)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- · Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0<1>)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- 7. For the next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum Wait of 2 TAD is required before the next acquisition starts.

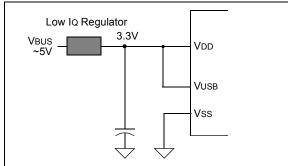

### 23.6 USB Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are Bus Power Only, Self-Power Only and Dual Power with Self-Power Dominance. The most common cases are presented here. Also provided is a means of estimating the current consumption of the USB transceiver.

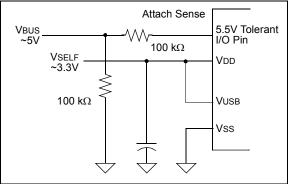

#### 23.6.1 BUS POWER ONLY

In Bus Power Only mode, all power for the application is drawn from the USB (Figure 23-9). This is effectively the simplest power method for the device.

In order to meet the inrush current requirements of the USB 2.0 Specification, the total effective capacitance appearing across VBUS and ground must be no more than 10  $\mu$ F. If not, some kind of inrush timing is required. For more details, see Section 7.2.4 of the USB 2.0 Specification.

According to the USB 2.0 Specification, all USB devices must also support a Low-Power Suspend mode. In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable.

The host signals the USB device to enter the Suspend mode by stopping all USB traffic to that device for more than 3 ms. This condition will cause the IDLEIF bit in the UIR register to become set.

During the USB Suspend mode, the D+ or D- pull-up resistor must remain active, which will consume some of the allowed suspend current: 2.5 mA budget.

#### FIGURE 23-9: BUS POWER ONLY

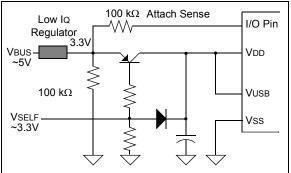

#### 23.6.2 SELF-POWER ONLY

In Self-Power Only mode, the USB application provides its own power, with very little power being pulled from the USB. See Figure 23-10 for an example.

Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

In order to meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

#### FIGURE 23-10: SELF-POWER ONLY

#### 23.6.3 DUAL POWER WITH SELF-POWER DOMINANCE

Some applications may require a dual power option. This allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. See Figure 23-11 for a simple Dual Power with Self-Power Dominance mode example, which automatically switches between Self-Power Only and USB Bus Power Only modes.

Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current, and must not enable the USB module until VBUS is driven high. See Section 23.6.1 "Bus Power Only" and Section 23.6.2 "Self-Power Only" for descriptions of those requirements. Additionally, dual power devices must never source current onto the 5V VBUS pin of the USB cable.

#### FIGURE 23-11: DUAL POWER EXAMPLE

Note: Users should keep in mind the limits for devices drawing power from the USB. According to USB Specification 2.0, this cannot exceed 100 mA per low-power device or 500 mA per high-power device.

### 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

#### EQUATION 25-1: CALCULATING OUTPUT OF THE COMPARATOR VOLTAGE REFERENCE

<u>When CVRR = 1 and CVRSS = 0:</u> CVREF = ((CVR<3:0>)/24) x (CVRSRC) <u>When CVRR = 0 and CVRSS = 0:</u> CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) x (CVRSRC) <u>When CVRR = 1 and CVRSS = 1:</u> CVREF = ((CVR<3:0>)/24) x (CVRSRC) + VREF-<u>When CVRR = 0 and CVRSS = 1:</u> CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) x (CVRSRC) + VREF-) The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0** "**Electrical Characteristics**").

### REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER (F53h)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                             |                  |       |                   |                  |                 | . ,   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|-------|

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                       | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| CVREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CVROE <sup>(1)</sup>                                                                                                                                                                                                        | CVRR             | CVRSS | CVR3              | CVR2             | CVR1            | CVR0  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                             |                  |       |                   |                  |                 | bit 0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                             |                  |       |                   |                  |                 |       |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                             |                  |       |                   |                  |                 |       |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit                                                                                                                                                                                                                         | W = Writable     | bit   | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | POR                                                                                                                                                                                                                         | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

| bit 7 CVREN: Comparator Voltage Reference Enable bit<br>1 = CVREF circuit is powered on<br>0 = CVREF circuit is powered down<br>bit 6 CVROE: Comparator VREF Output Enable bit <sup>(1)</sup><br>1 = CVREF voltage level is also output on the RA2/AN2//C2INB/C1IND/C3INB/VREF-/CVREF pin<br>0 = CVREF voltage is disconnected from the RA2/AN2//C2INB/C1IND/C3INB/VREF-/CVREF pin<br>bit 5 CVRR: Comparator VREF Range Selection bit<br>1 = 0 to 0.667 CVRSRC with CVRSRC/24 step size (low range)<br>0 = 0.25 CVRSRC to 0.75 CVRSRC with CVRSRC/32 step size (high range) |                                                                                                                                                                                                                             |                  |       |                   |                  |                 |       |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CVRSS: Comparator VREF Source Selection bit<br>1 = Comparator reference source, CVRSRC = (VREF+) – (VREF-)<br>0 = Comparator reference source, CVRSRC = AVDD – AVSS                                                         |                  |       |                   |                  |                 |       |

| bit 3-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $CVR<3:0>: Comparator VREF Value Selection bits (0 \le (CVR<3:0>) \le 15)$ $\frac{When CVRR = 1:}{CVREF = ((CVR<3:0>)/24) \bullet (CVRSRC)}$ $\frac{When CVRR = 0:}{CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) \bullet (CVRSRC)}$ |                  |       |                   |                  |                 |       |

**Note 1:** CVROE overrides the TRIS bit setting.

# PIC18F47J53

| RRN   | CF                       | Rotate Rig                                                 | Rotate Right f (No Carry)                                        |                                                    |                                                              |  |  |  |

|-------|--------------------------|------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Synt  | ax:                      | RRNCF                                                      | f {,d {,a}}                                                      |                                                    |                                                              |  |  |  |

| Oper  | rands:                   | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$        |                                                                  |                                                    |                                                              |  |  |  |

| Oper  | ration:                  | $(f \le n >) \rightarrow c$<br>$(f \le 0 >) \rightarrow c$ |                                                                  | .>,                                                |                                                              |  |  |  |

| Statu | is Affected:             | N, Z                                                       |                                                                  |                                                    |                                                              |  |  |  |

| Enco  | oding:                   | 0100                                                       | 00da                                                             | fff                                                | f ffff                                                       |  |  |  |

| Desc  | cription:                | one bit to                                                 | the right. I<br>n W. If 'd'                                      | lf 'd' is<br>is '1', '                             | are rotated<br>'0', the result<br>the result is<br>default). |  |  |  |

|       |                          |                                                            | overriding<br>the bank                                           | the BS<br>will be                                  | R value. If 'a' selected as                                  |  |  |  |

|       |                          | set is enal<br>in Indexed<br>mode whe<br><b>Section 2</b>  | bled, this i<br>Literal O<br>never f ≤<br>9.2.3 "By<br>ed Instru | instruct<br>ffset A<br>95 (5F<br>te-Orie<br>ctions | h). See<br>ented and<br>in Indexed                           |  |  |  |

|       |                          |                                                            | ► re                                                             | egister                                            | f -                                                          |  |  |  |

| Word  | ds:                      | 1                                                          |                                                                  |                                                    |                                                              |  |  |  |

| Cycle | es:                      | 1                                                          |                                                                  |                                                    |                                                              |  |  |  |

|       | ycle Activity:           |                                                            |                                                                  |                                                    |                                                              |  |  |  |

|       | Q1                       | Q2                                                         | Q3                                                               | 3                                                  | Q4                                                           |  |  |  |

|       | Decode                   | Read                                                       | Proce                                                            |                                                    | Write to destination                                         |  |  |  |

|       |                          | register 'f'                                               | Data                                                             | a                                                  | uestination                                                  |  |  |  |

| Exar  | nple 1:                  | RRNCF                                                      | REG, 1,                                                          | 0                                                  |                                                              |  |  |  |

|       | Before Instruc           | tion                                                       |                                                                  |                                                    |                                                              |  |  |  |

|       | REG<br>After Instruction | = 1101                                                     | 0111                                                             |                                                    |                                                              |  |  |  |

|       | After Instructio         | = 1110                                                     | 1011                                                             |                                                    |                                                              |  |  |  |

| Exar  | nple 2:                  | RRNCF                                                      | REG, 0,                                                          | 0                                                  |                                                              |  |  |  |

|       | Before Instruc           |                                                            |                                                                  |                                                    |                                                              |  |  |  |

|       | W<br>REG                 | = ?<br>= 1101                                              | 0111                                                             |                                                    |                                                              |  |  |  |

|       | After Instructio         | ==0=                                                       | ~ + + + +                                                        |                                                    |                                                              |  |  |  |

|       | ₩<br>REG                 | = 1110<br>= 1101                                           |                                                                  |                                                    |                                                              |  |  |  |

|       |                          |                                                            |                                                                  |                                                    |                                                              |  |  |  |

| SETF                    | Set f                                                                                                 |                                                                 |                                                                 |                                                |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|--|--|--|

| Syntax:                 | SETF f{,                                                                                              | SETF f {,a}                                                     |                                                                 |                                                |  |  |  |

| Operands:               | $0 \le f \le 255$                                                                                     |                                                                 |                                                                 |                                                |  |  |  |

|                         | a ∈ [0,1]                                                                                             |                                                                 |                                                                 |                                                |  |  |  |

| Operation:              | $FFh\tof$                                                                                             |                                                                 |                                                                 |                                                |  |  |  |

| Status Affected:        | None                                                                                                  |                                                                 |                                                                 |                                                |  |  |  |

| Encoding:               | 0110                                                                                                  | 100a                                                            | ffff                                                            | ffff                                           |  |  |  |

| Description:            | The conter<br>are set to F                                                                            |                                                                 | specified                                                       | register                                       |  |  |  |

|                         | If 'a' is '0',<br>If 'a' is '1',<br>GPR bank                                                          | the BSR i                                                       | is used to                                                      |                                                |  |  |  |

|                         | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>Section 29<br>Bit-Oriente<br>Literal Off | led, this i<br>Literal O<br>never f ≤<br>9.2.3 "By<br>ed Instru | nstruction<br>ffset Addr<br>95 (5Fh).<br>te-Orient<br>ctions in | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |

| Words:                  | 1                                                                                                     |                                                                 |                                                                 |                                                |  |  |  |

| Cycles:                 | 1                                                                                                     |                                                                 |                                                                 |                                                |  |  |  |

| Q Cycle Activity:       |                                                                                                       |                                                                 |                                                                 |                                                |  |  |  |

| Q1                      | Q2                                                                                                    | Q3                                                              | 3                                                               | Q4                                             |  |  |  |

| Decode                  | Read                                                                                                  | Proce                                                           |                                                                 | Write                                          |  |  |  |

|                         | register 'f'                                                                                          | Data                                                            | a re                                                            | gister 'f'                                     |  |  |  |

| Example:                | SETF                                                                                                  | RE                                                              | G,1                                                             |                                                |  |  |  |

| Before Instruct         |                                                                                                       |                                                                 |                                                                 |                                                |  |  |  |

| REG<br>After Instructio | = 54                                                                                                  | ۸h                                                              |                                                                 |                                                |  |  |  |

| After Instructio<br>REG | n<br>= Ff                                                                                             | =h                                                              |                                                                 |                                                |  |  |  |

|                         |                                                                                                       |                                                                 |                                                                 |                                                |  |  |  |

| CAL                                                                                                                                                                                                                                                            | LW                             | Subroutine                                                                                                                           | Subroutine Call Using WREG                                                                                                                                                                                                                                                                                                                                                                                                  |           |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

| Syntax:                                                                                                                                                                                                                                                        |                                | CALLW                                                                                                                                | CALLW                                                                                                                                                                                                                                                                                                                                                                                                                       |           |  |  |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                           | ands:                          | None                                                                                                                                 | None                                                                                                                                                                                                                                                                                                                                                                                                                        |           |  |  |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                           | ation:                         | (W) → PCL<br>(PCLATH) -                                                                                                              | $(PC + 2) \rightarrow TOS,$<br>$(W) \rightarrow PCL,$<br>$(PCLATH) \rightarrow PCH,$<br>$(PCLATU) \rightarrow PCU$                                                                                                                                                                                                                                                                                                          |           |  |  |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                          | s Affected:                    | None                                                                                                                                 | None                                                                                                                                                                                                                                                                                                                                                                                                                        |           |  |  |  |  |  |  |  |