#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j53-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FJ MICROCONTROLLERS

# 2.1 Basic Connection Requirements

Getting started with the PIC18F47J53 family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

- VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

- Note: On 44-pin QFN packages, the AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used. On other package types, the AVDD and AVss pins are internally connected to the VDD/Vss pins.

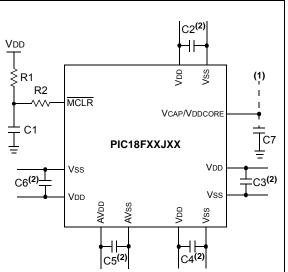

The minimum mandatory connections are shown in Figure 2-1.

# FIGURE 2-1: RECOMMENDED

### MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10 µF, 6.3V or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100Ω to 470Ω

- Note 1: See Section 2.4 "Voltage Regulator Pins (VCAP/VDDCORE)" for explanation of VCAP/VDDCORE connections.

- 2: The example shown is for a PIC18F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

# PIC18F47J53

## REGISTER 3-3: OSCCON2: OSCILLATOR CONTROL REGISTER 2 (ACCESS F87h)

| U-0                                | R-0 <sup>(2)</sup>                                              | U-0                            | R/W-1           | R/W-0 <sup>(2)</sup>  | R/W-1             | U-0             | U-0   |

|------------------------------------|-----------------------------------------------------------------|--------------------------------|-----------------|-----------------------|-------------------|-----------------|-------|

| _                                  | SOSCRUN                                                         | —                              | SOSCDRV         | SOSCGO <sup>(3)</sup> | PRISD             | —               | _     |

| bit 7                              |                                                                 |                                |                 |                       |                   |                 | bit C |

|                                    |                                                                 |                                |                 |                       |                   |                 |       |

| Legend:                            |                                                                 |                                |                 |                       |                   |                 |       |

| R = Readable                       | e bit                                                           | W = Writable                   | bit             | U = Unimpler          | nented bit, read  | <b>as</b> `0′   |       |

| -n = Value at                      | POR                                                             | '1' = Bit is set               |                 | '0' = Bit is cle      | ared              | x = Bit is unkn | own   |

|                                    |                                                                 |                                |                 |                       |                   |                 |       |

| bit 7                              | Unimplemen                                                      | ted: Read as '                 | 0'              |                       |                   |                 |       |

| bit 6                              | SOSCRUN: S                                                      | SOSC Run Stat                  | tus bit         |                       |                   |                 |       |

|                                    | 1 = System clock comes from secondary SOSC                      |                                |                 |                       |                   |                 |       |

|                                    | 0 = System c                                                    | lock comes fro                 | om an oscillato | or other than So      | OSC               |                 |       |

| bit 5                              | Unimplemen                                                      | ted: Read as '                 | 0'              |                       |                   |                 |       |

| bit 4                              | SOSCDRV: S                                                      | OSC Drive Co                   | ntrol bit       |                       |                   |                 |       |

|                                    |                                                                 | SOSC oscillato<br>er T1OSC/SOS |                 | •                     | Configuration bit | ts, CONFIG2L <  | <4:3> |

| bit 3                              | •                                                               | scillator Start C              |                 |                       |                   |                 |       |

|                                    | 1 = Turns on                                                    | the oscillator,                | even if no peri | pherals are red       | questing it       |                 |       |

|                                    | 0 = Oscillator is shut off unless peripherals are requesting it |                                |                 |                       |                   |                 |       |

| bit 2                              | PRISD: Primary Oscillator Drive Circuit Shutdown bit            |                                |                 |                       |                   |                 |       |

|                                    | 1 = Oscillator drive circuit is on                              |                                |                 |                       |                   |                 |       |

|                                    | 0 = Oscillator drive circuit is off (zero power)                |                                |                 |                       |                   |                 |       |

| bit 1-0 Unimplemented: Read as '0' |                                                                 |                                |                 |                       |                   |                 |       |

- 2: Default output frequency of INTOSC on Reset (4 MHz).

- **3:** When the SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.

### 6.1.4.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off of the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a Power-on Reset (POR).

The action that takes place when the stack becomes full depends on the state of the Stack Overflow Reset Enable (STVREN) Configuration bit.

Refer to **Section 28.1 "Configuration Bits"** for device Configuration bits' description.

If STVREN is set (default), the  $31^{st}$  push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31<sup>st</sup> push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31<sup>st</sup> push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |

|-------|-------------------------------------------|

|       | underflow has the effect of vectoring the |

|       | program to the Reset vector, where the    |

|       | stack conditions can be verified and      |

|       | appropriate actions can be taken. This is |

|       | not the same as a Reset, as the contents  |

|       | of the SFRs are not affected.             |

#### 6.1.4.3 PUSH and POP Instructions

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off of the stack, without disturbing normal program execution, is necessary. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

### REGISTER 6-1: STKPTR: STACK POINTER REGISTER (ACCESS FFCh)

| R/C-0                 | R/C-0                 | U-0              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------------|-----------------------|------------------|-------|-----------------------------------------|-------|-------|-------|

| STKFUL <sup>(1)</sup> | STKUNF <sup>(1)</sup> | —                | SP4   | SP3                                     | SP2   | SP1   | SP0   |

| bit 7                 |                       |                  |       |                                         |       |       | bit 0 |

|                       |                       |                  |       |                                         |       |       |       |

| Legend:               |                       | C = Clearable    | bit   |                                         |       |       |       |

| R = Readable          | bit                   | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at F       | POR                   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>                                         |

|---------|------------------------------------------------------------------------------------|

|         | 1 = Stack became full or overflowed<br>0 = Stack has not become full or overflowed |

|         |                                                                                    |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup>                                    |

|         | 1 = Stack underflow occurred                                                       |

|         | 0 = Stack underflow did not occur                                                  |

| bit 5   | Unimplemented: Read as '0'                                                         |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits                                               |

**Note 1:** Bits 7 and 6 are cleared by user software or by a POR.

# 6.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

# 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under proper conditions, instructions that use the Access Bank, that is, most bit and byte-oriented instructions, can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing) or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is provided in Figure 6-9.

Those who desire to use byte or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 29.2.1 "Extended Instruction Syntax"**.

## 9.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER (ACCESS FF2h)

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7  | GIE/GIEH: Global Interrupt Enable bit                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|

|        | When IPEN = 0:                                                                                                                         |

|        | 1 = Enables all unmasked interrupts                                                                                                    |

|        | 0 = Disables all interrupts                                                                                                            |

|        | When IPEN = 1:                                                                                                                         |

|        | 1 = Enables all high-priority interrupts                                                                                               |

| 1.1.0  | 0 = Disables all interrupts                                                                                                            |

| bit 6  | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                             |

|        | <u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts                                                                |

|        | 0 = Disables all peripheral interrupts                                                                                                 |

|        | When IPEN = 1:                                                                                                                         |

|        | 1 = Enables all low-priority peripheral interrupts                                                                                     |

|        | 0 = Disables all low-priority peripheral interrupts                                                                                    |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                             |

|        | 1 = Enables the TMR0 overflow interrupt                                                                                                |

|        | 0 = Disables the TMR0 overflow interrupt                                                                                               |

| bit 4  | INTOIE: INTO External Interrupt Enable bit                                                                                             |

|        | 1 = Enables the INTO external interrupt                                                                                                |

|        | 0 = Disables the INT0 external interrupt                                                                                               |

| bit 3  | RBIE: RB Port Change Interrupt Enable bit                                                                                              |

|        | 1 = Enables the RB port change interrupt                                                                                               |

| 1.11.0 | 0 = Disables the RB port change interrupt                                                                                              |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                               |

|        | <ul> <li>1 = The TMR0 register has overflowed (must be cleared in software)</li> <li>0 = The TMR0 register did not overflow</li> </ul> |

| bit 1  |                                                                                                                                        |

| DILI   | INTOIF: INTO External Interrupt Flag bit<br>1 = The INTO external interrupt occurred (must be cleared in software)                     |

|        | 0 = The INTO external interrupt did not occur                                                                                          |

| bit 0  | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                          |

| bit 0  | 1 = At least one of the RB<7:4> pins changed state (must be cleared in software)                                                       |

|        | 0 = None of the RB<7:4> pins have changed state                                                                                        |

| Nata 4 | A minmetely and this will continue to act this kit. Deadling DODTD and waiting 4 Toy will and the minmetely                            |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB and waiting 1 TCY will end the mismatch condition and allow the bit to be cleared.

# PIC18F47J53

| R/W-1         | R/W-1                                              | R/W-1            | R/W-1            | R/W-1             | R/W-1            | R/W-1           | R/W-1  |

|---------------|----------------------------------------------------|------------------|------------------|-------------------|------------------|-----------------|--------|

| SSP2IP        | BCL2IP                                             | RC2IP            | TX2IP            | TMR4IP            | CTMUIP           | TMR3GIP         | RTCCIP |

| bit 7         |                                                    |                  |                  |                   |                  |                 | bit    |

| Legend:       |                                                    |                  |                  |                   |                  |                 |        |

| R = Readabl   | le bit                                             | W = Writable     | bit              | U = Unimplen      | nented bit, read | d as '0'        |        |

| -n = Value at | t POR                                              | '1' = Bit is set |                  | '0' = Bit is clea | ared             | x = Bit is unkn | own    |

| bit 7         | <b>SSP2IP:</b> Ma<br>1 = High pri<br>0 = Low pric  |                  | is Serial Port : | 2 Interrupt Prior | ity bit          |                 |        |

| bit 6         | <b>BCL2IP:</b> Bus<br>1 = High pri<br>0 = Low pric | •                | upt Priority bit | (MSSP2 modu       | le)              |                 |        |

| bit 5         | <b>RC2IP:</b> EUS<br>1 = High pri<br>0 = Low pric  | •                | nterrupt Priori  | ty bit            |                  |                 |        |

| bit 4         | <b>TX2IP:</b> EUS<br>1 = High pri<br>0 = Low pric  |                  | nterrupt Prior   | ity bit           |                  |                 |        |

| bit 3         | <b>TMR4IE:</b> TM<br>1 = High pri<br>0 = Low pric  | •                | rupt Priority b  | it                |                  |                 |        |

| bit 2         | <b>CTMUIP:</b> Ch<br>1 = High pri<br>0 = Low pric  |                  | surement Unit    | (CTMU) Interru    | pt Priority bit  |                 |        |

| bit 1         | <b>TMR3GIP:</b> T<br>1 = High pri<br>0 = Low pric  | •                | rrupt Priority b | bit               |                  |                 |        |

| bit 0         | <b>RTCCIP:</b> RT<br>1 = High pri<br>0 = Low pric  | •                | ority bit        |                   |                  |                 |        |

# REGISTER 9-16: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3 (ACCESS FA5h)

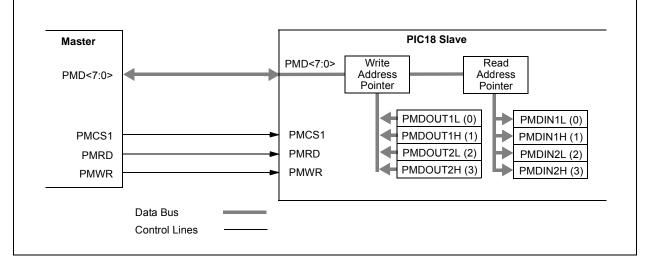

#### 11.2.4 BUFFERED PARALLEL SLAVE PORT MODE

Buffered Parallel Slave Port mode is functionally identical to the legacy PSP mode with one exception, the implementation of 4-level read and write buffers. Buffered PSP mode is enabled by setting the INCM bits in the PMMODEH register. If the INCM<1:0> bits are set to '11', the PMP module will act as the buffered PSP.

When the Buffered PSP mode is active, the PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2H registers become the write buffers and the PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H registers become the read buffers. Buffers are numbered, 0 through 3, starting with the lower byte of PMDIN1L to PMDIN2H as the read buffers and PMDOUT1L to PMDOUT2H as the write buffers.

### 11.2.4.1 READ FROM SLAVE PORT

For read operations, the bytes will be sent out sequentially, starting with Buffer 0 (PMDOUT1L<7:0>) and ending with Buffer 3 (PMDOUT2H<7:0>) for every read strobe. The module maintains an internal pointer to keep track of which buffer is to be read. Each buffer has a corresponding read status bit, OBxE, in the PMSTATL register. This bit is cleared when a buffer contains data that has not been written to the bus, and is set when data is written to the bus. If the current buffer location being read from is empty, a buffer underflow is generated and the Buffer Overflow Flag bit, OBUF, is set. If all four OBxE status bits are set, then the Output Buffer Empty flag (OBE) will also be set.

# 11.2.4.2 WRITE TO SLAVE PORT

For write operations, the data has to be stored sequentially, starting with Buffer 0 (PMDIN1L<7:0>) and ending with Buffer 3 (PMDIN2H<7:0>). As with read operations, the module maintains an internal pointer to the buffer that is to be written next.

The input buffers have their own write status bits: IBxF in the PMSTATH register. The bit is set when the buffer contains unread incoming data and cleared when the data has been read. The flag bit is set on the write strobe. If a write occurs on a buffer when its associated IBxF bit is set, the Buffer Overflow flag, IBOV, is set; any incoming data in the buffer will be lost. If all four IBxF flags are set, the Input Buffer Full Flag (IBF) is set.

In Buffered Slave mode, the module can be configured to generate an interrupt on every read or write strobe (IRQM<1:0> = 01). It can be configured to generate an interrupt on a read from Read Buffer 3 or a write to Write Buffer 3, which is essentially an interrupt every fourth read or write strobe (RQM<1:0> = 11). When interrupting every fourth byte for input data, all input buffer registers should be read to clear the IBxF flags. If these flags are not cleared, then there is a risk of hitting an overflow condition.

#### FIGURE 11-5: PARALLEL MASTER/SLAVE CONNECTION BUFFERED EXAMPLE

| R/W-0        | R/W-0                                          | R/W-0            | R/W-0          | R/W-0            | R/W-0                       | R/W-0                      | R/W-0       |  |  |

|--------------|------------------------------------------------|------------------|----------------|------------------|-----------------------------|----------------------------|-------------|--|--|

| ALRMEN       | CHIME                                          | AMASK3           | AMASK2         | AMASK1           | AMASK0                      | ALRMPTR1                   | ALRMPTR0    |  |  |

| bit 7        |                                                |                  |                |                  |                             |                            | bit (       |  |  |

| Legend:      |                                                |                  |                |                  |                             |                            |             |  |  |

| R = Readable | e bit                                          | W = Writable     | bit            | U = Unimpler     | mented bit, rea             | d as '0'                   |             |  |  |

|              |                                                | '1' = Bit is set |                | '0' = Bit is cle | ared                        | x = Bit is unki            | nown        |  |  |

|              |                                                |                  |                |                  |                             |                            |             |  |  |

| bit 7        |                                                | arm Enable bit   |                |                  |                             |                            |             |  |  |

|              |                                                |                  | ed automatical | y after an alarr | n event whene               | ver ARPT<7:0>              | = 0000 0000 |  |  |

|              | and CHII<br>0 = Alarm is                       | ,                |                |                  |                             |                            |             |  |  |

| bit 6        | CHIME: Chim                                    |                  |                |                  |                             |                            |             |  |  |

|              |                                                |                  | T<7:0> bits ar | e allowed to ro  | oll over from 00            | h to FFh                   |             |  |  |

|              |                                                | disabled; ARF    |                |                  |                             |                            |             |  |  |

| bit 5-2      | AMASK<3:0                                      | >: Alarm Mask    | Configuration  | bits             |                             |                            |             |  |  |

|              |                                                | y half second    |                |                  |                             |                            |             |  |  |

|              | 0001 = Every second                            |                  |                |                  |                             |                            |             |  |  |

|              | 0010 = Every 10 seconds<br>0011 = Every minute |                  |                |                  |                             |                            |             |  |  |

|              | 0100 = Ever                                    |                  |                |                  |                             |                            |             |  |  |

|              | 0101 = Ever                                    |                  |                |                  |                             |                            |             |  |  |

|              | 0110 = Once<br>0111 = Once                     |                  |                |                  |                             |                            |             |  |  |

|              | 1000 = Once                                    |                  |                |                  |                             |                            |             |  |  |

|              |                                                |                  | t when config  | ured for Febru   | ary 29 <sup>th</sup> , once | every four years           | 5)          |  |  |

|              |                                                | erved - do not   | -              |                  | •                           |                            |             |  |  |

|              |                                                | erved – do not   |                |                  |                             |                            |             |  |  |

| bit 1-0      |                                                | :0>: Alarm Val   | -              |                  |                             |                            |             |  |  |

|              |                                                |                  |                |                  |                             | ALRMVALH ar<br>of ALRMVALH |             |  |  |

|              | '00'.                                          |                  |                |                  | ry lead of white            |                            |             |  |  |

|              | ALRMVAL<1                                      | <u>5:8&gt;:</u>  |                |                  |                             |                            |             |  |  |

|              | 00 = ALRMMIN                                   |                  |                |                  |                             |                            |             |  |  |

|              | 01 = ALRMW                                     |                  |                |                  |                             |                            |             |  |  |

|              | 10 = ALRMM<br>11 = Unimple                     |                  |                |                  |                             |                            |             |  |  |

|              | <u>ALRMVAL&lt;7</u>                            |                  |                |                  |                             |                            |             |  |  |

|              | 00 = ALRMS                                     |                  |                |                  |                             |                            |             |  |  |

|              | 01 = ALRMH                                     |                  |                |                  |                             |                            |             |  |  |

|              | 10 = ALRMD                                     |                  |                |                  |                             |                            |             |  |  |

|              | 11 = Unimple                                   | emented          |                |                  |                             |                            |             |  |  |

# REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER (ACCESS F47h)

#### 20.2 **Control Registers**

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differs significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

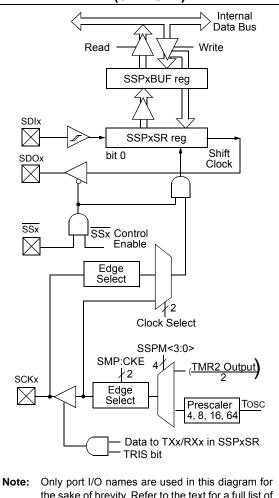

#### 20.3 **SPI Mode**

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in Section 20.4 "SPI DMA Module".

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC7/CCP10/RX1/DT1/SDO1/RP18 or SDO2/Remappable

- · Serial Data In (SDIx) -RB5/CCP5/KBI1/SDI1/SDA1/RP8 or SDI2/Remappable

- Serial Clock (SCKx) RB4/CCP4/KBI0/SCK1/SCL1/RP7 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/C1INC/SS1/ HLVDIN/RCV/RP2 or SS2/Remappable

Figure 20-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### **FIGURE 20-1: MSSPx BLOCK DIAGRAM** (SPI MODE)

the sake of brevity. Refer to the text for a full list of multiplexed functions.

# PIC18F47J53

SSPOV is set because SSPxBUF is still full. ACK is not sent. Bus master terminates transfer ٩ ACK 6 8 D3 Receiving Data 4 D5 D6 6 Note 1: In this example, an address equal to A7, A6, A5, X, A3, X, X will be Acknowledged and cause an interrupt. ACK 8 5 D2 D3 Receiving Data  $^{D4}$ Cleared in software SSPxBUF is read D5 D6 2 ACK R/W = 0 (CKP does not reset to '0' when SEN = 0) A3 eivina Addr × 45 A SSPxIF (PIR1<3> or PIR3<7>) A6 SSPOV (SSPxCON1<6>) CKP (SSPxCON1<4>) Å BF (SSPxSTAT<0>) s SDAX SCLX

# REGISTER 23-1: UCON: USB CONTROL REGISTER (ACCESS F65h)

| U-0   | R/W-0                 | R-x | R/C-0  | R/W-0                | R/W-0  | R/W-0  | U-0   |

|-------|-----------------------|-----|--------|----------------------|--------|--------|-------|

| _     | PPBRST <sup>(2)</sup> | SE0 | PKTDIS | USBEN <sup>(1)</sup> | RESUME | SUSPND | —     |

| bit 7 |                       |     |        |                      |        |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PPBRST: Ping-Pong Buffers Reset bit <sup>(2)</sup>                                                                                                                                                                      |

|       | <ul> <li>1 = Reset all Ping-Pong Buffer Pointers to the Even Buffer Descriptor (BD) banks</li> <li>0 = Ping-Pong Buffer Pointers are not being reset</li> </ul>                                                         |

| bit 5 | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                                    |

|       | <ul> <li>1 = Single-ended zero is active on the USB bus</li> <li>0 = No single-ended zero is detected</li> </ul>                                                                                                        |

| bit 4 | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                                     |

|       | <ul> <li>1 = SIE token and packet processing are disabled, automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing are enabled</li> </ul>                                         |

| bit 3 | USBEN: USB Module Enable bit <sup>(1)</sup>                                                                                                                                                                             |

|       | <ul> <li>1 = USB module and supporting circuitry are enabled (device attached)</li> <li>0 = USB module and supporting circuitry are disabled (device detached)</li> </ul>                                               |

| bit 2 | RESUME: Resume Signaling Enable bit                                                                                                                                                                                     |

|       | <ul><li>1 = Resume signaling is activated</li><li>0 = Resume signaling is disabled</li></ul>                                                                                                                            |

| bit 1 | SUSPND: Suspend USB bit                                                                                                                                                                                                 |

|       | <ul> <li>1 = USB module and supporting circuitry are in Power Conserve mode, SIE clock inactive</li> <li>0 = USB module and supporting circuitry are in normal operation, SIE clocked at the configured rate</li> </ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                                                                                                                              |

- Note 1: Make sure the USB clock source is correctly configured before setting this bit.

- 2: There should be at least four cycles of delay between the setting and PPBRST.

The BDnSTAT byte of the BDT should always be the last byte updated when preparing to arm an endpoint. The SIE will clear the UOWN bit when a transaction has completed.

No hardware mechanism exists to block access when the UOWN bit is set. Thus, unexpected behavior can occur if the microcontroller attempts to modify memory when the SIE owns it. Similarly, reading such memory may produce inaccurate data until the USB peripheral returns ownership to the microcontroller.

#### 23.4.1.2 BDnSTAT Register (CPU Mode)

When UOWN = 0, the microcontroller core owns the BD. At this point, the other seven bits of the register take on control functions.

The Data Toggle Sync Enable bit, DTSEN (BDnSTAT<3>), controls data toggle parity checking. Setting DTSEN enables data toggle synchronization by the SIE. When enabled, it checks the data packet's parity against the value of DTS (BDnSTAT<6>). If a packet arrives with an incorrect synchronization, the data will essentially be ignored. It will not be written to the USB RAM and the USB transfer complete interrupt flag will not be set. The SIE will send an ACK token back to the host to Acknowledge receipt, however. The effects of the DTSEN bit on the SIE are summarized in Table 23-1.

The Buffer Stall bit, BSTALL (BDnSTAT<2>), provides support for control transfers, usually one-time stalls on Endpoint 0. It also provides support for the SET\_FEA-TURE/CLEAR\_FEATURE commands specified in Chapter 9 of the USB Specification; typically, continuous STALLs to any endpoint other than the default control endpoint.

The BSTALL bit enables buffer stalls. Setting BSTALL causes the SIE to return a STALL token to the host if a received token would use the BD in that location. The EPSTALL bit in the corresponding UEPn Control register is set and a STALL interrupt is generated when a STALL is issued to the host. The UOWN bit remains set and the BDs are not changed unless a SETUP token is received. In this case, the STALL condition is cleared and the ownership of the BD is returned to the microcontroller core.

The BCx<9:8> bits (BDnSTAT<1:0>) store the two most significant digits of the SIE byte count. The lower 8 digits are stored in the corresponding BDnCNT register. See **Section 23.4.2 "BD Byte Count"** for more information.

| OUT Packet         | BDnSTAT | Settings | Device Response after Receiving Packet |      |             |                          |  |

|--------------------|---------|----------|----------------------------------------|------|-------------|--------------------------|--|

| from Host          | DTSEN   | DTS      | Handshake                              | UOWN | TRNIF       | BDnSTAT and USTAT Status |  |

| DATA0              | 1       | 0        | ACK                                    | 0    | 1           | Updated                  |  |

| DATA1              | 1       | 0        | ACK                                    | 1    | 0           | Not Updated              |  |

| DATA0              | 1       | 1        | ACK                                    | 1    | 0           | Not Updated              |  |

| DATA1              | 1       | 1        | ACK                                    | 0    | 1           | Updated                  |  |

| Either             | 0       | x        | ACK                                    | 0    | 1           | Updated                  |  |

| Either, with error | х       | NAK      | 1                                      | 0    | Not Updated |                          |  |

# TABLE 23-1: EFFECT OF DTSEN BIT ON ODD/EVEN (DATA0/DATA1) PACKET RECEPTION

**Legend:** x = don't care

#### 23.5.1 USB INTERRUPT STATUS REGISTER (UIR)

The USB Interrupt Status register (Register 23-7) contains the flag bits for each of the USB status interrupt sources. Each of these sources has a corresponding interrupt enable bit in the UIE register. All of the USB status flags are ORed together to generate the USBIF interrupt flag for the microcontroller's interrupt funnel.

Once an interrupt bit has been set by the SIE, it must be cleared in software by writing a '0'. The flag bits can also be set in software, which can aid in firmware debugging. When the USB module is in the Low-Power Suspend mode (UCON<1> = 1), the SIE does not get clocked. When in this state, the SIE cannot process packets, and therefore, cannot detect new interrupt conditions other than the Activity Detect Interrupt, ACTVIF. The ACTVIF bit is typically used by USB firmware to detect when the microcontroller should bring the USB module out of the Low-Power Suspend mode (UCON<1> = 0).

## REGISTER 23-7: UIR: USB INTERRUPT STATUS REGISTER (ACCESS F62h)

| U-0   | R/W-0 | R/W-0   | R/W-0                 | R/W-0                | R/W-0                 | R-0                   | R/W-0  |

|-------|-------|---------|-----------------------|----------------------|-----------------------|-----------------------|--------|

| —     | SOFIF | STALLIF | IDLEIF <sup>(1)</sup> | TRNIF <sup>(2)</sup> | ACTVIF <sup>(3)</sup> | UERRIF <sup>(4)</sup> | URSTIF |

| bit 7 |       |         |                       |                      |                       |                       | bit 0  |

| Legend:           |                 |                                                                |                                                                  |                                                         |

|-------------------|-----------------|----------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------|

| R = Read          | able bit        | W = Writable bit                                               | U = Unimplemented bit                                            | , read as '0'                                           |

| -n = Value at POR |                 | '1' = Bit is set                                               | '0' = Bit is cleared                                             | x = Bit is unknown                                      |

|                   |                 |                                                                |                                                                  |                                                         |

| bit 7             | •               | emented: Read as '0'                                           |                                                                  |                                                         |

| bit 6             |                 | Start-Of-Frame Token Interru                                   | •                                                                |                                                         |

|                   |                 | art-Of-Frame token is receive<br>Start-Of-Frame token is recei |                                                                  |                                                         |

| bit 5             | STALLI          | : A STALL Handshake Interr                                     | rupt bit                                                         |                                                         |

|                   |                 | TALL handshake was sent by<br>TALL handshake has not bee       |                                                                  |                                                         |

| bit 4             | IDLEIF:         | Idle Detect Interrupt bit <sup>(1)</sup>                       |                                                                  |                                                         |

|                   |                 | condition is detected (consta<br>dle condition is detected     | ant Idle state of 3 ms or more)                                  |                                                         |

| bit 3             | TRNIF:          | Transaction Complete Interru                                   | ıpt bit <sup>(2)</sup>                                           |                                                         |

|                   |                 |                                                                | on is complete; read the USTA<br>on is not complete or no transa | T register for endpoint informatio<br>action is pending |

| bit 2             | ACTVIF          | Bus Activity Detect Interrup                                   | t bit <sup>(3)</sup>                                             |                                                         |

|                   |                 | vity on the D+/D- lines was d<br>activity detected on the D+/D |                                                                  |                                                         |

| bit 1             | UERRIF          | : USB Error Condition Interru                                  | ıpt bit <sup>(4)</sup>                                           |                                                         |

|                   |                 | unmasked error condition has<br>unmasked error condition has   |                                                                  |                                                         |

| bit 0             | URSTIF          | USB Reset Interrupt bit                                        |                                                                  |                                                         |

|                   |                 | d USB Reset occurred; 00h i<br>USB Reset has occurred          | s loaded into the UADDR regi                                     | ster                                                    |

| Note 1:           | Once an Idle    | state is detected, the user ma                                 | ay want to place the USB mod                                     | dule in Suspend mode.                                   |

| 2:                | Clearing this   | bit will cause the USTAT FIF                                   | O to advance (valid only for IN                                  | I, OUT and SETUP tokens).                               |

| 3:                | This bit is typ | ically unmasked only followin                                  | g the detection of a UIDLE in                                    | terrupt event.                                          |

| 4:                | Only error co   | nditions enabled through the                                   | UEIE register will set this bit.                                 | This bit is a status bit only and                       |

4: Only error conditions enabled through the UEIE register will set this bit. This bit is a status bit only and cannot be set or cleared by the user.

### 25.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRCON register (Register 25-1). The comparator voltage reference provides two ranges of output voltage, each with 16 distinct levels. The range to be used is selected by the CVRR bit (CVRCON<5>). The primary difference between the ranges is the size of the steps selected by the CVREF Selection bits (CVR<3:0>), with one range offering finer resolution. The equations used to calculate the output of the comparator voltage reference are as follows:

#### EQUATION 25-1: CALCULATING OUTPUT OF THE COMPARATOR VOLTAGE REFERENCE

<u>When CVRR = 1 and CVRSS = 0:</u> CVREF = ((CVR<3:0>)/24) x (CVRSRC) <u>When CVRR = 0 and CVRSS = 0:</u> CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) x (CVRSRC) <u>When CVRR = 1 and CVRSS = 1:</u> CVREF = ((CVR<3:0>)/24) x (CVRSRC) + VREF-<u>When CVRR = 0 and CVRSS = 1:</u> CVREF = (CVRSRC/4) + ((CVR<3:0>)/32) x (CVRSRC) + VREF-) The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF- that are multiplexed with RA2 and RA3. The voltage source is selected by the CVRSS bit (CVRCON<4>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output (see Table 31-2 in **Section 31.0** "**Electrical Characteristics**").

## REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER (F53h)

|                         |                                                                                                                             |                                                                         |                                                                                                                           |                                                                                                    |                  |                 | . ,   |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|-----------------|-------|

| R/W-0                   | R/W-0                                                                                                                       | R/W-0                                                                   | R/W-0                                                                                                                     | R/W-0                                                                                              | R/W-0            | R/W-0           | R/W-0 |

| CVREN                   | CVROE <sup>(1)</sup>                                                                                                        | CVRR                                                                    | CVRSS                                                                                                                     | CVR3                                                                                               | CVR2             | CVR1            | CVR0  |

| bit 7                   |                                                                                                                             |                                                                         |                                                                                                                           |                                                                                                    |                  |                 | bit 0 |

|                         |                                                                                                                             |                                                                         |                                                                                                                           |                                                                                                    |                  |                 |       |

| Legend:                 |                                                                                                                             |                                                                         |                                                                                                                           |                                                                                                    |                  |                 |       |

| R = Readable            | bit                                                                                                                         | W = Writable                                                            | bit                                                                                                                       | U = Unimplem                                                                                       | nented bit, read | l as '0'        |       |

| -n = Value at F         | POR                                                                                                                         | '1' = Bit is set                                                        |                                                                                                                           | '0' = Bit is clea                                                                                  | ared             | x = Bit is unkn | own   |

| bit 7<br>bit 6<br>bit 5 | 1 = CVREF cii<br>0 = CVREF cii<br>CVROE: Com<br>1 = CVREF vc<br>0 = CVREF vc<br>CVRR: Comp<br>1 = 0 to 0.66<br>0 = 0.25 CVR | bltage is discon<br>parator VREF Ra<br>7 CVRSRC with<br>asRC to 0.75 CV | d on<br>d down<br>Dutput Enable<br>Iso output on t<br>nected from th<br>ange Selection<br>CVRSRC/24 ste<br>/RSRC with CVI | bit <sup>(1)</sup><br>he RA2/AN2//C<br>e RA2/AN2//C2<br>bit<br>ep size (low ran<br>RSRC/32 step si | 2INB/C1IND/C3    | BINB/Vref-/CVf  |       |

| bit 4                   | 1 = Compara                                                                                                                 |                                                                         | ource, CVRSR                                                                                                              | on bit<br>c = (VREF+) – (\<br>c = AVDD – AVs                                                       | ,                |                 |       |

| bit 3-0                 | When CVRR<br>CVREF = ((CV<br>When CVRR                                                                                      | <u>= 1:</u><br>/R<3:0>)/24) •                                           | (CVRSRC)                                                                                                                  | ion bits ( $0 \le (CV)$                                                                            | /R<3:0>) ≤ 15)   | )               |       |

**Note 1:** CVROE overrides the TRIS bit setting.

# 26.0 HIGH/LOW VOLTAGE DETECT (HLVD)

The High/Low-Voltage Detect (HLVD) module can be used to monitor the absolute voltage on VDD or the HLVDIN pin. This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point.

If the module detects an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The High/Low-Voltage Detect Control register (Register 26-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

Figure 26-1 provides a block diagram for the HLVD module.

### REGISTER 26-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (ACCESS F85h)

| R/W-0                                                                | R-0   | R-0   | R/W-0  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|----------------------------------------------------------------------|-------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG                                                              | BGVST | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7                                                                |       |       | •      |                       |                       | •                     | bit 0                 |

|                                                                      |       |       |        |                       |                       |                       |                       |

| Legend:                                                              |       |       |        |                       |                       |                       |                       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |        |                       |                       |                       |                       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared              |       |       |        |                       | ared                  | x = Bit is unkr       | nown                  |

| bit 7   | VDIRMAG: Voltage Direction Magnitude Select bit                                                                                                                                                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Event occurs when the voltage equals or exceeds the trip point (HLVDL&lt;3:0&gt;)</li> <li>0 = Event occurs when the voltage equals or falls below the trip point (HLVDL&lt;3:0&gt;)</li> </ul>                                                                                          |

| bit 6   | <b>BGVST:</b> Band Gap Reference Voltages Stable Status Flag bit<br>1 = Indicates internal band gap voltage references is stable<br>0 = Indicates internal band gap voltage reference is not stable                                                                                                   |

| bit 5   | IRVST: Internal Reference Voltage Stable Flag bit                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Indicates that the voltage detect logic will generate the interrupt flag at the specified voltage range</li> <li>0 = Indicates that the voltage detect logic will not generate the interrupt flag at the specified voltage range and the HLVD interrupt should not be enabled</li> </ul> |

| bit 4   | HLVDEN: High/Low-Voltage Detect Power Enable bit                                                                                                                                                                                                                                                      |

|         | <ul><li>1 = HLVD is enabled</li><li>0 = HLVD is disabled</li></ul>                                                                                                                                                                                                                                    |

| bit 3-0 | HLVDL<3:0>: Voltage Detection Limit bits <sup>(1)</sup>                                                                                                                                                                                                                                               |

|         | 1111 = External analog input is used (input comes from the HLVDIN pin)<br>1110 = Maximum setting                                                                                                                                                                                                      |

|         |                                                                                                                                                                                                                                                                                                       |

|         | •                                                                                                                                                                                                                                                                                                     |

|         | •<br>0000 = Minimum setting                                                                                                                                                                                                                                                                           |

|         |                                                                                                                                                                                                                                                                                                       |

Note 1: See Table 31-8 in Section 31.0 "Electrical Characteristics" for specifications.

The module is enabled by setting the HLVDEN bit. Each time the module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit that indicates when the circuit is stable. The module can generate an interrupt only after the circuit is stable and IRVST is set. The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

# TABLE 28-1:MAPPING OF THE FLASH CONFIGURATION WORDS TO THE CONFIGURATION<br/>REGISTERS

| Configuration Register<br>(Volatile) | Configuration Register<br>Address | Flash Configuration Byte Address |

|--------------------------------------|-----------------------------------|----------------------------------|

| CONFIG1L                             | 300000h                           | XXXF8h                           |

| CONFIG1H                             | 300001h                           | XXXF9h                           |

| CONFIG2L                             | 300002h                           | XXXFAh                           |

| CONFIG2H                             | 300003h                           | XXXFBh                           |

| CONFIG3L                             | 300004h                           | XXXFCh                           |

| CONFIG3H                             | 300005h                           | XXXFDh                           |

| CONFIG4L                             | 300006h                           | XXXFEh                           |

| CONFIG4H                             | 300007h                           | XXXFFh                           |

# TABLE 28-2: CONFIGURATION BITS AND DEVICE IDs

| File    | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0    | Default/<br>Unprog.<br>Value <sup>(1)</sup> |

|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|---------------------------------------------|

| 300000h | CONFIG1L | DEBUG    | XINST    | STVREN   | CFGPLLEN | PLLDIV2  | PLLDIV1 | PLLDIV0 | WDTEN    | 1111 1111                                   |

| 300001h | CONFIG1H | (2)      | (2)      | (2)      | (2)      |          | CP0     | CPDIV1  | CPDIV0   | 1111 -111                                   |

| 300002h | CONFIG2L | IESO     | FCMEN    | CLKOEC   | SOSCSEL1 | SOSCSEL0 | FOSC2   | FOSC1   | FOSC0    | 1111 1111                                   |

| 300003h | CONFIG2H | (2)      | (2)      | (2)      | (2)      | WDTPS3   | WDTPS2  | WDTPS1  | WDTPS0   | 1111 1111                                   |

| 300004h | CONFIG3L | DSWDTPS3 | DSWDTPS2 | DSWDTPS1 | DSWDTPS0 | DSWDTEN  | DSBOREN | RTCOSC  | DSWDTOSC | 1111 1111                                   |

| 300005h | CONFIG3H | (2)      | (2)      | (2)      | (2)      | MSSPMSK  | _       | ADCSEL  | IOL1WAY  | 1111 1-11                                   |

| 300006h | CONFIG4L | WPCFG    | WPFP6    | WPFP5    | WPFP4    | WPFP3    | WPFP2   | WPFP1   | WPFP0    | 1111 1111                                   |

| 300007h | CONFIG4H | (2)      | (2)      | (2)      | (2)      | LS48MHZ  | _       | WPEND   | WPDIS    | 1111 1-11                                   |

| 3FFFFEh | DEVID1   | DEV2     | DEV1     | DEV0     | REV4     | REV3     | REV2    | REV1    | REV0     | xxx0 0000 <b>(3)</b>                        |

| 3FFFFFh | DEVID2   | DEV10    | DEV9     | DEV8     | DEV7     | DEV6     | DEV5    | DEV4    | DEV3     | 0100 00xx <b>(3)</b>                        |

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

**Note 1:** Values reflect the unprogrammed state as received from the factory and following Power-on Resets. In all other Reset states, the configuration bytes maintain their previously programmed states.

2: The value of these bits in program memory should always be programmed to '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

3: See Register 28-9 and Register 28-10 for DEVID values. These registers are read-only and cannot be programmed by the user.

# 29.1.1 STANDARD INSTRUCTION SET

| ADDLW                                     | ADD Litera                        | l to W          |      |               | ADDWF                                               |

|-------------------------------------------|-----------------------------------|-----------------|------|---------------|-----------------------------------------------------|

| Syntax:                                   | ADDLW                             | k               |      |               | Syntax:                                             |

| Operands:                                 | $0 \le k \le 255$                 |                 |      |               | Operands:                                           |

| Operation:                                | $(W) + k \rightarrow V$           | N               |      |               |                                                     |

| Status Affected:                          | N, OV, C, D                       | C, Z            |      |               | Operation                                           |

| Encoding:                                 | 0000                              | 1111            | kkkk | kkkk          | Operation:<br>Status Affected:                      |

| Description:                              | The conten<br>8-bit literal<br>W. |                 |      |               | Encoding:<br>Description:                           |

| Words:                                    | 1                                 |                 |      |               |                                                     |

| Cycles:                                   | 1                                 |                 |      |               |                                                     |

| Q Cycle Activity:                         |                                   |                 |      |               |                                                     |

| Q1                                        | Q2                                | Q3              |      | Q4            |                                                     |

| Decode                                    | Read<br>literal 'k'               | Process<br>Data | 5 V  | /rite to<br>W |                                                     |

| Example:                                  |                                   | .5h             |      |               |                                                     |

| Before Instruc<br>W =<br>After Instructio | 10h                               |                 |      |               |                                                     |

| W =                                       | 25h                               |                 |      |               | Words:                                              |

|                                           |                                   |                 |      |               | Cycles:                                             |

|                                           |                                   |                 |      |               | Q Cycle Activit<br>Q1<br>Decode                     |

|                                           |                                   |                 |      |               | Example:<br>Before Inst<br>W<br>REG<br>After Instru |

|                                              | a ∈ [0,1]                                                                                                   | a ∈ [0,1]                                    |                                |                                |                          |  |  |  |  |