#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j53-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                | Pin Nu                     | mber   |                              |                                                           |                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                                       | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN | Pin<br>Type                  | Buffer<br>Type                                            | Description                                                                                                                                                                                        |

|                                                                                                                                |                            |        |                              |                                                           | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups<br>on all inputs.                                                                                |

| RB0/AN12/C3IND/INT0/RP3<br>RB0<br>AN12<br>C3IND<br>INT0<br>RP3                                                                 | 21                         | 18     | I/O<br>I<br>I<br>I/O         | TTL/DIG<br>Analog<br>Analog<br>ST<br>ST/DIG               | Digital I/O.<br>Analog Input 12.<br>Comparator 3 Input D.<br>External Interrupt 0.<br>Remappable Peripheral Pin 3 input/output.                                                                    |

| RB1/AN10/C3INC/RTCC/RP4<br>RB1<br>AN10<br>C3INC<br>RTCC<br>RP4                                                                 | 22                         | 19     | I/O<br>I<br>I<br>O<br>I/O    | TTL/DIG<br>Analog<br>Analog<br>DIG<br>ST/DIG              | Digital I/O.<br>Analog Input 10.<br>Comparator 3 input.<br>Asynchronous serial transmit data output.<br>Remappable Peripheral Pin 4 input/output.                                                  |

| RB2/AN8/C2INC/CTED1/<br>VMO/REFO/RP5<br>RB2<br>AN8<br>C2INC<br>CTED1<br>VMO<br>REFO<br>RP5                                     | 23                         | 20     | I/O<br> <br> <br> <br>0 0 /O | TTL/DIG<br>Analog<br>Analog<br>ST<br>DIG<br>DIG<br>ST/DIG | Digital I/O.<br>Analog Input 8.<br>Comparator 2 Input C.<br>CTMU Edge 1 input.<br>External USB Transceiver D- data output.<br>Reference output clock.<br>Remappable Peripheral Pin 5 input/output. |

| RB3/AN9/C3INA/CTED2/<br>VPO/RP6<br>RB3<br>AN9<br>C3INA<br>CTED2<br>VPO<br>RP6                                                  | 24                         | 21     | I/O<br> <br> <br> <br>0      | TTL/DIG<br>Analog<br>Analog<br>ST<br>DIG<br>ST/DIG        | Digital I/O.<br>Analog Input 9.<br>Comparator 3 Input A.<br>CTMU edge 2 Input.<br>External USB Transceiver D+ data output.<br>Remappable Peripheral Pin 6 input/output.                            |

| Legend: TTL = TTL compati<br>ST = Schmitt Trigg<br>I = Input<br>P = Power<br>DIG = Digital outpu<br>Note 1: RA7 and RA6 will b | ger input wi<br>t          |        |                              | Ar<br>O<br>OI<br>I <sup>2</sup> (                         | MOS = CMOS compatible input or output<br>nalog = Analog input<br>= Output<br>D = Open-Drain (no P diode to VDD)                                                                                    |

### TABLE 1-3: PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

| REGISTER 3-1: | OSCTUNE: OSCILLATOR TUNING REGISTER (ACCESS F9Bh) |

|---------------|---------------------------------------------------|

|               |                                                   |

| R/W-0           | R/W-0                          | R/W-0                             | R/W-0                         | R/W-0                                                 | R/W-0            | R/W-0           | R/W-0 |

|-----------------|--------------------------------|-----------------------------------|-------------------------------|-------------------------------------------------------|------------------|-----------------|-------|

| INTSRC          | PLLEN <sup>(1)</sup>           | TUN5                              | TUN4                          | TUN3                                                  | TUN2             | TUN1            | TUN0  |

| bit 7           |                                |                                   |                               |                                                       |                  |                 | bit ( |

| Legend:         |                                |                                   |                               |                                                       |                  |                 |       |

| R = Readable b  | oit                            | W = Writable                      | bit                           | U = Unimplen                                          | nented bit, read | l as '0'        |       |

| -n = Value at P | OR                             | '1' = Bit is set                  |                               | '0' = Bit is clea                                     | ared             | x = Bit is unkr | nown  |

| bit 7<br>bit 6  | 1 = 31.25 kHz<br>0 = 31 kHz de | z device clock o                  | lerived from a ved directly f | cy Source Sele<br>8 MHz INTOSC<br>rom INTRC inte<br>) | source (divide-  | by-256 enable   | d)    |

|                 | 1 = 96 MHz P                   | PLL is enabled<br>PLL is disabled |                               |                                                       |                  |                 |       |

| bit 5-0         |                                | requency Tunir<br>iximum frequer  | •                             |                                                       |                  |                 |       |

**Note 1:** When the CFGPLLEN Configuration bit is used to enable the PLL, clearing OSCTUNE<6> will not disable the PLL.

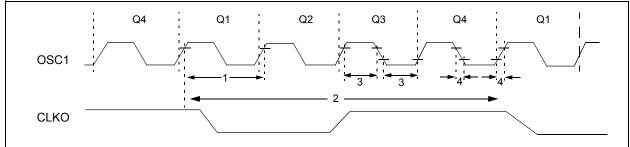

#### 3.3 Oscillator Settings for USB

When the PIC18F47J53 family devices are used for USB connectivity, a 6 MHz or 48 MHz clock must be provided to the USB module for operation in either Low-Speed or Full-Speed modes, respectively. This may require some forethought in selecting an oscillator frequency and programming the device.

The full range of possible oscillator configurations compatible with USB operation is shown in Table 3-5.

#### 3.3.1 LOW-SPEED OPERATION

The USB clock for Low-Speed mode is derived from the primary oscillator or from the 96 MHz PLL. In order to operate the USB module in Low-Speed mode, a 6 MHz clock must be provided to the USB module.

See Table 3-4 and Table 3-5 for possible combinations which can be used for low-speed USB operation.

| System Clock CPDIV<1:0> |    | CPDIV<1:0> Microcontroller Clock |   | USB Clock    |  |  |  |  |

|-------------------------|----|----------------------------------|---|--------------|--|--|--|--|

| 48                      | 11 | 48 MHz                           | 1 | 48/8 = 6 MHz |  |  |  |  |

| 48                      | 10 | 48/2 = 24 MHz                    | 1 | 48/8 = 6 MHz |  |  |  |  |

| 48                      | 01 | 48/3 = 16 MHz                    | 1 | 48/8 = 6 MHz |  |  |  |  |

| 48                      | 00 | 48/6 = 8 MHz                     | 1 | 48/8 = 6 MHz |  |  |  |  |

| 24                      | 11 | 24 MHz                           | 0 | 24/4 = 6 MHz |  |  |  |  |

| 24                      | 10 | 24/2 = 12 MHz                    | 0 | 24/4 = 6 MHz |  |  |  |  |

| 24                      | 01 | 24/3 = 8 MHz                     | 0 | 24/4 = 6 MHz |  |  |  |  |

| 24                      | 00 | 24/6 = 4 MHz                     | 0 | 24/4 = 6 MHz |  |  |  |  |

| TABLE 3-4: | CLOCK FOR LOW-SPEED USB |

|------------|-------------------------|

|------------|-------------------------|

#### 4.6.2 I/O PINS DURING DEEP SLEEP

During Deep Sleep, the general purpose I/O pins will retain their previous states.

Pins that are configured as inputs (TRIS bit set) prior to entry into Deep Sleep will remain high-impedance during Deep Sleep.

Pins that are configured as outputs (TRIS bit clear) prior to entry into Deep Sleep will remain as output pins during Deep Sleep. While in this mode, they will drive the output level determined by their corresponding LAT bit at the time of entry into Deep Sleep.

When the device wakes back up, the I/O pin behavior depends on the type of wake up source.

If the device wakes back up by an RTCC alarm, INT0 interrupt, DSWDT or ULPWU event, all I/O pins will continue to maintain their previous states, even after the device has finished the POR sequence and is executing application code again. Pins configured as inputs during Deep Sleep will remain high-impedance, and pins configured as outputs will continue to drive their previous value.

After waking up, the TRIS and LAT registers will be reset, but the I/O pins will still maintain their previous states. If firmware modifies the TRIS and LAT values for the I/O pins, they will not immediately go to the newly configured states. Once the firmware clears the RELEASE bit (DSCONL<0>), the I/O pins will be "released". This causes the I/O pins to take the states configured by their respective TRIS and LAT bit values.

If the Deep Sleep BOR (DSBOR) circuit is enabled, and VDD drops below the DSBOR and VDD rail POR thresholds, the I/O pins will be immediately released similar to clearing the RELEASE bit. All previous state information will be lost, including the general purpose DSGPR0 and DSGPR1 contents. See **Section 4.6.5** "**Deep Sleep Brown-Out Reset (DSBOR)**" for additional details regarding this scenario

If a MCLR Reset event occurs during Deep Sleep, the I/O pins will also be released automatically, but in this case, the DSGPR0 and DSGPR1 contents will remain valid.

In all other Deep Sleep wake-up cases, application firmware needs to clear the RELEASE bit in order to reconfigure the I/O pins.

#### 4.6.3 DEEP SLEEP WAKE-UP SOURCES

The device can be awakened from Deep Sleep mode by a MCLR, POR, RTCC, INTO I/O pin interrupt, DSWDT or ULPWU event. After waking, the device performs a POR. When the device is released from Reset, code execution will begin at the device's Reset vector.

The software can determine if the wake-up was caused from an exit from Deep Sleep mode by reading the DS bit (WDTCON<3>). If this bit is set, the POR was caused by a Deep Sleep exit. The DS bit must be manually cleared by the software.

The software can determine the wake event source by reading the DSWAKEH and DSWAKEL registers. When the application firmware is done using the DSWAKEH and DSWAKEL status registers, individual bits do not need to be manually cleared before entering Deep Sleep again. When entering Deep Sleep mode, these registers are automatically cleared.

#### 4.6.3.1 Wake-up Event Considerations

Deep Sleep wake-up events are only monitored while the processor is fully in Deep Sleep mode. If a wake-up event occurs before Deep Sleep mode is entered, the event status will not be reflected in the DSWAKE registers. If the wake-up source asserts prior to entering Deep Sleep, the CPU will either go to the interrupt vector (if the wake source has an interrupt bit and the interrupt is fully enabled) or will abort the Deep Sleep entry sequence by executing past the SLEEP instruction if the interrupt was not enabled. In this case, a wake-up event handler should be placed after the SLEEP instruction to process the event and re-attempt entry into Deep Sleep if desired.

When the device is in Deep Sleep with more than one wake-up source simultaneously enabled, only the first wake-up source to assert will be detected and logged in the DSWAKEH/DSWAKEL status registers.

#### 4.6.4 DEEP SLEEP WATCHDOG TIMER (DSWDT)

Deep Sleep has its own dedicated WDT (DSWDT) with a postscaler for time-outs of 2.1 ms to 25.7 days, configurable through the bits, DSWDTPS<3:0>.

The DSWDT can be clocked from either the INTRC or the T1OSC/T1CKI input. If the T1OSC/T1CKI source will be used with a crystal, the T1OSCEN bit in the T1CON register needs to be set prior to entering Deep Sleep. The reference clock source is configured through the DSWDTOSC bit.

DSWDT is enabled through the DSWDTEN bit. Entering Deep Sleep mode automatically clears the DSWDT. See **Section 28.0 "Special Features of the CPU**" for more information.

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                                   |        |                                 |  |  |  |  |

|------------|---------------------------------------------------------|-------------|-----------------------------------------------------------------------------------|--------|---------------------------------|--|--|--|--|

| Register   | Applicable Devices                                      |             | Applicable Devices Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep |        | Wake-up via WDT<br>or Interrupt |  |  |  |  |

| RPINR22    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR21    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR17    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR16    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR14    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR13    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR12    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR9     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR8     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR7     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR15    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR6     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR4     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR3     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR2     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPINR1     | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                                            | 1 1111 | u uuuu                          |  |  |  |  |

| RPOR24     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR23     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR22     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR21     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR20     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR19     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR18     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR17     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR13     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR12     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR11     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR10     | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR9      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR8      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR7      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

| RPOR6      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                                            | 0 0000 | u uuuu                          |  |  |  |  |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

## 9.0 INTERRUPTS

Devices of the PIC18F47J53 family have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are 19 registers, which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3, PIR4, PIR5

- PIE1, PIE2, PIE3, PIE4, PIE5

- IPR1, IPR2, IPR3, IPR4, IPR5

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address, 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a low-priority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine (ISR), the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the Interrupt Control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 12-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 12-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER (ACCESS FD5h)

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                      |                                                            |                               |                    |  |  |  |

|------------|----------------------|------------------------------------------------------------|-------------------------------|--------------------|--|--|--|

| R = Reada  | ble bit              | W = Writable bit                                           | U = Unimplemented bit,        | read as '0'        |  |  |  |

| -n = Value | at POR               | '1' = Bit is set                                           | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |

|            |                      |                                                            |                               |                    |  |  |  |

| bit 7      | TMR0ON               | I: Timer0 On/Off Control bit                               |                               |                    |  |  |  |

|            | 1 = Enab             | les Timer0                                                 |                               |                    |  |  |  |

|            | 0 = Stops            | s Timer0                                                   |                               |                    |  |  |  |

| bit 6      | <b>T08BIT</b> : 7    | Timer0 8-Bit/16-Bit Control bi                             | t                             |                    |  |  |  |

|            | 1 = Timei            | r0 is configured as an 8-bit ti                            | mer/counter                   |                    |  |  |  |

|            | 0 = Timei            | r0 is configured as a 16-bit ti                            | mer/counter                   |                    |  |  |  |

| bit 5      | TOCS: Ti             | mer0 Clock Source Select bit                               | t                             |                    |  |  |  |

|            | 1 = Trans            | sition on TOCKI pin                                        |                               |                    |  |  |  |

|            |                      | nal instruction cycle clock (CL                            | -KO)                          |                    |  |  |  |

| bit 4      | TOSE: Tir            | mer0 Source Edge Select bit                                |                               |                    |  |  |  |

|            | 1 = Incre            | ment on high-to-low transition                             | n on T0CKI pin                |                    |  |  |  |

|            | 0 = Incre            | ment on low-to-high transition                             | n on T0CKI pin                |                    |  |  |  |

| bit 3      | PSA: Tim             | ner0 Prescaler Assignment bi                               | t                             |                    |  |  |  |

|            | 1 = Timei            | r0 prescaler is not assigned.                              | Timer0 clock input bypasses p | orescaler.         |  |  |  |

|            | 0 = Timei            | r0 prescaler is assigned. Tim                              | er0 clock input comes from pr | escaler output.    |  |  |  |

| bit 2-0    | T0PS<2:              | 0>: Timer0 Prescaler Select                                | bits                          |                    |  |  |  |

|            | 111 <b>= 1</b> :2    | 111 = 1:256 Prescale value                                 |                               |                    |  |  |  |

|            | 110 <b>= 1</b> :1    | 128 Prescale value                                         |                               |                    |  |  |  |

|            |                      | 64 Prescale value                                          |                               |                    |  |  |  |

|            |                      | 32 Prescale value                                          |                               |                    |  |  |  |

|            |                      | 16 Prescale value                                          |                               |                    |  |  |  |

|            |                      | <ul> <li>Prescale value</li> <li>Prescale value</li> </ul> |                               |                    |  |  |  |

|            | 001 = 12<br>000 = 12 |                                                            |                               |                    |  |  |  |

## 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on ECCP Special Event Trigger

- Device clock status flag (SOSCRUN)

- · Timer with gated control

Figure 13-1 displays a simplified block diagram of the Timer1 module.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Fosc clock source (TMR1CS<1:0> = 01) should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER (ACCESS FCDh)

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0 | R/W-0  |

|---------|---------|---------|---------|---------|--------|-------|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | RD16  | TMR10N |

| bit 7   |         |         |         |         |        |       | bit 0  |

| Legend:   |                                                                            |                                                                                                                                       |                                                                                  |                                 |

|-----------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|

| R = Read  | dable bit                                                                  | W = Writable bit                                                                                                                      | U = Unimplemented bit,                                                           | read as '0'                     |

| -n = Valu | e at POR                                                                   | '1' = Bit is set                                                                                                                      | '0' = Bit is cleared                                                             | x = Bit is unknown              |

| bit 7-6   | 10 = Timer<br>01 = Timer                                                   | <b>1:0&gt;:</b> Timer1 Clock Source S<br>1 clock source is the T1OSC<br>1 clock source is the system<br>1 clock source is the instruc | C or T1CKI pin<br>i clock (Fosc) <sup>(1)</sup>                                  |                                 |

| bit 5-4   | 11 = 1:8 P<br>10 = 1:4 P<br>01 = 1:2 P                                     | I:0>: Timer1 Input Clock Pre<br>rescale value<br>rescale value<br>rescale value<br>rescale value<br>rescale value                     | escale Select bits                                                               |                                 |

| bit 3     | <u>When TMF</u><br>1 = Power<br>0 = Timer1<br><u>When TMF</u><br>1 = Power |                                                                                                                                       | elect bit<br>and supply the Timer1 clock fro<br>clock is from the T1CKI input pi |                                 |

| bit 2     | <u>TMR1CS&lt;</u><br>1 = Do not<br>0 = Synchr<br><u>TMR1CS&lt;</u>         | synchronize external clock i<br>onize external clock input<br>1:0> = 0x:                                                              | -                                                                                | > = 0x.                         |

| bit 1     | 1 = Enable                                                                 | Bit Read/Write Mode Enable<br>es register read/write of Time<br>es register read/write of Time                                        | er1 in one 16-bit operation                                                      |                                 |

| bit 0     | <b>TMR1ON:</b><br>1 = Enable<br>0 = Stops                                  |                                                                                                                                       |                                                                                  |                                 |

| Note 1:   | The Fosc cl                                                                | ock source should not be sele                                                                                                         | cted if the timer will be used with                                              | the ECCP capture/compare featur |

2: The Timer1 oscillator crystal driver is powered whenever T1OSCEN (T1CON<3>) or T3OSCEN (T3CON<3>) = 1. The circuit is enabled by the logical OR of these two bits. When disabled, the inverter and feedback resistor are disabled to eliminate power drain. The TMR1ON and TMR3ON bits do not have to be enabled to power up the crystal driver.

# REGISTER 16-1: TxCON: TIMER4/6/8 CONTROL REGISTER (ACCESS F76h, BANKED F1Eh, BANKED F1Bh)

| <b></b> |          |          |          |          |        |         |         |

|---------|----------|----------|----------|----------|--------|---------|---------|

| bit 7   |          |          |          |          |        |         | bit 0   |

| —       | TxOUTPS3 | TxOUTPS2 | TxOUTPS1 | TxOUTPS0 | TMRxON | TxCKPS1 | TxCKPS0 |

| U-0     | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                        |

|---------|---------------------------------------------------|

| bit 6-3 | TxOUTPS<3:0>: Timerx Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         | •                                                 |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMRxON: Timerx On bit                             |

|         | 1 = Timerx is on                                  |

|         | 0 = Timerx is off                                 |

| bit 1-0 | TxCKPS<1:0>: Timerx Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 1x = Prescaler is 16                              |

|         |                                                   |

### 16.2 Timer4/6/8 Interrupt

The Timer4/6/8 modules have 8-bit Period registers, PRx, that are both readable and writable. Timer4/6/8 increment from 00h until they match PR4/6/8 and then reset to 00h on the next increment cycle. The PRx registers are initialized to FFh upon Reset.

### 16.3 Output of TMRx

The outputs of TMRx (before the postscaler) are used only as a PWM time base for the ECCP modules. They are not used as baud rate clocks for the MSSP modules as is the Timer2 output.

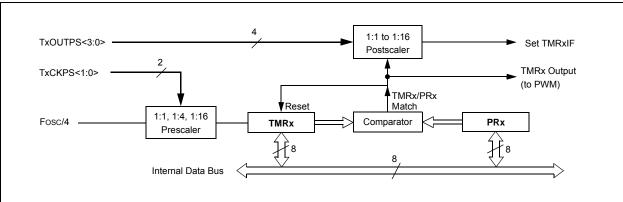

#### FIGURE 16-1: TIMER4 BLOCK DIAGRAM

## 17.1 RTCC MODULE REGISTERS

The RTCC module registers are divided into following categories:

### **RTCC Control Registers**

- RTCCFG

- RTCCAL

- PADCFG1

- ALRMCFG

- ALRMRPT

## **RTCC Value Registers**

- RTCVALH and RTCVALL Can access the following registers

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOUR

- MINUTE

- SECOND

#### **Alarm Value Registers**

- ALRMVALH and ALRMVALL Can access the following registers:

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

- Note: The RTCVALH and RTCVALL registers can be accessed through RTCRPT<1:0>. ALRMVALH and ALRMVALL can be accessed through ALRMPTR<1:0>.

| Name     | Bit 7                     | Bit 6         | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |  |  |  |  |  |

|----------|---------------------------|---------------|----------|----------|----------|----------|----------|----------|--|--|--|--|--|

| INTCON   | GIE/GIEH                  | PEIE/GIEL     | TMR0IE   | INT0IE   | RBIE     | TMR0IF   | INT0IF   | RBIF     |  |  |  |  |  |

| RCON     | IPEN                      | _             | CM       | RI       | TO       | PD       | POR      | BOR      |  |  |  |  |  |

| PIR4     | CCP10IF                   | CCP9IF        | CCP8IF   | CCP7IF   | CCP6IF   | CCP5IF   | CCP4IF   | CCP3IF   |  |  |  |  |  |

| PIE4     | CCP10IE                   | CCP9IE        | CCP8IE   | CCP7IE   | CCP6IE   | CCP5IE   | CCP4IE   | CCP3IE   |  |  |  |  |  |

| IPR4     | CCP10IP                   | CCP9IP        | CCP8IP   | CCP7IP   | CCP6IP   | CCP5IP   | CCP4IP   | CCP3IP   |  |  |  |  |  |

| TRISB    | TRISB7                    | TRISB6        | TRISB5   | TRISB4   | TRISB3   | TRISB2   | TRISB1   | TRISB0   |  |  |  |  |  |

| TRISC    | TRISC7                    | TRISC6        |          |          |          | TRISC2   | TRISC1   | TRISC0   |  |  |  |  |  |

| TRISE    | RDPU                      | REPU          |          | _        |          | TRISE2   | TRISE1   | TRISE0   |  |  |  |  |  |

| TMR1L    | Timer1 Register Low Byte  |               |          |          |          |          |          |          |  |  |  |  |  |

| TMR1H    | Timer1 Register High Byte |               |          |          |          |          |          |          |  |  |  |  |  |

| TMR3L    | Timer3 Register Low Byte  |               |          |          |          |          |          |          |  |  |  |  |  |

| TMR3H    | Timer3 Register High Byte |               |          |          |          |          |          |          |  |  |  |  |  |

| TMR5L    | Timer5 Register Low Byte  |               |          |          |          |          |          |          |  |  |  |  |  |

| TMR5H    | Timer5 Regi               | ster High Byt | е        |          |          |          |          |          |  |  |  |  |  |

| T1CON    | TMR1CS1                   | TMR1CS0       | T1CKPS1  | T1CKPS0  | T1OSCEN  | T1SYNC   | RD16     | TMR10N   |  |  |  |  |  |

| T3CON    | TMR3CS1                   | TMR3CS0       | T3CKPS1  | T3CKPS0  | T3OSCEN  | T3SYNC   | RD16     | TMR3ON   |  |  |  |  |  |

| T5CON    | TMR5CS1                   | TMR5CS0       | T5CKPS1  | T5CKPS0  | T5OSCEN  | T5SYNC   | RD16     | TMR5ON   |  |  |  |  |  |

| CCPR4L   | CCPR4L7                   | CCPR4L6       | CCPR4L5  | CCPR4L4  | CCPR4L3  | CCPR4L2  | CCPR4L1  | CCPR4L0  |  |  |  |  |  |

| CCPR4H   | CCPR4H7                   | CCPR4H6       | CCPR4H5  | CCPR4H4  | CCPR4H3  | CCPR4H2  | CCPR4H1  | CCPR4H0  |  |  |  |  |  |

| CCPR5L   | CCPR5L7                   | CCPR5L6       | CCPR5L5  | CCPR5L4  | CCPR5L3  | CCPR5L2  | CCPR5L1  | CCPR5L0  |  |  |  |  |  |

| CCPR5H   | CCPR5H7                   | CCPR5H6       | CCPR5H5  | CCPR5H4  | CCPR5H3  | CCPR5H2  | CCPR5H1  | CCPR5H0  |  |  |  |  |  |

| CCPR6L   | CCPR6L7                   | CCPR6L6       | CCPR6L5  | CCPR6L4  | CCPR6L3  | CCPR6L2  | CCPR6L1  | CCPR6L0  |  |  |  |  |  |

| CCPR6H   | CCPR6H7                   | CCPR6H6       | CCPR6H5  | CCPR6H4  | CCPR6H3  | CCPR6H2  | CCPR6H1  | CCPR6H0  |  |  |  |  |  |

| CCPR7L   | CCPR7L7                   | CCPR7L6       | CCPR7L5  | CCPR7L4  | CCPR7L3  | CCPR7L2  | CCPR7L1  | CCPR7L0  |  |  |  |  |  |

| CCPR7H   | CCPR7H7                   | CCPR7H6       | CCPR7H5  | CCPR7H4  | CCPR7H3  | CCPR7H2  | CCPR7H1  | CCPR7H0  |  |  |  |  |  |

| CCPR8L   | CCPR8L7                   | CCPR8L6       | CCPR8L5  | CCPR8L4  | CCPR8L3  | CCPR8L2  | CCPR8L1  | CCPR8L0  |  |  |  |  |  |

| CCPR8H   | CCPR8H7                   | CCPR8H6       | CCPR8H5  | CCPR8H4  | CCPR8H3  | CCPR8H2  | CCPR8H1  | CCPR8H0  |  |  |  |  |  |

| CCPR9L   | CCPR9L7                   | CCPR9L6       | CCPR9L5  | CCPR9L4  | CCPR9L3  | CCPR9L2  | CCPR9L1  | CCPR9L0  |  |  |  |  |  |

| CCPR9H   | CCPR9H7                   | CCPR9H6       | CCPR9H5  | CCPR9H4  | CCPR9H3  | CCPR9H2  | CCPR9H1  | CCPR9H0  |  |  |  |  |  |

| CCPR10L  | CCPR10L7                  | CCPR10L6      | CCPR10L5 | CCPR10L4 | CCPR10L3 | CCPR10L2 | CCPR10L1 | CCPR10L0 |  |  |  |  |  |

| CCPR10H  | CCPR10H7                  | CCPR10H6      | CCPR10H5 | CCPR10H4 | CCPR10H3 | CCPR10H2 | CCPR10H1 | CCPR10H0 |  |  |  |  |  |

| CCP4CON  | —                         | _             | DC4B1    | DC4B0    | CCP4M3   | CCP4M2   | CCP4M1   | CCP4M0   |  |  |  |  |  |

| CCP5CON  | _                         |               | DC5B1    | DC5B0    | CCP5M3   | CCP5M2   | CCP5M1   | CCP5M0   |  |  |  |  |  |

| CCP6CON  | _                         |               | DC6B1    | DC6B0    | CCP6M3   | CCP6M2   | CCP6M1   | CCP6M0   |  |  |  |  |  |

| CCP7CON  | —                         |               | DC7B1    | DC7B0    | CCP7M3   | CCP7M2   | CCP7M1   | CCP7M0   |  |  |  |  |  |

| CCP8CON  | —                         | —             | DC8B1    | DC8B0    | CCP8M3   | CCP8M2   | CCP8M1   | CCP8M0   |  |  |  |  |  |

| CCP9CON  | —                         | —             | DC9B1    | DC9B0    | CCP9M3   | CCP9M2   | CCP9M1   | CCP9M0   |  |  |  |  |  |

| CCP10CON | —                         | _             | DC10B1   | DC10B0   | CCP10M3  | CCP10M2  | CCP10M1  | CCP10M0  |  |  |  |  |  |

| CCPTMRS1 | C7TSEL1                   | C7TSEL0       |          | C6TSEL0  | —        | C5TSEL0  | C4TSEL1  | C4TSEL0  |  |  |  |  |  |

| CCPTMRS2 | —                         | —             | _        | C10TSEL0 | _        | C9TSEL0  | C8TSEL1  | C8TSEL0  |  |  |  |  |  |

| TABLE 10-4. REGISTERS ASSOCIATED WITH CAFTURE, COWFARE, HWER 1/3/3/1 | TABLE 18-4: | <b>REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1/3/5/7</b> |

|----------------------------------------------------------------------|-------------|-----------------------------------------------------------------|

|----------------------------------------------------------------------|-------------|-----------------------------------------------------------------|

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare or Timer1/3/5.

#### 19.4.5 AUTO-RESTART MODE

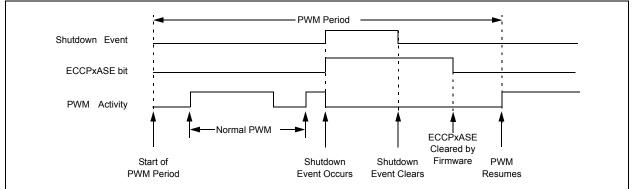

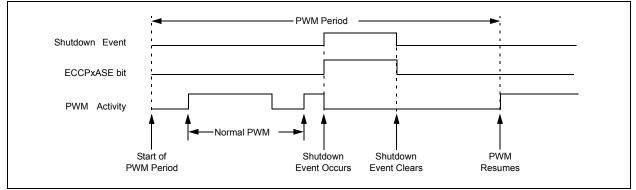

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit (ECCPxDEL<7>).

If auto-restart is enabled, the ECCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPxASE bit will be cleared via hardware and normal operation will resume. The module will wait until the next PWM period begins, however, before re-enabling the output pin. This behavior allows the auto-shutdown with auto-restart features to be used in applications based on the current mode of PWM control.

### FIGURE 19-13: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PxRSEN = 1)

# 19.4.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be immediately stable.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCPx module without change.

#### 19.4.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC RUN mode and the OSCFIF bit of the PIR2 register

will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

#### 19.4.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced CCP modules used on other PIC18 and PIC16 devices.

| TABLE 19-4: | <b>REGISTERS ASSOCIATED WITH ECCP1/2/3 MODULE AND</b> |

|-------------|-------------------------------------------------------|

|             | TIMER1/2/3/4/6/8                                      |

| File Name | Bit 7           | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1         | Bit 0   |

|-----------|-----------------|-----------|----------|----------|----------|--------|---------------|---------|

| INTCON    | GIE/GIEH        | PEIE/GIEL | TMR0IE   | INT0IE   | RBIE     | TMR0IF | <b>INT0IF</b> | RBIF    |

| RCON      | IPEN            |           | CM       | RI       | TO       | PD     | POR           | BOR     |

| PIR1      | PMPIF           | ADIF      | RC1IF    | TX1IF    | SSP1IF   | CCP1IF | TMR2IF        | TMR1IF  |

| PIR2      | OSCFIF          | CM2IF     | CM1IF    | USBIF    | BCL1IF   | HLVDIF | TMR3IF        | CCP2IF  |

| PIR4      | CCP10IF         | CCP9IF    | CCP8IF   | CCP7IF   | CCP6IF   | CCP5IF | CCP4IF        | CCP3IF  |

| PIE1      | PMPIE           | ADIE      | RC1IE    | TX1IE    | SSP1IE   | CCP1IE | TMR2IE        | TMR1IE  |

| PIE2      | OSCFIE          | CM2IE     | CM1IE    | USBIE    | BCL1IE   | HLVDIE | TMR3IE        | CCP2IE  |

| PIE4      | CCP10IE         | CCP9IE    | CCP8IE   | CCP7IE   | CCP6IE   | CCP5IE | CCP4IE        | CCP3IE  |

| IPR1      | PMPIP           | ADIP      | RC1IP    | TX1IP    | SSP1IP   | CCP1IP | TMR2IP        | TMR1IP  |

| IPR2      | OSCFIP          | CM2IP     | CM1IP    | USBIP    | BCL1IP   | HLVDIP | TMR3IP        | CCP2IP  |

| IPR4      | CCP10IP         | CCP9IP    | CCP8IP   | CCP7IP   | CCP6IP   | CCP5IP | CCP4IP        | CCP3IP  |

| TRISB     | TRISB7          | TRISB6    | TRISB5   | TRISB4   | TRISB3   | TRISB2 | TRISB1        | TRISB0  |

| TRISC     | TRISC7          | TRISC6    | _        | _        | —        | TRISC2 | TRISC1        | TRISC0  |

| TRISE     | RDPU            | REPU      |          |          | —        | TRISE2 | TRISE1        | TRISE0  |

| TMR1H     | Timer1 Register | High Byte |          |          |          |        |               |         |

| TMR1L     | Timer1 Register | Low Byte  |          |          |          |        |               |         |

| TMR2      | Timer2 Register |           |          |          |          |        |               |         |

| TMR3H     | Timer3 Register | High Byte |          |          |          |        |               |         |

| TMR3L     | Timer3 Register | Low Byte  |          |          |          |        |               |         |

| TMR4      | Timer4 Register |           |          |          |          |        |               |         |

| TMR6      | Timer6 Register |           |          |          |          |        |               |         |

| TMR8      | Timer8 Register |           |          |          |          |        |               |         |

| PR2       | Timer2 Period R | Register  |          |          |          |        |               |         |

| PR4       | Timer4 Period R | Register  |          |          |          |        |               |         |

| PR6       | Timer6 Period R | Register  |          |          |          |        |               |         |

| PR8       | Timer8 Period R | Register  |          |          |          |        |               |         |

| T1CON     | TMR1CS1         | TMR1CS0   | T1CKPS1  | T1CKPS0  | T1OSCEN  | T1SYNC | RD16          | TMR10N  |

| T2CON     |                 | T2OUTPS3  | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1       | T2CKPS0 |

| T3CON     | TMR3CS1         | TMR3CS0   | T3CKPS1  | T3CKPS0  | T3OSCEN  | T3SYNC | RD16          | TMR3ON  |

| T4CON     | —               | T4OUTPS3  | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1       | T4CKPS0 |

| T6CON     |                 | T6OUTPS3  | T6OUTPS2 | T6OUTPS1 | T6OUTPS0 | TMR6ON | T6CKPS1       | T6CKPS0 |

© 2009-2016 Microchip Technology Inc.

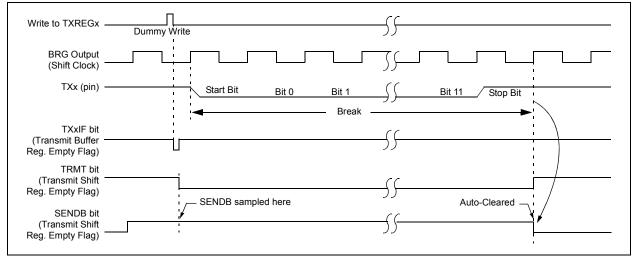

### 21.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTAx<3> and TXSTAx<5>) are set while the Transmit Shift Register is loaded with data.

Note that the value of data written to TXREGx will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREGx for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 21-10 for the timing of the Break character sequence.

#### 21.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREGx with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREGx to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREGx becomes empty, as indicated by the TXxIF, the next data byte can be written to TXREGx.

#### 21.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 of the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 21.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RXx/DTx, cause an RCxIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABDEN bit once the TXxIF interrupt is observed.

#### FIGURE 21-10: SEND BREAK CHARACTER SEQUENCE

## 22.0 10/12-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module in the PIC18F47J53 family of devices has 10 inputs for the 28-pin devices and 13 inputs for the 44-pin devices. This module allows conversion of an analog input signal to a corresponding 10 or 12-bit digital number.

The module has these registers:

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Port Configuration Register 0 (ANCON0)

- A/D Port Configuration Register 1 (ANCON1)

- A/D Result Registers (ADRESH and ADRESL)

- A/D Trigger Register (ADCTRIG)

- Configuration Register 3 High (ADCSEL, CON-FIG3H<1>)

The ADCON0 register, shown in Register 22-1, controls the operation of the A/D module.

The ADCON1 register, shown in Register 22-1, configures the A/D clock source, programmed acquisition time and justification. The ANCON0 and ANCON1 registers, in Register 22-1 and Register 22-2, configure the functions of the port pins.

The ADCSEL Configuration bit (CONFIG3H<1>) sets the module for 10 or 12-bit conversions. The 10-Bit Conversion mode is useful for applications that favor conversion speed over conversion resolution.

| MULLW                                  | Multiply L                  | iteral with W                                                          |                                             | MULWF                     | Multiply W w                                                                                                                                                                                                                                                                                         | rith f                                                                             |                                             |  |

|----------------------------------------|-----------------------------|------------------------------------------------------------------------|---------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|--|

| Syntax:                                | MULLW                       | k                                                                      |                                             | Syntax:                   | MULWF f{                                                                                                                                                                                                                                                                                             | ,a}                                                                                |                                             |  |

| Operands:                              | $0 \le k \le 255$           | 5                                                                      |                                             | Operands:                 | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                  |                                                                                    |                                             |  |

| Operation:                             | (W) x k $\rightarrow$       | PRODH:PRO                                                              | DL                                          |                           | a ∈ [0,1]                                                                                                                                                                                                                                                                                            |                                                                                    |                                             |  |

| Status Affected:                       | None                        |                                                                        |                                             | Operation:                | $(W) \mathrel{x} (f) \to P$                                                                                                                                                                                                                                                                          | RODH:PROD                                                                          | L                                           |  |

| Encoding:                              | 0000                        | 1101 kk                                                                | kk kkkk                                     | Status Affected:          | None                                                                                                                                                                                                                                                                                                 |                                                                                    |                                             |  |

| Description:                           | out betwee<br>8-bit literal | ed multiplication<br>on the contents<br>'k'. The 16-bit<br>he PRODH:PF | of W and the result is                      | Encoding:<br>Description: | 0000         001a         ffff         ffff           An unsigned multiplication is carried out<br>between the contents of W and the<br>register file location 'f'. The 16-bit result i<br>stored in the PRODH:PRODL register<br>pair. PRODH contains the high byte. Bot<br>W and 'f' are unchanged. |                                                                                    |                                             |  |

|                                        | pair. PROE<br>W is uncha    | OH contains th<br>anged.                                               | e high byte.                                |                           |                                                                                                                                                                                                                                                                                                      |                                                                                    |                                             |  |

|                                        | None of the                 | e Status flags                                                         | are affected.                               |                           | None of the S                                                                                                                                                                                                                                                                                        | •                                                                                  | e affected                                  |  |

|                                        | possible in                 | either Overflo<br>this operation<br>but not detect                     | A Zero result                               |                           | Note that neither Overflow nor Carry is possible in this operation. A Zero result possible but not detected.                                                                                                                                                                                         |                                                                                    |                                             |  |

| Words:                                 | 1                           |                                                                        |                                             |                           | •                                                                                                                                                                                                                                                                                                    |                                                                                    | k is selected. If                           |  |

| Cycles:<br>Q Cycle Activity:           | 1                           |                                                                        |                                             |                           | 'a' is '1', the E<br>GPR bank (de                                                                                                                                                                                                                                                                    | BSR is used to                                                                     |                                             |  |

| Q1<br>Decode                           | Q2<br>Read<br>literal 'k'   | Q3<br>Process<br>Data                                                  | Q4<br>Write<br>registers<br>PRODH:<br>PRODL |                           | is enabled, th<br>Indexed Liter<br>whenever f ≤<br>Section 29.2<br>Bit-Oriented                                                                                                                                                                                                                      | is instruction<br>al Offset Addr<br>95 (5Fh). See<br>.3 "Byte-Orie<br>Instructions | essing mode<br>ented and<br>in Indexed      |  |

| Example:                               | MULLW                       | 0C4h                                                                   |                                             |                           | Literal Offse                                                                                                                                                                                                                                                                                        | t Mode" for d                                                                      | etails.                                     |  |

| Before Instruc                         | ction                       |                                                                        |                                             | Words:                    | 1                                                                                                                                                                                                                                                                                                    |                                                                                    |                                             |  |

| W<br>PRODH                             | = E2<br>= ?                 | 2h                                                                     |                                             | Cycles:                   | 1                                                                                                                                                                                                                                                                                                    |                                                                                    |                                             |  |

| PRODL                                  | = ?                         |                                                                        |                                             | Q Cycle Activity:         |                                                                                                                                                                                                                                                                                                      | 02                                                                                 | 04                                          |  |

| After Instructi<br>W<br>PRODH<br>PRODL | = E2                        | Dh                                                                     |                                             | Q1<br>Decode              | Q2<br>Read<br>register 'f'                                                                                                                                                                                                                                                                           | Q3<br>Process<br>Data                                                              | Q4<br>Write<br>registers<br>PRODH:<br>PRODL |  |

|                                        |                             |                                                                        |                                             | Example:<br>Before Instri | MULWF                                                                                                                                                                                                                                                                                                | REG, 1                                                                             |                                             |  |

Before Instruction

W

=

C4h

REG

=

B5h

PRODH

=

?

PRODL

=

?

After Instruction

W

=

C4h

REG

=

B5h

PRODH

=

24h

PRODH

=

8Ah

PRODH

=

94h

| SUBLW Subtract W from Literal |                |                  |                      |                      |        |      |               |  |

|-------------------------------|----------------|------------------|----------------------|----------------------|--------|------|---------------|--|

| Syntax:                       | yntax: SUBLW k |                  |                      |                      |        |      |               |  |

| Operands:                     | C              | $0 \le k \le 2$  | 255                  | 5                    |        |      |               |  |

| Operation:                    | k              | - (W) -          | $\rightarrow$        | W                    |        |      |               |  |

| Status Affected:              | ١              | 1, OV, C         | C, I                 | DC, Z                |        |      |               |  |

| Encoding:                     |                | 0000             |                      | 1000                 | kkł    | ĸk   | kkkk          |  |

| Description:                  |                |                  |                      | acted from           |        |      |               |  |

| Words:                        | 1              |                  |                      |                      |        |      |               |  |

| Cycles:                       | 1              |                  |                      |                      |        |      |               |  |

| Q Cycle Activity:             |                |                  |                      |                      |        |      |               |  |

| Q1                            |                | Q2               |                      | Q3                   |        |      | Q4            |  |

| Decode                        | -              | Read<br>eral 'k' |                      |                      |        |      | Vrite to<br>W |  |

| Example 1:                    | S              | SUBLW            | С                    | 2h                   |        |      |               |  |

| Before Instruc                | tion           |                  |                      |                      |        |      |               |  |

| W<br>C                        | =              | 01h<br>?         |                      |                      |        |      |               |  |

| After Instruction             | on             | ·                |                      |                      |        |      |               |  |

| W<br>C                        | =              | <b>01h</b><br>1  | ; result is positive |                      |        |      |               |  |

| Z                             | =              | 0                | , '                  | iesuit is p          | JUSITI |      |               |  |

| N                             | =              | 0                |                      |                      |        |      |               |  |

| Example 2:                    |                | SUBLW            | C                    | 2h                   |        |      |               |  |

| Before Instruc<br>W           | tion<br>=      | 02h              |                      |                      |        |      |               |  |

| ċ                             | =              | ?                |                      |                      |        |      |               |  |

| After Instructio<br>W         | on<br>=        | 00h              |                      |                      |        |      |               |  |

| Ċ                             | =              | 1                | ;।                   | result is z          | zero   |      |               |  |

| Z<br>N                        | =              | 1<br>0           |                      |                      |        |      |               |  |

| Example 3:                    | 2              | SUBLW            | C                    | 2h                   |        |      |               |  |

| Before Instruc                | tion           |                  |                      |                      |        |      |               |  |

| W<br>C                        | =              | 03h<br>?         |                      |                      |        |      |               |  |

| After Instruction             | on             |                  |                      |                      |        |      |               |  |